### **General Description**

The MAX97200 is a 45mW Class H headphone amplifier that runs from a single low 1.8V supply voltage and employs Maxim's second-generation DirectDrive® technology.

The MAX97200 features a Dual Mode™ internal charge pump to generate the power rails for the amplifier. The charge-pump output can be ±PVIN/2 or ±PVIN depending on the amplitude of the output signal. When the output voltage is low, the power-supply voltage is ±PVIN/2. When the output signal demands larger output voltage, the charge pump switches modes so that a greater power-supply voltage is realized and more output power can be delivered to the load.

Second-generation DirectDrive technology improves power consumption when compared to first-generation DirectDrive amplifiers. The MAX97200 can be powered from a regulated 1.8V and have similar power consumption to a traditional DirectDrive amplifier that is powered from 0.9V.

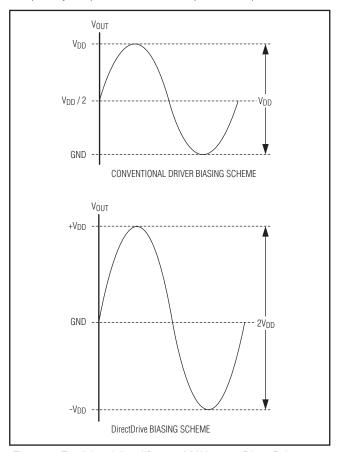

Maxim's DirectDrive architecture uses an inverting charge pump to derive a negative voltage supply. The headphone amplifier is powered between the positive supply and the generated negative rail. This scheme allows the audio output signal to be biased about ground, eliminating the need for large DC-blocking capacitors between the amplifier output and the headphone load.

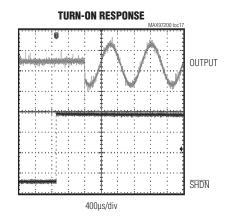

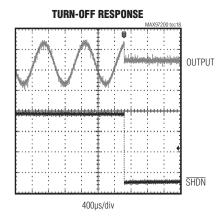

Low-output offset voltage provides very good click-andpop performance both into and out of shutdown. High signal-to-noise ratio maintains system fidelity.

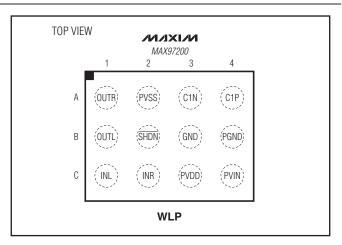

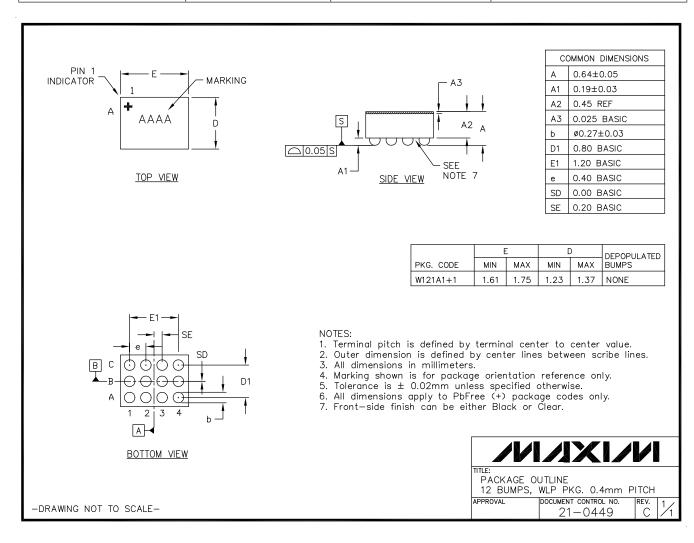

The MAX97200 is available in a tiny, 12-bump wafer level packaging (WLP 1.27mm x 1.65mm) with a small, 0.4mm lead pitch and specified over the -40°C to +85°C extended temperature range.

### **Applications**

Cellular Phones

Smartphones

MP3 Players

**VoIP Phones**

DirectDrive is a registered trademark of Maxim Integrated Products, Inc.

Dual Mode is a trademark of Maxim Integrated Products, Inc.

#### **Features**

- ♦ Second-Generation DirectDrive Technology

- ♦ Dynamic, Class H, Dual Mode Charge Pump

- **♦** Low Voltage Operation, VPVIN = 1.8V

- **♦** Low Quiescent Current, 1.15mA (typ) at VPVIN = 1.8V

- ♦ Eliminates Large Output DC-Blocking Capacitors

- ♦ Industry-Leading Click-and-Pop Performance

- ♦ High-Fidelity, SNR 105dB (5.6µV Output Noise)

- ♦ Output Power 34mW into 32Ω (THD+N 1%)

- ♦ Output Power 45mW into 16Ω (THD+N 10%)

- ♦ Tiny, 12-Bump, 1.27mm x 1.65mm (0.4mm Lead Pitch) WLP Package

### **Ordering Information**/ Selector Guide

| PART          | GAIN<br>(dB) | PIN-<br>PACKAGE | TOP<br>MARK |  |

|---------------|--------------|-----------------|-------------|--|

| MAX97200AEWC+ | 3            | 12 WLP          | ABF         |  |

| MAX97200BEWC+ | 0            | 12 WLP          | ABG         |  |

Note: All devices operate over the -40°C to +85°C tempera-

+Denotes a lead(Pb)-free and RoHS-compliant package.

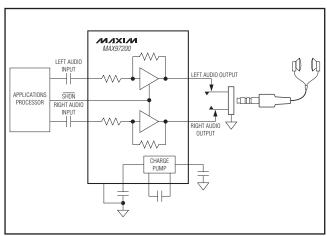

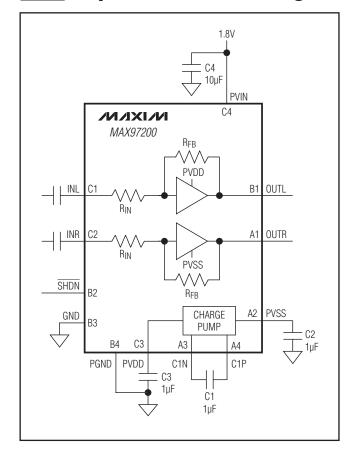

### **Typical Operating Circuit**

#### **ABSOLUTE MAXIMUM RATINGS**

| PVIN or PVDD to PGND         | 0.3V to +2.2V                  |

|------------------------------|--------------------------------|

| GND to PGND                  | 0.3V to +0.3V                  |

| PVSS to PGND                 | 2.2V to +0.3V                  |

| OUT_ and IN_ to GND          | (PVSS - 0.2V) to (PVDD + 0.2V) |

| C1P, C1N                     | Cap connection only            |

| SHDN to GND                  | 0.3V to +4V                    |

| Output Short-Circuit Current | Continuous                     |

| Thermal Limits (Note 1)      |                                |

| Multiple Layer PCB           |                                |

| Continuous Power Dissipation (TA = +70° | °C)            |

|-----------------------------------------|----------------|

| 12-Bump WLP (derate 13.7mW/°C above     | +70°C)1095mW   |

| Junction Temperature                    | +150°C         |

| Operating Temperature Range             | 40°C to +85°C  |

| Storage Temperature Range               | 65°C to +150°C |

| Soldering Temperature (reflow)          | +260°C         |

|                                         |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **PACKAGE THERMAL CHARACTERISTICS (Note 1)**

| Junction-to-Ambient Thermal Resistance (θJA) | .73°C/W |

|----------------------------------------------|---------|

| Junction-to-Case Thermal Resistance (ACA)    | 30°C/W  |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to **www.maxim-ic.com/thermal-tutorial**.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{PVIN} = 1.8V, V_{PGND} = V_{GND} = 0V, V_{\overline{SHDN}} = 1.8V, C1 = C2 = C3 = 1\mu F, C4 = 10\mu F, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                    | SYMBOL             | CONDITIONS                                                                                                                                | CONDITIONS MIN TYP MAX |      | MAX  | UNITS |  |

|------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|------|-------|--|

| POWER SUPPLY                 |                    |                                                                                                                                           |                        |      |      |       |  |

| Supply Voltage Range         | PVIN               | Guaranteed by PSRR                                                                                                                        | 1.62                   | 1.80 | 1.98 | V     |  |

| UVLO Rising                  |                    |                                                                                                                                           |                        | 1.48 | 1.58 | V     |  |

| UVLO Falling                 |                    |                                                                                                                                           | 1.36                   | 1.46 |      | V     |  |

| Outles agent Complex Comment | loo                | Inputs grounded, TA = +25°C, no load                                                                                                      |                        | 1.15 | 1.7  | - mA  |  |

| Quiescent Supply Current     | IDD                | 16Ω load, inputs grounded, $T_A = +25$ °C                                                                                                 |                        | 1.16 |      | mA    |  |

| Shutdown Current             | ISHDN              | VSHDN = 0V, TA = +25°C                                                                                                                    |                        | 0.2  |      | μΑ    |  |

| Turn-On Time                 | ton                |                                                                                                                                           |                        | 0.6  | 1    | ms    |  |

| CHARGE PUMP                  |                    |                                                                                                                                           |                        |      |      |       |  |

| Oscillator Frequency         | fosc1              | V <sub>OUT</sub> = 0V, T <sub>A</sub> = +25°C                                                                                             | 78                     | 83   | 88   | kHz   |  |

| Oscillator Frequency         | fosc2              | V <sub>OUT</sub> = 0.2V, R <sub>L</sub> = ∞, f <sub>IN</sub> = 1kHz                                                                       |                        | 665  |      | kHz   |  |

| Oscillator Frequency         | fosc3              | V <sub>OUT</sub> = 0.5V, R <sub>L</sub> = ∞, f <sub>IN</sub> = 1kHz                                                                       |                        | 500  |      | kHz   |  |

| Positive Output Voltage      | V <sub>P</sub> VDD | V <sub>OUT</sub> = 0.2V, R <sub>L</sub> = ∞                                                                                               | PVIN/2                 |      |      | V     |  |

|                              |                    | V <sub>OUT</sub> = 0.5V, R <sub>L</sub> = ∞                                                                                               |                        | PVIN |      |       |  |

| Negative Output Valtage      | 1/51/00            | Vout = 0.2V, R <sub>L</sub> = ∞                                                                                                           | -PVIN/2<br>-PVIN       |      | V    |       |  |

| Negative Output Voltage      | VPVSS              | V <sub>OUT</sub> = 0.5V, R <sub>L</sub> = ∞                                                                                               |                        |      | V    |       |  |

| Output Voltage Threshold     | VTH1               | $R_L = \infty$ , output voltage at which the charge pump switches modes, V <sub>OUT</sub> rising, transition from 1/8 to normal frequency | ±PVIN<br>x<br>0.08     |      | V    |       |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(VPVIN = 1.8V, VPGND = VGND = 0V, V\overline{SHDN} = 1.8V, C1 = C2 = C3 = 1\mu F, C4 = 10\mu F, TA = TMIN to TMAX, unless otherwise noted. Typical values are at TA = +25°C) (Note 2)$

| PARAMETER                        | SYMBOL                     | CONDI                                                                                                                                                        | TIONS                    | MIN   | TYP                | MAX   | UNITS |  |

|----------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------|--------------------|-------|-------|--|

| Output Voltage Threshold         | V <sub>TH2</sub>           | R <sub>L</sub> = ∞, output voltage at which the charge pump switches modes, V <sub>OUT</sub> rising, transition from high-efficiency mode to high-power mode |                          |       | ±PVIN<br>x<br>0.24 |       | V     |  |

| Charge-Pump Mode Transition      | tHOLD                      | Time it takes for the cl<br>transition from high-po<br>high-efficiency mode;                                                                                 | ower mode to             |       | 32                 |       | ms    |  |

| Timeouts (Figure 2)              | tRISE                      | Time it takes for the charge pump to transition from high-efficiency mode to high-power mode (90% of its value); R <sub>L</sub> = ∞                          |                          |       | 20                 |       | μs    |  |

| AMPLIFIER                        |                            |                                                                                                                                                              |                          |       |                    |       |       |  |

| Voltago Gain                     | Av                         | MAX97200A                                                                                                                                                    |                          | 2.75  | 2.92               | 3.09  | dB    |  |

| Voltage Gain                     | AV                         | MAX97200B                                                                                                                                                    |                          | -0.17 | 0                  | +0.17 | uв    |  |

| Maximum Output Voltage           |                            | $R_L = 10k\Omega$ , THD+N =                                                                                                                                  | 1%                       |       | 1.295              |       | VPK   |  |

| Maximum Output Voltage           |                            | $R_L = 10k\Omega$ , THD+N =                                                                                                                                  | 10%                      |       | 1.44               |       | VPK   |  |

| Channel-to-Channel Gain Matching |                            |                                                                                                                                                              |                          |       | ±0.1               |       | dB    |  |

| Total Output Offset Voltage      | Vos                        | TA = +25°C                                                                                                                                                   |                          |       | ±0.1               | ±0.3  | mV    |  |

| Input Desistance                 | Dur                        | MAX97200A                                                                                                                                                    |                          | 6     | 10                 | 14    | 10    |  |

| Input Resistance                 | Resistance R <sub>IN</sub> |                                                                                                                                                              | MAX97200B                |       | 12                 | 16.8  | kΩ    |  |

|                                  |                            | $V_{PVDD} = 1.62V \text{ to } 1.98$                                                                                                                          | $BV, T_A = +25^{\circ}C$ | 62    | 83                 |       |       |  |

| Power-Supply Rejection Ratio     | PSRR                       | 100mV <sub>P-P</sub> ripple                                                                                                                                  | fin = 217Hz              |       | 96                 |       | dB    |  |

| Tower-Supply Rejection Ratio     |                            |                                                                                                                                                              | f <sub>IN</sub> = 1kHz   |       | 94                 |       |       |  |

|                                  |                            |                                                                                                                                                              | fin = 20kHz              |       | 61                 |       |       |  |

|                                  |                            |                                                                                                                                                              | $R_L = 10k\Omega$        |       | 0.16               |       |       |  |

| Output Power                     | Pout                       | THD+N = 1%                                                                                                                                                   | $R_L = 32\Omega$         |       | 34                 |       | mW    |  |

|                                  |                            |                                                                                                                                                              | $R_L = 16\Omega$         | 45    |                    |       |       |  |

| Line Output Voltage              | VLINE                      | $R_L = 10k\Omega$                                                                                                                                            |                          |       | 1                  |       | VRMS  |  |

| Total Harmonic Distortion Plus   |                            | $R_L = 16\Omega$ , $P_{OUT} = 0.1$ mW, $f_{IN} = 1$ kHz (Note 3)                                                                                             |                          |       | 0.02               |       |       |  |

| Noise                            | THD+N                      | THD+N $R_L = 16\Omega$ , $P_{OUT} = 10$ mW, $f_{IN} = 1$ kHz (No                                                                                             |                          |       | 0.003              |       | %     |  |

| Noise                            |                            | $R_L = 10k\Omega$ , $V_{OUT} = 1V$ , $f_{IN} = 1kHz$ (Note 4)                                                                                                |                          |       | 0.008              |       |       |  |

| Output Noise                     | VN                         | Inputs grounded, A-weighted, MAX97200B                                                                                                                       |                          |       | 5.6                |       | μV    |  |

| Signal-to-Noise Ratio            | SNR                        | A-weighted, MAX97200B                                                                                                                                        |                          |       | 105                |       | dB    |  |

| Click-and-Pop Level              | VCP                        | $R_L = 32\Omega$ , peak voltage, A-weighted,                                                                                                                 | Into shutdown            |       | 80                 |       | dBV   |  |

| Choix and 1 Op Lover             |                            | 32 samples/second,<br>MAX97200B                                                                                                                              | Out of shutdown          |       | 68                 |       | GD V  |  |

| Crosstalk                        | XTALK                      | $R_L = 16\Omega$ , 1kHz, $P_{OUT} = 5$ mW 94                                                                                                                 |                          | dB    |                    |       |       |  |

| Maximum Capacitive Load          |                            |                                                                                                                                                              |                          |       | 200                |       | pF    |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{PVIN} = 1.8V, V_{PGND} = V_{GND} = 0V, V_{\overline{SHDN}} = 1.8V, C1 = C2 = C3 = 1\mu F, C4 = 10\mu F, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25$ °C) (Note 2)

| PARAMETER             | SYMBOL | BOL CONDITIONS                                 |     | TYP | MAX | UNITS |

|-----------------------|--------|------------------------------------------------|-----|-----|-----|-------|

| DIGITAL INPUT (SHDN)  |        |                                                |     |     |     |       |

| Input High Voltage    | VIH    |                                                | 1.4 |     | ,   | V     |

| Input Low Voltage     | VIL    |                                                |     |     | 0.4 | V     |

|                       | luu    | V <del>SHDN</del> = 4V, T <sub>A</sub> = +25°C | -1  |     | +1  |       |

| Input Leakage Current | IIH    | VSHDN = 1.8V, TA = +25°C                       | -1  |     | +1  | μΑ    |

|                       | IIL    | VSHDN = 0V, TA = +25°C                         | -1  |     | +1  |       |

Note 2: All specifications are 100% tested at  $T_A = +25^{\circ}C$ . Temperature limits are guaranteed by design.

**Note 3:**  $V_{PVDD} = 0.9V$ ,  $V_{PVSS} = -0.9V$ .

Note 4: VPVDD = 1.8V, VPVSS = -1.8V.

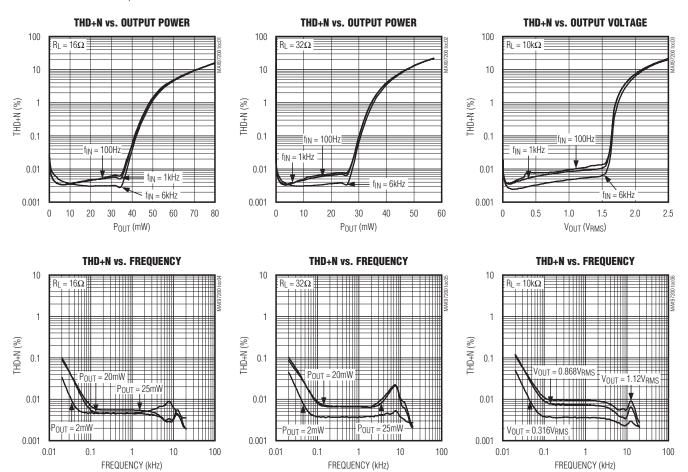

### Typical Operating Characteristics

$(V_{PVIN} = 1.8V, V_{PGND} = V_{GND} = 0V, V_{\overline{SHDN}} = 1.8V, C1 = C2 = C3 = 1\mu F, C4 = 10\mu F, both channels driven in phase, T_A = +25°C, unless otherwise noted.)$

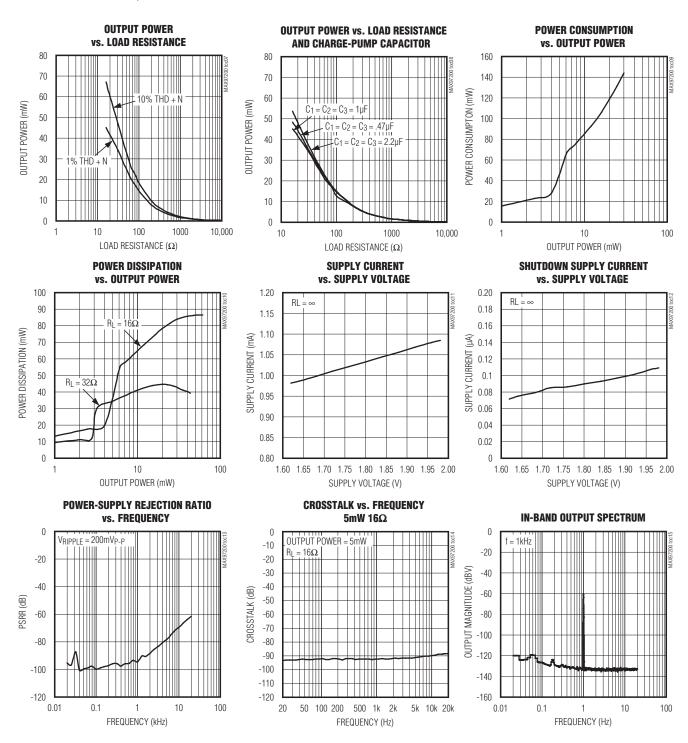

### **Typical Operating Characteristics (continued)**

$(V_{PVIN} = 1.8V, V_{PGND} = V_{GND} = 0V, V_{\overline{SHDN}} = 1.8V, C1 = C2 = C3 = 1\mu F, C4 = 10\mu F, both channels driven in phase, T_A = +25°C, unless otherwise noted.)$

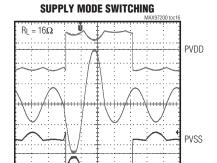

### Typical Operating Characteristics (continued)

(V<sub>PVIN</sub> = 1.8V, V<sub>PGND</sub> = V<sub>GND</sub> = 0V, V<sub>SHDN</sub> = 1.8V, C1 = C2 = C3 = 1μF, C4 = 10μF, both channels driven in phase, T<sub>A</sub> = +25°C, unless otherwise noted.)

20ms/div

**Pin Configuration**

## **Pin Description**

| BUMP | NAME | FUNCTION                                                                               |

|------|------|----------------------------------------------------------------------------------------|

| A1   | OUTR | Right Amplifier Output                                                                 |

| A2   | PVSS | Negative Charge-Pump Output. Connect a 1µF capacitor between PVSS and PGND.            |

| АЗ   | C1N  | Charge-Pump Flying Cap Negative Connection. Connect 1µF capacitor between C1N and C1P. |

| A4   | C1P  | Charge-Pump Flying Cap Positive Connection. Connect 1µF capacitor between C1P and C1N. |

| B1   | OUTL | Left Amplifier Output                                                                  |

| B2   | SHDN | Active-Low Shutdown                                                                    |

| В3   | GND  | Signal Ground. Connect to PGND.                                                        |

| B4   | PGND | Power Ground. Connect to GND.                                                          |

| C1   | INL  | Left Audio Input                                                                       |

| C2   | INR  | Right Audio Input                                                                      |

| C3   | PVDD | Positive Charge-Pump Output. Bypass to PGND with 1µF.                                  |

| C4   | PVIN | Main Power-Supply Connection. Bypass to PGND with 10µF.                                |

### **Detailed Description**

The MAX97200 is a 45mW Class H headphone amplifier that runs from a single low 1.8V supply voltage and employs Maxim's second-generation DirectDrive technology.

Maxim's DirectDrive architecture uses an inverting charge pump to derive a negative voltage supply. The headphone amplifier is powered between the positive supply and the generated negative rail. This scheme allows the audio output signal to be biased about ground, eliminating the need for large DC blocking capacitors between the amplifier output and the headphone load.

Second-generation DirectDrive technology improves power consumption when compared to first-generation DirectDrive amplifiers. The MAX97200 can be powered from a regulated 1.8V supply and have similar power consumption to a traditional DirectDrive amplifier that is powered from 0.9V.

The MAX97200 features a dual-mode internal charge pump to generate the power rails for the DirectDrive amplifier. The charge-pump output can be ±PVIN/2 or ±PVIN depending on the amplitude of the output signal. When the output voltage is low the power-supply voltage is ±PVIN/2. When the output signal demands larger output voltage, the charge pump switches modes so that a greater power-supply voltage is realized and more output power can be delivered to the load.

#### DirectDrive Headphone Amplifier

Traditional single-supply headphone amplifiers have outputs biased at a nominal DC voltage (typically half the supply). Large coupling capacitors are needed to block this DC bias from the headphone. Without these capacitors, a significant amount of DC current flows to the headphone, resulting in unnecessary power dissipation and possible damage to both headphone and headphone amplifier.

Maxim's second-generation DirectDrive architecture uses a charge pump to create an internal negative supply voltage. This allows the headphone outputs of the MAX97200 to be biased at GND while operating from a single supply (Figure 1). Without a DC component, there is no need for the large DC-blocking capacitors. Instead of two large (220 $\mu$ F typ) capacitors, the MAX97200 charge pump requires 3 small ceramic capacitors, conserving board space, reducing cost, and improving the frequency response of the headphone amplifier.

Figure 1. Traditional Amplifier vs. MAX97200 DirectDrive Output

#### **Dual Mode Charge Pump**

The MAX97200's Dual Mode, charge pump outputs either ±PVIN/2 in high-efficiency mode or ±PVIN in high-power mode, resulting in a power-supply differential of 1.8V or 3.6V. The charge-pump mode changes based on the level of the output signal needed. When the output voltage is small, the voltage rails are reduced to minimize power consumption. When the output voltage is large, the voltage rails are increased to accommodate the larger output need.

High-power mode is similar to Maxim's traditional DirectDrive architecture and is best suited for loads that require high voltage swing. High-efficiency mode improves power consumption by reducing the power-supply voltage across the amplifier's output stage by half. The reduced power-supply voltage is good for idle conditions or low-signal level conditions into a head-phone.

#### **Class H Operation**

The MAX97200's internal Class H amplifier uses a class AB output stage with multiple, discrete power supplies. This result's in two power-supply differentials of 1.8V and 3.6V generated from a single 1.8V external supply. The PVIN/2 power-supply differential is used when the output voltage requirements are low, and the output is below VTH2 as seen in Figure 2. The higher supply differential is used when the output voltage exceeds the high threshold VTH2, maximizing output power and voltage swing. The transition time from high-efficiency mode to high-power mode occurs when the threshold is crossed.

Figure 2. Inverting and Split Mode Transitions

The switch from high-power mode to high-efficiency mode occurs 32ms (typ) after the threshold is crossed. Built-in hysteresis keeps the charge pump from erratic mode switching when the output voltage is near the high and low thresholds.

#### Click-and-Pop Suppression

In conventional single-supply audio amplifiers, the output-coupling capacitor contributes significantly to audible clicks and pops. Upon startup, the amplifier charges the coupling capacitor to its bias voltage, typically half the supply. Likewise, on shutdown, the capacitor is discharged. This results in a DC shift across the capacitor, which appears as an audible transient at the speaker. Since the MAX97200 does not require output coupling capacitors, this problem does not arise. Additionally, the MAX97200 features extensive click-and-pop suppression that eliminates any audible transient sources internal to the device.

Typically, the output of the device driving the MAX97200 has a DC bias of half the supply voltage. At startup, the input-coupling capacitor,  $C_{IN}$ , is charged to the preamplifier's DC bias voltage through the MAX97200 input resistor,  $R_{IN}$ . This DC shift across the capacitor results in an audible click-and-pop. The MAX97200 precharges the input capacitors when power is applied to ensure that no audible clicks or pops are heard when  $\overline{SHDN}$  is pulled high.

#### Shutdown

The MAX97200 features a 1 $\mu$ A, low-power shutdown mode that reduces quiescent current consumption and extends battery life. Shutdown is controlled by the  $\overline{SHDN}$  input. Driving the  $\overline{SHDN}$  input low disables the drive amplifiers and charge pump and sets the headphone amplifier output resistance to  $100\Omega$ .

### **Applications Information**

# Component Selection Input-Coupling Capacitor

The input capacitor ( $C_{IN}$ ), in conjunction with the amplifier input resistance ( $R_{IN}$ ), forms a highpass filter that removes the DC bias from the incoming signal. The AC-coupling capacitor allows the amplifier to bias the signal to an optimum DC level. Assuming zero source impedance, the -3dB point of the highpass filter is given by:

$$f-_{3dB} = \frac{1}{2\pi R_{IN}C_{IN}}$$

$R_{\mbox{\footnotesize{IN}}}$  is the amplifier's input resistance value. Choose  $C_{\mbox{\footnotesize{IN}}}$  such that  $f_{\mbox{\footnotesize{-3dB}}}$  is well below the lowest frequency of interest. Setting  $f_{\mbox{\footnotesize{-3dB}}}$  too high affects the amplifier's low frequency. Capacitors with higher voltage coefficients, such as ceramics, result in increased distortion at low frequencies.

#### Charge-Pump Capacitor Selection

Use capacitors with an ESR less than  $100m\Omega$  for optimum performance. Low ESR ceramic capacitors minimize the output resistance of the charge pump. For best performance over the extended temperature range, select capacitors with an X7R dielectric.

#### Flying Capacitor (C1)

The value of the flying capacitor (C1) affects the load regulation and output resistance of the charge pump. A C1 value that is too small degrades the device's ability to provide sufficient current drive, which leads to a loss of output voltage. Connect a  $1\mu F$  capacitor between C1P and C1N.

#### Output Capacitors (C2, C3)

The output capacitor value and ESR directly affect the ripple at PVSS. Increasing the value of C2 and C3 reduces output ripple. Likewise, decreasing the ESR of C2 and C3 reduces both ripple and output resistance. Lower capacitance values can be used in systems with low maximum output power levels. Connect a  $1\mu F$  capacitor between PVDD and PGND. Connect a  $1\mu F$  capacitor between PVSS and PGND.

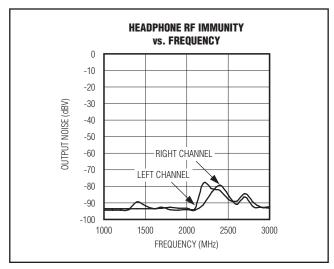

#### **RF Susceptibility**

Improvements to both layout and component selection can decrease the MAX97200 susceptibility to RF noise and prevent RF signals from being demodulated into audible noise. Trace lengths should be kept below  $\frac{1}{4}$  of the wavelength of the RF frequency of interest. Minimizing the trace lengths prevents the traces from functioning as antennas and coupling RF signals into the MAX97200. The wavelength  $(\lambda)$  in meters is given by:

$$\lambda = c/f$$

where  $c = 3 \times 10^8$  m/s, and f is the RF frequency of interest.

Route audio signals to the middle layers of the PCB to allow the ground planes above and below to shield them from RF interference. Ideally, the top and bottom layers of the PCB should primarily be ground planes to create effective shielding.

Additional RF immunity can also be obtained from relying on the self-resonant frequency of capacitors as it exhibits the frequency response similar to a notch filter. Depending on the manufacturer, 10pF to 20pF capacitors typically exhibit self resonance at RF frequencies. These capacitors when placed at the input pins can effectively shunt the RF noise at the inputs of the MAX97200. For these capacitors to be effective, provide a low-impedance, low-inductance path from the capacitors to the ground plane. Do not use microvias to connect to the ground plane as these vias do not conduct well at RF frequencies. Figure 3 shows headphone RF immunity with a well laid out PCB.

Figure 3. Headphone RF Immunity

#### **Layout and Grounding**

Proper layout and grounding are essential for optimum performance. Use large traces for the power-supply inputs and amplifier outputs to minimize losses due to parasitic trace resistance, as well as route heat away from the device. Good grounding improves audio performance, minimizes crosstalk between channels, and prevents switching noise from coupling into the audio signal. Connect PGND and GND together at a single point on the PCB. Route PGND and all traces that carry switching transients away from GND, and the traces and components in the audio signal path.

Connect C2 to the PGND plane. Place the charge-pump capacitors (C1, C2) as close as possible to the device. Bypass PVDD with a  $1\mu F$  capacitor to PGND. Place the bypass capacitors as close as possible to the device.

## Simplified Functional Diagram

**Chip Information**

PROCESS: BiCMOS

### Package Information

For the latest package outline information and land patterns (footprints), go to <a href="www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE PACKAGE CODE |          | OUTLINE NO.    | LAND<br>PATTERN NO.            |

|---------------------------|----------|----------------|--------------------------------|

| 12 WLP                    | W121A1+1 | <u>21-0449</u> | Refer to Application Note 1891 |

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                        | PAGES<br>CHANGED |

|--------------------|------------------|------------------------------------|------------------|

| 0                  | 1/10             | Initial release                    | _                |

| 1                  | 3/10             | Removed shutdown current max value | 2                |

| 2                  | 3/11             | Corrected crosstalk data in TOC 14 | 5                |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.