August 2011

## FMS6346E Six-Channel, Selectable SD / HD Video Filter Driver with Disable

#### **Features**

- Three Selectable 8/30MHz (SD/HD) Filters

- Three Fixed 8MHz (SD) Filters

- Enable / Disable Pin

- Input Clamp and Bias

- Single Video Load Drive ( $2V_{PP}$ ,  $150\Omega$ ,  $A_V = 6dB$ )

- AC- or DC-Coupled Inputs

- AC- or DC-Coupled Outputs

- Robust Output ESD Protection: 9kV HBM

### **Applications**

- Cable and Satellite Set-Top Boxes

- DVD Players

- HDTV

- Portable Media Players (PMP)

- Personal Video Recorders (PVR)

- Video On Demand (VOD)

#### Description

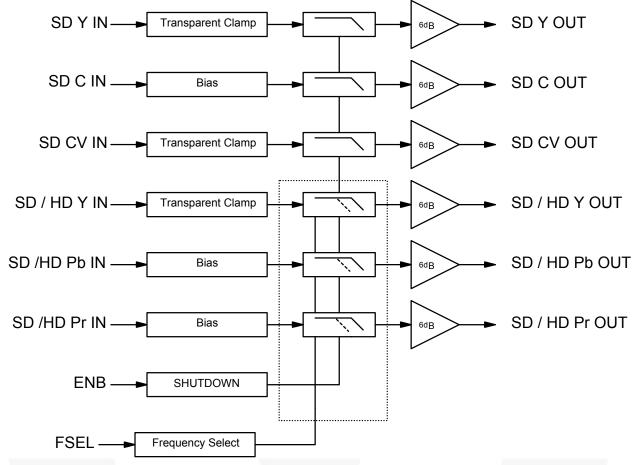

FMS6346E VoltagePlus™ video filter is intended to replace passive LC filters and drivers with a cost-effective integrated device. Six Butterworth filters improve image quality compared to typical passive solutions. The combination of low-power Standard-Definition (SD) and High-Definition (HD) filters greatly simplifies DVD video output circuitry. Three channels offer fixed SD 6<sup>th</sup>-order filters, while the other three are selectable between SD and HD 7<sup>th</sup>-order filters.

The FMS6346E offers a fixed gain of 6dB.

The FMS6346E may be directly driven by a DC-coupled DAC output or an AC-coupled signal. Internal diode clamps and bias circuitry may be used if AC-coupled inputs are required (see the Applications Information section for details).

The outputs can drive AC- or DC-coupled single (150 $\Omega$ ) video loads. DC-coupling the outputs remove the need for output coupling capacitors. The input DC levels are offset approximately +280mV at the output.

### **Ordering Information**

| Part Number    | Operating<br>Temperature Range | Gain Setting | Package                                                | Packing Method      |

|----------------|--------------------------------|--------------|--------------------------------------------------------|---------------------|

| FMS6346EMTC20X | -40°C to +85°C                 | 6dB          | 20-Lead, Thin-Shrink Small-<br>Outline Package (TSSOP) | 2500 Units per Reel |

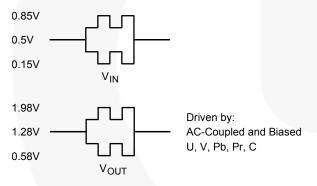

# Functional Block Diagram

Figure 1. Block Diagram

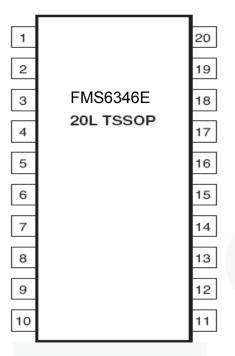

### **Pin Configuration**

Figure 2. Pin Layout

### **Pin Definitions**

| Pin# | Name              | Type   | Description                                                                      |  |

|------|-------------------|--------|----------------------------------------------------------------------------------|--|

| 1    | SD Y IN1          | Input  | SD Y Video Input, Channel 1                                                      |  |

| 2    | SD C IN2          | Input  | SD C Video Input, Channel 2                                                      |  |

| 3    | SD CV IN3         | Input  | SD CV Video Input, Channel 3                                                     |  |

| 4    | ENB               | Input  | Enable / Disable, ENB = GND (0): Device Enabled; ENB = HIGH (1): Device Disabled |  |

| 5    | $V_{CC}$          | Input  | +3.3V or 5.0V Supply                                                             |  |

| 6    | F <sub>cSEL</sub> | Input  | Selects Filter Corner Frequency for Pins 7, 8, and 9: "0" = SD, "1" = HD         |  |

| 7    | SD/HD Y IN1       | Input  | Selectable SD or HD Y Video Input, Channel 1                                     |  |

| 8    | SD/HD Pb IN2      | Input  | Selectable SD or HD Pb Video Input, Channel 2                                    |  |

| 9    | SD/HD Pr IN3      | Input  | Selectable SD or HD Pr Video Input, Channel 3                                    |  |

| 10   | N/C               | Input  | No Connection                                                                    |  |

| 11   | N/C               | Input  | No Connection                                                                    |  |

| 12   | SD/HD Pr OUT3     | Output | Filtered SD or HD Pr Video Output, Channel 3                                     |  |

| 13   | SD/HD Pb OUT2     | Output | Filtered SD or HD Pb Video Output, Channel 2                                     |  |

| 14   | SD/HD Y OUT1      | Output | Filtered SD or HD Y Video Output, Channel 1                                      |  |

| 15   | N/C               | Input  | No Connection                                                                    |  |

| 16   | GND               | Input  | Must Be Tied to Ground                                                           |  |

| 17   | GND               | Input  | Must Be Tied to Ground                                                           |  |

| 18   | SD CV OUT3        | Output | Filtered SD CV Video Output, Channel 3                                           |  |

| 19   | SD C OUT2         | Output | Filtered SD C Video Output, Channel 2                                            |  |

| 20   | SD Y OUT1         | Output | Filtered SD Y Video Output, Channel 1                                            |  |

### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           | Parameter                                      | Min. | Max.                 | Unit |

|------------------|------------------------------------------------|------|----------------------|------|

| V <sub>CC</sub>  | DC Supply Voltage                              | -0.3 | 6.0                  | V    |

| V <sub>IO</sub>  | Analog and Digital I/O                         | -0.3 | V <sub>CC</sub> +0.3 | V    |

| I <sub>OUT</sub> | Output Current, Any One Channel, Do Not Exceed |      | 50                   | mA   |

### **Reliability Information**

| Symbol           | Parameter                                                             | Min. | Тур. | Max. | Unit |

|------------------|-----------------------------------------------------------------------|------|------|------|------|

| T <sub>J</sub>   | Junction Temperature                                                  |      |      | +150 | °C   |

| T <sub>STG</sub> | Storage Temperature Range                                             | -65  |      | +150 | ů    |

| TL               | Reflow Temperature                                                    |      |      | +260 | °C   |

| $\Theta_{JA}$    | Thermal Resistance, JEDEC Standard Multi-Layer Test Boards, Still Air |      | 74   |      | °C/W |

### **Electrostatic Discharge Information**

| Symbol | Parameter                               | Max. | Unit |

|--------|-----------------------------------------|------|------|

| ECD    | Human Body Model, JESD22-A114           | 9    | kV   |

| ESD    | ESD Charged Device Model, JESD22-C101 2 |      | KV   |

### **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol          | Parameter                   | Min.  | Тур.  | Max.  | Unit |

|-----------------|-----------------------------|-------|-------|-------|------|

| T <sub>A</sub>  | Operating Temperature Range | -40   |       | +85   | ů    |

| V <sub>CC</sub> | Supply Voltage Range        | 3.135 | 3.300 | 5.250 | V    |

### **DC Electrical Characteristics**

Unless otherwise noted,  $T_A$ =25°C,  $V_{CC}$ =3.3V,  $R_{SOURCE}$ =37.5 $\Omega$ , inputs AC coupled with 0.1 $\mu$ F, all outputs AC coupled with 220 $\mu$ F into 150 $\Omega$  loads, and referenced to 400kHz.

| Symbol              | Parameter                         | Conditions                                     | Min. | Тур. | Max.            | Units    |

|---------------------|-----------------------------------|------------------------------------------------|------|------|-----------------|----------|

|                     | (1)                               | V <sub>CC</sub> = 3.3V, No Load,<br>EN=LOW     |      | 50   | 62              | mA       |

| Icc                 | Supply Current <sup>(1)</sup>     | $V_{CC}$ = 5.0V, No Load,<br>EN = LOW          |      | 60   | 70              | mA       |

| I <sub>CC_SD</sub>  | Shutdown Supply Current           | $V_{CC}$ = 3.3V or 5.0V, No<br>Load, EN = HIGH |      | 10   | 200             | μΑ       |

| V <sub>IN</sub>     | Video Input Voltage Range         | Referenced to GND if DC Coupled                |      | 1.2  |                 | $V_{PP}$ |

| $V_{IL}$            | Digital Input Low <sup>(1)</sup>  | EN = LOW, Device Enabled                       | 0    |      | 0.8             | V        |

| V <sub>IH</sub>     | Digital Input High <sup>(1)</sup> | EN = HIGH, Device<br>Disabled                  | 2.4  |      | V <sub>CC</sub> | V        |

| I <sub>EN_Low</sub> | Input Current                     | V <sub>IL</sub> = 0.8V                         |      | 0.01 | 1.00            | μA       |

| EN_HIGH             | Input Current                     | V <sub>IH</sub> = 2.4V                         |      | 0.01 | 1.00            | μA       |

| PSRR                | Power Supply Rejection Ratio      |                                                |      | -50  |                 | dB       |

#### Note:

1. 100% tested at TA=25°C.

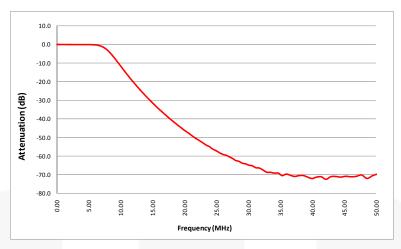

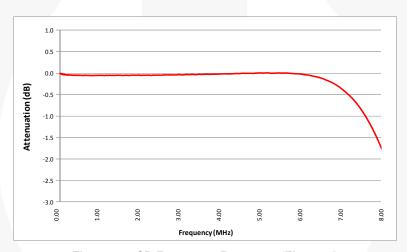

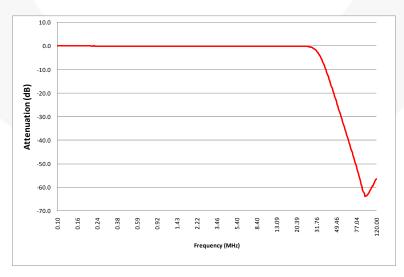

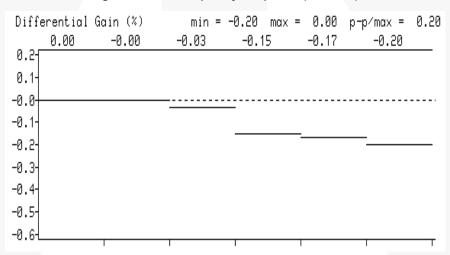

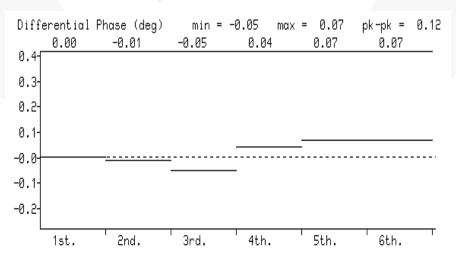

### Standard-Definition (480i) Electrical Characteristics

Unless otherwise noted,  $T_A$ =25°C,  $V_{IN}$ =1 $V_{PP}$ ,  $V_{CC}$ =3.3V,  $R_{SOURCE}$ =37.5 $\Omega$ , all inputs AC coupled with 0.1 $\mu$ F, all outputs AC coupled with 220 $\mu$ F into 150 $\Omega$  loads, and referenced to 400kHz.

| Symbol              | Parameter                                    | Conditions                                           | Min. | Тур. | Max. | Units |

|---------------------|----------------------------------------------|------------------------------------------------------|------|------|------|-------|

| $AV_{SD}$           | Channel Gain <sup>(2)</sup>                  | All SD Channels, DC                                  | 5.8  | 6.0  | 6.2  | dB    |

| f <sub>01dBSD</sub> | -0.1dB Flatness                              | All SD Channels                                      |      | 5.5  |      | MHz   |

| f <sub>1dBSD</sub>  | -1dB Flatness <sup>(2)</sup>                 | All SD Channels                                      | 5.50 | 7.15 |      | MHz   |

| $f_{cSD}$           | -3dB Bandwidth <sup>(2)</sup>                | All SD Channels                                      | 6.5  | 8.0  | 9    | MHz   |

| $f_{SBSD}$          | Attenuation (Stopband Reject) <sup>(2)</sup> | All SD Channels at f = 27MHz                         | 50   | 60   | 1    | dB    |

| DG                  | Differential Gain                            | All SD Channels                                      |      | 0.2  |      | %     |

| DP                  | Differential Phase                           | All SD Channels                                      |      | 0.4  |      | ٥     |

| THD                 | Total Harmonic Distortion, Output            | $V_{OUT} = 1.4V_{PP}, 3.58MHz$                       |      | 0.4  |      | %     |

| X <sub>TALKSD</sub> | Crosstalk (Channel-to-Channel)               | 1MHz                                                 |      | -70  |      | dB    |

| SNR                 | Signal-to-Noise Ratio <sup>(3)</sup>         | NTC-7 Weighting, 100kHz to 4.2MHz                    |      | 72   |      | dB    |

| t <sub>pdSD</sub>   | Propagation Delay                            | Delay from Input to Output,<br>4.5MHz                |      | 84   |      | ns    |

| CLG <sub>SD</sub>   | Chroma Luma Gain                             | f = 3.58MHz<br>(Refer to SD <sub>IN</sub> at 400kHz) |      | 100  |      | %     |

| CLD <sub>SD</sub>   | Chroma Luma Delay                            | f = 3.58MHz<br>(Refer to SD <sub>IN</sub> at 400kHz) |      | 6    |      | ns    |

#### Notes:

- 2. 100% tested at  $T_A$ =25°C.

- 3. SNR=20 log (714mV / rms noise).

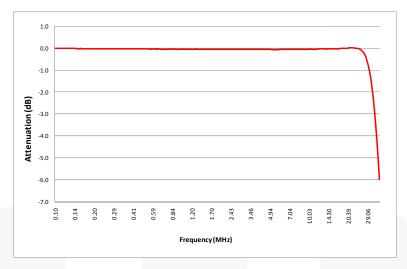

### **High-Definition Electrical Characteristics**

Unless otherwise noted,  $T_A$ =25°C,  $V_{IN}$ =1 $V_{PP}$ ,  $V_{CC}$ =3.3V,  $R_{SOURCE}$ =37.5 $\Omega$ , all inputs AC coupled with 0.1 $\mu$ F, all outputs AC coupled with 220 $\mu$ F into 150 $\Omega$  loads, and referenced to 400kHz.

| Symbol              | Parameter                            | Conditions                                       | Min. | Тур. | Max. | Units |

|---------------------|--------------------------------------|--------------------------------------------------|------|------|------|-------|

| $AV_{HD}$           | Channel Gain <sup>(4)</sup>          | All HD Channels, DC                              | 5.8  | 6.0  | 6.2  | dB    |

| BW <sub>0.5dB</sub> | +/-0.5dB Bandwidth <sup>(4)</sup>    | All HD Channels                                  |      | 28   |      | MHz   |

| BW-1dB              | -1dB Bandwidth <sup>(4)</sup>        | All HD Channels                                  | 28   | 31   |      | MHz   |

| BW-3dB              | -3dB Bandwidth <sup>(4)</sup>        | All HD Channels                                  | 30   | 32   |      | MHz   |

| Att37.125M          |                                      | $R_{SOURCE} = 75\Omega$ , $f = 37.325MHz$        |      | 6.5  |      | dB    |

| Att44.25M           | Normalized Stopband                  | $R_{SOURCE} = 75\Omega$ , $f = 44.25MHz$         |      | 14.5 |      | dB    |

| Att74.25M           | Attenuation <sup>(4)</sup>           | $R_{SOURCE} = 75\Omega$ , $f = 74.25MHz$         | 40   | 44   |      | dB    |

| Att <sub>78M</sub>  |                                      | $R_{SOURCE} = 75\Omega$ , $f = 78MHz$            | 42   | 46   |      | dB    |

| THD1                |                                      | $f = 10MHz; V_{OUT} = 1.4V_{PP}$                 |      | 0.4  |      | %     |

| THD2                | Output Distortion (All Channel)      | f = 15MHz; V <sub>OUT</sub> = 1.4V <sub>PP</sub> |      | 0.4  |      | %     |

| THD2                |                                      | $f = 30MHz; V_{OUT} = 1.4V_{PP}$                 | \    | 0.4  |      | %     |

| X <sub>TALKHD</sub> | Crosstalk (Channel-to-Channel)       | $f = 1.0MHz; V_{OUT} = 1.4V_{PP}$                |      | -60  |      | dB    |

| SNR                 | Signal-to-Noise Ratio <sup>(5)</sup> | Weighted; 100kHz to 30MHz                        |      | 72   |      | dB    |

| t <sub>pdHD</sub>   | Propagation Delay                    | Delay from Input to Output,<br>10MHz             |      | 24   |      | ns    |

#### Notes:

- 4. 100% tested at 25°C.

- 5. SNR=20 log (714mV / rms noise).

### **Typical Performance Characteristics**

Figure 3. SD Frequency Response

Figure 4. SD Frequency Response (Flatness)

Figure 5. HD Frequency Response

### **Typical Performance Characteristics** (Continued)

Figure 6. HD Frequency Response (Flatness)

Figure 7. Differential Gain

Figure 8. Differential Phase

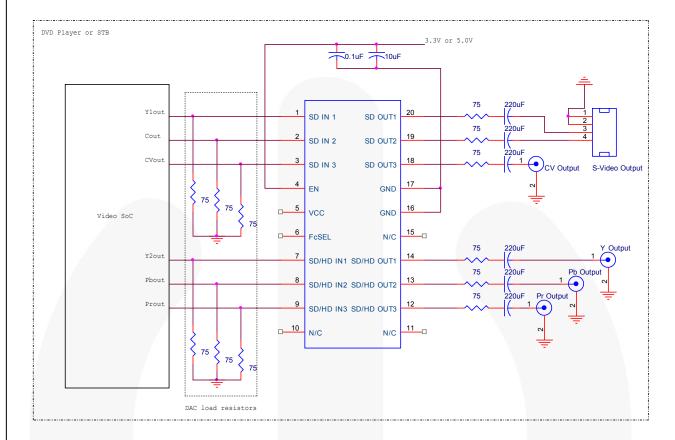

### **Typical Application**

Figure 9. Typical Application

#### **Applications Information**

#### **Functional Description**

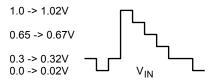

The FMS6346E VoltagePlus™ video filter provides 6dB gain from input to output. In addition, the input is slightly offset to optimize the output driver performance. The offset is held to the minimum required value to decrease the standing DC current into the load. Typical voltage levels are shown in Figure 10.

There is a 280mV offset from the DC input level to the  $^{\perp}$  DC output level.  $V_{OUT}$  = 2 •  $V_{IN}$  + 280mV.

Figure 10. Typical Voltage Levels

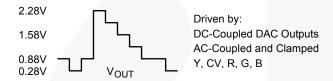

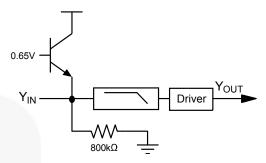

The FMS6346E offers three channels with internal diode clamps and three channels with biasing to support AC-coupled input signals. If the input signal does not go below ground, the input clamp does not operate. This allows DAC outputs to directly drive the FMS6346E without an AC-coupling capacitor. The worst-case synctip compression due to the clamp does not exceed 7mV. The input level set by the clamp, combined with the internal DC offset, keeps the output within its acceptable range. When the input is AC coupled, the diode clamp sets the sync-tip (or lowest voltage) just below ground.

For symmetric signals like C, Pb, and Pr; the average DC bias is fairly constant and the inputs are biased to set the DC input voltage to approximately 600mV. DAC outputs can also drive these same signals without the AC coupling capacitor. A conceptual illustration of the input clamp circuit is shown in Figure 11.

Figure 11. Input Clamp Circuit

#### I/O Configurations

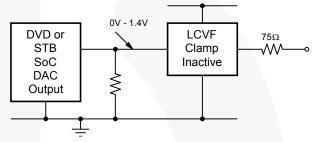

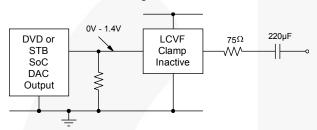

For DC-coupled DAC drive with DC-coupled outputs, use the configuration shown in Figure 12.

Figure 12. DC-Coupled Inputs and Outputs

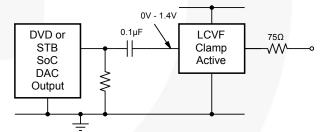

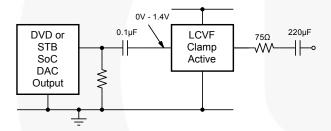

If the DAC's average DC output level causes the signal to exceed the range of 0V to 1.4V, it can be AC coupled as shown in Figure 13.

Figure 13. AC-Coupled Inputs, DC-Coupled Outputs

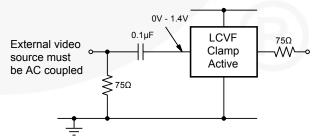

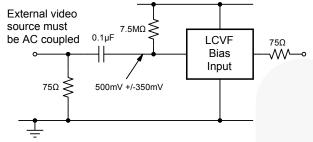

When driven by an unknown external source or a SCART switch with its own clamping circuitry, the inputs should be AC coupled as shown in Figure 14.

Figure 14. SCART Configuration with DC-Coupled Outputs

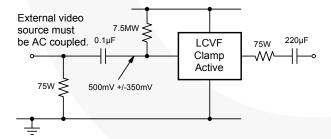

The same method can be used to bias the clamp signals.

Figure 15. Biased SCART with DC-Coupled Outputs

The same circuits can be used with AC-coupled outputs if desired, as shown in Figure 16.

Figure 16. DC-Coupled Inputs, AC-Coupled Outputs

Figure 17. Coupled Inputs, AC-Coupled Outputs

Figure 18. Biased SCART with AC-Coupled Outputs

#### Note:

The video tilt or line time distortion is dominated by the AC-coupling capacitor. The value may need to be increased beyond 220µF to obtain satisfactory operation in some applications.

#### **Power Dissipation**

The FMS6346E output drive configuration must be considered when calculating overall power dissipation. Care must be taken not to exceed the maximum die junction temperature. The following example can be used to calculate the power dissipation and internal temperature rise:

$$T_{J} = T_{A} + P_{d} \cdot \theta_{JA} \tag{1}$$

$$\text{where } P_{d} = P_{CH1} + P_{CH2} + P_{CHx} \text{ and}$$

$$P_{CHx} = V_{S} \cdot I_{CH} - (V_{O}^{2}/R_{L})$$

$$\text{where } V_{O} = 2V_{IN} + 0.280V$$

$$I_{CH} = (I_{CC} / 6) + (V_{O}/R_{L})$$

$$V_{IN} = RMS \text{ value of input signal}$$

$$I_{CC} = 50\text{mA}, V_{S} = 3.3V$$

Board layout affects thermal characteristics. Refer to the Layout Considerations section for more information.

#### **Output Considerations**

R<sub>I</sub> = channel load resistance

The FMS6346E outputs are DC offset from the input by 150mV; therefore  $V_{\text{OUT}}=2 \, ^{\bullet} V_{\text{IN}}$  DC+150mV. This offset is required to obtain optimal performance from the output driver and is held at the minimum value to decrease the standing DC current into the load. Since the FMS6346E has a 2 x (6dB) gain, the output is typically connected via a  $75\Omega$  series back-matching resistor followed by the  $75\Omega$  video cable. Due to the inherent divide by two of this configuration, the blanking level at the load of the video signal is always less then 1V. When AC-coupling the output, ensure that the coupling capacitor passes the lowest frequency content in the video signal and that line time distortion (video tilt) is kept as low as possible.

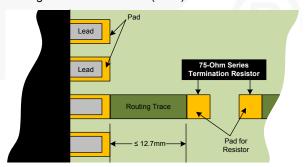

The selection of the coupling capacitor is a function of the subsequent circuit input impedance and the leakage current of the input driven. To obtain the highest quality output video signal, the series termination resistor must be placed as close to the device output pin as possible. This greatly reduces the parasitic capacitance and inductance effect on the output driver. The distance from the device pin to the series termination resistor should be no greater than 12.7mm (0.5in).

Figure 19. Termination Resistor Placement

### **Layout Considerations**

General layout and supply bypassing play major roles in high-frequency performance and thermal characteristics. Fairchild offers a demonstration board, FMS6346EDEMO, to guide layout and aid device testing and characterization.

The FMS6346EDEMO is a four-layer board with a full power and ground plane. Following this layout configuration provides the optimum performance and thermal characteristics. For best results, follow the steps below as a basis for high-frequency layout:

- Include 0.01µF and 0.1µF ceramic bypass capacitors.

- Place the 0.01µF capacitor within 0.75 inches of the power pin.

- Place the 0.1μF capacitor within 0.1 inches of the power pin.

- For multi-layer boards, use a large ground plane to help dissipate heat.

- For two-layer boards, use a ground plane that extends beyond the device by at least 0.5 inches.

- Minimize all trace lengths to reduce series inductances.

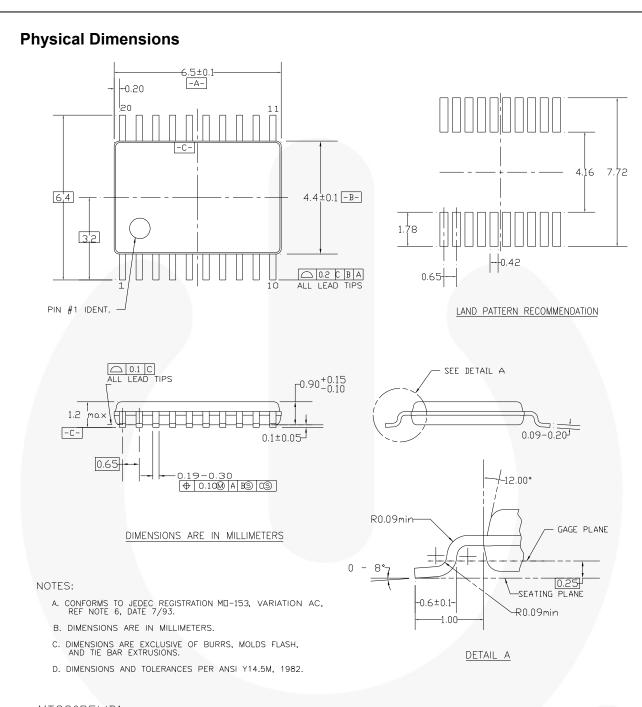

MTC20REVD1

Figure 20. 20-Lead, Thin-Shrink Small-Outline Package (TSSOP)

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: <a href="http://www.fairchildsemi.com/packaging/">http://www.fairchildsemi.com/packaging/</a>.

#### TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

2Cool™

FPS™

AccuPower™

F-PFS™

Auto-SPM™

FRFET®

AX-CAP™\*

Global Power Resource®

BitSiC®

Green FPS™

Build it Now™

Green FPS™ e-Series™

CorePLUS™

Gmax™

CorePOWER™

GTO™

CROSSVOLT™

IntelliMAX™

CTL™

ISOPLANAR™

Aligner Small Speakers

Making Small Speakers

Current Transfer Logic™ Making Small Speakers Sound Louder DEUXPEED® and Better™

Dual Cool™

MegaBuck™

EcoSPARK®

MICROCOUPLER™

EfficientMax™

MicroFET™

ESBC™

MicroPak™

Image: MicroPak2™

Fairchild® MillerDrive™

Fairchild Semiconductor® MotionMax™

FACT Quiet Series™ mWSaver™

FACT® OptoHiT™

FAST® OPTOLOGIC®

FastvCore™ OPTOPLANAR®

PDP SPM™ Power-SPM™ PowerTrench® PowerXS™

Programmable Active Droop™

QFĒT® QS™ Quiet Series™ RapidConfigure™

Saving our world, 1mW/W/kW at a time™

SignafWiseTM

SmartMaxTM

SMART STARTTM

SPM®

STEALTHTM

SuperFET®

SuperSOTTM-3

SuperSOTTM-6

SuperSOTTM-8

SuperSOTTM-8

SuperSOTTM-8

SuperMOS®

SyncETTM

Sync-LockTM

SYSTEM GENERAL®\* TinyBoost™

TinyCalc™

TinyCalc™

TinyLogic®

TINYOPTO™

TinyPower™

TinyPower™

TinyPWIT™

TinyWire™

TranSic®

TriFault Detect™

TRUECURRENT®\*

µSerDes™

UHC®

UHC®

The Power Franchise®

wer

UHC®

Ultra FRFET™

UniFET™

VCX™

VisualMax™

VoltagePlus™

XS™

#### DISCLAIMER

FlashWriter®\*

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN, NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

#### As used herein:

- Life support devices or systems are devices or systems which, (a)

are intended for surgical implant into the body or (b) support or

sustain life, and (c) whose failure to perform when properly used in

accordance with instructions for use provided in the labeling, can be

reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Sales Support.

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

#### Definition of Terms

| Permitted of Terms    |                                                                                                                                                                                                     |  |  |  |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Product Status        | Definition                                                                                                                                                                                          |  |  |  |

| Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |  |  |  |

| First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |  |  |  |

| Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |  |  |  |

| Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor.<br>The datasheet is for reference information only.                                                 |  |  |  |

|                       | Formative / In Design First Production Full Production                                                                                                                                              |  |  |  |

Rev. 157

<sup>\*</sup> Trademarks of System General Corporation, used under license by Fairchild Semiconductor