## 34-Channel Symmetric Row Driver

### **Ordering Information**

|          | Package Options                                            |            |                       |                                                                    |  |  |  |  |  |  |

|----------|------------------------------------------------------------|------------|-----------------------|--------------------------------------------------------------------|--|--|--|--|--|--|

| Device   | 44 J-Lead Quad  Ceramic Chip Carrier  Plastic Chip Carrier |            | Die in<br>waffle pack | 44 J-Lead Quad<br>Ceramic Chip Carrier<br>(MIL-Std-883 Processed*) |  |  |  |  |  |  |

| HV7022-C | HV7022DJ-C                                                 | HV7022PJ-C | HV7022X-C             | RBHV7022DJ-C                                                       |  |  |  |  |  |  |

<sup>\*</sup>For Hi-Rel process flows, refer to page 5-3 of the databook.

### **Features**

- ☐ Processed with HVCMOS® technology

- Symmetric row drive (reduces latent imaging in ACTFEL displays)

- Output voltages up to 230V

- Low-power level shifting

- ☐ Source/Sink current 70mA (min.)

- Shift register speed 4MHz

- Pin-programmable shift direction

- 44-lead plastic & ceramic surface-mount packages

- Hi-Rel processing available

## **Absolute Maximum Ratings**

| Supply voltage, V <sub>DD</sub> <sup>1</sup>          | -0.3V to +15V                  |                  |         |                      |

|-------------------------------------------------------|--------------------------------|------------------|---------|----------------------|

| Supply voltage, V <sub>PP</sub> <sup>1</sup>          |                                |                  | -0.3V   | to +250V             |

| Logic input levels <sup>1</sup>                       | -0.3V to V <sub>DD</sub> +0.3V |                  |         |                      |

| Ground current <sup>2</sup>                           |                                |                  |         | 1.5A                 |

| Continuous total power dissipati                      | ion <sup>3</sup> :             | Plastic<br>Ceram |         | 1200mW<br>1500mW     |

| Operating temperature range                           | Plas<br>Cera                   | stic<br>amic     |         | to +85°C<br>to 125°C |

| Storage temperature range                             |                                |                  | -65°C t | o +150°C             |

| Lead temperature 1.6mm (1/16 from case for 10 seconds | inch)                          |                  |         | 260°C                |

### Notes:

- 1. All voltages are referenced to GND.

- 2. Duty cycle is limited by the total power dissipated in the package.

- For operation above 25°C ambient derate linearly to maximum operating temperature at 25mW/°C for plastic and at 15mW/°C for ceramic.

## **General Description**

The HV7022-C is a low-voltage serial to high-voltage parallel converter with push-pull outputs. It is especially suited for use as a symmetric row driver in AC thin-film electroluminescent (ACTFEL) displays. The HV70 offers 34 output lines, a direction (DIR) pin to give CW or CCW shift register loading, output enable (OE), and polarity (POL) control. After DATA INPUT is entered (on the falling edge of CLOCK), a logic high will cause the output to swing to  $V_{PP}$  if POL is high, or to GND if POL is low.

For Detailed circuit and application information, please refer to Application Note AN-H3.

### 02/96/022

Supertex Inc. does not recommend the use of its products in life support applications and will not knowingly sell its products for use in such applications unless it receives an adequate "products liability indemnification insurance agreement." Supertex does not assume responsibility for use of devices described and limits its liability to the replacement of devices determined to be defective due to workmanship. No responsibility is assumed for possible omissions or inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications, refer to the Supertex website: http://www.supertex.com. For complete liability information on all Supertex products, refer to the most current databook or to the Legal/Disclaimer page on the Supertex website.

### **Electrical Characteristics**

(over recommended operating conditions of  $V_{DD} = 12V$ ,  $T_A = 25$ °C and  $V_{PP} = 230V$  unless otherwise noted)

### **DC Characteristics**

| Symbol           | Parameter                           | Min               | Max | Units | Conditions                                   |                                             |

|------------------|-------------------------------------|-------------------|-----|-------|----------------------------------------------|---------------------------------------------|

| I <sub>DD</sub>  | V <sub>DD</sub> supply current      |                   | 10  | mA    | f <sub>CLK</sub> = 4MHz                      |                                             |

| I <sub>PP</sub>  | High voltage supply cui             | rrent             |     | 4     | mA                                           | 1 Output high <sup>1</sup>                  |

|                  |                                     |                   |     | 100   | μΑ                                           | All Outputs low or High-Z                   |

|                  |                                     |                   |     | 750   | μА                                           | All Outputs low or High-Z (125°C)           |

| I <sub>DDQ</sub> | Quiescent V <sub>DD</sub> supply of |                   | 100 | μΑ    | All V <sub>IN</sub> = GND or V <sub>DD</sub> |                                             |

| V <sub>OH</sub>  | High-level output                   | HV <sub>OUT</sub> | 195 |       | V                                            | I <sub>O</sub> = -70mA (-50mA) <sup>2</sup> |

|                  |                                     | Data out          | 11  |       | V                                            | I <sub>O</sub> = -500μA                     |

| V <sub>OL</sub>  | Low-level output                    | HV <sub>OUT</sub> |     | 30    | V                                            | I <sub>O</sub> = 70mA (+50mA) <sup>2</sup>  |

|                  |                                     | Data out          |     | 1     | V                                            | I <sub>O</sub> = 500μA                      |

| I <sub>IH</sub>  | High-level logic input cu           |                   | 1   | μΑ    | V <sub>IH</sub> = 12V                        |                                             |

| I <sub>IL</sub>  | Low-level logic input cu            | irrent            |     | -1    | μΑ                                           | V <sub>IL</sub> = 0V                        |

### Notes:

# **AC** Characteristics $(V_{DD} = 12V, T_C = 25^{\circ}C)$

| Symbol            | Parameter                                                        | Min | Max  | Units | Conditions                                                                                             |

|-------------------|------------------------------------------------------------------|-----|------|-------|--------------------------------------------------------------------------------------------------------|

| f <sub>CLK</sub>  | Clock frequency                                                  |     | 4    | MHz   |                                                                                                        |

| t <sub>W</sub>    | Pulse duration clock high or low                                 | 125 |      | ns    |                                                                                                        |

| t <sub>SUD</sub>  | Data set-up time before falling clock                            | 100 |      | ns    |                                                                                                        |

| t <sub>HD</sub>   | Data hold time after falling clock                               | 100 |      | ns    |                                                                                                        |

| t <sub>SUC</sub>  | Setup time clock low before V <sub>PP</sub> ↑ or GND↓            | 300 |      | ns    |                                                                                                        |

| t <sub>SUE</sub>  | Setup time enable high before V <sub>PP</sub> ↑ or GND↓          | 300 |      | ns    |                                                                                                        |

| t <sub>SUP</sub>  | Setup time polarity high or low before V <sub>PP</sub> ↑ or GND↓ | 300 |      | ns    |                                                                                                        |

| t <sub>HC</sub>   | Hold time clock high after V <sub>PP</sub> ↑ or GND↓             | 500 |      | ns    |                                                                                                        |

| t <sub>HE</sub>   | Hold time enable high after V <sub>PP</sub> ↑ or GND↓            | 300 |      | ns    |                                                                                                        |

| t <sub>HP</sub>   | Hold time polarity high or low after V <sub>PP</sub> ↑ or GND↓   | 300 |      | ns    |                                                                                                        |

| t <sub>DHL</sub>  | Delay time high to low level output from clock                   |     | 150  | ns    | C <sub>L</sub> = 10pF                                                                                  |

| t <sub>DLH</sub>  | Delay time low to high level output from clock                   |     | 200  | ns    | C <sub>L</sub> = 10pF                                                                                  |

| t <sub>THL</sub>  | Transition time high to low level serial output                  |     | 200  | ns    | C <sub>L</sub> = 15pF                                                                                  |

| t <sub>TLH</sub>  | Transition time low to high level serial output                  |     | 100  | ns    | C <sub>L</sub> = 15pF                                                                                  |

| t <sub>ONH</sub>  | High level turn-on time Q outputs from enable                    |     | 500  | ns    | $I_{O} = -50 \text{ mA}, V_{OH} = 195 \text{V}$<br>$R_{L} = 2 \text{ k}\Omega \text{ to } 95 \text{V}$ |

| t <sub>ONL</sub>  | Low level turn-on time Q outputs from enable                     |     | 500  | ns    | $I_O = 50 \text{ mA}, V_{OH} = 130 \text{V}$<br>$R_L = 2 \text{ k}\Omega \text{ to } 30 \text{V}$      |

| t <sub>OFFH</sub> | High level turn-off time Q outputs from enable                   |     | 1000 | ns    | $I_O = -50 \text{ mA}, V_{OH} = 195 \text{V}$ $R_L = 2 \text{ k}\Omega \text{ to } 95 \text{V}$        |

| t <sub>OFFL</sub> | Low level turn-off time Q outputs from enable                    |     | 500  | ns    | $I_O = 50 \text{ mA}, V_{OH} = 130 \text{V}$<br>$R_L = 2 \text{ k}\Omega \text{ to } 30 \text{V}$      |

|                   | Slew rate, V <sub>PP</sub> or GND                                |     | 45   | V/μs  | With one active output driving a 4.7 nF load to $V_{PP}$ or GND                                        |

<sup>1.</sup> The total number of ON outputs times the duty cycle must not exceed the allowable package power disspation.

<sup>2.</sup> Over military temperature range (-55°C to 125°C).

# **Recommended Operating Conditions**

| Symbol           | Paramete                            | Min                                           | Max  | Units |     |

|------------------|-------------------------------------|-----------------------------------------------|------|-------|-----|

| V <sub>DD</sub>  | Logic supply voltage                |                                               | 10.8 | 13.2  | V   |

| V <sub>PP</sub>  | High voltage supply                 |                                               |      | 230   | V   |

| V <sub>IH</sub>  | High-level input voltage            | V <sub>DD</sub> = 10.8V                       | 8.1  |       | V   |

|                  |                                     | V <sub>DD</sub> = 13.2V                       | 9.9  |       |     |

| V <sub>IL</sub>  | Low-level input voltage             | V <sub>DD</sub> = 10.8V                       |      | 2.7   | V   |

|                  |                                     | V <sub>DD</sub> = 13.2V                       |      | 3.3   |     |

| f <sub>CLK</sub> | Clock frequency                     |                                               |      | 4     | MHz |

| T <sub>A</sub>   | Operating free-air temperature      | Plastic                                       | -40  | +85   | °C  |

|                  |                                     | Ceramic                                       | -55  | +125  | °C  |

| I <sub>OD</sub>  | Allowable pulse current through out | Allowable pulse current through output diodes |      |       |     |

#### Note:

Power-up sequence should be the following:

- 1. Connect ground.

- 2. Apply  $V_{DD}$ .

- 3. Set all inputs (Data, CLK, Enable, etc.) to a known state.

- 4. Apply V<sub>PP</sub>.

- 5. The V<sub>PP</sub> should not drop below V<sub>DD</sub> or float during operation.

Power-down sequence should be the reverse of the above.

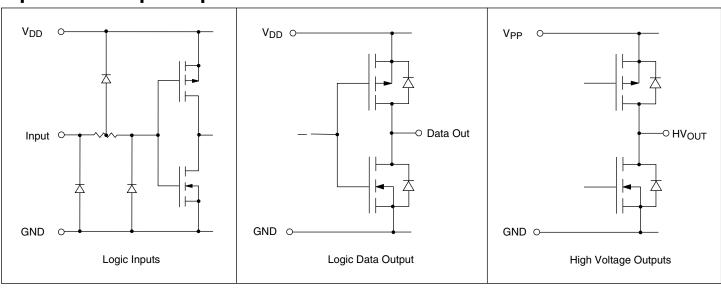

# **Input and Output Equivalent Circuits**

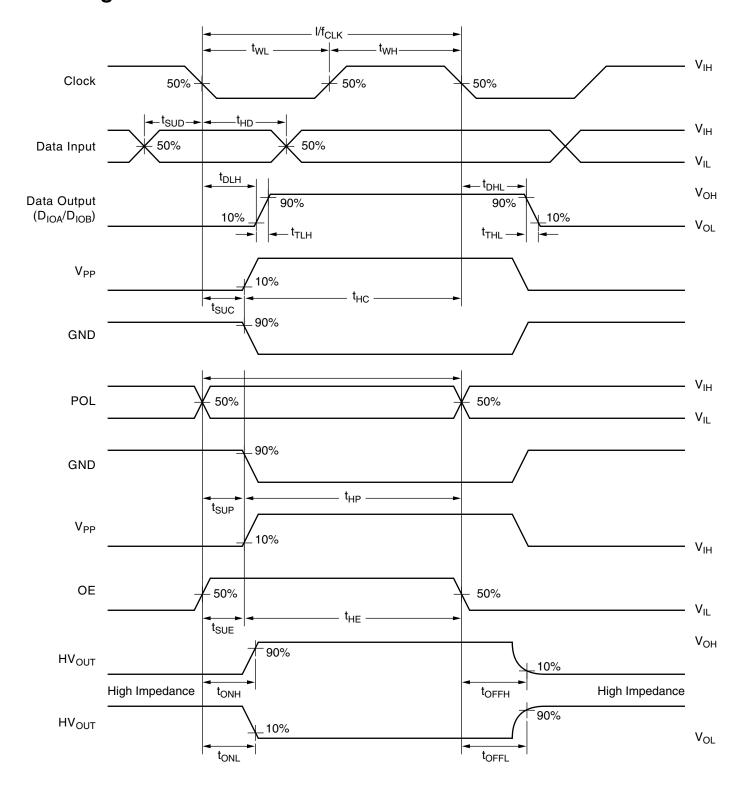

# **Switching Waveforms**

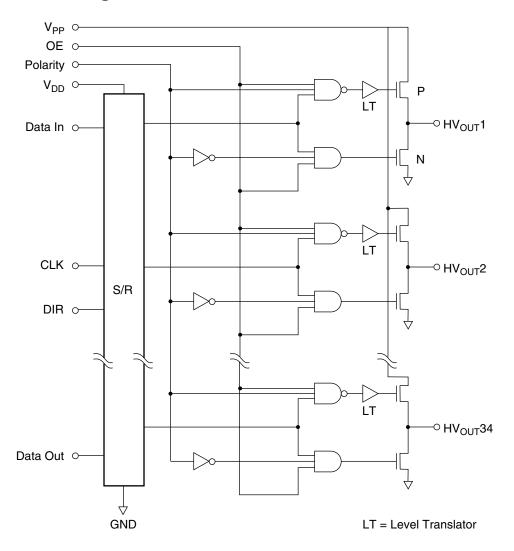

# **Functional Block Diagram**

# **Function Table**

|                  |          |     | Inputs |     | Outputs |                           |                |                 |  |

|------------------|----------|-----|--------|-----|---------|---------------------------|----------------|-----------------|--|

| I/O<br>Relations | CLK      | DIR | Data   | POL | OE      | Shift Reg                 | HV Outputs     | Data Out        |  |

| O/P HIGH         | Х        | Х   | Н      | Н   | Н       | *                         | Н              |                 |  |

| O/P OFF          | Х        | Х   | L      | Н   | Н       | *                         | HIGH-Z         | *               |  |

| O/P LOW          | X        | X   | Н      | L   | Н       | *                         | L              | *               |  |

| O/P OFF          | Х        | Х   | L      | L   | Н       | *                         | HIGH-Z         | *               |  |

| O/P OFF          | Х        | X   | Х      | Х   | L       | *                         | All O/P HIGH-Z | *               |  |

| Load S/R,        | <b>↓</b> | L   | Х      | Х   | Х       | $Q_n \rightarrow Q_{n+1}$ | *              | Q <sub>34</sub> |  |

| set DIR          | <b>↓</b> | Н   | Х      | Х   | Х       | $Q_n \rightarrow Q_{n-1}$ | *              | $Q_{_1}$        |  |

|                  | No ↓     | Х   | Х      | Х   | Х       | *                         | No Change      | No Change       |  |

### Notes:

$H = logic \ high \ level, \ L = logic \ low \ level, \ X = irrelevant, \ \downarrow = high-to-low \ transition,$

$Q_1 = HV_{OUT} 1$ ,  $Q_n = HV_{OUT}(n)$ , etc.

<sup>\* =</sup> dependent on previous state and whether an O/P or S/R command occured.

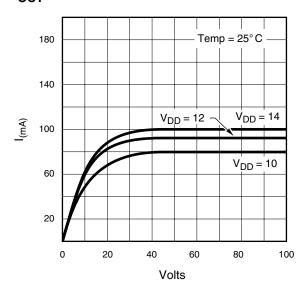

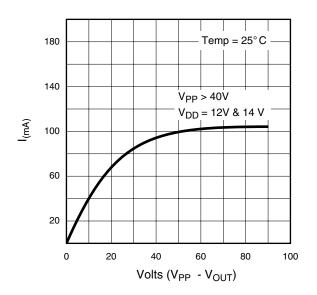

# **HV<sub>OUT</sub> Characteristics**

Output N-Channel Characteristics through FET

Output P-Channel Characteristics through FET

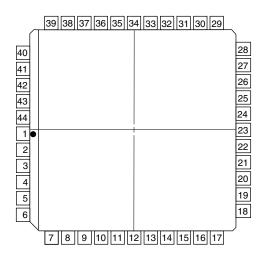

# **Pin Configurations**

### HV70 44 Pin J-Lead Package

| Pin | Function                | Pin | Function                |

|-----|-------------------------|-----|-------------------------|

| 1   | HV <sub>OUT</sub> 18/17 | 23  | DIR                     |

| 2   | HV <sub>OUT</sub> 17/18 | 24  | $V_{_{ m DD}}$          |

| 3   | HV <sub>OUT</sub> 16/19 | 25  | Polarity                |

| 4   | HV <sub>OUT</sub> 15/20 | 26  | Data In                 |

| 5   | HV <sub>OUT</sub> 14/21 | 27  | $V_{pp}$                |

| 6   | HV <sub>OUT</sub> 13/22 | 28  | N/C                     |

| 7   | HV <sub>OUT</sub> 12/23 | 29  | HV <sub>OUT</sub> 34/1  |

| 8   | HV <sub>OUT</sub> 11/24 | 30  | HV <sub>OUT</sub> 33/2  |

| 9   | HV <sub>OUT</sub> 10/25 | 31  | HV <sub>OUT</sub> 32/3  |

| 10  | HV <sub>OUT</sub> 9/26  | 32  | HV <sub>OUT</sub> 31/4  |

| 11  | HV <sub>out</sub> 8/27  | 33  | HV <sub>оит</sub> 30/5  |

| 12  | HV <sub>OUT</sub> 7/28  | 34  | HV <sub>OUT</sub> 29/6  |

| 13  | HV <sub>OUT</sub> 6/29  | 35  | HV <sub>OUT</sub> 28/7  |

| 14  | HV <sub>OUT</sub> 5/30  | 36  | HV <sub>OUT</sub> 27/8  |

| 15  | HV <sub>OUT</sub> 4/31  | 37  | HV <sub>OUT</sub> 26/9  |

| 16  | HV <sub>OUT</sub> 3/32  | 38  | HV <sub>OUT</sub> 25/10 |

| 17  | HV <sub>OUT</sub> 2/33  | 39  | HV <sub>OUT</sub> 24/11 |

| 18  | HV <sub>OUT</sub> 1/34  | 40  | HV <sub>OUT</sub> 23/12 |

| 19  | Data Out                | 41  | HV <sub>OUT</sub> 22/13 |

| 20  | Output Enable           | 42  | HV <sub>OUT</sub> 21/14 |

| 21  | Clock                   | 43  | HV <sub>OUT</sub> 20/15 |

| 22  | GND                     | 44  | HV <sub>OUT</sub> 19/16 |

### Note:

Pin designation for DIR L/H  $Example: For DIR = L, pin 1 is HV_{OUT} 18$   $For DIR = H, pin 1 is HV_{OUT} 17$

# **Package Outline**

top view

44-pin J-Lead Package

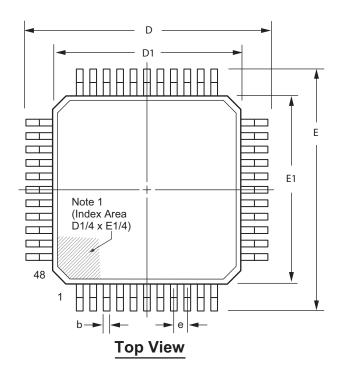

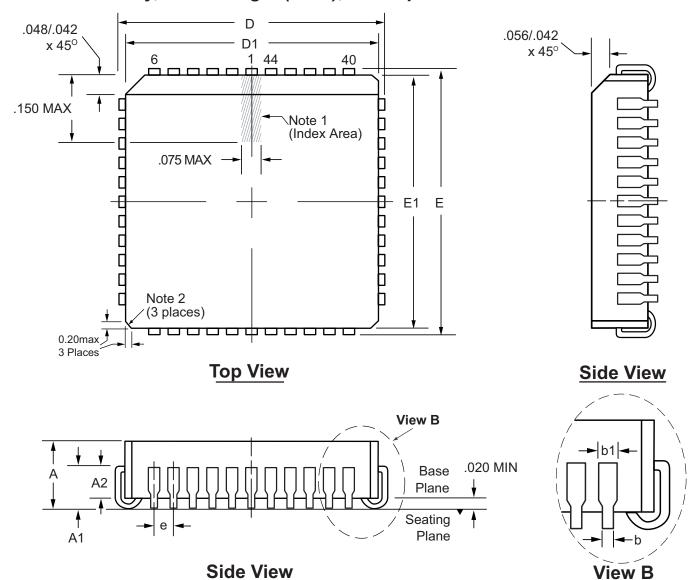

# 44-Lead PQFP Package Outline (PG)

Side View

**Note 1:**A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier may be either a mold, or an embedded metal or marked feature.

| Symbo          | ol  | Α    | A1   | A2   | b    | D     | D1    | E     | E1    | е           | L    | L1          | L2          | θ    | θ1  |

|----------------|-----|------|------|------|------|-------|-------|-------|-------|-------------|------|-------------|-------------|------|-----|

| Dimension (mm) | MIN | -    | 0.25 | 1.95 | 0.30 | 13.65 | 9.80  | 13.65 | 9.80  | 0.73        |      |             | 0.25<br>BSC | 3.5° | 5°  |

|                | NOM | -    | -    | 2.00 | -    | 13.90 | 10.00 | 13.90 | 10.00 | 0.80<br>BSC | 0.88 | 1.95<br>REF |             | -    | -   |

|                | MAX | 2.45 | -    | 2.10 | 0.45 | 14.15 | 10.20 | 14.15 | 10.20 | 200         | 1.03 | 1,721       | 200         | 7°   | 16° |

JEDEC Registration M0-112, Variation AA-2, Issue B, Sep.1995.

**Supertex inc.** does not recommend the use of its products in life support applications, and will not knowingly sell its products for use in such applications, unless it receives an adequate "product liability indemnification insurance agreement". **Supertex** does not assume responsibility for use of devices described and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions or inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications, refer to the **Supertex** website: http://www.supertex.com.

©2007 **Supertex inc.** All rights reserved. Unauthorized use or reproduction is prohibited.

Doc. #: DSPD-44PQFPPG

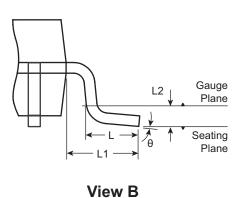

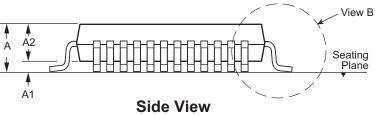

## 44-Lead PLCC Package Outline (PJ)

.653x.653in body, .180in height (max.), .050in pitch

### Note:

1. A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier may be either a mold, or an embedded metal or marked feature. 2. Exact shape of this feature is optional.

| Sym                | bol | Α    | A1   | A2   | b    | b1   | D    | D1   | E    | E1   | е           |

|--------------------|-----|------|------|------|------|------|------|------|------|------|-------------|

| Dimension (inches) | MIN | .165 | .090 | .062 | .013 | .026 | .685 | .650 | .685 | .650 | 0.50        |

|                    | NOM | .172 | .105 | -    | -    | -    | .690 | .653 | .690 | .653 | .050<br>BSC |

| (mones)            | MAX | .180 | .120 | .083 | .021 | .036 | .695 | .656 | .695 | .656 | ВОО         |

JEDEC Registration MS-018, Variation AC, Issue A, June, 1993. Drawings are not to scale.

**Supertex inc.** does not recommend the use of its products in life support applications, and will not knowingly sell its products for use in such applications, unless it receives an adequate "product liability indemnification insurance agreement". Supertex does not assume responsibility for use of devices described and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions or inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications, refer to the **Supertex** website: http://www.supertex.com.

©2007 **Supertex inc.** All rights reserved. Unauthorized use or reproduction is prohibited.

View B

Doc. #: DSPD-44PLCCPJ