# DLP® 0.55 XGA Series 450 DMD

Check for Samples: DLP5500

#### **FEATURES**

- 0.55-Inch Micromirror Array Diagonal

- 1024 × 768 Array of Aluminum, Micrometer-Sized Mirrors (XGA Resolution)

- 10.8-µm Micromirror Pitch

- ±12° Micromirror Tilt Angle (Relative to Flat State)

- Designed for Corner Illumination

- Designed for Use With Broadband Visible Light (420 nm–700 nm):

- Window Transmission 97% (Single Pass, Through Two Window Surfaces)

- Micromirror Reflectivity 88%

- Array Diffraction Efficiency 86%

- Array Fill Factor 92%

- 16-Bit, Low Voltage Differential Signaling (LVDS) Double Data Rate (DDR) input data bus

- 200 MHz Input Data Clock Rate

- Series 450 Package Characteristics:

- Thermal Area 18.0 mm by 12.0 mm enabling high on screen lumens (>2000 lm)

149 Micro Pin Grid Array

Robust electrical connection

#### **APPLICATIONS**

- · 3D Machine Vision

- 3D Optical Measurement

- Industrial and Medical Imaging

- Medical Instrumentation

- · Digital Exposure systems

### **DESCRIPTION**

The DLP5500 Digital Micromirror Device (DMD) is a digitally controlled MOEMS (micro-opto-electromechanical system) spatial light modulator (SLM). When coupled to an appropriate optical system, the DLP5500 can be used to modulate the amplitude, direction, and/or phase of incoming (illumination) light.

Architecturally, the DLP5500 is a latchable, electrical-in/optical-out semiconductor device. This architecture makes the DLP5500 well suited for use in applications such as structured lighting, 3D optical metrology, Industrial & Medical imaging, microscopy, and spectroscopy. The compact physical size of the DLP5500 enables integration into portable equipment.

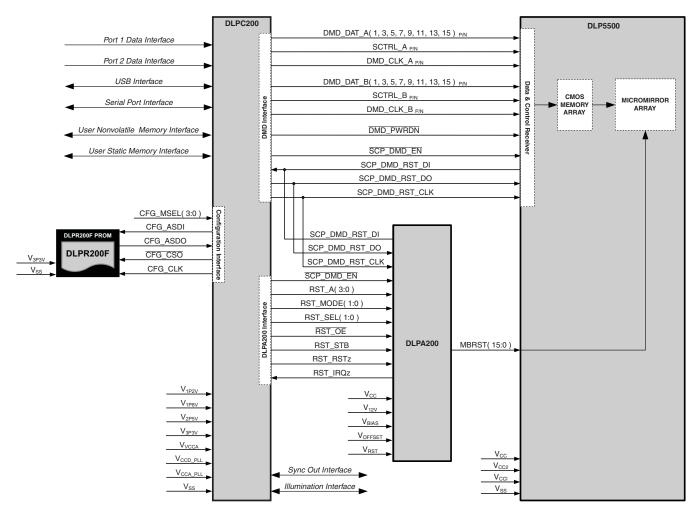

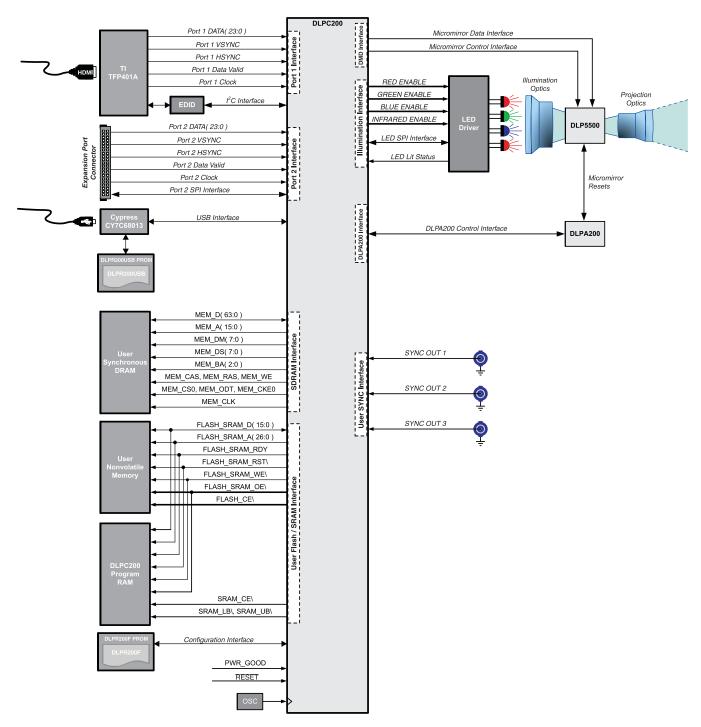

The DLP5500 is one of three components in the DLP 0.55 XGA chip-set (see Figure 1). Proper function and operation of the DLP5500 requires that it be used in conjunction with the other components of the chip-set. The DLPC200 (TI literature number DLPS014) and DLPA200 (TI literature number DLPS015) control and coordinate the data loading and micromirror switching to guarantee reliable operation. Refer to DLP 0.55 XGA chip-set data sheet (TI literature number DLPZ004) for further details. DLPR200F is DLPC200 firmware code provided to enable Video and Structured Lighting Applicaions. To locate the latest version of the DLPR200F, go to www.ti.com and search keyword "DLPR200".

Electrically, the DLP5500 consists of a two-dimensional array of 1-bit CMOS memory cells, organized in a square grid of 1024 memory cell columns by 768 memory cell rows. The CMOS memory array is written to on a column-by-column basis, over a 16-bit Low Voltage Differential Signaling (LVDS) double data rate (DDR) bus. Row addressing is handled via a serial control bus. The specific CMOS memory access protocol is handled by the DLPC200 Digital Controller.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

DLP is a registered trademark of Texas Instruments.

Figure 1. Block Diagram of 0.55 XGA Chipset

Figure 2. Typical Application

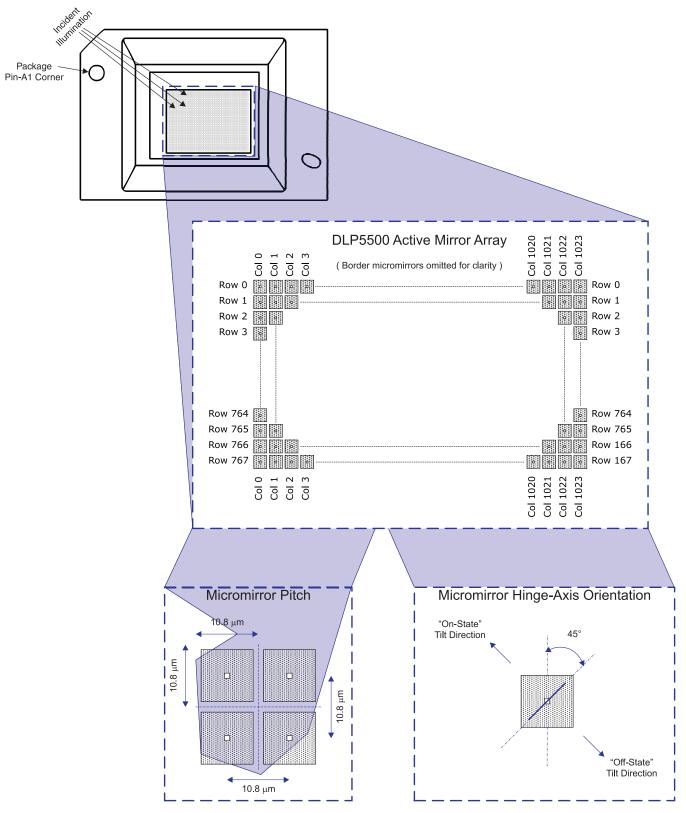

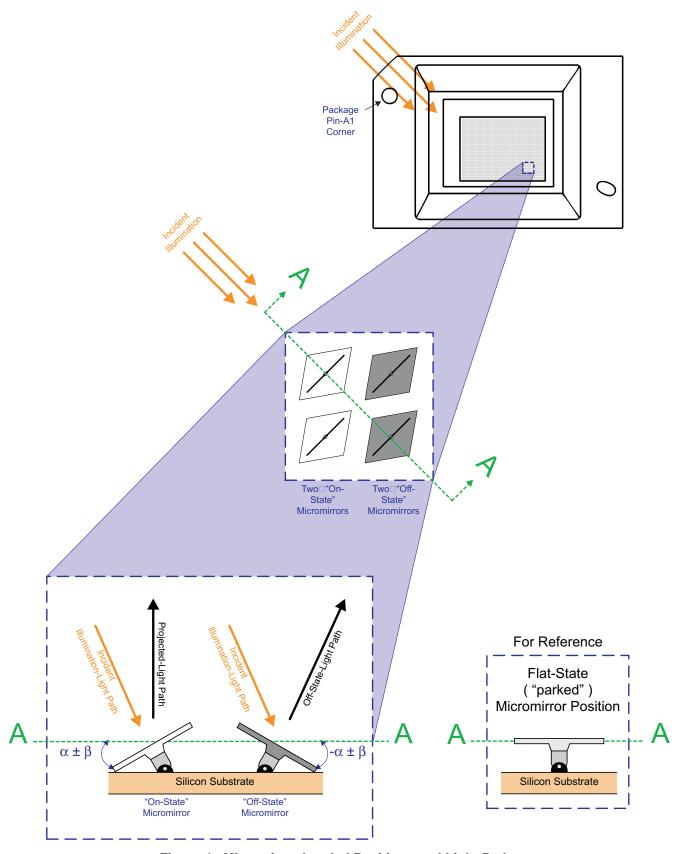

Optically, the DLP5500 consists of 786,432 highly reflective, digitally switchable, micrometer-sized mirrors ("micromirrors"), organized in a two-dimensional array of 1024 micromirror columns by 768 micromirror rows (Figure 3). Each aluminum micromirror is approximately 10.8 microns in size (refer to "Micromirror Pitch" in Figure 3), and is switchable between two discrete angular positions: –12° and +12°. The angular positions are measured relative to a 0° "flat state", which is parallel to the array plane (see Figure 4). The tilt direction is perpendicular to the hinge-axis which is positioned diagonally relative to the overall array, with the "On State" landed position directed towards "Row 0, Column 0" corner of the device package (refer to "Micromirror Hinge-Axis Orientation" in Figure 3). In the field of visual displays, the 1024 by 768 "pixel" resolution is referred to as "XGA".

Each individual micromirror is positioned over a corresponding CMOS memory cell. The angular position of a specific micromirror is determined by the binary state (logic 0 or 1) of the corresponding CMOS memory cell contents. Writing a logic 1 into a memory cell will result in the corresponding micromirror switching to a +12° position. Writing a logic 0 into a memory cell will result in the corresponding micromirror switching to a -12° position.

Around the perimeter of the 1024 by 768 array of micromirrors is a uniform band of "border" micromirrors. The border micromirrors are not user-addressable. The border micromirrors land in the –12° position once power has been applied to the device. There are 10 border micromirrors on each side of the 1024 by 768 active array.

The angular position (-12° or +12°) of the individual micromirrors changes synchronously with a micromirror "clocking pulse" (rather than being synchronous with the CMOS memory cell data update). The micromirror "clocking pulse" is referred to as a Mirror Reset. Application of the Mirror Reset signal results in each micromirror being electro-mechanically "latched" into the angular position dictated by the contents of the corresponding CMOS memory cell. The micromirror "clocking pulse" is input to the DLP5500 via the 16 "RESET" signals provided from the DLPA200 DMD Analog Reset Driver.

Operationally, updating the angular position of the micromirror array consists of first updating the contents of the CMOS memory, followed by application of a Mirror Reset to all or a portion of the micromirror array (depending upon the configuration of the system). Mirror Reset pulses are generated by the DLPA200, with application of the pulses being coordinated by the DLPC200 controller.

Figure 3. DMD Micromirror Array, Pitch, and Hinge-Axis Orientation

Figure 4. Micromirror Landed Positions and Light Paths

### **Related Documents**

The following documents contain additional information related to the use of the DLP5500 device:

#### **Related Documents**

| DOCUMENT                               | TI LITERATURE NUMBER |

|----------------------------------------|----------------------|

| DLP 0.55 XGA Chip-Set data sheet       | DLPZ004              |

| DLPC200 Digital Controller data sheet  | DLPS014              |

| DLPA200 DMD Analog Reset Driver        | DLPS015              |

| s4xx DMD Mechanical & Thermal App note | DLPA015              |

| DLPC200 API Reference Manual           | DLPA024              |

| DLPC200 API Programmer's Guide         | DLPA014              |

| s4xx DMD Cleaning Application Note     | DLPA025              |

| s4xx DMD Handling Application Note     | DLPA019              |

### **Orderable Part Number**

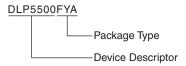

# **Device Marking**

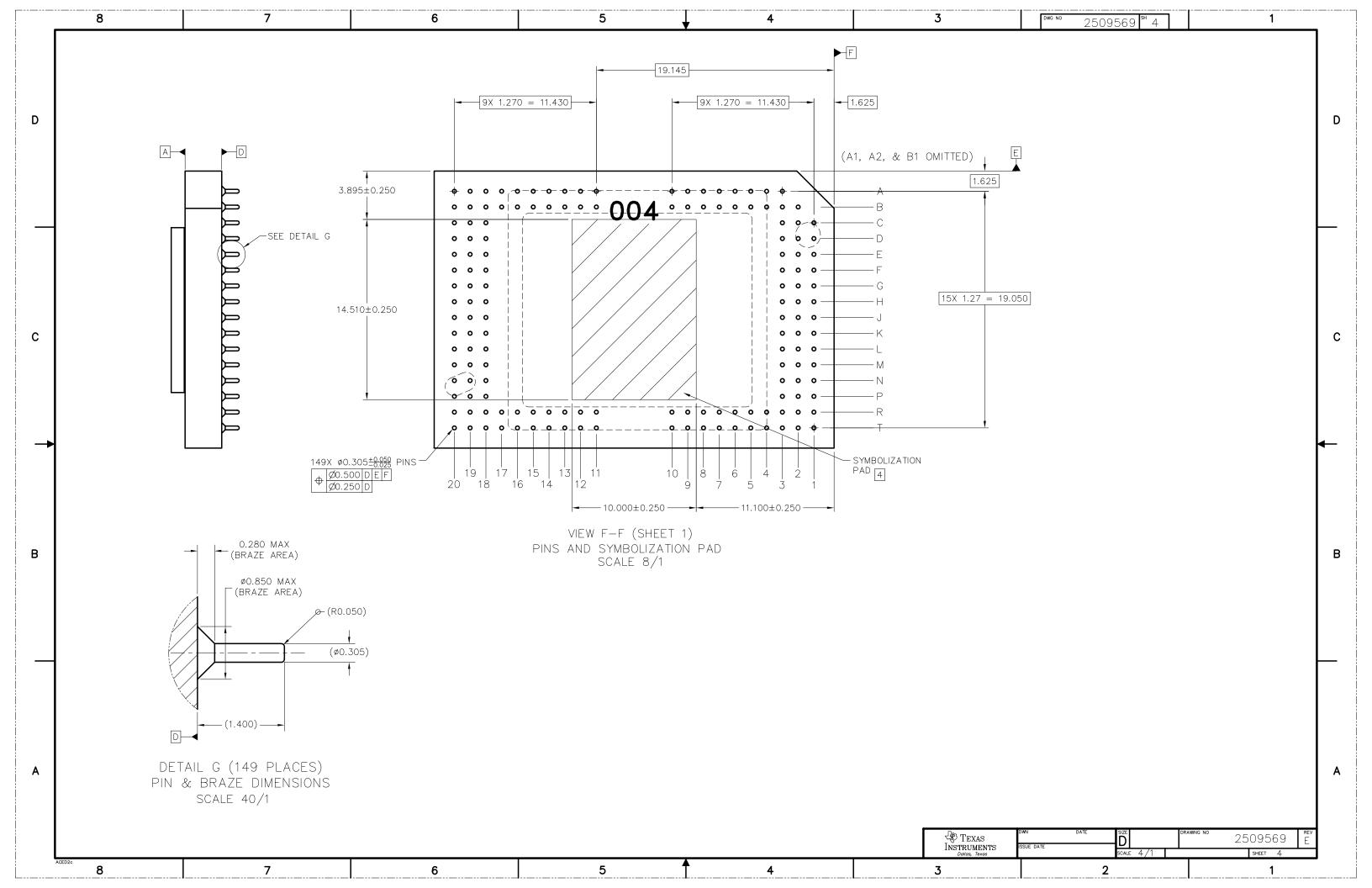

The device marking consists of the fields shown in Figure 5.

Figure 5. DMD Marking (Device Top View)

Copyright © 2010–2011, Texas Instruments Incorporated

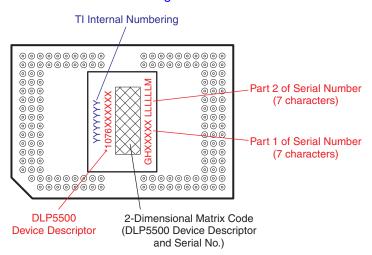

#### **Terminal Characteristics**

|                   | Terminal Characteristics |        |        |                         |               |                                                      |              |                  |

|-------------------|--------------------------|--------|--------|-------------------------|---------------|------------------------------------------------------|--------------|------------------|

| TERMINAL<br>NAME  | PIN<br>See Figure 6      | I/O/P  | TYPE   | INTERNAL<br>TERMINATION | CLOCKED<br>BY | Internal<br>Trace<br>Length<br>(mils) <sup>(1)</sup> | DATA<br>RATE | DESCRIPTION      |

| Data Inputs       |                          |        |        |                         |               |                                                      |              |                  |

| D_AN1             | G20                      | Input  | LVCMOS | Differential Terminated | DCLK_A        | 715                                                  | LVDS         |                  |

| D_AP1             | H20                      | Input  | LVCMOS | Differential Terminated | DCLK_A        | 744                                                  | LVDS         |                  |

| D_AN3             | H19                      | Input  | LVCMOS | Differential Terminated | DCLK_A        | 688                                                  | LVDS         |                  |

| D_AP3             | G19                      | Input  | LVCMOS | Differential Terminated | DCLK_A        | 703                                                  | LVDS         |                  |

| D_AN5             | F18                      | Input  | LVCMOS | Differential Terminated | DCLK_A        | 686                                                  | LVDS         |                  |

| D_AP5             | G18                      | Input  | LVCMOS | Differential Terminated | DCLK_A        | 714                                                  | LVDS         |                  |

| D_AN7             | E18                      | Input  | LVCMOS | Differential Terminated | DCLK_A        | 689                                                  | LVDS         |                  |

| D_AP7             | D18                      | Input  | LVCMOS | Differential Terminated | DCLK_A        | 705                                                  | LVDS         | Input data bus A |

| D_AN9             | C20                      | Input  | LVCMOS | Differential Terminated | DCLK_A        | 687                                                  | LVDS         | input data bus A |

| D_AP9             | D20                      | Input  | LVCMOS | Differential Terminated | DCLK_A        | 715                                                  | LVDS         |                  |

| D_AN11            | B18                      | Input  | LVCMOS | Differential Terminated | DCLK_A        | 715                                                  | LVDS         |                  |

| D_AP11            | A18                      | Input  | LVCMOS | Differential Terminated | DCLK_A        | 732                                                  | LVDS         |                  |

| D_AN13            | A20                      | Input  | LVCMOS | Differential Terminated | DCLK_A        | 686                                                  | LVDS         |                  |

| D_AP13            | B20                      | Input  | LVCMOS | Differential Terminated | DCLK_A        | 715                                                  | LVDS         |                  |

| D_AN15            | B19                      | Input  | LVCMOS | Differential Terminated | DCLK_A        | 700                                                  | LVDS         |                  |

| D_AP15            | A19                      | Input  | LVCMOS | Differential Terminated | DCLK_A        | 719                                                  | LVDS         |                  |

| D_BN1             | K20                      | Input  | LVCMOS | Differential Terminated | DCLK_B        | 716                                                  | LVDS         |                  |

| D_BP1             | J20                      | Input  | LVCMOS | Differential Terminated | DCLK_B        | 745                                                  | LVDS         |                  |

| D_BN3             | J19                      | Input  | LVCMOS | Differential Terminated | DCLK_B        | 686                                                  | LVDS         |                  |

| D_BP3             | K19                      | Input  | LVCMOS | Differential Terminated | DCLK_B        | 703                                                  | LVDS         |                  |

| D_BN5             | L18                      | Input  | LVCMOS | Differential Terminated | DCLK_B        | 686                                                  | LVDS         |                  |

| D_BP5             | K18                      | Input  | LVCMOS | Differential Terminated | DCLK_B        | 714                                                  | LVDS         |                  |

| D_BN7             | M18                      | Input  | LVCMOS | Differential Terminated | DCLK_B        | 693                                                  | LVDS         |                  |

| D_BP7             | N18                      | Input  | LVCMOS | Differential Terminated | DCLK_B        | 709                                                  | LVDS         |                  |

| D_BN9             | P20                      | Input  | LVCMOS | Differential Terminated | DCLK_B        | 687                                                  | LVDS         | Input data bus B |

| D_BP9             | N20                      | Input  | LVCMOS | Differential Terminated | DCLK_B        | 715                                                  | LVDS         |                  |

| D_BN11            | R18                      | Input  | LVCMOS | Differential Terminated | DCLK_B        | 702                                                  | LVDS         |                  |

| D_BP11            | T18                      | Input  | LVCMOS | Differential Terminated | DCLK_B        | 719                                                  | LVDS         |                  |

| D_BN13            | T20                      | Input  | LVCMOS | Differential Terminated | DCLK_B        | 686                                                  | LVDS         |                  |

| D_BP13            | R20                      | Input  | LVCMOS | Differential Terminated | DCLK_B        | 715                                                  | LVDS         |                  |

| D_BN15            | R19                      | Input  | LVCMOS | Differential Terminated | DCLK_B        | 680                                                  | LVDS         |                  |

| D_BP15            | T19                      | Input  | LVCMOS | Differential Terminated | DCLK_B        | 700                                                  | LVDS         |                  |

| DCLK_AN           | D19                      | Input  | LVCMOS | Differential Terminated | _             | 700                                                  | _            | Input data bus A |

| DCLK_AP           | E19                      | Input  | LVCMOS | Differential Terminated | -             | 728                                                  | _            | Clock            |

| DCLK_BN           | N19                      | Input  | LVCMOS | Differential Terminated | -             | 700                                                  | -            | Input data bus B |

| DCLK_BP           | M19                      | Input  | LVCMOS | Differential Terminated | _             | 728                                                  | _            | Clock            |

| Data Control Inpu | ıts                      |        |        |                         |               |                                                      |              |                  |

| SCTRL_AN          | F20                      | Input  | LVCMOS | Differential Terminated | DCLK_A        | 716                                                  | LVDS         |                  |

| SCTRL_AP          | E20                      | Input  | LVCMOS | Differential Terminated | DCLK_A        | 731                                                  | LVDS         |                  |

| SCTRL_BN          | L20                      | Input  | LVCMOS | Differential Terminated | DCLK_B        | 707                                                  | LVDS         |                  |

| SCTRL_BP          | M20                      | Input  | LVCMOS | Differential Terminated | DCLK_B        | 722                                                  | LVDS         |                  |

| Serial Communic   | ation & Configurat       | tion   |        |                         |               |                                                      |              |                  |

| SCP_CLK           | A8                       | Input  | LVCMOS | pull-down               | -             | _                                                    | _            |                  |

| SCP_DO            | A9                       | Output | LVCMOS | _                       | SCP_CLK       | _                                                    | _            |                  |

| SCP_DI            | A5                       | Input  | LVCMOS | pull-down               | SCP_CLK       | _                                                    | _            |                  |

| SCP_ENZ           | B7                       | Input  | LVCMOS | pull-down               | SCP_CLK       | _                                                    | _            |                  |

| PWRDNZ            | В9                       | Input  | LVCMOS | pull-down               | -             | -                                                    | _            |                  |

<sup>(1)</sup> Internal Trace Length (mils) refers to the Package electrical trace length. Refer to the DLP 0.55 XGA Chip-Set Data Sheet (TI literature number DLPS012) for details regarding signal integrity considerations for end-equipment designs.

Submit Documentation Feedback

Copyright © 2010–2011, Texas Instruments Incorporated

# **Terminal Characteristics (continued)**

| TERMINAL<br>NAME | PIN<br>See Figure 6                                                                                                                                             | I/O/P | TYPE   | INTERNAL<br>TERMINATION | CLOCKED<br>BY | Internal<br>Trace<br>Length<br>(mils) <sup>(1)</sup> | DATA<br>RATE | DESCRIPTION                             |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|-------------------------|---------------|------------------------------------------------------|--------------|-----------------------------------------|

| MODE_A           | A4                                                                                                                                                              | Input | LVCMOS | pull-down               | _             | _                                                    | _            |                                         |

| Micromirror Bias | Reset                                                                                                                                                           |       |        |                         |               | •                                                    |              |                                         |

| MBRST0           | C3                                                                                                                                                              | Input | Analog | _                       | -             | _                                                    | -            |                                         |

| MBRST1           | D2                                                                                                                                                              | Input | Analog | _                       | _             | _                                                    | -            |                                         |

| MBRST2           | D3                                                                                                                                                              | Input | Analog | _                       | -             | _                                                    | -            |                                         |

| MBRST3           | E2                                                                                                                                                              | Input | Analog | -                       | -             | _                                                    | -            |                                         |

| MBRST4           | G3                                                                                                                                                              | Input | Analog | _                       | -             | _                                                    | -            |                                         |

| MBRST5           | E1                                                                                                                                                              | Input | Analog | _                       | -             | _                                                    | -            | Micromirror Bias                        |

| MBRST6           | G2                                                                                                                                                              | Input | Analog | _                       | -             | _                                                    | -            | Reset "MBRST"                           |

| MBRST7           | G1                                                                                                                                                              | Input | Analog | _                       | -             | _                                                    | -            | signals "clock"<br>micromirrors into    |

| MBRST8           | N3                                                                                                                                                              | Input | Analog | _                       | -             | _                                                    | -            | state of LVCMOS                         |

| MBRST9           | M2                                                                                                                                                              | Input | Analog | _                       | _             | _                                                    | _            | memory cell associated with             |

| MBRST10          | M3                                                                                                                                                              | Input | Analog | _                       | -             | _                                                    | -            | each mirror.                            |

| MBRST11          | L2                                                                                                                                                              | Input | Analog | _                       | -             | _                                                    | _            |                                         |

| MBRST12          | J3                                                                                                                                                              | Input | Analog | _                       | -             | _                                                    | -            |                                         |

| MBRST13          | L1                                                                                                                                                              | Input | Analog | _                       | -             | _                                                    | _            |                                         |

| MBRST14          | J2                                                                                                                                                              | Input | Analog | _                       | -             | _                                                    | _            |                                         |

| MBRST15          | J1                                                                                                                                                              | Input | Analog | _                       | _             | _                                                    | _            |                                         |

| Power            |                                                                                                                                                                 |       |        |                         |               |                                                      |              |                                         |

| V <sub>CC</sub>  | B11,B12,B13,B1<br>6,R12,R13,R16,<br>R17                                                                                                                         | Power | Analog | -                       | -             | -                                                    | -            | Power for LVCMOS<br>Logic               |

| V <sub>CCI</sub> | A12,A14,A16,T1<br>2,T14,T16                                                                                                                                     | Power | Analog | -                       | _             | -                                                    | _            | Power supply for LVDS Interface         |

| V <sub>CC2</sub> | C1,D1,M1,N1                                                                                                                                                     | Power | Analog | -                       | -             | _                                                    | _            | Power for High<br>Voltage CMOS<br>Logic |

| V <sub>SS</sub>  | A6,A11,A13,A15,<br>A17,B4,B5,B8,B1<br>4,B15,B17,C2,C1<br>8,C19,F1,F2,F19,<br>H1,H2,H3,H18,J1<br>8,K1,K2,L19,N2,<br>P18,P19,R4,R9,<br>R14,R15,T7,T13,<br>T15,T17 | Power | Analog | nalog – – Cor           |               | Common return for all power inputs                   |              |                                         |

| Reserved Signals | (Not for use in sy                                                                                                                                              | stem) |        |                         |               |                                                      |              |                                         |

| RESERVED_R7      | R7                                                                                                                                                              | input | LVCMOS | pull-down               | _             | -                                                    | _            | Pins should be                          |

| RESERVED_R8      | R8                                                                                                                                                              | input | LVCMOS | pull-down               | _             | -                                                    | _            | connected to V <sub>SS</sub>            |

| RESERVED_T8      | T8                                                                                                                                                              | input | LVCMOS | pull-down               | 1             | -                                                    | _            |                                         |

| RESERVED_B6      | B6                                                                                                                                                              | input | LVCMOS | pull-down               |               | -                                                    | _            |                                         |

| NO_CONNECT       | A3, A7, A10, B2,<br>B3, B10, E3, F3,<br>K3, L3, P1, P2,<br>P3, R1, R2, R3,<br>R5, R6, R10,<br>R11, T1, T2, T3,<br>T4, T5, T6, T9,<br>T10, T11                   | -     | _      | -                       | _             | -                                                    | -            | DO NOT CONNECT                          |

Copyright © 2010–2011, Texas Instruments Incorporated

Submit Docum

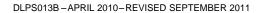

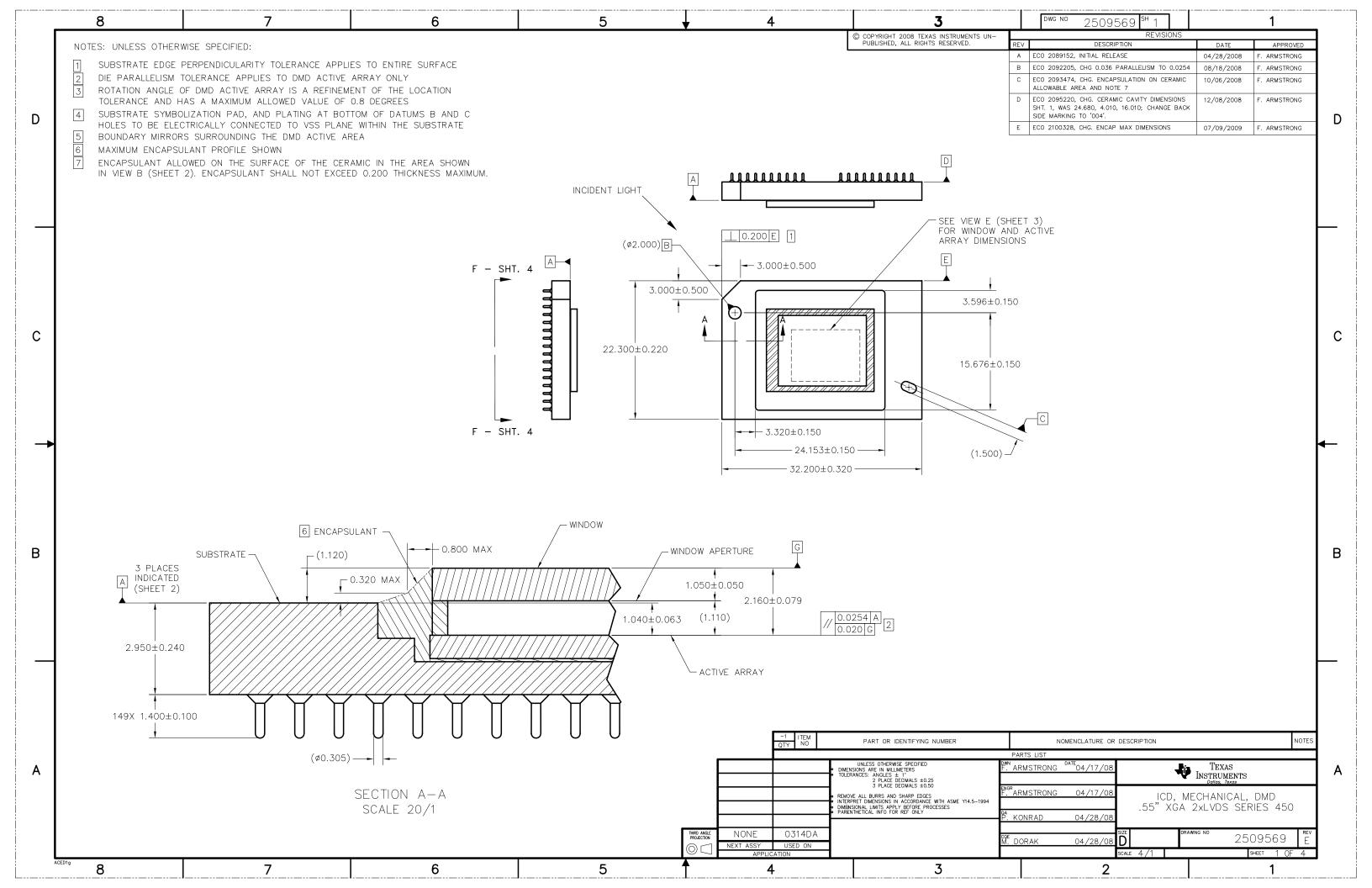

Figure 6. Series 450 Package Pins (Device Bottom View)

#### ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range (unless otherwise noted). Stresses beyond those listed under " Absolute Maximum Ratings" may cause permanent damage to the device. The Absolute Maximum Ratings are stress ratings only, and functional performance of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to Absolute Maximum Rated conditions for extended periods may affect device reliability.

|                    | PARAMETER                                                                                            | CONDITIONS                                                                       | MIN  | Nom MAX               | UNIT               |

|--------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------|-----------------------|--------------------|

| V <sub>CC</sub>    | Voltage applied to V <sub>CC</sub> <sup>(1)(2)</sup>                                                 |                                                                                  | -0.5 | 4                     | V                  |

| V <sub>CCI</sub>   | Voltage applied to V <sub>CCI</sub> <sup>(1)(2)</sup>                                                |                                                                                  | -0.5 | 4                     | V                  |

| V <sub>ID</sub>    | Maximum differential voltage,<br>Damage can occur to internal<br>resistor if exceeded, See Figure 10 |                                                                                  |      | 700                   | mV                 |

|                    | Delta supply voltage  V <sub>CC</sub> - V <sub>CCI</sub>                                             |                                                                                  |      | .3                    | V                  |

| VCC2               | Voltage applied to V <sub>OFFSET</sub> <sup>(1)(2)(3)</sup>                                          |                                                                                  | -0.5 | 9                     | V                  |

| V <sub>MBRST</sub> | Voltage applied to MBRST[0:15]<br>Input Pins                                                         |                                                                                  | -28  | 28                    | V                  |

|                    | Voltage applied to all other input terminals (1)                                                     |                                                                                  | -0.5 | V <sub>CC</sub> + 0.3 | V                  |

|                    | Current required from a high-level output                                                            | V <sub>OH</sub> = 2.4 V                                                          |      | -20                   | mA                 |

|                    | Current required from a low-level output                                                             | V <sub>OL</sub> = 0.4 V                                                          |      | 15                    | mA                 |

|                    | - Carpai                                                                                             | Operating Temperature -<br>Micromirror Array<br>Temperature <sup>(4)(5)(6)</sup> | 10   | 70                    |                    |

|                    | Device Operating and Non-operating Temperature                                                       | Device Case Temperature - TC1, see Figure 13                                     | 10   | 80                    | °C                 |

|                    |                                                                                                      | Device Temperature Gradient <sup>(7)</sup>                                       |      | 10                    |                    |

|                    |                                                                                                      | Non-operating Temperature                                                        | -40  | 80                    |                    |

|                    | Local ambient relative bumidity (8)                                                                  | Operating                                                                        |      | 95                    | %                  |

|                    | Local ambient relative humidity <sup>(8)</sup>                                                       | Non-operating                                                                    |      | 95                    | 70                 |

|                    |                                                                                                      | < 420 nm <sup>(6)</sup>                                                          |      | 20                    |                    |

|                    | Illumination power density (9)                                                                       | 420 to 700 <sup>(10)</sup>                                                       |      |                       | mW/cm <sup>2</sup> |

|                    |                                                                                                      | > 700 nm                                                                         |      | 10                    |                    |

|                    | Electrostatic discharge immunity for LVCMOS pins (11)                                                |                                                                                  |      | 2000                  | W                  |

|                    | Electrostatic discharge immunity for MBRST[0:15] pins                                                |                                                                                  |      | 250                   | V                  |

- (1) All voltages referenced to  $V_{SS}$  (ground).

- Voltages V<sub>CC</sub>, V<sub>CCI</sub>, and V<sub>CC2</sub> are required for proper DMD operation.

- Exceeding the recommended allowable absolute voltage difference between V<sub>CC</sub> and V<sub>CCI</sub> may result in excess current draw. The difference between V<sub>CC</sub> and V<sub>CCI</sub>, | V<sub>CC</sub> - V<sub>CCI</sub>|, should be less than .3V. Refer to Thermal Characteristics for Thermal Test Point Locations, Package Thermal Resistance, and Device Temperature Calculation.

- Micromirror Array can operate from 0 °C to 10 °C at power up for a maximum of 10 minutes without damage

- The maximum operating conditions for operating temperature and illumination power density for wavelengths < 420 nm shall not be implemented simultaneously.

- As measured between the case temperature (TC1) and the predicted temperature of the Micromirror array. Refer to Thermal Characteristics for Thermal Test Point Locations, Package Thermal Resistance, and Device Temperature Calculation.

- Non-condensing

- (9) Total integrated illumination power density, above or below the indicated wavelength threshold.

- (10) Limited only by the resulting micromirror array temperature.

- (11) Tested in accordance with JESD22-A114-B Electrostatic Discharge (ESD) sensitivity testing Human Body Model (HBM).

#### RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted). The functional performance of the device specified in this data sheet is achieved when operating the device within the limits defined by the Recommended Operating Conditions. No level of performance is implied when operating the device above or below the Recommended Operating Conditions limits.

|                      | PARAMETER                                                                       | CONDITIONS                                                          | MIN  | NOM | MAX  | UNIT |

|----------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------|------|-----|------|------|

| V <sub>CC</sub>      | LVCMOS interface supply voltage <sup>(1)(2)</sup>                               |                                                                     | 3.0  | 3.3 | 3.6  | V    |

| V <sub>CCI</sub>     | LVCMOS logic supply voltage (1)(2)                                              |                                                                     | 3.0  | 3.3 | 3.6  | V    |

| V <sub>CC2</sub>     | Mirror electrode and HVCMOS supply voltage (1)(2)                               |                                                                     | 8.25 | 8.5 | 8.75 | V    |

| V <sub>MBRST</sub>   |                                                                                 |                                                                     | -27  |     | 26.5 | V    |

| f <sub>DCLK_*</sub>  | DCLK_A & DCLK_B clock frequency                                                 |                                                                     |      | 150 |      | MHz  |

| f <sub>SCP_CLK</sub> | SCP_CLK Frequency                                                               |                                                                     |      |     | 500  | KHz  |

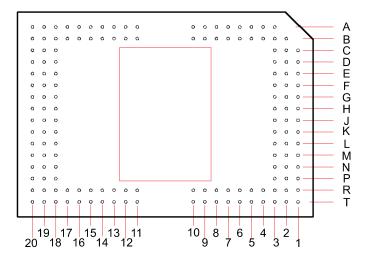

|                      | Static load applied to each electrical interface area #1 & #2, See (3) Figure 7 |                                                                     |      |     | 55   | N    |

|                      | Static load applied to the thermal interface area, See <sup>(4)</sup> Figure 7  |                                                                     |      |     | 111  | N    |

|                      | Device Operating Temperature                                                    | Operating Temperature -<br>Micromirror Array<br>Temperature (5) (6) | 10   |     | 70   | °C   |

- All voltages referenced to V<sub>SS</sub> (ground).

- (2) Voltages V<sub>CC</sub>, V<sub>CCI</sub>, and V<sub>CC2</sub>, are required for proper DMD operation.

- (3) Load should be uniformly distributed across the entire Electrical Interface area #1 and #2.

- (4) Load should be uniformly distributed across Thermal Interface Area. Refer to the for size and location of the datum-A surfaces.

- (5) Refer to Thermal Characteristics for Thermal Test Point Locations, Package Thermal Resistance, and Device Temperature Calculation.

- (6) In some applications, the total DMD heat load can be dominated by the amount of incident light energy absorbed. Refer to the Thermal Characteristics for further details.

Figure 7. System Interface Loads

#### **ELECTRICAL CHARACTERISTICS**

Over the range of recommended supply voltage and recommended case operating temperature (unless otherwise noted)

| PARAMETERS<br>(Under RECOMMENDED OPERATING<br>CONDITIONS) |                                                          | TEST CONDITIO                                                                                             | TEST CONDITIONS             |      | NOM | MAX        | UNIT |

|-----------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------|------|-----|------------|------|

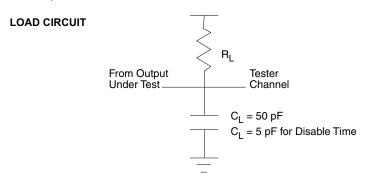

| V <sub>OH</sub>                                           | High-level output voltage <sup>(1)</sup> , See Figure 8  | V <sub>CC</sub> = 3.0 V,                                                                                  | I <sub>OH</sub> = -20<br>mA | 2.4  |     |            | V    |

| V <sub>OL</sub>                                           | Low-level output voltage <sup>(1)</sup> , See Figure 8   | V <sub>CC</sub> = 3.6 V,                                                                                  | I <sub>OH</sub> = 15<br>mA  |      |     | 0.4        | ٧    |

| I <sub>OZ</sub>                                           | High impedance output current <sup>(1)</sup>             | V <sub>CC</sub> = 3.6 V                                                                                   |                             |      |     | 10         | μΑ   |

| I <sub>OH</sub>                                           | High-level output current (1)                            | $V_{OH} = 2.4 \text{ V}, V_{CC} \ge 3.0 \text{ V}$<br>$V_{OH} = 1.7 \text{ V}, V_{CC} \ge 2.25 \text{ V}$ |                             |      |     | -20<br>-15 | mA   |

| I <sub>OL</sub>                                           | Low-level output current (1)                             | $V_{OL} = 0.4 \text{ V}, V_{CC} \ge 3.0 \text{ V}$<br>$V_{OL} = 0.4 \text{ V}, V_{CC} \ge 2.25 \text{ V}$ |                             |      |     | 15<br>14   | mA   |

| V <sub>IH</sub>                                           | High-level input voltage <sup>(1)</sup>                  |                                                                                                           |                             | 1.7  |     | VCC + .3   | V    |

| V <sub>IL</sub>                                           | Low-level input voltage <sup>(1)</sup>                   |                                                                                                           |                             | -0.3 |     | 0.7        | V    |

| I <sub>IL</sub>                                           | Low-level input current <sup>(1)</sup>                   | $V_{CC} = 3.6 \text{ V},$                                                                                 | $V_I = 0 V$                 |      |     | -60        | μΑ   |

| I <sub>IH</sub>                                           | High-level input current <sup>(1)</sup>                  | $V_{CC} = 3.6 \text{ V},$                                                                                 | $V_I = V_{CC}$              |      |     | 200        | μΑ   |

| Icc                                                       | Current into V <sub>CC</sub> terminal                    | $V_{CC} = 3.6 V,$                                                                                         |                             |      |     | 750        | mA   |

| I <sub>CCI</sub>                                          | Current into V <sub>OFFSET</sub> terminal <sup>(2)</sup> | V <sub>CCI</sub> = 3.6 V                                                                                  |                             |      |     | 450        | mA   |

| I <sub>CC2</sub>                                          | Current into V <sub>CC2</sub> terminal                   | $V_{CC2} = 8.75V$                                                                                         |                             |      |     | 25         | mA   |

| $Z_{IN}$                                                  | Internal Differential Impedance                          |                                                                                                           |                             | 95   |     | 105        | Ohms |

| Z <sub>LINE</sub>                                         | Line Differential Impedance (PWB/Trace)                  |                                                                                                           |                             | 90   | 100 | 110        | Ohms |

| C <sub>I</sub>                                            | Input capacitance (1)                                    | f = 1 MHz                                                                                                 |                             |      |     | 10         | pF   |

| Co                                                        | Output capacitance (1)                                   | f = 1 MHz                                                                                                 |                             |      |     | 10         | pF   |

| C <sub>IM</sub>                                           | Input capacitance for MBRST[0:15] pins                   | f = 1 MHz                                                                                                 |                             | 160  |     | 210        | pF   |

Applies to LVCMOS pins only.

Exceeding the maximum allowable absolute voltage difference between  $V_{CC}$  and  $V_{CCI}$  may result in excess current draw. (Refer to Absolute Maximum Ratings for details)

Figure 8. Measurment Condition for LVCMOS Output

# **SWITCHING CHARACTERISTICS**

over operating free-air temperature range (unless otherwise noted)

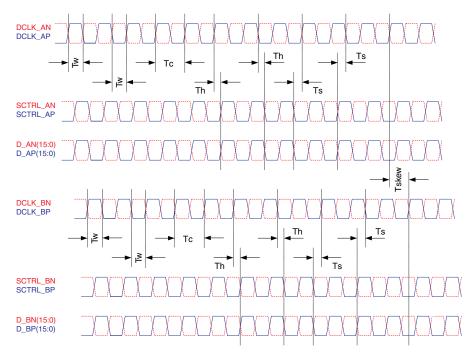

|                        | LVDS TIMING PARAMETERS See Figure 9                                       | MIN   | NOM  | MAX  | UNIT |

|------------------------|---------------------------------------------------------------------------|-------|------|------|------|

| T <sub>c</sub>         | Clock Cycle DLCK_A or DCLKC_B                                             |       | 4.0  |      | ns   |

| T <sub>w</sub>         | Pulse Width DCLK_A or DCLK_B                                              |       | 1.25 |      | ns   |

| T <sub>s</sub>         | Setup Time, D_A[0:15] before DCLK_A                                       | .35   |      |      | ns   |

| T <sub>s</sub>         | Setup Time, D_B[0:15] before DCLK_B                                       | .35   |      |      | ns   |

| T <sub>h</sub>         | Hold Time, D_A[0:15] after DCLK_A                                         | .35   |      |      | ns   |

| T <sub>h</sub>         | Hold Time, D_B[0:15] after DCLK_B                                         | .35   |      |      | ns   |

| T <sub>skew</sub>      | Channel B relative to Channel A                                           | -1.25 |      | 1.25 | ns   |

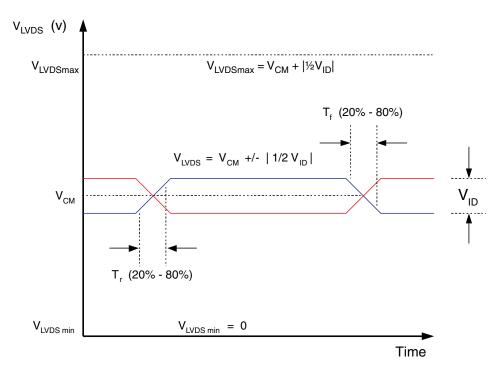

|                        | LVDS Waveform Requirements See Figure 10                                  |       |      |      |      |

| V <sub>ID</sub>        | Input Differential Voltage (absolute difference)                          | 100   | 400  | 600  | mV   |

| $V_{CM}$               | Common Mode Voltage                                                       |       | 1200 |      | mV   |

| $V_{LVDS}$             | LVDS Voltage                                                              | 0     |      | 2000 | mV   |

| T <sub>r</sub>         | Rise Time (20% to 80%)                                                    | 100   |      | 400  | ps   |

| T <sub>r</sub>         | Fall Time (80% to 20%)                                                    | 100   |      | 400  | ps   |

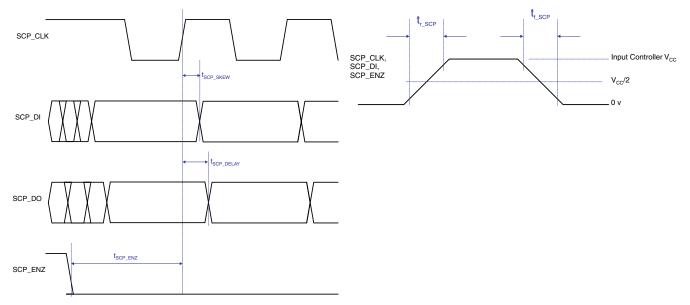

|                        | Serial Control Bus Timing Parameters See Figure 11 and Figure 12          |       |      |      |      |

| f <sub>SCP_CLK</sub>   | SCP Clock Frequency                                                       | 50    |      | 500  | KHz  |

| T <sub>SCP_SKEW</sub>  | Time between valid SCP_DI and rising edge of SCP_CLK                      | -300  |      | 300  | ns   |

| T <sub>SCP_DELAY</sub> | Time between valid SCP_DO and rising edge of SCP_CLK                      |       |      | 2600 | ns   |

| T <sub>SCP_ENZ</sub>   | Time between falling edge of SCP_ENZ and the first rising edge of SCP_CLK | 30    |      | _    | ns   |

| T <sub>r_SCP</sub>     | Rise time for SCP signals                                                 |       |      | 200  | ns   |

| T <sub>fP</sub>        | Fall time for SCP signals                                                 |       |      | 200  | ns   |

Figure 9. LVDS Timing Waveforms

Figure 10. LVDS Waveform Requirements

Figure 11. Serial Communications Bus Timing **Parameters**

Figure 12. Serial Communications Bus Waveform Requirements

# **DMD Power-Up and Power-Down Procedures**

Repeated failure to adhere to the prescribed power-up and power-down procedures may affect device reliability. The DLP5500 power-up and power-down procedures are defined by the DLPC200 Datasheet (TI Literature number DLPS012) and the .55 XGA Chipset Datasheet (TI Literature number DLPZ004). These procedures must be followed to ensure reliable operation of the device.

# **Micromirror Array Physical Characteristics**

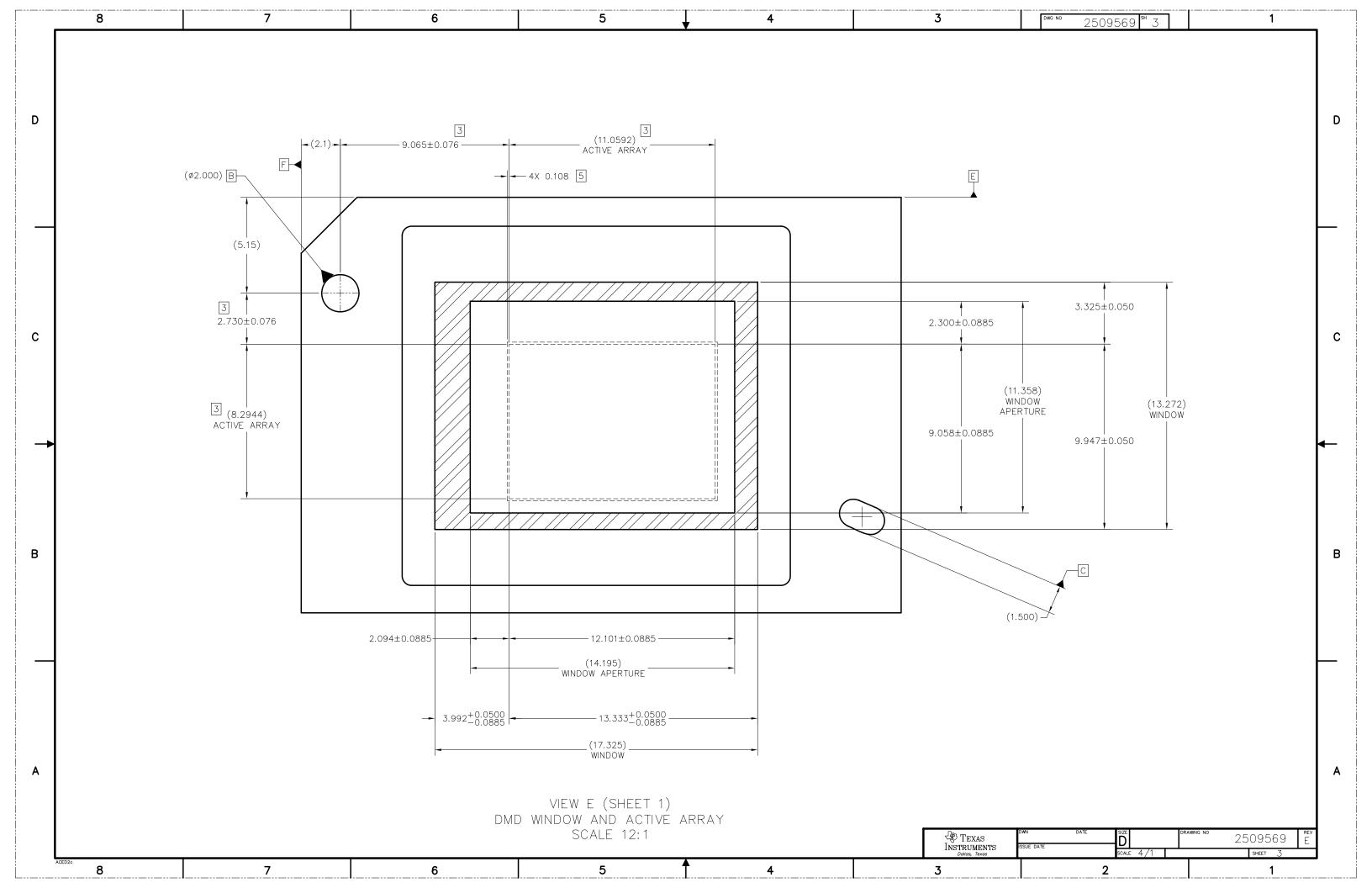

Physical characteristics of the micromirror array are provided in . Additional details are provided in the **Package Mechanical Characteristics** section at the end of this document.

**Table 1. Micromirror Array Physical Characteristics**

| PARAMETER                                               | VALUE  | UNITS        |

|---------------------------------------------------------|--------|--------------|

| Number of active micromirror columns <sup>(1)</sup>     | 1024   | micromirrors |

| Number of active micromirror rows <sup>(1)</sup>        | 768    | micromirrors |

| Micromirror pitch (1)                                   | 10.8   | microns      |

| Minuscrimon astina amenda hainta (1)                    | 768    | micromirrors |

| Micromirror active array height (1)                     | 8.294  | millimeters  |

| Adiana rational and in a sure of the first transfer (1) | 1024   | micromirrors |

| Micromirror active array width (1)                      | 11.059 | millimeters  |

| Micromirror array border <sup>(2)</sup>                 | 10     | mirrors/side |

<sup>(1)</sup> See Figure 3

# **Micromirror Array Optical Characteristics**

TI assumes no responsibility for end-equipment optical performance. Achieving the desired end-equipment optical performance involves making trade-off's between numerous component and system design parameters. Refer to the following Application Notes for additional details, considerations, and guidelines:

Single-Panel DLP™ Projection System Optics Application Report (TI literature number DLPA002)

<sup>(2)</sup> The mirrors that form the array border are hard-wired to tilt in the -12° ("Off") direction once power is applied to the DMD (see Figure 3 and Figure 4).

#### **Table 2. Micromirror Array Optical Characteristics**

|   | PARAMETER                                                | CONDITIONS                                              | MIN | NOM                       | MAX | UNIT         |

|---|----------------------------------------------------------|---------------------------------------------------------|-----|---------------------------|-----|--------------|

| _ | Micromirror tilt angle                                   | DMD "parked" state <sup>(1)(2)(3)</sup> , see Figure 4  |     | 0                         |     | 4            |

| α |                                                          | DMD "landed" state (1)(4)(5)see Figure 4                |     | 12                        |     | degrees      |

| β | Micromirror tilt angle variation (1)(4)(6)(7)(8)         | See Figure 4                                            | -1  |                           | 1   | degrees      |

|   | Micromirror Cross Over Time <sup>(9)</sup>               |                                                         |     | 16                        | 22  | us           |

|   | Micromirror Switching Time <sup>(10)</sup>               |                                                         |     | 140                       |     | us           |

|   | Non Operation animom (11)                                | Non-adjacent micromirrors                               |     |                           | 10  | :            |

|   | Non Operating micromirrors <sup>(11)</sup>               | adjacent micromirrors                                   |     |                           | 0   | micromirrors |

|   | Orientation of the micromirror axis-of-rotation (12)     | See Figure 3                                            | 44  | 45                        | 46  | degrees      |

|   | Micromirror array optical efficiency <sup>(13)(14)</sup> | 420 nm to 700 nm, with all micromirrors in the ON state |     | 68                        |     | %            |

|   | Window material                                          |                                                         |     | Eagle 2000<br>ng Eagle XG |     |              |

|   | Window refractive index                                  | at 546.1 nm                                             |     | 1.5119                    |     |              |

- (1) Measured relative to the plane formed by the overall micromirror array

- (2) "Parking" the micromirror array returns all of the micromirrors to an essentially flat (0°) state (as measured relative to the plane formed by the overall micromirror array).

- (3) When the micromirror array is "parked", the tilt angle of each individual micromirror is uncontrolled.

- (4) Additional variation exists between the micromirror array and the package datums, as shown in the Package Mechanical Characteristics section at the end of this document.

- (5) When the micromirror array is "landed", the tilt angle of each individual micromirror is dictated by the binary contents of the CMOS memory cell associated with each individual micromirror. A binary value of "1" will result in a micromirror "landing" in an nominal angular position of "+12 degrees". A binary value of 0 will result in a micromirror "landing" in an nominal angular position of "-12 degrees".

- (6) Represents the "landed" tilt angle variation relative to the Nominal "landed" tilt angle.

- (7) Represents the variation that can occur between any two individual micromirrors, located on the same device or located on different devices.

- (8) For some applications, it is critical to account for the micromirror tilt angle variation in the overall System Optical Design. With some System Optical Designs, the micromirror tilt angle variation within a device may result in perceivable non-uniformities in the light field reflected from the micromirror array. With some System Optical Designs, the micromirror tilt angle variation between devices may result in colorimetry variations and/or system contrast variations.

- (9) Micromirror Cross Over time is primarily a function of the natural response time of the micromirrors.

- (10) Micromirror switching is controlled and coordinated by the DLPC200 (TI Literature number DLPS014) AND DLPA200 (TI Literature number DLPS015). Nominal Switching time depends on the system implementation and represents the time for the entire micromirror array to be refreshed.

- (11) Non-operating micromirror is defined as a micromirror that is unable to transition nominally from the -12 degree position to +12 degree or vice versa.

- (12) Measured relative to the package datums "B" and "C", shown in the Package Mechanical Characteristics section at the end of this document.

- (13) The minimum or maximum DMD optical efficiency observed in a specific application depends on numerous application-specific design variables, such as:

- (a) Illumination wavelength, bandwidth/line-width, degree of coherence

- (b) Illumination angle, plus angle tolerance

- (c) Illumination and projection aperture size, and location in the system optical path

- (d) Illumination overfill of the DMD micromirror array

- (e) Aberrations present in the illumination source and/or path

- (f) Aberrations present in the projection path

- (g) Etc.

The specified nominal DMD optical efficiency is based on the following use conditions:

- (a) Visible illumination (420 nm 700 nm)

- (b) Input illumination optical axis oriented at 24° relative to the window normal

- (c) Projection optical axis oriented at 0° relative to the window normal

- (d) f/3.0 illumination aperture

- (e) f/2.4 projection aperture

Based on these use conditions, the nominal DMD optical efficiency results from the following four components:

- (a) Micromirror array fill factor: nominally 92%

- (b) Micromirror array diffraction efficiency: nominally 86%

- (c) Micromirror surface reflectivity: nominally 88%

- (d) Window transmission: nominally 97% (single pass, through two surface transitions)

- (14) Does not account for the effect of micromirror switching duty cycle, which is application dependant. Micromirror switching duty cycle represents the percentage of time that the micromirror is actually reflecting light from the optical illumination path to the optical projection path. This duty cycle depends on the illumination aperture size, the projection aperture size, and the micromirror array update rate.

### Table 2. Micromirror Array Optical Characteristics (continued)

| PARAMETER                       | CONDITIONS                                        | MIN | NOM      | MAX | UNIT    |

|---------------------------------|---------------------------------------------------|-----|----------|-----|---------|

| Window flatness <sup>(15)</sup> | Per 25 mm                                         |     |          | 4   | fringes |

| Window Artifact Size            | Within the Window<br>Aperture <sup>(16)(17)</sup> |     |          | 400 | um      |

| Window aperture                 |                                                   |     | See (16) |     |         |

<sup>(15)</sup> At a wavelength of 632.8nm.

#### **Thermal Characteristics**

Achieving optimal DMD performance requires proper management of the maximum DMD case temperature, the maximum temperature of any individual micromirror in the active array, the maximum temperature of the window aperture, and the temperature gradient between case temperature and the predicted micromirror array temperature. (see Figure 13).

Refer to the RECOMMEND OPERATING CONDITIONS for applicable temperature limits.

#### **Package Thermal Resistance**

The DMD is designed to conduct absorbed and dissipated heat to the back of the Series 450 package where it can be removed by an appropriate heat sink. The heat sink and cooling system must be capable of maintaining the package within the specified operational temperatures, refer to Figure 13. The total heat load on the DMD is typically driven by the incident light absorbed by the active area; although other contributions include light energy absorbed by the window aperture and electrical power dissipation of the array.

#### Package Thermal Resistance

|                                            | Min | Nom | Max | Units |

|--------------------------------------------|-----|-----|-----|-------|

| Active Micromirror Array resistance to TC2 |     |     | 0.6 | °C/W  |

#### **Case Temperature**

The temperature of the DMD case can be measured directly. For consistency, a Thermal Test Point locations TC1 & TC2 are defined, as shown in Figure 13.

<sup>(16)</sup> Refer to the Package Mechanical Characteristics section at the end of this document for details regarding the size and location of the window aperture.

<sup>(17)</sup> Refers only to non-cleanable artifacts. Refer to DMD S4xx Glass Cleaning Procedure (TI Literature number DLPA025) and DMD S4xx Handling Specifications (TI Literature number DLPA014) for recommend handling and cleaning processes.

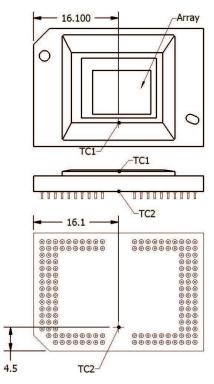

Figure 13. Thermal Test Point Location

### **Micromirror Array Temperature Calculuation**

Micromirror array temperature cannot be measured directly; therefore it must be computed analytically from measurement points (Figure 13), the package thermal resistance, the electrical power, and the illumination heat load. The relationship between micromirror array temperature and the case temperature are provided by the following equations:

$$T_{Array} = T_{Ceramic} + (Q_{Array} \cdot R_{Array-To-Ceramic})$$

$$Q_{Array} = Q_{ELE} + Q_{ILL}$$

Where the following elements are defined as:

T<sub>Array</sub> = computed micromirror array temperature (°C)

T<sub>Ceramic</sub> = Ceramic temperature (°C) (TC2 Location Figure 13)

Q<sub>Array</sub> = Total DMD array power (electrical + absorbed) (measured in Watts)

R<sub>Array-To-Ceramic</sub> = thermal resistance of DMD package from array to TC2 (°C/Watt) (see Package Thermal Resistance)

Q<sub>ELE</sub> = Nominal electrical power (Watts)

Q<sub>ILL</sub> = Absorbed illumination energy (Watts)

An example calculation is provided below based on a traditional DLP Video projection system. The electrical power dissipation of the DMD is variable and depends on the voltages, data rates, and operating frequencies. The nominal electrical power dissipation to be used in the calculation is 2.0 Watts. Thus,  $Q_{ELE} = 2.0$  Watts. The absorbed power from the illumination source is variable and depends on the operating state of the mirrors and the intensity of the light source. Based on modeling and measured data from DLP projection system  $Q_{ILL} = C_{L2W} \cdot SL$ . Where

C<sub>I 2W</sub> is a Lumens to Watts constant, and can be estimated at 0.00288 Watt/Lumen

SL = Screen Lumens nominally measured to be 2000 lumens

Copyright © 2010–2011, Texas Instruments Incorporated

Qarray = 2.0 + (0.00288 • 2000) = 7.76 watts, Estimated total power on micromirror Array

T<sub>Ceramic</sub> = 55.0 °C, assumed system measurement

Finally, T<sub>Array</sub> (micromirror active array temperature) is

$$T_{Array}$$

= 55.0 °C + (7.76 watts • 0.6 °C/watt) = **59.7** °C

For additional explanation of DMD Mechanical and Thermal calculations and considerations please refer to DLP Series-450 DMD and System Mounting Concepts (TI Literature number DLPA015).

www.ti.com

# **Table 3. Revision History**

| REVISION | SECTION(S)                | COMMENT                                                                                                                                                                                                             |

|----------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *        | All                       | Initial release                                                                                                                                                                                                     |

| А        | Absolute Maximum Ratings  | Changed $V_{REF}$ to $V_{CCI}$ Changed Illumination Power Density < 420nm Max spec to 20 mW/cm^2 Clarified Note 6 measurement point Added $ V_{ID} $ to absolute max table. Added $V_{MBRST}$ to absolute max table |

|          | Related Documents         | Added additional related documents                                                                                                                                                                                  |

| _        | Micromirror Array Optical | Changed window refractive index NOM spec from 1.5090 to 1.5119                                                                                                                                                      |

| В        | Characteristics, Table 2  | Added table note "At a wavelength of 632.8 nm"                                                                                                                                                                      |

Product Folder Link(s): DLP5500

# PACKAGE OPTION ADDENDUM

10-May-2012

#### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package Type | Package<br>Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup>    | Lead/<br>Ball Finish | MSL Peak Temp <sup>(3)</sup> | Samples<br>(Requires Login) |

|------------------|-----------------------|--------------|--------------------|------|-------------|----------------------------|----------------------|------------------------------|-----------------------------|

| DLP5500FYA       | ACTIVE                | CPGA         | FYA                | 149  | 5           | Green (RoHS<br>& no Sb/Br) | FE NIAU              | Level-1-NC-NC                |                             |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE OPTION ADDENDUM

10-May-2012

#### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package Type | Package<br>Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup>    | Lead/<br>Ball Finish | MSL Peak Temp <sup>(3)</sup> | Samples<br>(Requires Login) |

|------------------|-----------------------|--------------|--------------------|------|-------------|----------------------------|----------------------|------------------------------|-----------------------------|

| DLP5500FYA       | ACTIVE                | CPGA         | FYA                | 149  | 5           | Green (RoHS<br>& no Sb/Br) | FE NIAU              | Level-1-NC-NC                |                             |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

**Applications**

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

**Products**

Wireless Connectivity

#### Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive **Amplifiers** amplifier.ti.com Communications and Telecom www.ti.com/communications dataconverter.ti.com Computers and Peripherals www.ti.com/computers **Data Converters DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps DSP dsp.ti.com **Energy and Lighting** www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical Logic logic.ti.com Security www.ti.com/security Power Mgmt www.ti.com/space-avionics-defense power.ti.com Space, Avionics and Defense Microcontrollers Video and Imaging microcontroller.ti.com www.ti.com/video www.ti-rfid.com **OMAP Mobile Processors** www.ti.com/omap

TI E2E Community Home Page

www.ti.com/wirelessconnectivity

e2e.ti.com