TDA8595 I<sup>2</sup>C-bus controlled 4 × 45 W power amplifier Rev. 02 — 21 November 2007

**Product data sheet**

# 1. General description

The TDA8595 is a complementary quad Bridge Tied Load (BTL) audio power amplifier made in BCDMOS technology. It contains four independent amplifiers in BTL configuration. Through the I<sup>2</sup>C-bus, diagnosis of temperature warning and clipping level is fully programmable and the information available via two diagnostic pins is selectable. The status of each amplifier (output offset, load or no load, short-circuit or speaker incorrectly connected) can be read separately.

## 2. Features

## 2.1 General

- Operates in legacy mode (non I<sup>2</sup>C-bus) and I<sup>2</sup>C-bus mode (3.3 V and 5 V compliant)

- Three hardware-programmable I<sup>2</sup>C-bus addresses

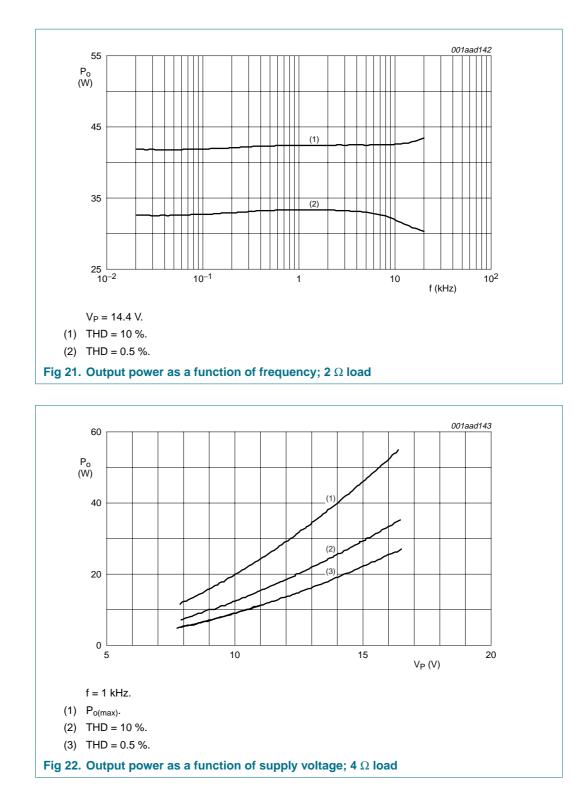

- Drive 4  $\Omega$  or 2  $\Omega$  loads

- Speaker fault detection

- Independent short-circuit protection per channel

- Loss of ground and open V<sub>P</sub> safe (with 150 mΩ series impedance and a supply decoupling capacitor of 2200 µF maximum)

- All outputs short-circuit proof to ground, supply voltage and across the load

- All pins short-circuit proof to ground

- Temperature-controlled gain reduction to prevent audio holes at high junction temperatures

- Low battery voltage detection

- Offset detection

- This part has been qualified in accordance with AEC-Q100

## 2.2 I<sup>2</sup>C-bus mode

- DC load detection: open-circuit, short-circuit and load present

- AC load (tweeter) detection

- During start-up, can detect which load is connected so the appropriate gain can be selected without audio pop

- Independently selectable soft mute of front channels (channel 1 and channel 3) and rear channels (channel 2 and channel 4)

- Programmable gain (26 dB and 16 dB) of front channels and rear channels

- Fully programmable diagnostic levels can be set:

- Programmable clip detection: 2 %, 5 % or 10 %

- Programmable thermal pre-warning

- Selectable information on the DIAG and STB pins:

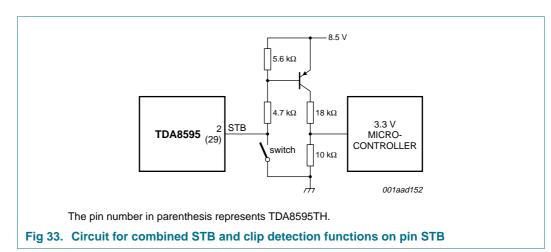

- The STB pin can be programmed/multiplexed with second clip detection

- Clip information of each channel can be directed separately to the DIAG pin or the STB pin

- Independent enabling of thermal, clip or load fault detection (short across or to V<sub>P</sub> or to ground) on DIAG pin

## 3. Quick reference data

#### Table 1.Quick reference data

Refer to test circuit (see <u>Figure 30</u>) at  $V_P = V_{P1} = V_{P2} = 14.4 \text{ V}$ ;  $R_L = 4 \Omega$ ; f = 1 kHz;  $R_S = 0 \Omega$ ; normal mode; unless otherwise specified. Tested at  $T_{amb} = 25 \text{ °C}$ ; guaranteed for  $T_{amb} = -40 \text{ °C}$  to +105 °C.

| Symbol            | Parameter                 | Conditions                                                                          | Min | Тур  | Max | Unit |

|-------------------|---------------------------|-------------------------------------------------------------------------------------|-----|------|-----|------|

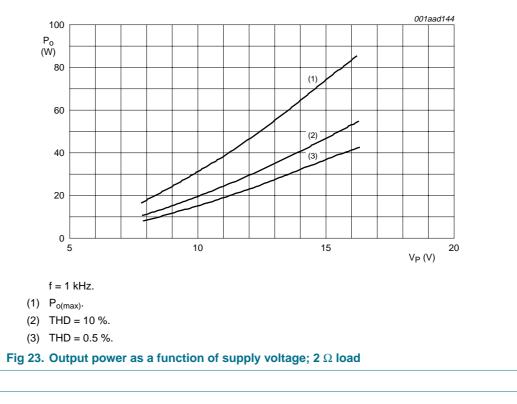

| VP                | supply voltage            | $R_L = 4 \Omega$                                                                    | 8   | 14.4 | 18  | V    |

| lq                | quiescent current         | no load                                                                             | -   | 270  | 400 | mA   |

| Po                | output power              | V <sub>P</sub> = 14.4 V                                                             |     |      |     |      |

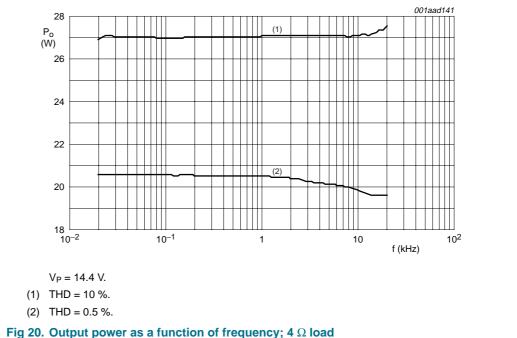

|                   |                           | $R_{L}$ = 4 $\Omega$ ; THD = 0.5 %                                                  | 18  | 20   | -   | W    |

|                   |                           | $R_L$ = 4 $\Omega$ ; THD = 10 %                                                     | 23  | 25   | -   | W    |

|                   |                           | $R_L = 4 \Omega$ ; maximum<br>power; V <sub>i</sub> = 2 V (RMS)<br>square wave      | 37  | 40   | -   | W    |

|                   |                           | $R_L = 2 \Omega$ ; maximum<br>power; V <sub>i</sub> = 2 V (RMS)<br>square wave      | 58  | 64   | -   | W    |

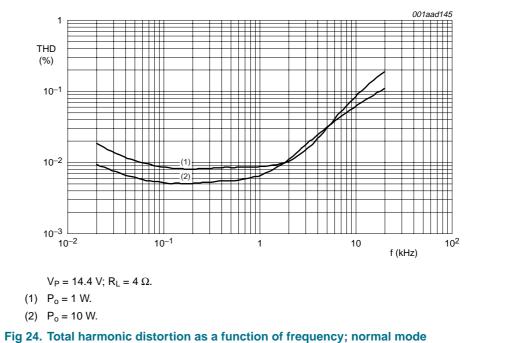

| THD               | total harmonic distortion | $      R_L = 4 \ \Omega; \ f = 1 \ \text{kHz};                                    $ | -   | 0.01 | 0.1 | %    |

| V <sub>n(o)</sub> | noise output<br>voltage   | filter 20 Hz to 22 kHz; $R_S = 1 \ k\Omega$                                         |     |      |     |      |

|                   |                           | normal mode                                                                         | -   | 45   | 65  | μV   |

|                   |                           | line driver mode                                                                    | -   | 22   | 29  | μV   |

# 4. Ordering information

| Туре      | Package |                                                                                               |          |  |  |  |  |  |

|-----------|---------|-----------------------------------------------------------------------------------------------|----------|--|--|--|--|--|

| number    | Name    | Description                                                                                   | Version  |  |  |  |  |  |

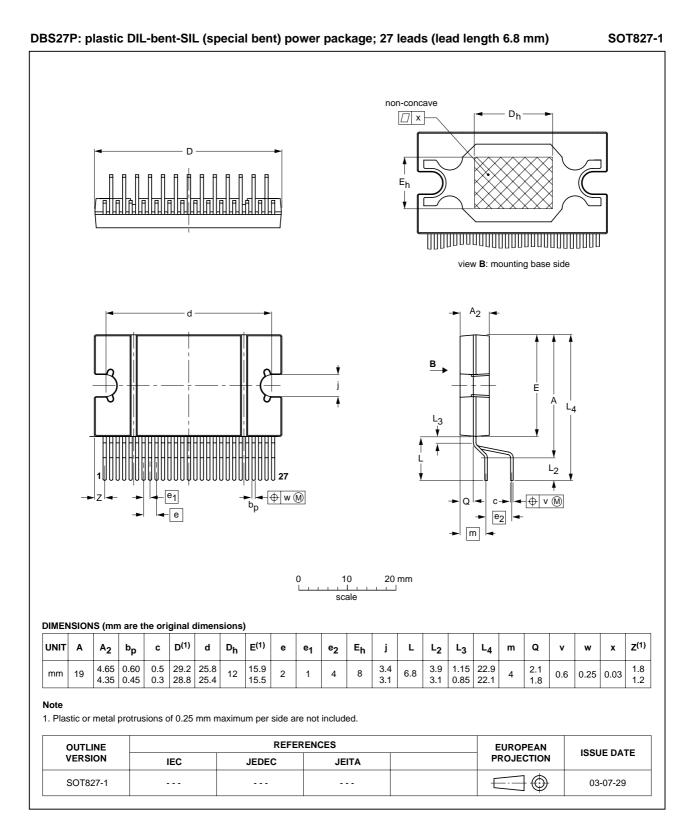

| TDA8595J  | DBS27P  | plastic DIL-bent-SIL (special bent) power package;<br>27 leads (lead length 6.8 mm)           | SOT827-7 |  |  |  |  |  |

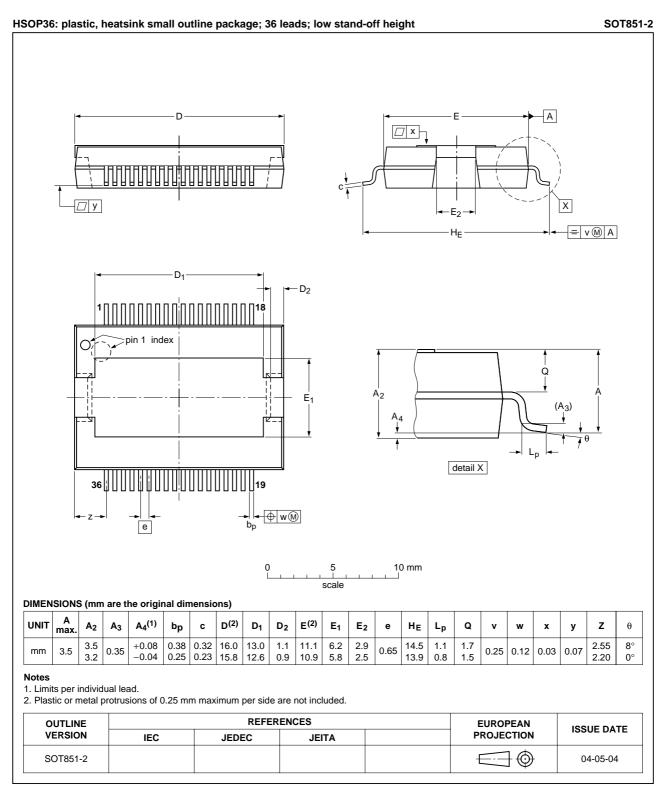

| TDA8595TH | HSOP36  | plastic, heatsink small outline package; 36 leads;<br>low stand-off height                    | SOT851-2 |  |  |  |  |  |

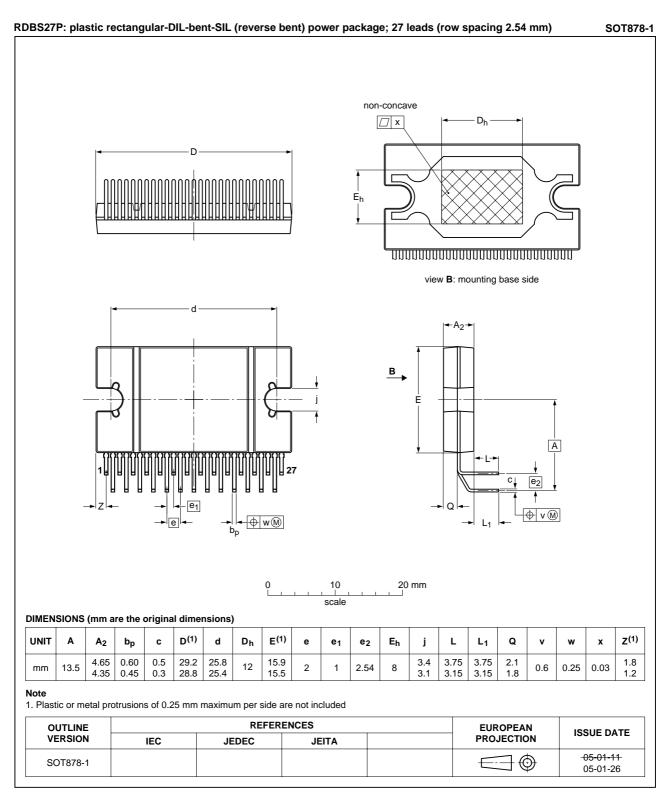

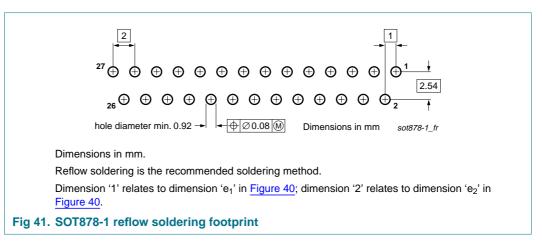

| TDA8595SD | RDBS27P | plastic rectangular-DIL-bent-SIL (reverse bent) power package; 27 leads (row spacing 2.54 mm) | SOT878-1 |  |  |  |  |  |

#### $I^2C\text{-bus}$ controlled $4\times45$ W power amplifier

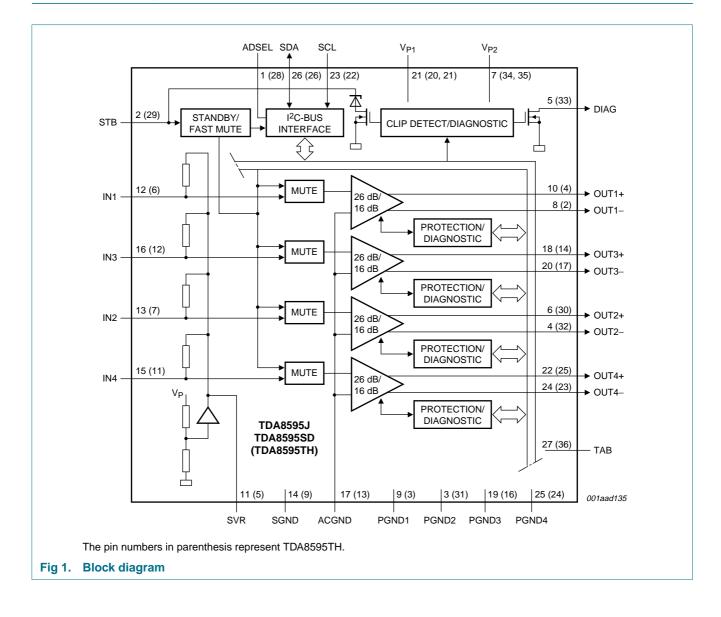

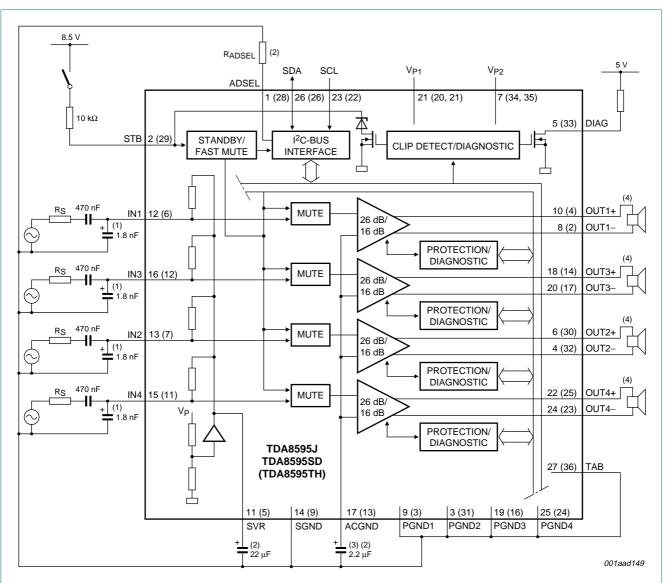

# 5. Block diagram

$I^2C\text{-bus}$  controlled  $4\times45$  W power amplifier

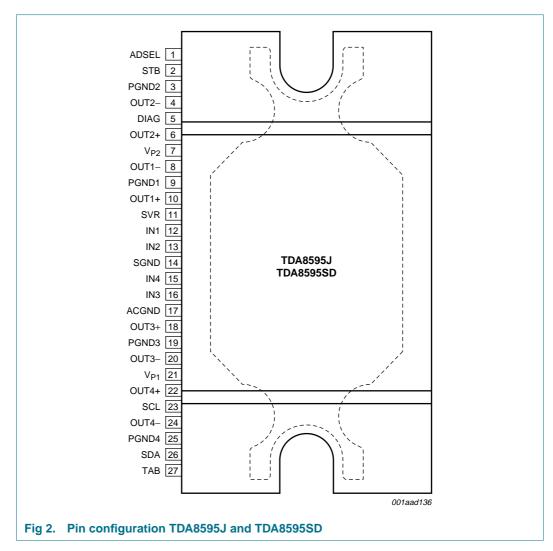

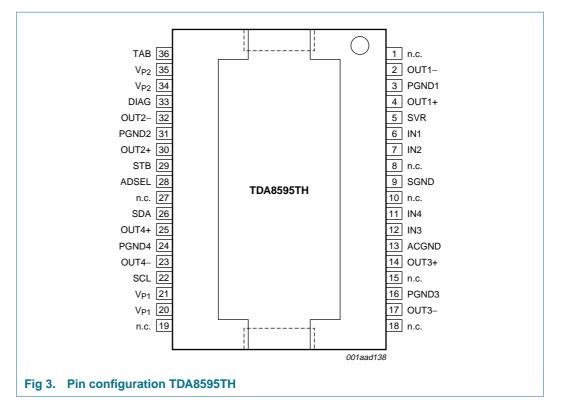

# 6. Pinning information

## 6.1 Pinning

#### $I^2C\text{-bus}$ controlled $4\times45$ W power amplifier

## 6.2 Pin description

| Symbol          | Pin                                    |           | Description                                                                                       |  |  |  |  |  |

|-----------------|----------------------------------------|-----------|---------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                 | TDA8595J<br>TDA8595SD <mark>[1]</mark> | TDA8595TH |                                                                                                   |  |  |  |  |  |

| ADSEL           | 1                                      | 28        | I <sup>2</sup> C-bus address select                                                               |  |  |  |  |  |

| STB             | 2                                      | 29        | standby (I <sup>2</sup> C-bus mode) or mode pin (legacy mode); programmable second clip indicator |  |  |  |  |  |

| PGND2           | 3                                      | 31        | power ground channel 2                                                                            |  |  |  |  |  |

| OUT2-           | 4                                      | 32        | negative channel 2 output                                                                         |  |  |  |  |  |

| DIAG            | 5                                      | 33        | diagnostic/clip detection output                                                                  |  |  |  |  |  |

| OUT2+           | 6                                      | 30        | positive channel 2 output                                                                         |  |  |  |  |  |

| V <sub>P2</sub> | 7                                      | 34 and 35 | supply voltage 2                                                                                  |  |  |  |  |  |

| n.c.            | -                                      | 1         | not connected                                                                                     |  |  |  |  |  |

| OUT1-           | 8                                      | 2         | negative channel 1 output                                                                         |  |  |  |  |  |

| PGND1           | 9                                      | 3         | power ground channel 1                                                                            |  |  |  |  |  |

| OUT1+           | 10                                     | 4         | positive channel 1 output                                                                         |  |  |  |  |  |

| SVR             | 11                                     | 5         | half supply filter capacitor                                                                      |  |  |  |  |  |

| IN1             | 12                                     | 6         | channel 1 input                                                                                   |  |  |  |  |  |

| IN2             | 13                                     | 7         | channel 2 input                                                                                   |  |  |  |  |  |

| n.c.            | -                                      | 8         | not connected                                                                                     |  |  |  |  |  |

| SGND            | 14                                     | 9         | signal ground                                                                                     |  |  |  |  |  |

### Table 3. Pin description

| IN41511channel 4 inputIN31612channel 3 inputACGND1713AC ground inputOUT3+1814positive channel 3 outputn.c15not connectedPGND31916power ground channel 3OUT3-2017negative channel 3 outputn.c18 and 19not connectedVP12120 and 21supply voltage 1OUT4+2225positive channel 4 outputSCL2322l²C-bus clock inputOUT4-2423negative channel 4 outputPGND42524power ground channel 4SDA2626l²C-bus data input/outputn.c27not connected | Symbol          | Pin |           | Description                            |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----------|----------------------------------------|--|--|

| INA1511channel 4 inputIN31612channel 3 inputACGND1713AC ground inputOUT3+1814positive channel 3 outputn.c15not connectedPGND31916power ground channel 3OUT3-2017negative channel 3 outputn.c18 and 19not connectedVP12120 and 21supply voltage 1OUT4+2225positive channel 4 outputSCL2322l²C-bus clock inputOUT4-2423negative channel 4 outputPGND42524power ground channel 4SDA2626l²C-bus data input/outputn.c27not connected |                 |     | TDA8595TH |                                        |  |  |

| IN31612channel 3 inputACGND1713AC ground inputOUT3+1814positive channel 3 outputn.c15not connectedPGND31916power ground channel 3OUT3-2017negative channel 3 outputn.c18 and 19not connectedVP12120 and 21supply voltage 1OUT4+2225positive channel 4 outputSCL2322l²C-bus clock inputOUT4-2423negative channel 4 outputPGND42524power ground channel 4SDA2626l²C-bus data input/outputn.c27not connected                       | n.c.            | -   | 10        | not connected                          |  |  |

| ACGND1713AC ground inputOUT3+1814positive channel 3 outputn.c15not connectedPGND31916power ground channel 3OUT3-2017negative channel 3 outputn.c18 and 19not connectedVP12120 and 21supply voltage 1OUT4+2225positive channel 4 outputSCL2322l²C-bus clock inputOUT4-2423negative channel 4 outputPGND42524power ground channel 4SDA2626l²C-bus data input/outputn.c27not connected                                             | IN4             | 15  | 11        | channel 4 input                        |  |  |

| OUT3+1814positive channel 3 outputn.c15not connectedPGND31916power ground channel 3OUT3-2017negative channel 3 outputn.c18 and 19not connectedVp12120 and 21supply voltage 1OUT4+2225positive channel 4 outputSCL2322l²C-bus clock inputOUT4-2423negative channel 4 outputPGND42524power ground channel 4SDA2626l²C-bus data input/outputn.c27not connected                                                                     | IN3             | 16  | 12        | channel 3 input                        |  |  |

| n.c15not connectedPGND31916power ground channel 3OUT3-2017negative channel 3 outputn.c18 and 19not connectedVP12120 and 21supply voltage 1OUT4+2225positive channel 4 outputSCL2322l²C-bus clock inputOUT4-2423negative channel 4 outputPGND42524power ground channel 4SDA2626l²C-bus data input/outputn.c27not connectedTAB2736heatsink connection; must be connected to                                                       | ACGND           | 17  | 13        | AC ground input                        |  |  |

| PGND31916power ground channel 3OUT32017negative channel 3 outputn.c18 and 19not connectedVp12120 and 21supply voltage 1OUT4+2225positive channel 4 outputSCL2322l²C-bus clock inputOUT42423negative channel 4 outputPGND42524power ground channel 4SDA2626l²C-bus data input/outputn.c27not connectedTAB2736heatsink connection; must be connected to                                                                           | OUT3+           | 18  | 14        | positive channel 3 output              |  |  |

| OUT3-2017negative channel 3 outputn.c18 and 19not connectedVP12120 and 21supply voltage 1OUT4+2225positive channel 4 outputSCL2322l²C-bus clock inputOUT4-2423negative channel 4 outputPGND42524power ground channel 4SDA2626l²C-bus data input/outputn.c27not connectedTAB2736heatsink connection; must be connected to                                                                                                        | n.c.            | -   | 15        | not connected                          |  |  |

| n.c18 and 19not connectedVP12120 and 21supply voltage 1OUT4+2225positive channel 4 outputSCL2322l²C-bus clock inputOUT4-2423negative channel 4 outputPGND42524power ground channel 4SDA2626l²C-bus data input/outputn.c27not connectedTAB2736heatsink connection; must be connected to                                                                                                                                          | PGND3           | 19  | 16        | power ground channel 3                 |  |  |

| VP12120 and 21supply voltage 1OUT4+2225positive channel 4 outputSCL2322I²C-bus clock inputOUT4-2423negative channel 4 outputPGND42524power ground channel 4SDA2626I²C-bus data input/outputn.c27not connectedTAB2736heatsink connection; must be connected to                                                                                                                                                                   | OUT3-           | 20  | 17        | negative channel 3 output              |  |  |

| OUT4+2225positive channel 4 outputSCL2322I²C-bus clock inputOUT4-2423negative channel 4 outputPGND42524power ground channel 4SDA2626I²C-bus data input/outputn.c27not connectedTAB2736heatsink connection; must be connected to                                                                                                                                                                                                 | n.c.            | -   | 18 and 19 | not connected                          |  |  |

| SCL2322I²C-bus clock inputOUT42423negative channel 4 outputPGND42524power ground channel 4SDA2626I²C-bus data input/outputn.c27not connectedTAB2736heatsink connection; must be connected to                                                                                                                                                                                                                                    | V <sub>P1</sub> | 21  | 20 and 21 | supply voltage 1                       |  |  |

| OUT4-2423negative channel 4 outputPGND42524power ground channel 4SDA2626l²C-bus data input/outputn.c27not connectedTAB2736heatsink connection; must be connected to                                                                                                                                                                                                                                                             | OUT4+           | 22  | 25        | positive channel 4 output              |  |  |

| PGND42524power ground channel 4SDA2626l²C-bus data input/outputn.c27not connectedTAB2736heatsink connection; must be connected to                                                                                                                                                                                                                                                                                               | SCL             | 23  | 22        | I <sup>2</sup> C-bus clock input       |  |  |

| SDA2626I²C-bus data input/outputn.c27not connectedTAB2736heatsink connection; must be connected to                                                                                                                                                                                                                                                                                                                              | OUT4-           | 24  | 23        | negative channel 4 output              |  |  |

| n.c27not connectedTAB2736heatsink connection; must be connected to                                                                                                                                                                                                                                                                                                                                                              | PGND4           | 25  | 24        | power ground channel 4                 |  |  |

| TAB2736heatsink connection; must be connected to                                                                                                                                                                                                                                                                                                                                                                                | SDA             | 26  | 26        | I <sup>2</sup> C-bus data input/output |  |  |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                           | n.c.            | -   | 27        | not connected                          |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                 | TAB             | 27  | 36        |                                        |  |  |

Table 3.

Pin description ...continued

[1] To keep the output pins on the front side, special reverse bending is applied.

## 7. Functional description

The TDA8595 is a complementary quad BTL audio power amplifier made in BCDMOS technology. It contains four independent amplifiers in BTL configuration (see Figure 1). Through the l<sup>2</sup>C-bus, the diagnostic functions of temperature level and clip level are fully programmable and the information to be shown on the two diagnostic pins can be selected. The status of each amplifier (output offset, load or no load, short-circuit or speaker incorrectly connected) can be read separately. The TDA8595 is protected against overvoltage, short-circuit, over-temperature, open ground and open V<sub>P</sub> connections.

Three different  $I^2$ C-bus addresses are selected with an external resistor connected to the ADSEL pin. If the ADSEL pin is short-circuit to ground, the TDA8595 operates in legacy mode. In this mode, no  $I^2$ C-bus is needed and the function of the STB pin will change from two level (Standby mode and On mode) to a three level pin (Standby mode, On mode and mute).

### 7.1 Input stage

The input stage is a high-impedance pseudo-differential input stage. The negative inputs of the four channels are combined on the ACGND pin. For the best performance on supply voltage ripple rejection and pop noise, the capacitor connected to the ACGND pin must be four times the value of the input capacitor (or as close to the value as possible).

### 7.2 Output stage

The output stage of each amplifier channel consists of two PMOS power transistors and two NMOS transistors in BTL configuration. The process used is the BCDMOS process with an isolated substrate, SOI process, which has almost no parasitic components and therefore prevents latch-up.

### 7.3 Distortion (clip-) detection

If the output of the amplifier starts clipping to the supply voltage or to ground, the output will become distorted. If the distortion per channel exceeds a selectable threshold (2 %, 5 % or 10 %), one of the two diagnostic pins (DIAG pin or STB pin) will be activated. To be able to detect if, for instance, the front channels (channel 1 and channel 3) or rear channels (channel 2 and channel 4) are clipping, the clip information can be directed per channel to the DIAG pin or the STB pin. It is possible to have only the clip information on the diagnostic pins by disabling the temperature and load information on the diagnostic pin. In this mode the temperature and load protection are still functional but can only be read via the l<sup>2</sup>C-bus.

### 7.4 Output protection and short-circuit operation

When a short-circuit to ground,  $V_P$  or across the load occurs on one or more outputs of an amplifier, only the amplifier with the short-circuit is switched off. The channel that has a short-circuit and the type of short-circuit can be read-back via the l<sup>2</sup>C-bus. If the diagnostic pin is enabled for load fault information (IB2[D4] = 0) the DIAG pin will be pulled LOW. After 16 ms the amplifier will be switched on again and, if the short-circuit conditions still occur, the amplifier will be switched off.

The 16 ms cycle will reduce the dissipation. To prevent audible distortion, the amplifier channel with the short-circuit can be disabled via the  $l^2C$ -bus.

### 7.5 SOAR protection

The output transistors are protected by Safe Operating ARea (SOAR) protection. The TDA8595 has a two-stage SOAR protection:

- If the differential output voltage across the load is less than 1 V, and the current through the load is more than 4 A, the amplifier channel will be switched off during 16 ms. To prevent incorrect switch-off with an inductive load or very high input signals, the condition ( $V_o < 1$  V and  $I_L > 4$  A) must exist for more than 300 µs.

- If the differential output voltage across the load is more than 1 V, and the current through the load is more than 8 A, the amplifier channel will be switched off during 16 ms.

### 7.6 Speaker protection

To prevent damage of the speaker when one side of the speaker is connected to ground, a missing current protection is implemented. When in one channel the current in the high side power is not equal to the current in the low side power, a fault condition is assumed and the channel will be switched off. The speaker protection will be activated under the following conditions:

- $V_o < 1.75$  V and  $I_{missing(det)} > 1$  A during 80  $\mu$ s

- $V_o > 1.75$  V and  $I_{missing(det)} > 3$  A during 80  $\mu$ s

### 7.7 Standby and mute operation

The function of the STB pin is different in legacy mode and I<sup>2</sup>C-bus mode.

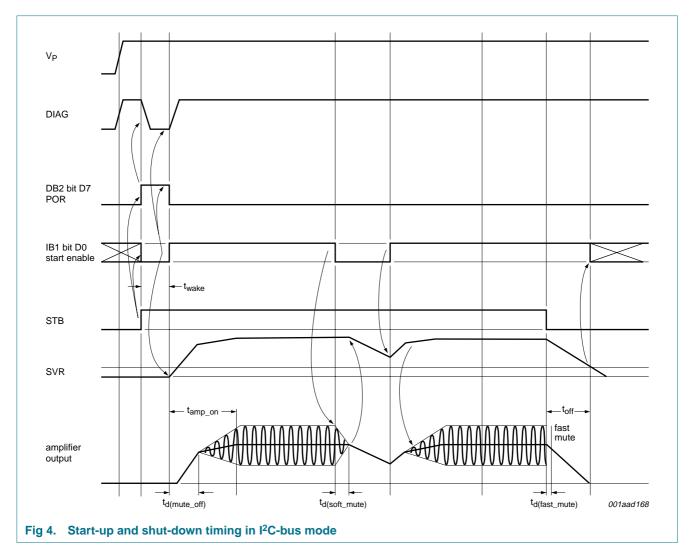

### 7.7.1 I<sup>2</sup>C-bus mode

When the STB pin is LOW, the total quiescent current is low, and the  $I^2C$ -bus lines will not be loaded.

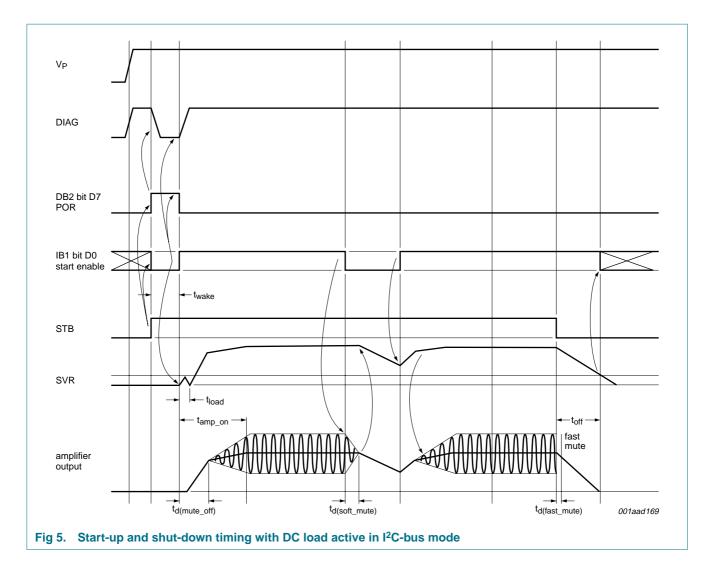

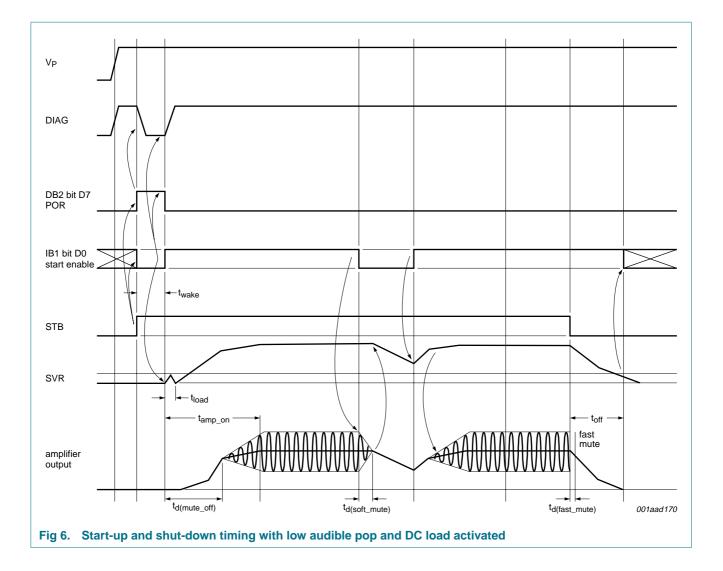

When the STB pin is switched HIGH the TDA8595 is put in operating condition and will perform a power-on reset, which results in a LOW-level DIAG pin. The TDA8595 will start up when instruction bit IB1[D0] is set. Bit D0 will also reset the 'power-on reset occurred' bit (DB2[D7]) and releases the DIAG pin.

The soft mute and soft mute can be activated via the  $l^2$ C-bus. The soft mute can be activated independently for the front channels (channel 1 and channel 3) and rear channels (channel 2 and channel 4), and mutes the audio in 20 ms. The fast mute activates the mute for all channels at the same time and mutes the audio in 0.1 ms. Releasing the mute after a fast mute will be by a soft un-mute of approximately 20 ms.

When the STB pin is switched to Standby mode and the amplifier has started, first the fast mute will be activated and then the amplifier will shut-down. For instance, during an engine start, it is possible to fully mute the amplifiers within 100  $\mu$ s by switching the STB pin to zero.

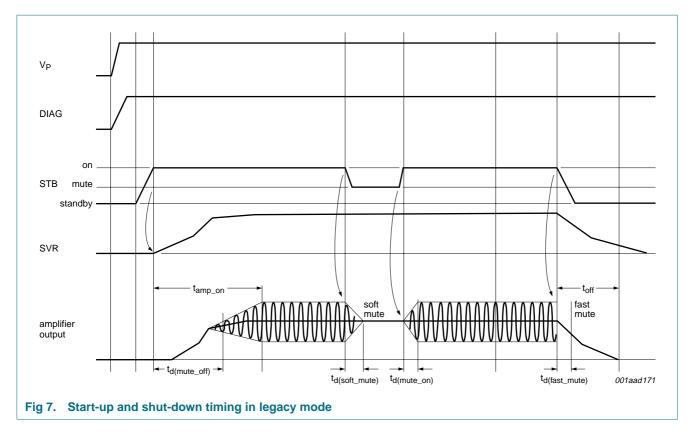

### 7.7.2 Legacy mode (pin ADSEL connected to ground)

The function of the STB pin will change from standby/operating to standby/mute/operating and the amplifier will start directly when the STB is put into mute or operating. Mute operating is controlled via an internal timer (20 ms) to minimize mute-on pops. When the STB pin is switched directly from operating to standby, first the fast mute will be activated (switching to mute within 100  $\mu$ s) and then the amplifier will shut-down.

### 7.8 Start-up and shut-down sequence

To prevent the amplifier producing switch-on or switch-off pop noise, the capacitor on the SVR pin is used for smooth start-up and shut-down. Increasing the value of the SVR capacitor will mean a longer start-up and shut-down time. The amplifier output voltage is charged to half the supply voltage minus 1.4 V in mute condition, independent of the I<sup>2</sup>C-bus mute settings in I<sup>2</sup>C-bus mode or pin STB voltage in legacy mode. The last 1.4 V, where the output will reach half the supply voltage, is used to release the mute if the I<sup>2</sup>C-bus bits (IB2[D2:D0] = 000) were set to mute-off (V<sub>STB</sub> > 6.5 V in legacy mode), or will stay in mute when the bits were set to mute (2.6 V < V<sub>STB</sub> < 4.5 V in legacy mode).

When the amplifier is switched off by pulling the STB pin LOW, the amplifier is first muted (fast mute) and then the capacitor on the SVR pin is discharged. With an SVR capacitor of 22  $\mu$ F the standby current is reached 1 second after the STB pin is switched to zero (see Figure 4, Figure 5, Figure 6 and Figure 7).

The start-up and shut-down pop can be further decreased by activating the low pop mode. When the low pop mode is enabled (IB2[D3] = 0), the output voltage rise from ground level during start-up will be slower (see Figure 6). This will decrease the pop even more but will increase the start-up time.

## **NXP Semiconductors**

# TDA8595

$I^2C\text{-bus}$  controlled  $4\times45$  W power amplifier

## **NXP Semiconductors**

# TDA8595

$I^2C\text{-bus}$  controlled  $4\times45$  W power amplifier

### **NXP Semiconductors**

# TDA8595

I<sup>2</sup>C-bus controlled  $4 \times 45$  W power amplifier

### 7.9 Power-on reset and supply voltage spikes

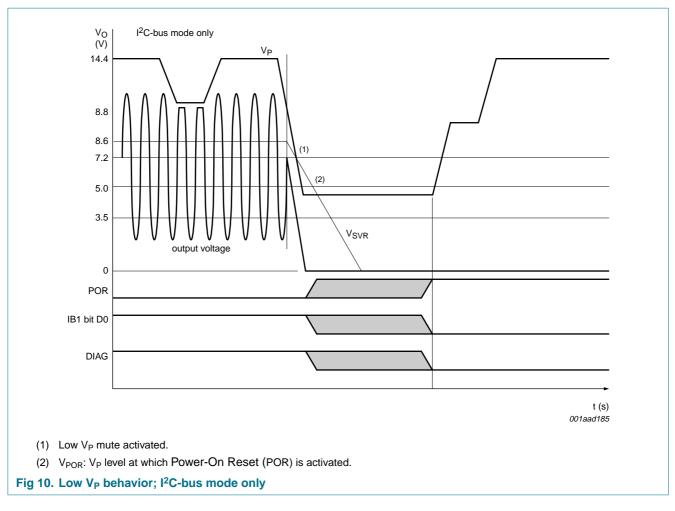

If in I<sup>2</sup>C-bus mode the supply voltage drops below 5 V (see Figure 10) the content of the I<sup>2</sup>C-bus latches cannot be guaranteed and the power-on reset will be activated. All latches are reset, the amplifier is switched off and the DIAG pin is pulled LOW to indicate that a power-on reset has occurred (see bit DB2[D7]). When bit IB1[D0] is set, the power-on flag is reset, the DIAG pin will be released and the amplifier will start-up.

In legacy mode a supply voltage drop below 5 V will switch off the amplifier and the DIAG pin will not be pulled LOW.

### 7.10 Engine start and low voltage operation

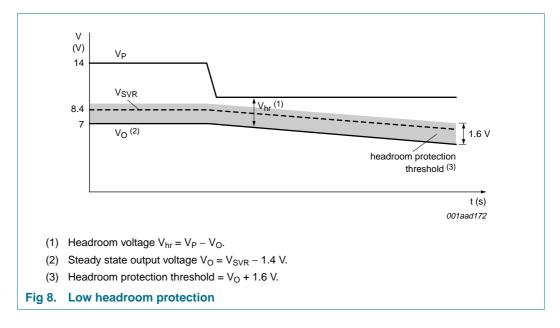

The DC output voltage of the amplifier (V<sub>O</sub>) is set to half of the supply voltage and is related to the voltage on the SVR pin (see Figure 8; V<sub>O</sub> = V<sub>SVR</sub> – 1.4 V). A capacitor is connected on the SVR pin to suppress the ripple on the power supply.

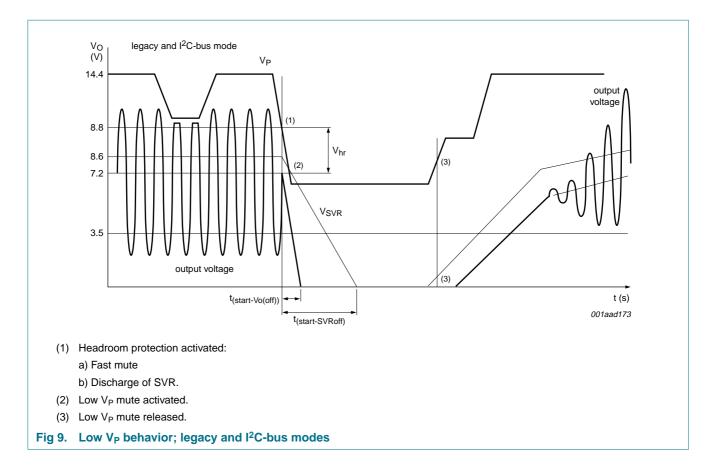

If the supply voltage drops, for instance, during an engine start, the output follows slowly due to the SVR capacitor. The headroom voltage is the voltage needed for good operation of the amplifier and is defined as  $V_{hr} = V_P - V_O$  (see Figure 8). If the headroom voltage becomes lower than the headroom protection threshold of 1.6 V, the headroom protection is activated to prevent pop noise at the output. This protection first activates the hard mute and then discharges the capacitors on the SVR and ACGND pins to generate more headroom for the amplifier (see Figure 9.)

When the SVR capacitor has discharged, the amplifier starts up again if the V<sub>P</sub> voltage is above the low V<sub>P</sub> mute threshold, typically 7.5 V. Below the low V<sub>P</sub> mute threshold, the outputs of the amplifier remain low. In I<sup>2</sup>C-bus mode, a supply voltage drop below V<sub>P(reset)</sub>, typically 5 V, results in setting bit DB2[D7]. The amplifiers will not start-up but wait for an I<sup>2</sup>C-bus command to start-up.

The amplifier prevents audio pops during engine start. To prevent pops on the output caused by the application during an engine start (for instance tuner regulator out of regulation), the STB pin can be made zero when an engine start is detected. The STB pin activates the fast mute and disturbances at the amplifier inputs are suppressed.

$I^2C\text{-bus}$  controlled  $4\times45$  W power amplifier

#### $I^2C\text{-bus}$ controlled $4\times45$ W power amplifier

### 7.11 Overvoltage and load dump protection

When the battery voltage  $V_P$  is higher than 22 V, the amplifier stage will be switched to high-impedance. The TDA8595 is protected against load dump voltage with supply voltage up to 50 V.

### 7.12 Thermal pre-warning and thermal protection

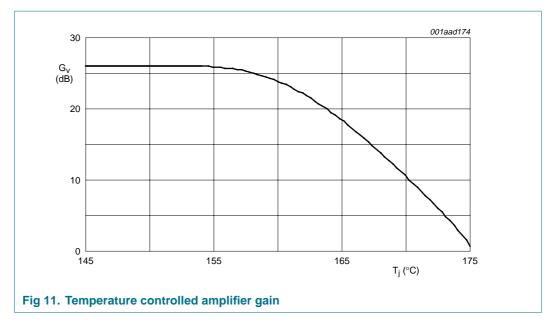

If the average junction temperature reaches a level that is adjustable via the l<sup>2</sup>C-bus, selected with bit IB3[D4], the pre-warning will be activated resulting in a LOW-level on pin DIAG (if selected) and can be read out via the l<sup>2</sup>C-bus. The default setting for the thermal pre-warning is IB3[D4] = 0, setting the warning level at 145 °C. In legacy mode the thermal pre-warning is set at 145 °C.

If the temperature increases further, the temperature controlled gain reduction will be activated for all four channels to reduce the output power (see Figure 11). If this does not reduce the average junction temperature, all four channels will be switched off at the absolute maximum temperature  $T_{off}$ , typical 175 °C.

#### I<sup>2</sup>C-bus controlled $4 \times 45$ W power amplifier

## 7.13 Diagnostics

Diagnostic information can be read via the I<sup>2</sup>C-bus, and can also be available on the DIAG pin or on the STB pin. The DIAG pin has both fixed information (power-on reset occurred, low battery and high battery) and, via the I<sup>2</sup>C-bus, selectable information (temperature, load fault and clip). This information will be seen at the DIAG pin as a logic OR. In case of a failure, the DIAG pin remains LOW and the microprocessor can read the failure information via the I<sup>2</sup>C-bus (the DIAG pin can be used as microprocessor interrupt to minimize I<sup>2</sup>C-bus traffic). When the failure is removed, the DIAG pin will be released.

To have full control over the clipping information, the STB pin can be programmed as a second clip detection pin. The clip detection level can be selected for all channels at once. It is possible to select whether the clip information is available on the DIAG pin or on the STB pin, for each channel separately. It is, for instance, possible to distinguish between clipping of the front and the rear channels.

Diagnostic information selection possibilities are shown in Table 4.

|                             | _                                                                                        |                            |                                          |

|-----------------------------|------------------------------------------------------------------------------------------|----------------------------|------------------------------------------|

| Diagnostic                  | I <sup>2</sup> C-bus mode                                                                | Legacy mode                |                                          |

| information                 | DIAG pin                                                                                 | STB pin                    | DIAG pin                                 |

| Power-On Reset<br>(POR)     | after power-on reset,<br>DIAG pin will remain<br>LOW until amplifier has<br>been started | no                         | no                                       |

| Low battery                 | yes                                                                                      | no                         | yes                                      |

| Clip detection              | can be enabled per channel                                                               | can be enabled per channel | yes, fixed level for all channels on 2 % |

| Temperature pre-<br>warning | can be enabled                                                                           | no                         | yes, pre-warning level<br>is 145 °C      |

| Short                       | can be enabled                                                                           | no                         | yes                                      |

#### Table 4. Diagnostic information availability

| Diagnostic                           | I <sup>2</sup> C-bus mode | Legacy mode |          |

|--------------------------------------|---------------------------|-------------|----------|

| information                          | DIAG pin                  | STB pin     | DIAG pin |

| Speaker protection (missing current) | can be enabled            | no          | yes      |

| Offset detection                     | no                        | no          | no       |

| Load detection                       | no                        | no          | no       |

| Overvoltage                          | yes                       | no          | yes      |

Table 4.

Diagnostic information availability ...continued

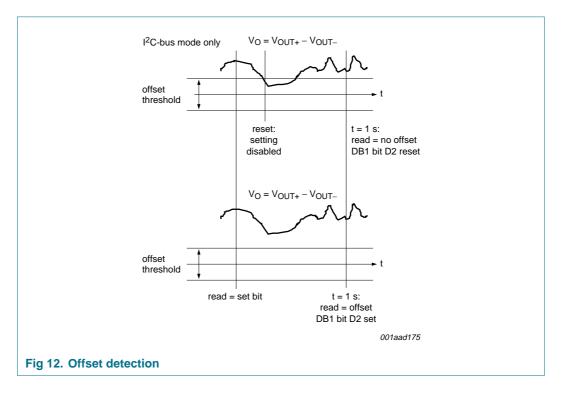

## 7.14 Offset detection

The offset detection can be performed with no input signal (for instance when the DSP is in mute after a start-up) or with an input signal. In I<sup>2</sup>C-bus mode, if an I<sup>2</sup>C-bus read of the output offset is performed, the I<sup>2</sup>C-bus latches DBx[D2] will be set. When the amplifier BTL output voltage is within a window with threshold of 1.75 V typical, the latches DBx[D2] are reset and setting is disabled. If, for instance, after one second an I<sup>2</sup>C-bus read is performed again and the offset bits are still set, the output has not crossed the offset threshold during the last second (see Figure 12). This can mean the applied frequency is below 1 Hz (one second I<sup>2</sup>C-bus read interval) or an output offset of more than 1.75 V is present.

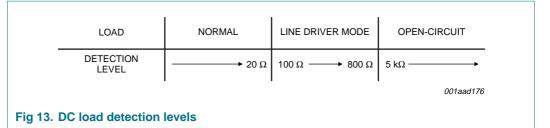

### 7.15 DC load detection

When the DC load detection is enabled with bit IB1[D1], an offset is slowly applied at the output of the amplifiers during the start-up cycle and the load currents are measured. Different load levels will be detected to differentiate between normal load, line driver load or open load (see Figure 13).

#### I<sup>2</sup>C-bus controlled $4 \times 45$ W power amplifier

If the amplifier is used as line driver and the external booster has an input impedance of more than 100  $\Omega$  and less than 800  $\Omega$  (DC-coupled), the DC load bits will contain DBx[D5:D4] = 10, independent of the gain setting (see Table 5).

#### Table 5.DC load detection

| DC load bits | Meaning (when IB1[D2] = 0) |                  |

|--------------|----------------------------|------------------|

| DBx[D5]      | DBx[D4]                    |                  |

| 0            | 0                          | normal load      |

| 1            | 0                          | line driver load |

| 1            | 1                          | open load        |

| 0            | 1                          | not valid        |

By reading the I<sup>2</sup>C-bus bits the microprocessor can determine, after the start-up of the amplifier, whether a speaker or an external booster is connected.

Depending on these bits, the amplifier gain can be selected, 26 dB for normal mode or 16 dB for line driver mode. If the gain select is performed when the amplifier is muted, the gain select will be pop free.

The DC load bits are combined with the AC load bits and are only valid when the AC load detection is disabled. When the AC load detection is enabled (IB1[D2] = 1), the bits DBx[D4] will show the content of the AC load detection. When the AC load detection is disabled again, bit DBx[D4] will show the content of the DC load measurement, which was stored during the AC load measurement. The AC load detection can only be performed after the amplifier has completed its start-up cycle and will not conflict with the DC load detection.

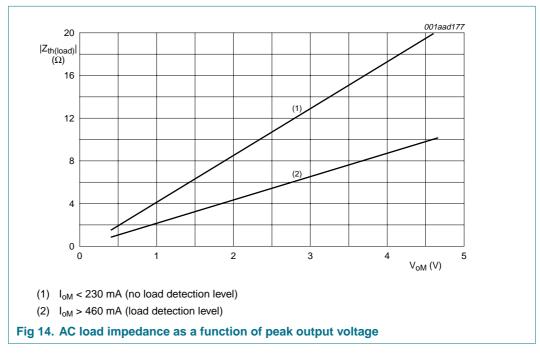

### 7.16 AC load detection

The AC load detection, enabled with IB1[D2] = 1, is used to detect if AC coupled speakers, for example tweeters, are connected correctly during assembly. The detection is audible because a sine wave of a certain frequency (e.g. 19 kHz) needs to be applied to the inputs of the amplifier. The output voltage over the load impedance will generate an amplifier current. If the amplifier peak current triggers a 460 mA (peak) threshold detector three times, the AC load detection bit will be set. A three 'threshold cross' counter is used to prevent false AC load detection when switching the input signal on or off.

An AC coupled speaker will reduce the impedance at the output of the amplifier in a certain frequency band. The presence of an AC coupled speaker can be determined using 460 mA (peak) and 230 mA (peak) threshold current detection. For instance, at an output voltage of 2 V (peak) the total impedance must be less than 4  $\Omega$  to detect the AC coupled load, or more than 8  $\Omega$  to guarantee only a DC connection is detected.

The interpretation of line driver and normal mode DC load bit setting for AC load detection is shown in <u>Table 6</u>.

| Table 6. | AC load detection |                            |

|----------|-------------------|----------------------------|

| DBx[D4]  |                   | Meaning (when IB1[D2] = 1) |

| 0        |                   | no AC load detected        |

| 1        |                   | AC load detected           |

When bit IB1[D2] = 1, the AC load detection is enabled. The AC load detection can only be performed after the amplifier has completed its start-up cycle and will not conflict with the DC load detection.

### 7.17 I<sup>2</sup>C-bus diagnostic readout

The diagnostic information of the amplifier can be read via the I<sup>2</sup>C-bus. The I<sup>2</sup>C-bus bits are set on a failure and will be reset with the I<sup>2</sup>C-bus read command. Even when the failure is removed, the microprocessor will know what was wrong by reading the I<sup>2</sup>C-bus. The consequence of this procedure is that old information is read during the I<sup>2</sup>C-bus readout. Most actual information will be gathered after two successive read commands.

The DIAG pin will give actual diagnostic information (when selected). When a failure is removed, the DIAG pin will be released instantly, independently of the I<sup>2</sup>C-bus latches.

### $I^2C\text{-bus}$ controlled $4\times45$ W power amplifier

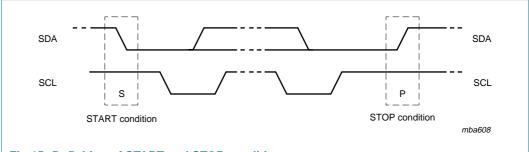

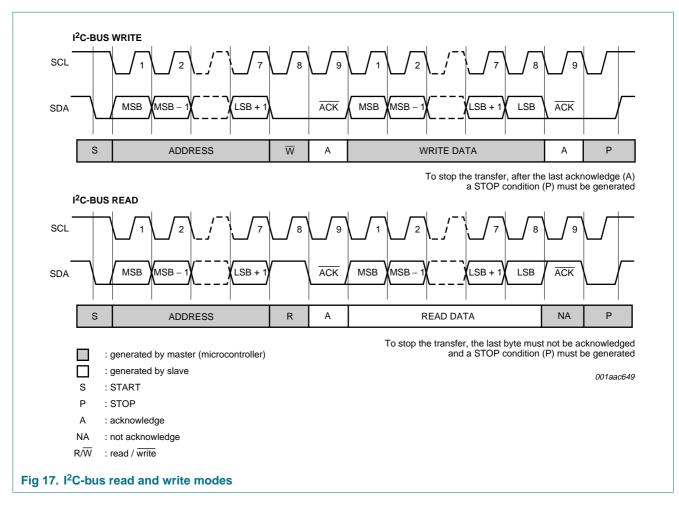

# 8. I<sup>2</sup>C-bus specification

| Table 7. TDA8595 hardware address select |     |    |    |    |    |    |                      |                       |

|------------------------------------------|-----|----|----|----|----|----|----------------------|-----------------------|

| Pin ADSEL                                | A6  | A5 | A4 | A3 | A2 | A1 | A0                   | R/W                   |

| Open                                     | 1   | 1  | 0  | 1  | 1  | 0  | 0                    | 0 = write to TDA8595  |

|                                          |     |    |    |    |    |    |                      | 1 = read from TDA8595 |

| 51 k $\Omega$ to ground                  | 1   | 1  | 0  | 1  | 1  | 0  | 1                    | 0 = write to TDA8595  |

|                                          |     |    |    |    |    |    |                      | 1 = read from TDA8595 |

| 10 k $\Omega$ to ground                  | 1 1 | 0  | 1  | 1  | 1  | 1  | 0 = write to TDA8595 |                       |

|                                          |     |    |    |    |    |    |                      | 1 = read from TDA8595 |

#### $I^2C\text{-bus}$ controlled $4\times45$ W power amplifier

### 8.1 Instruction bytes

I<sup>2</sup>C-bus mode:

- If  $R/\overline{W}$  bit = 0, the TDA8595 expects three instruction bytes; IB1, IB2 and IB3

- After a power-on reset, all instruction bits are set to zero

Legacy mode:

• All bits equal to zero define the setting, with the exception of bit IB1[D0] which is ignored (see Table 8).

| Table 8. | Instruction byte IB1                          |

|----------|-----------------------------------------------|

| Bit      | Description                                   |

| D7       | don't care                                    |

| D6       | channel 3 clip information on DIAG or STB pin |

|          | 0 = clip information on DIAG pin              |

|          | 1 = clip information on STB pin               |

| D5       | channel 1 clip information on DIAG or STB pin |

|          | 0 = clip information on DIAG pin              |

|          | 1 = clip information on STB pin               |

#### $I^2C\text{-bus}$ controlled $4\times45$ W power amplifier

|     | Instruction byte IB1continued                                                                        |

|-----|------------------------------------------------------------------------------------------------------|

| Bit | Description                                                                                          |

| D4  | channel 4 clip information on DIAG or STB pin                                                        |

|     | 0 = clip information on DIAG pin                                                                     |

|     | 1 = clip information on STB pin                                                                      |

| D3  | channel 2 clip information on DIAG or STB pin                                                        |

|     | 0 = clip information on DIAG pin                                                                     |

|     | 1 = clip information on STB pin                                                                      |

| D2  | AC load detection enable:                                                                            |

|     | 0 = AC load detection disabled                                                                       |

|     | 1 = AC load detection enabled; bit DBx[D4] not available for DC load detection                       |

| D1  | DC load detection enable:                                                                            |

|     | 0 = DC load detection disabled                                                                       |

|     | 1 = DC load detection enabled                                                                        |

| D0  | amplifier start enable                                                                               |

|     | 0 = amplifier not enabled, DIAG pin will remain LOW                                                  |

|     | 1 = amplifier will start up, power-on occurred (DB2[D7] will be reset) and DIAG pin will be released |

#### Table 9.Instruction byte IB2

| Bit       | Description                                                  |  |  |  |  |  |

|-----------|--------------------------------------------------------------|--|--|--|--|--|

| D7 and D6 | clip detection level                                         |  |  |  |  |  |

|           | 00 = clip detection level 2 %                                |  |  |  |  |  |

|           | 01 = clip detection level 5 %                                |  |  |  |  |  |

|           | 10 = clip detection level 10 %                               |  |  |  |  |  |

|           | 11 = clip detection level disabled                           |  |  |  |  |  |

| D5        | temperature information on DIAG pin                          |  |  |  |  |  |

|           | 0 = temperature information on DIAG pin                      |  |  |  |  |  |

|           | 1 = no temperature information on DIAG pin                   |  |  |  |  |  |

| D4        | load fault information (shorts, missing current) on DIAG pin |  |  |  |  |  |

|           | 0 = fault information on DIAG pin                            |  |  |  |  |  |

|           | 1 = no fault information on DIAG pin                         |  |  |  |  |  |

| D3        | low pop (slow start) enable                                  |  |  |  |  |  |

|           | 0 = low pop enabled                                          |  |  |  |  |  |

|           | 1 = low pop disabled                                         |  |  |  |  |  |

| D2        | soft mute channel 1 and channel 3 (mute delay 20 ms)         |  |  |  |  |  |

|           | 0 = no mute                                                  |  |  |  |  |  |

|           | 1 = mute                                                     |  |  |  |  |  |

| D1        | soft mute channel 2 and channel 4 (mute delay 20 ms)         |  |  |  |  |  |

|           | 0 = no mute                                                  |  |  |  |  |  |

|           | 1 = mute                                                     |  |  |  |  |  |

| Table 9.  | Instruction byte IB2continued                             |

|-----------|-----------------------------------------------------------|

| Bit       | Description                                               |

| D0        | fast mute all amplifier channels (mute delay 100 $\mu$ s) |

|           | 0 = no mute                                               |

|           | 1 = mute                                                  |

|           |                                                           |

| Table 10. | Instruction byte IB3                                      |

| Bit       | Description                                               |

| D7        | don't care                                                |

| D6        | amplifier channel 1 and channel 3 gain select             |

|           | 0 = 26 dB                                                 |

|           | 1 = 16 dB                                                 |

| D5        | amplifier channel 2 and channel 4 gain select             |

|           | 0 = 26 dB                                                 |

|           | 1 = 16 dB                                                 |

| D4        | temperature pre-warning level                             |

|           | 0 = warning level on 145 °C                               |

|           | 1 = warning level on 122 °C                               |

| D3        | disable channel 3                                         |

|           | 0 = channel 3 enabled                                     |

|           | 1 = channel 3 disabled                                    |

| D2        | disable channel 1                                         |

|           | 0 = channel 1 enabled                                     |

|           | 1 = channel 1 disabled                                    |

| D1        | disable channel 4                                         |

|           | 0 = channel 4 enabled                                     |

|           | 1 = channel 4 disabled                                    |

| D0        | disable channel 2                                         |

|           | 0 = channel 2 enabled                                     |

|           | 1 = channel 2 disabled                                    |

## 8.2 Data bytes

I<sup>2</sup>C-bus mode:

- If R/W = 1, the TDA8595 sends four data bytes to the microprocessor: DB1, DB2, DB3 and DB4

- All bits except DB1[D7] and DB3[D7] are latched

- All bits except DBx[D4] and DBx[D5] are reset after a read operation. Bit DBx[D2] is set after a read operation, see <u>Section 7.14</u>

- For explanation of AC and DC load detection bits, see Section 7.15 and Section 7.16

### $I^2C\text{-bus}$ controlled $4\times45$ W power amplifier

| Bit       | Description                                                                                              |

|-----------|----------------------------------------------------------------------------------------------------------|

| D7        | temperature pre-warning                                                                                  |

|           | 0 = no warning                                                                                           |

|           | 1 = junction temperature too high                                                                        |

| D6        | speaker fault channel 2 (missing current)                                                                |

|           | 0 = no missing current                                                                                   |

|           | 1 = missing current                                                                                      |

| D5 and D4 | channel 2 DC load or AC load detection                                                                   |

|           | if bit IB1[D2] = 1, AC load detection is enabled, bit D5 is don't care, bit D4 has the following meaning |

|           | 0 = no AC load                                                                                           |

|           | 1 = AC load detected                                                                                     |

|           | if bit IB1[D2] = 0, AC load detection is disabled, bits D5 and D4 are available for DC load detection    |

|           | 00 = normal load                                                                                         |

|           | 01 = not valid                                                                                           |

|           | 10 = line driver load                                                                                    |

|           | 11 = open load                                                                                           |

| D3        | channel 2 shorted load                                                                                   |

|           | 0 = not shorted load                                                                                     |

|           | 1 = shorted load                                                                                         |

| D2        | channel 2 output offset                                                                                  |

|           | 0 = no output offset                                                                                     |

|           | 1 = output offset                                                                                        |

| D1        | channel 2 short to V <sub>P</sub>                                                                        |

|           | $0 = no short to V_P$                                                                                    |

|           | $1 = \text{short to } V_P$                                                                               |

| D0        | channel 2 short to ground                                                                                |

|           | 0 = no short to ground                                                                                   |

|           | 1 = short to ground                                                                                      |

#### Table 12.Data byte DB2

| Bit | Description                                    |

|-----|------------------------------------------------|

| D7  | power-on reset and amplifier status            |

|     | 0 = amplifier on                               |

|     | 1 = power-on reset has occurred; amplifier off |

| D6  | speaker fault channel 4 (missing current)      |

|     | 0 = no missing current                         |

|     | 1 = missing current                            |

### $I^2C\text{-bus}$ controlled $4\times45$ W power amplifier

| Bit       | Description                                                                                              |

|-----------|----------------------------------------------------------------------------------------------------------|

| D5 and D4 | channel 4 DC load or AC load detection                                                                   |

|           | if bit IB1[D2] = 1, AC load detection is enabled, bit D5 is don't care, bit D4 has the following meaning |

|           | 0 = no AC load                                                                                           |

|           | 1 = AC load detected                                                                                     |

|           | if bit IB1[D2] = 0, AC load detection is disabled, bits D5 and D4 are available for DC load detection    |

|           | 00 = normal load                                                                                         |

|           | 01 = not valid                                                                                           |

|           | 10 = line driver load                                                                                    |

|           | 11 = open load                                                                                           |

| D3        | channel 4 shorted load                                                                                   |

|           | 0 = not shorted load                                                                                     |

|           | 1 = shorted load                                                                                         |

| D2        | channel 4 output offset                                                                                  |

|           | 0 = no output offset                                                                                     |

|           | 1 = output offset                                                                                        |

| D1        | channel 4 short to V <sub>P</sub>                                                                        |

|           | $0 = no short to V_P$                                                                                    |

|           | $1 = $ short to $V_P$                                                                                    |

| D0        | channel 4 short to ground                                                                                |

|           | 0 = no short to ground                                                                                   |

|           | 1 = short to ground                                                                                      |

#### Table 13. Data byte DB3

|     | -                                         |

|-----|-------------------------------------------|

| Bit | Description                               |

| D7  | maximum temperature protection            |

|     | 0 = no protection                         |

|     | 1 = maximum temperature protection        |

| D6  | speaker fault channel 1 (missing current) |

|     | 0 = no missing current                    |

|     | 1 - missing current                       |

1 = missing current

### $I^2C\text{-bus}$ controlled $4\times45$ W power amplifier

| Bit       | Data byte DB3continued                                                                                   |

|-----------|----------------------------------------------------------------------------------------------------------|

|           | Description                                                                                              |

| D5 and D4 | channel 1 DC load or AC load detection                                                                   |

|           | if bit IB1[D2] = 1, AC load detection is enabled, bit D5 is don't care, bit D4 has the following meaning |

|           | 0 = no AC load                                                                                           |

|           | 1 = AC load detected                                                                                     |

|           | if bit IB1[D2] = 0, AC load detection is disabled, bits D5 and D4 are available for DC load detection    |

|           | 00 = normal load                                                                                         |

|           | 01 = not valid                                                                                           |

|           | 10 = line driver load                                                                                    |

|           | 11 = open load                                                                                           |

| D3        | channel 1 shorted load                                                                                   |

|           | 0 = not shorted load                                                                                     |

|           | 1 = shorted load                                                                                         |

| D2        | channel 1 output offset                                                                                  |

|           | 0 = no output offset                                                                                     |

|           | 1 = output offset                                                                                        |

| D1        | channel 1 short to V <sub>P</sub>                                                                        |

|           | $0 = no short to V_P$                                                                                    |

|           | $1 = \text{short to } V_P$                                                                               |

| D0        | channel 1 short to ground                                                                                |

|           | 0 = no short to ground                                                                                   |

|           | 1 = short to ground                                                                                      |

#### Table 14. Data byte DB4

| Description                                                                                              |

|----------------------------------------------------------------------------------------------------------|

| reserved                                                                                                 |

| speaker fault channel 3 (missing current)                                                                |

| 0 = no missing current                                                                                   |

| 1 = missing current                                                                                      |

| channel 3 DC load or AC load detection                                                                   |

| if bit IB1[D2] = 1, AC load detection is enabled, bit D5 is don't care, bit D4 has the following meaning |

| 0 = no AC load                                                                                           |

| 1 = AC load detected                                                                                     |

| if bit IB1[D2] = 0, AC load detection is disabled, bits D5 and D4 are available for DC load detection    |

| 00 = normal load                                                                                         |

| 01 = not valid                                                                                           |

| 10 = line driver load                                                                                    |

| 11 = open load                                                                                           |

|                                                                                                          |

### $I^2C\text{-bus}$ controlled $4\times45$ W power amplifier

| Table 14. | Data byte DB4 continued           |  |

|-----------|-----------------------------------|--|

| Bit       | Description                       |  |

| D3        | channel 3 shorted load            |  |

|           | 0 = not shorted load              |  |

|           | 1 = shorted load                  |  |

| D2        | channel 3 output offset           |  |

|           | 0 = no output offset              |  |

|           | 1 = output offset                 |  |

| D1        | channel 3 short to V <sub>P</sub> |  |

|           | $0 = no short to V_P$             |  |

|           | $1 = $ short to $V_P$             |  |

| D0        | channel 3 short to ground         |  |

|           | 0 = no short to ground            |  |

|           | 1 = short to ground               |  |

# 9. Limiting values

#### Table 15. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol              | Parameter                                     | Conditions                                                               | Min | Max            | Unit |

|---------------------|-----------------------------------------------|--------------------------------------------------------------------------|-----|----------------|------|

| V <sub>P</sub>      | supply voltage                                | operating                                                                | -   | 18             | V    |

|                     |                                               | non operating                                                            | -1  | +50            | V    |

|                     |                                               | load dump protection;<br>duration 50 ms, rise<br>time > 2.5 ms           | -   | 50             | V    |

| V <sub>P(r)</sub>   | reverse supply voltage                        | 10 minutes maximum                                                       | -   | -2             | V    |

| I <sub>OSM</sub>    | non-repetitive peak<br>output current         |                                                                          | -   | 13             | А    |

| I <sub>ORM</sub>    | repetitive peak output<br>current             |                                                                          | -   | 8              | А    |

| T <sub>j(max)</sub> | maximum junction temperature                  |                                                                          | -   | 150            | °C   |

| T <sub>stg</sub>    | storage temperature                           |                                                                          | -55 | +150           | °C   |

| T <sub>amb</sub>    | ambient temperature                           |                                                                          | -40 | +105           | °C   |

| V <sub>(prot)</sub> | protection voltage                            | AC and DC short-circuit<br>voltage of output pins and<br>across the load | -   | V <sub>P</sub> | V    |

| V <sub>x</sub>      | voltage on pin x                              |                                                                          |     |                |      |

|                     | SCL and SDA                                   |                                                                          | 0   | 6.5            | V    |

|                     | IN1, IN2, IN3, IN4,<br>SVR, ACGND and<br>DIAG |                                                                          | 0   | 13             | V    |

|                     | STB                                           |                                                                          | 0   | 24             | V    |

#### $I^2C\text{-bus}$ controlled $4\times45$ W power amplifier

| Symbol           | Parameter                       | Conditions                                                                                    | Min | Max  | Unit |

|------------------|---------------------------------|-----------------------------------------------------------------------------------------------|-----|------|------|

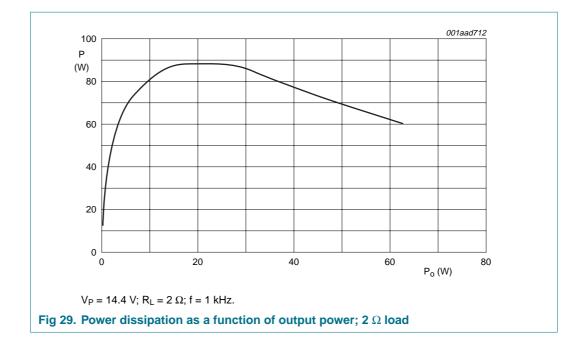

| P <sub>tot</sub> | total power dissipation         | T <sub>case</sub> = 70 °C                                                                     | -   | 80   | W    |

| V <sub>esd</sub> | electrostatic discharge voltage | human body model;<br>C = 100 pF; R <sub>s</sub> = 1.5 k $\Omega$                              | -   | 2000 | V    |

|                  |                                 | machine model;<br>C = 200 pF; R <sub>s</sub> = 10 $\Omega$ ;<br>L <sub>s</sub> = 0.75 $\mu$ H | -   | 200  | V    |

#### Table 15. Limiting values ...continued

## **10. Thermal characteristics**

| Table 16.            | Thermal characteristics                     |             |     |      |

|----------------------|---------------------------------------------|-------------|-----|------|

| Symbol               | Parameter                                   | Conditions  | Тур | Unit |

| TDA8595J             | ; TDA8595SD                                 |             |     |      |

| R <sub>th(j-c)</sub> | thermal resistance from junction to case    |             | 1   | K/W  |

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | in free air | 40  | K/W  |

| TDA8595T             | н                                           |             |     |      |

| R <sub>th(j-c)</sub> | thermal resistance from junction to case    |             | 1   | K/W  |

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | in free air | 40  | K/W  |

|                      |                                             |             |     |      |

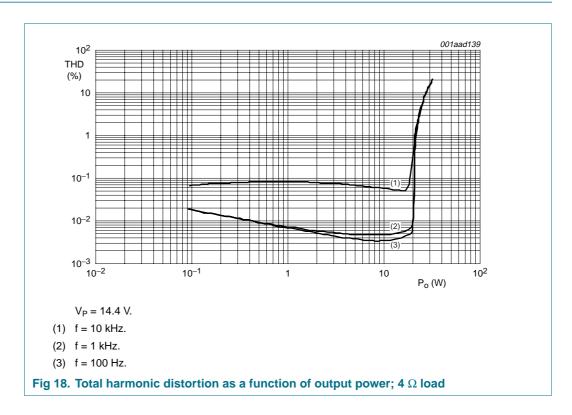

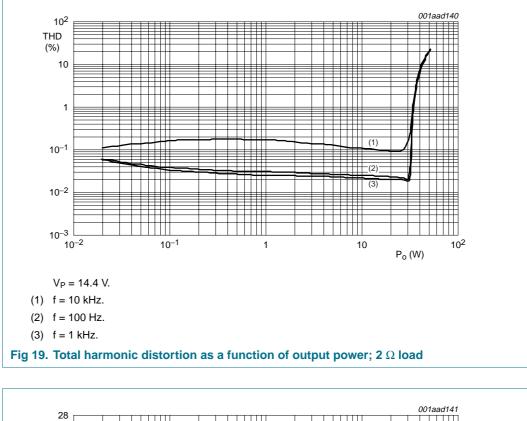

## **11. Characteristics**

#### Table 17. Characteristics

Refer to test circuit (see Figure 30) at  $V_P = V_{P1} = V_{P2} = 14.4 V$ ;  $R_L = 4 \Omega$ ; f = 1 kHz;  $R_S = 0 \Omega$ ; normal mode; unless otherwise specified. Tested at  $T_{amb} = 25 \degree C$ ; guaranteed for  $T_{amb} = -40 \degree C$  to  $+105 \degree C$ .

| Symbol                    | Parameter                                | Conditions                                          |            | Min | Тур  | Max | Unit |

|---------------------------|------------------------------------------|-----------------------------------------------------|------------|-----|------|-----|------|

| Supply voltag             | je behavior                              |                                                     |            |     |      |     |      |

| VP                        | supply voltage                           | $R_L = 4 \Omega$                                    |            | 8   | 14.4 | 18  | V    |

|                           |                                          | $R_L = 2 \Omega$                                    | <u>[1]</u> | 8   | 14.4 | 16  | V    |

| lq                        | quiescent current                        | no load                                             |            | -   | 270  | 400 | mA   |

| I <sub>stb</sub>          | standby current                          | $V_{STB} = 0.4 V$                                   |            | -   | 4    | 15  | μΑ   |

| Vo                        | output voltage                           |                                                     |            | 6.7 | 7    | 7.2 | V    |

| V <sub>P(low)(mute)</sub> | low supply voltage mute                  | with rising supply voltage                          |            | 6.9 | 7.5  | 8   | V    |

|                           |                                          | with falling supply voltage                         |            | 6.3 | 6.8  | 7.4 | V    |

| $\Delta V_{P(low)(mute)}$ | low supply voltage mute hysteresis       |                                                     |            | 0.1 | 0.7  | 1   | V    |

| V <sub>th(ovp)</sub>      | overvoltage protection threshold voltage |                                                     |            | 18  | 20   | 22  | V    |

| V <sub>hr</sub>           | headroom voltage                         | when headroom protection is activated; see Figure 8 |            | 1.1 | 1.6  | 2.0 | V    |

| V <sub>POR</sub>          | power-on reset voltage                   | see Figure 9                                        |            | 4.1 | 5.0  | 5.8 | V    |

| V <sub>O(offset)</sub>    | output offset voltage                    | amplifier on                                        |            | -95 | 0    | +95 | mV   |

|                           |                                          | amplifier mute                                      |            | -25 | 0    | +25 | mV   |

|                           |                                          | line driver mode                                    |            | -40 | 0    | +40 | mV   |

### $I^2C\text{-}bus$ controlled $4\times45$ W power amplifier

#### Table 17. Characteristics ...continued

Refer to test circuit (see Figure 30) at  $V_P = V_{P1} = V_{P2} = 14.4 \text{ V}$ ;  $R_L = 4 \Omega$ ; f = 1 kHz;  $R_S = 0 \Omega$ ; normal mode; unless otherwise specified. Tested at  $T_{amb} = 25 \degree C$ ; guaranteed for  $T_{amb} = -40 \degree C$  to  $+105 \degree C$ .

| Symbol                   | Parameter                            | Conditions                                                                                                                                                                                                                                                                       | Min | Тур | Max             | Unit             |

|--------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----------------|------------------|

| R <sub>L(tol)</sub>      | load resistance tolerance            | $V_P \le 18 V$                                                                                                                                                                                                                                                                   | 3.2 | 4   | -               | Ω                |

|                          |                                      | $V_P \le 16 V$                                                                                                                                                                                                                                                                   | 1.6 | 2   | -               | Ω                |

| Mode select              | t and second clip detection:         | oin STB                                                                                                                                                                                                                                                                          |     |     |                 |                  |

| V <sub>STB</sub>         | voltage on pin STB                   | Standby mode selected                                                                                                                                                                                                                                                            |     |     |                 |                  |

|                          |                                      | I <sup>2</sup> C-bus mode                                                                                                                                                                                                                                                        | -   | -   | 1               | V                |

|                          |                                      | legacy mode                                                                                                                                                                                                                                                                      | -   | -   | 1               | V                |

|                          |                                      | mute selected                                                                                                                                                                                                                                                                    |     |     |                 |                  |

|                          |                                      | legacy mode                                                                                                                                                                                                                                                                      | 2.5 | -   | 4.5             | V                |

|                          |                                      | Operating mode selected                                                                                                                                                                                                                                                          |     |     |                 |                  |

|                          |                                      | I <sup>2</sup> C-bus mode                                                                                                                                                                                                                                                        | 2.5 | -   | VP              | V                |

|                          |                                      | legacy mode                                                                                                                                                                                                                                                                      | 6.5 | -   | VP              | V                |

|                          |                                      | low voltage on pin STB when pulled down during clipping                                                                                                                                                                                                                          | [2] |     |                 |                  |

|                          |                                      | I <sub>STB</sub> = 150 μA                                                                                                                                                                                                                                                        | 5.6 | -   | 6.1             | V                |

|                          |                                      | I <sub>STB</sub> = 500 μA                                                                                                                                                                                                                                                        | 6.1 | -   | 7.2             | V                |