# INTEGRATED CIRCUITS

# DATA SHEET

For a complete data sheet, please also download:

• The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications

# **74HC/HCT40105**4-bit x 16-word FIFO register

Product specification Supersedes data of December 1990 File under Integrated Circuits, IC06

# 4-bit x 16-word FIFO register

# 74HC/HCT40105

#### **FEATURES**

- Independent asynchronous inputs and outputs

- · Expandable in either direction

- · Reset capability

- · Status indicators on inputs and outputs

- · 3-state outputs

- · Output capability: standard

- I<sub>CC</sub> category: MSI

#### **GENERAL DESCRIPTION**

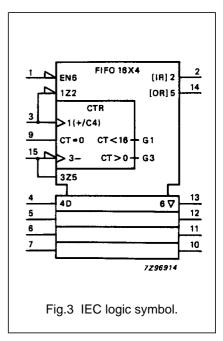

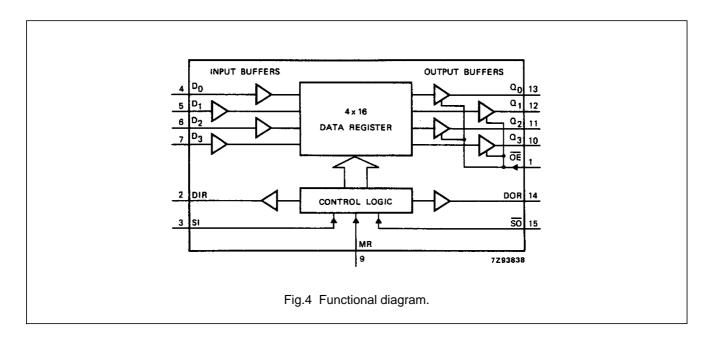

The 74HC/HCT40105 are high-speed Si-gate CMOS devices and are pin compatible with the "40105" of the "4000B" series. They are specified in compliance with JEDEC standard no. 7A.

The 74HC/HCT40105 are first-in/first-out (FIFO) "elastic" storage registers that can store sixteen 4-bit words. The "40105" is capable of handling input and output data at

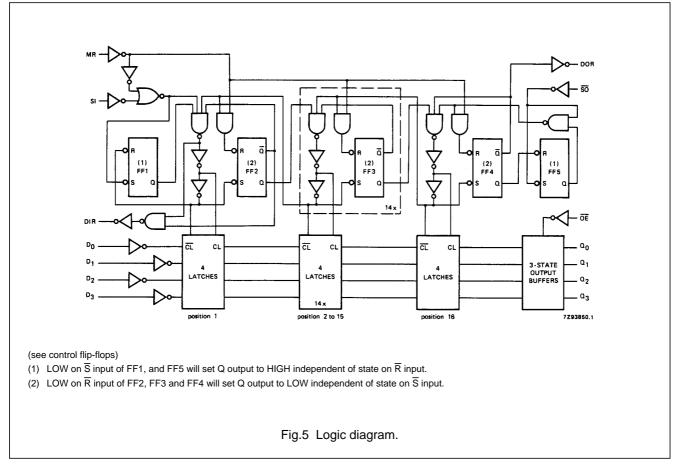

different shifting rates. This feature makes it particularly useful as a buffer between asynchronous systems. Each word position in the register is clocked by a control flip-flop, which stores a marker bit. A "1" signifies that the position's data is filled and a "0" denotes a vacancy in that position. The control flip-flop detects the state of the preceding flip-flop and communicates its own status to the succeeding flip-flop. When a control flip-flop is in the "0" state and sees a "1" in the preceding flip-flop, it generates a clock pulse that transfers data from the preceding four data latches into its own four data latches and resets the preceding flip-flop to "0". The first and last control flip-flops have buffered outputs. Since all empty locations "bubble" automatically to the input end, and all valid data ripples through to the output end, the status of the first control flip-flop (data-in ready output - DIR) indicates if the FIFO is full, and the status of the last flip-flop (data-out ready output - DOR) indicates if the FIFO contains data. As the earliest data is removed from the bottom of the data stack (output end), all data entered later will automatically ripple toward the output.

### **QUICK REFERENCE DATA**

$GND = 0 V; T_{amb} = 25 °C; t_r = t_f = 6 ns$

| CVMDOL                              | PARAMETER                                 | CONDITIONS                                    | TY  | YP. | LINUT |

|-------------------------------------|-------------------------------------------|-----------------------------------------------|-----|-----|-------|

| SYMBOL                              | PARAMETER                                 | CONDITIONS                                    | нс  | нст | UNIT  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay                         | C <sub>L</sub> = 15 pF; V <sub>CC</sub> = 5 V |     |     |       |

|                                     | MR to DIR, DOR                            |                                               | 16  | 15  | ns    |

|                                     | SO to Q <sub>n</sub>                      |                                               | 37  | 35  | ns    |

| t <sub>PHL</sub>                    | propagation delay                         |                                               |     |     |       |

|                                     | SI to DIR                                 |                                               | 16  | 18  | ns    |

|                                     | SO to DOR                                 |                                               | 17  | 18  | ns    |

| f <sub>max</sub>                    | maximum clock frequency                   |                                               | 33  | 31  | MHz   |

| C <sub>I</sub>                      | input capacitance                         |                                               | 3.5 | 3.5 | pF    |

| C <sub>PD</sub>                     | power dissipation capacitance per package | notes 1 and 2                                 | 134 | 145 | pF    |

#### **Notes**

1.  $C_{PD}$  is used to determine the dynamic power dissipation ( $P_D$  in  $\mu W$ ):

$P_D = C_{PD} \times V_{CC}^2 \times f_i + \sum (C_L \times V_{CC}^2 \times f_o)$  where:

$f_i$  = input frequency in MHz.

$f_0$  = output frequency in MHz.

$\sum (C_L \times V_{CC}^2 \times f_0) = \text{sum of outputs}$

C<sub>I</sub> = output load capacitance in pF

V<sub>CC</sub> = supply voltage in V

2. For HC the condition is  $V_I$  = GND to  $V_{CC}$ For HCT the condition is  $V_I$  = GND to  $V_{CC}$  – 1.5

# 4-bit x 16-word FIFO register

# 74HC/HCT40105

## **ORDERING INFORMATION**

| TYPE NUMBER    |         | PACKAGE                                                                |          |  |  |  |  |  |  |  |  |

|----------------|---------|------------------------------------------------------------------------|----------|--|--|--|--|--|--|--|--|

| I TPE NUMBER   | NAME    | DESCRIPTION                                                            | VERSION  |  |  |  |  |  |  |  |  |

| 74HC(T)40105N  | DIP16   | plastic dual in-line package; 16 leads (300 mil); long body            | SOT38-1  |  |  |  |  |  |  |  |  |

| 74HC(T)40105D  | SO16    | plastic small outline package; 16 leads; body width 3.9 mm             | SOT109-1 |  |  |  |  |  |  |  |  |

| 74HC(T)40105DB | SSOP16  | plastic shrink small outline package; 16 leads; body width 5.3 mm      | SOT338-1 |  |  |  |  |  |  |  |  |

| 74HC(T)40105PW | TSSOP16 | plastic thin shrink small outline package; 16 leads; body width 4.4 mm | SOT403-1 |  |  |  |  |  |  |  |  |

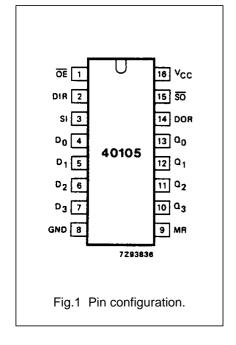

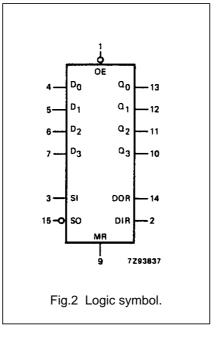

# **PIN DESCRIPTION**

| PIN NO.        | SYMBOL                           | NAME AND FUNCTION                             |

|----------------|----------------------------------|-----------------------------------------------|

| 1              | ŌĒ                               | output enable input (active LOW)              |

| 2              | DIR                              | data-in ready output                          |

| 3              | SI                               | shift-in input (LOW-to-HIGH, edge-triggered)  |

| 4, 5, 6, 7     | D <sub>0</sub> to D <sub>3</sub> | parallel data inputs                          |

| 8              | GND                              | ground (0 V)                                  |

| 9              | MR                               | asynchronous master reset input (active HIGH) |

| 13, 12, 11, 10 | Q <sub>0</sub> to Q <sub>3</sub> | 3-state data outputs                          |

| 14             | DOR                              | data-out ready output                         |

| 15             | SO                               | shift-out input (HIGH-to-LOW, edge-triggered) |

| 16             | V <sub>CC</sub>                  | positive supply voltage                       |

# 4-bit x 16-word FIFO register

# 74HC/HCT40105

#### INPUT AND OUTPUTS

#### Data inputs (D<sub>0</sub> to D<sub>3</sub>)

As there is no weighting of the inputs, any input can be assigned as the MSB. The size of the FIFO memory can be reduced from the  $4\times16$  configuration, i.e.  $3\times16$ , down to  $1\times16$ , by tying unused data input pins to  $V_{CC}$  or GND.

#### Data outputs (Q<sub>0</sub> to Q<sub>3</sub>)

As there is no weighting of the outputs, any output can be assigned as the MSB. The size of the FIFO memory can be reduced from the  $4\times16$  configuration as described for data inputs. In a reduced format, the unused data outputs pins must be left open circuit.

## Master-reset (MR)

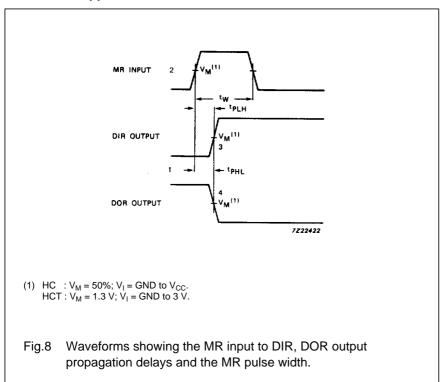

When MR is HIGH, the control functions within the FIFO are cleared, and date content is declared invalid. The data-in ready (DIR) flag is set HIGH and the data-out-ready (DOR) flag is set LOW. The output stage remains in the state of the last word that was shifted out, or in the random state existing at power-up.

## Status flag outputs (DIR, DOR)

Indication of the status of the FIFO is given by two status flags, data-in-ready (DIR) and data-out-ready (DOR):

DIR = HIGH indicates the input stage is empty and ready to accept valid data;

DIR = LOW indicates that the FIFO is full or that a previous shift-in operation is not complete (busy);

DOR = HIGH assures valid data is present at the outputs  $Q_0$  to  $Q_3$  (does not indicate that new data is awaiting transfer into the output stage);

DOR = LOW indicates the output stage is busy or there is no valid data.

## Shift-in control (SI)

Data is loaded into the input stage on a LOW-to-HIGH transition of SI. It also triggers an automatic data transfer process (ripple through). If SI is held HIGH during reset, data will be loaded at the falling edge of the MR signal.

## Shift-out control (SO)

A HIGH-to-LOW transition of SO causes the DOR flags to go LOW. A HIGH-to-LOW transition of SO causes upstream data to move into the output stage, and empty locations to move towards the input stage (bubble-up).

# Output enable (OE)

The outputs  $Q_0$  to  $Q_3$  are enabled when  $\overline{OE}$  = LOW. When  $\overline{OE}$  = HIGH the outputs are in the high impedance OFF-state.

# **FUNCTIONAL DESCRIPTION**

#### **Data input**

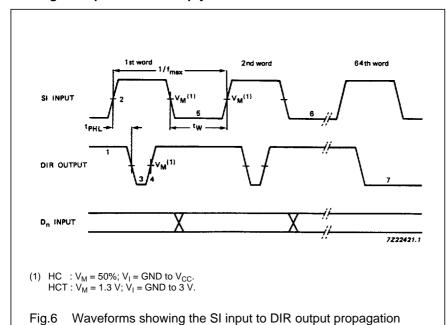

Following power-up, the master-reset (MR) input is pulsed HIGH to clear the FIFO memory (see Fig.8). The data-in-ready flag (DIR = HIGH) indicates that the FIFO input stage is empty and ready to receive data. When DIR is valid (HIGH), data present at  $D_0$  to  $D_3$  can be shifted-in using the SI control input. With SI = HIGH, data is shifted into the input stage and a busy indication is given by DIR going LOW.

The data remains at the first location in the FIFO until DIR is set to HIGH and data moves through the FIFO to the output stage, or to the last empty location. If the FIFO is not full after the SI pulse, DIR again becomes valid (HIGH) to indicate that space is available in the FIFO. The DIR flag remains LOW if the FIFO is full (see Fig.6). The SI use must be made

LOW in order to complete the shift-in process.

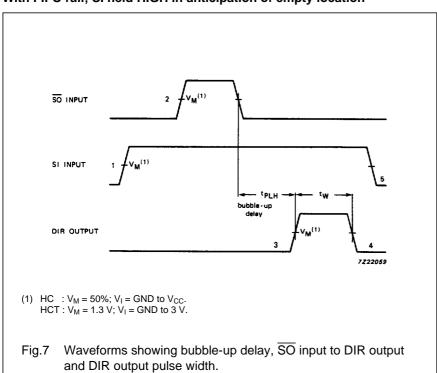

With the FIFO full, SI can be held HIGH until a shift-out (SO) pulse occurs. Then, following a shift-out of data, an empty location appears at the FIFO input and DIR goes HIGH to allow the next data to be shifted-in. This remains at the first FIFO location until SI goes LOW (see Fig.7).

## Data transfer

After data has been transferred from the input stage of the FIFO following SI = LOW, data moves through the FIFO asynchronously and is stacked at the output end of the register. Empty locations appear at the input end of the FIFO as data moves through the device.

## **Data output**

The data-out-ready flag (DOR = HIGH) indicates that there is valid data at the output ( $Q_0$  to  $Q_3$ ). The initial master-reset at power-on (MR = HIGH) sets DOR to LOW (see Fig.8). After MR = LOW, data shifted into the FIFO moves through to the output stage causing DOR to go HIGH.

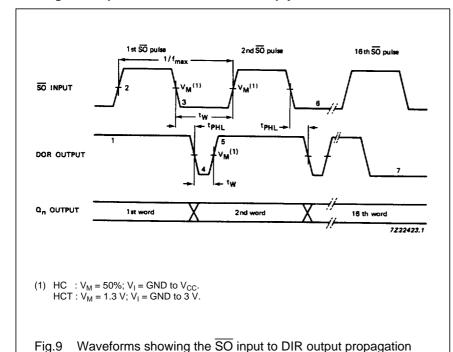

As the DOR flag goes HIGH, data can be shifted-out using the  $\overline{SO}$  = HIGH, data in the output stage is shifted out and a busy indication is given by DOR going LOW. When SO is made LOW, data moves through the FIFO to fill the output stage and an empty location appears at the input stage. When the output stage is filled DOR goes HIGH, but if the last of the valid data has been shifted-out leaving the FIFO empty the DOR flag remains LOW (see Fig.9). With the FIFO empty, the last word that was shifted-out is latched at the output  $Q_0$  to  $Q_3$ .

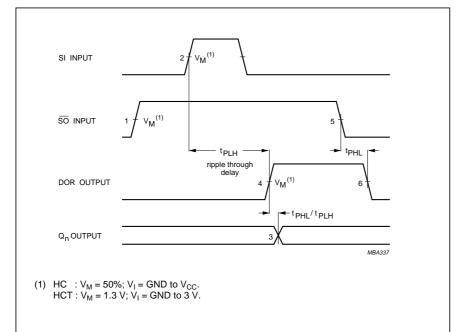

With the FIFO empty, the SO input can be held HIGH until the SI control input is used. Following an SI pulse,

# 4-bit x 16-word FIFO register

# 74HC/HCT40105

data moves through the FIFO to the output stage, resulting in the DOR flag pulsing HIGH and a shift-out of data occurring. The SO control must be made LOW before additional data can be shifted-out (see Fig.10).

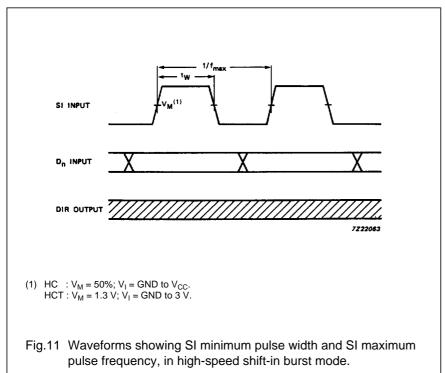

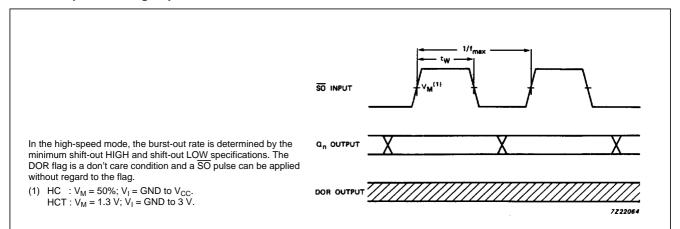

#### High-speed burst mode

If it is assumed that the shift-in/shift-out pulses are not applied until the respective status flags are valid, it follows that the shift-in/shift-out rates are determined by the status flags. However, without the status flags a high-speed burst mode can be implemented. In this mode, the burst-in/ burst-out rates are determined by the pulse widths of the shift-in/shift-out inputs and burst rates of 35 MHz can be obtained. Shift

pulses can be applied without regard to the status flags but shift-in pulses that would overflow the storage capacity of the FIFO are not allowed (see Figs 11 and 12).

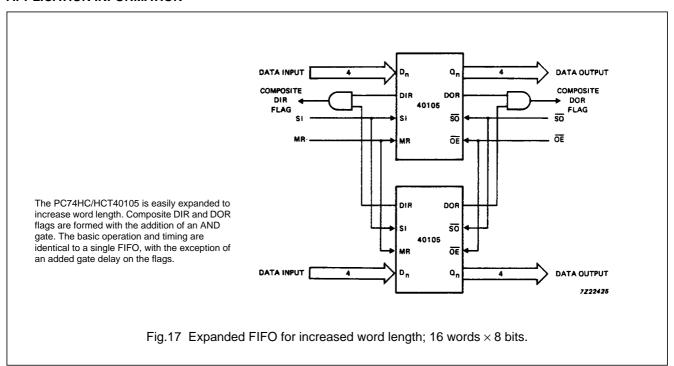

#### **Expanded format**

With the addition of a logic gate, the FIFO is easily expanded to increase word length (see Fig.17). The basic operation and timing are identical to a single FIFO, with the exception of an additional gate delay on the flag outputs. If during application, the following occurs:

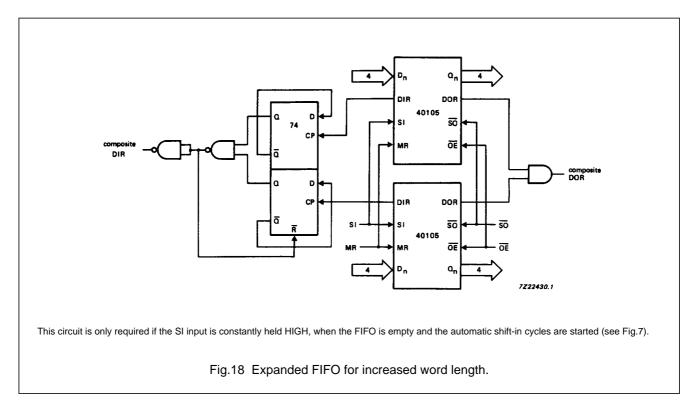

SI is held HIGH when the FIFO is empty, some additional logic is required to produce a composite DIR pulse (see Figs 7 and 18). Due to the part-to-part spread of the ripple through time, the SI signals of FIFO<sub>A</sub> and FIFO<sub>B</sub> will not always coincide and the AND-gate will not produce a composite flag signal. The solution is given in Fig.18.

The "40105" is easily cascaded to increase the word capacity and no external components are needed. In the cascaded configuration, all necessary communications and timing are performed by the FIFOs. The intercommunication speed is determined by the minimum flag pulse widths and the flag delays. The data rate of cascaded devices is typically 25 MHz. Word-capacity can be expanded to and beyond 32-words × 4-bits (see Fig.19).

# 4-bit x 16-word FIFO register

# 74HC/HCT40105

# 4-bit x 16-word FIFO register

# 74HC/HCT40105

# DC CHARACTERISTICS FOR 74HC

For the DC characteristics see "74HC/HCT/HCU/HCMOS Logic Family Specifications".

Output capability: standard

I<sub>CC</sub> category: MSI

# **AC CHARACTERISTICS FOR 74HC**

$GND = 0 \ V; \ t_f = t_f = 6 \ ns; \ C_L = 50 \ pF$

|                                     |                                |      |      |      | T <sub>amb</sub> ( | °C)   |       |        |       | TEST CONDITIONS |           |  |

|-------------------------------------|--------------------------------|------|------|------|--------------------|-------|-------|--------|-------|-----------------|-----------|--|

| 0.445.01                            | DADAMETED                      |      |      |      | 74H0               | 3     |       |        | ]<br> | WAVEFORMS       |           |  |

| SYMBOL                              | PARAMETER                      |      | +25  |      | −40 t              | o +85 | -40 t | o +125 | UNIT  | V <sub>CC</sub> | WAVEFORMS |  |

|                                     |                                | min. | typ. | max. | min.               | max.  | min.  | max.   |       | (*)             |           |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay              |      | 52   | 175  |                    | 220   |       | 265    | ns    | 2.0             | Fig.8     |  |

|                                     | MR to DIR, DOR                 |      | 19   | 35   |                    | 44    |       | 53     |       | 4.5             |           |  |

|                                     |                                |      | 15   | 30   |                    | 37    |       | 45     |       | 6.0             |           |  |

| t <sub>PHL</sub>                    | propagation delay              |      | 52   | 210  |                    | 265   |       | 315    | ns    | 2.0             | Fig.6     |  |

|                                     | SI to DIR                      |      | 19   | 42   |                    | 53    |       | 63     |       | 4.5             |           |  |

|                                     |                                |      | 15   | 36   |                    | 45    |       | 54     |       | 6.0             |           |  |

| t <sub>PHL</sub>                    | propagation delay              |      | 55   | 210  |                    | 265   |       | 315    | ns    | 2.0             | Fig.9     |  |

|                                     | SO to DOR                      |      | 20   | 42   |                    | 53    |       | 63     |       | 4.5             |           |  |

|                                     |                                |      | 16   | 36   |                    | 45    |       | 54     |       | 6.0             |           |  |

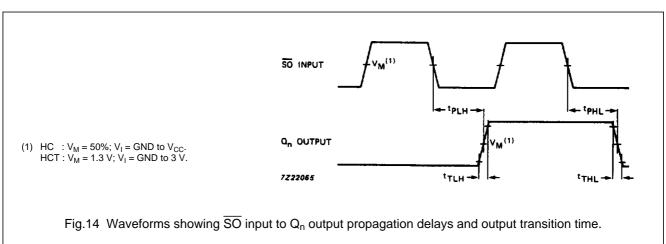

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay              |      | 116  | 400  |                    | 500   |       | 600    | ns    | 2.0             | Fig.14    |  |

|                                     | SO to Q <sub>n</sub>           |      | 42   | 80   |                    | 100   |       | 120    |       | 4.5             |           |  |

|                                     |                                |      | 34   | 68   |                    | 85    |       | 102    |       | 6.0             |           |  |

| t <sub>PLH</sub>                    | propagation delay/             |      | 564  | 2000 |                    | 2500  |       | 3000   | ns    | 2.0             | Fig.10    |  |

|                                     | ripple through delay SI to DOR |      | 205  | 400  |                    | 500   |       | 600    |       | 4.5             |           |  |

|                                     | 31 10 DOR                      |      | 165  | 340  |                    | 425   |       | 510    |       | 6.0             |           |  |

| t <sub>PLH</sub>                    | propagation delay/             |      | 701  | 2500 |                    | 3125  |       | 3750   | ns    | 2.0             | Fig.7     |  |

|                                     | bubble-up delay                |      | 255  | 500  |                    | 625   |       | 750    |       | 4.5             |           |  |

|                                     | SO to DIR                      |      | 204  | 425  |                    | 532   |       | 638    |       | 6.0             |           |  |

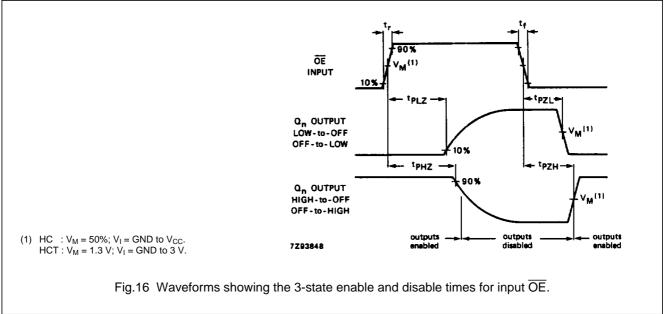

| t <sub>PZH</sub> / t <sub>PZL</sub> | 3-state output enable time     |      | 41   | 150  |                    | 190   |       | 225    | ns    | 2.0             | Fig.16    |  |

|                                     | OE to Q <sub>n</sub>           |      | 15   | 30   |                    | 38    |       | 45     |       | 4.5             |           |  |

|                                     |                                |      | 12   | 26   |                    | 33    |       | 38     |       | 6.0             |           |  |

| t <sub>PHZ</sub> / t <sub>PLZ</sub> | 3-state output disable         |      | 41   | 140  |                    | 175   |       | 210    | ns    | 2.0             | Fig.16    |  |

|                                     | time                           |      | 15   | 28   |                    | 35    |       | 42     |       | 4.5             |           |  |

|                                     | OE to Q <sub>n</sub>           |      | 12   | 24   |                    | 30    |       | 36     |       | 6.0             |           |  |

| t <sub>THL</sub> / t <sub>TLH</sub> | output transition time         |      | 19   | 75   |                    | 95    |       | 110    | ns    | 2.0             | Fig.14    |  |

|                                     |                                |      | 7    | 15   |                    | 19    |       | 22     |       | 4.5             |           |  |

|                                     |                                |      | 6    | 13   |                    | 16    |       | 19     |       | 6.0             |           |  |

| t <sub>W</sub>                      | SI pulse width                 | 80   | 19   |      | 100                |       | 120   |        | ns    | 2.0             | Fig.6     |  |

|                                     | HIGH or LOW                    | 16   | 7    |      | 20                 |       | 24    |        |       | 4.5             |           |  |

|                                     |                                | 14   | 6    |      | 17                 |       | 20    |        |       | 6.0             |           |  |

# 4-bit x 16-word FIFO register

# 74HC/HCT40105

|                  |                                  |      |      |      | T <sub>amb</sub> ( | °C)   |       |        |            | TEST CONDITIONS |              |  |

|------------------|----------------------------------|------|------|------|--------------------|-------|-------|--------|------------|-----------------|--------------|--|

| 0)/4504          | DAD 444575D                      |      |      |      | 74H                | C     |       |        | ļ <u>.</u> |                 |              |  |

| SYMBOL           | PARAMETER                        |      | +25  |      | −40 t              | o +85 | -40 t | o +125 | UNIT       | V <sub>CC</sub> | WAVEFORMS    |  |

|                  |                                  | min. | typ. | max. | min.               | max.  | min.  | max.   |            | (*)             |              |  |

| t <sub>W</sub>   | SO pulse width                   | 120  | 39   |      | 150                |       | 180   |        | ns         | 2.0             | Fig.9        |  |

|                  | HIGH or LOW                      | 24   | 14   |      | 30                 |       | 36    |        |            | 4.5             |              |  |

|                  |                                  | 20   | 11   |      | 26                 |       | 31    |        |            | 6.0             |              |  |

| $t_W$            | DIR pulse width                  | 12   | 58   | 180  | 10                 | 225   | 10    | 270    | ns         | 2.0             | Fig.7        |  |

|                  | HIGH                             | 6    | 21   | 36   | 5                  | 45    | 5     | 54     |            | 4.5             |              |  |

|                  |                                  | 5    | 17   | 31   | 4                  | 38    | 4     | 46     |            | 6.0             |              |  |

| $t_{W}$          | DOR pulse width                  | 12   | 55   | 170  | 10                 | 215   | 10    | 255    | ns         | 2.0             | Fig.9        |  |

|                  | LOW                              | 6    | 20   | 34   | 5                  | 43    | 5     | 51     |            | 4.5             |              |  |

|                  |                                  | 5    | 16   | 29   | 4                  | 37    | 4     | 43     |            | 6.0             |              |  |

| t <sub>W</sub>   | MR pulse width                   | 80   | 22   |      | 100                |       | 120   |        | ns         | 2.0             | Fig.8        |  |

|                  | HIGH                             | 16   | 8    |      | 20                 |       | 24    |        |            | 4.5             |              |  |

|                  |                                  | 14   | 6    |      | 17                 |       | 20    |        |            | 6.0             |              |  |

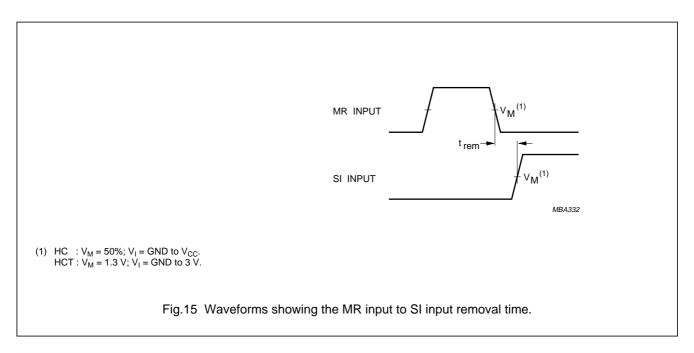

| t <sub>rem</sub> | removal time                     | 50   | 14   |      | 65                 |       | 75    |        | ns         | 2.0             | Fig.15       |  |

|                  | MR to SI                         | 10   | 5    |      | 13                 |       | 15    |        |            | 4.5             |              |  |

|                  |                                  | 9    | 4    |      | 11                 |       | 13    |        |            | 6.0             |              |  |

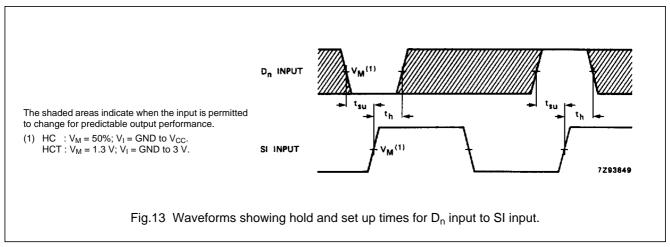

| t <sub>su</sub>  | set-up time                      | -5   | -39  |      | -5                 |       | -5    |        | ns         | 2.0             | Fig.13       |  |

|                  | D <sub>n</sub> to SI             | -5   | -14  |      | -5                 |       | -5    |        |            | 4.5             |              |  |

|                  |                                  | -5   | -11  |      | -5                 |       | -5    |        |            | 6.0             |              |  |

| t <sub>h</sub>   | hold time                        | 125  | 44   |      | 155                |       | 190   |        | ns         | 2.0             | Fig.13       |  |

|                  | D <sub>n</sub> to SI             | 25   | 16   |      | 31                 |       | 38    |        |            | 4.5             |              |  |

|                  |                                  | 21   | 13   |      | 26                 |       | 32    |        |            | 6.0             |              |  |

| f <sub>max</sub> | maximum pulse                    | 3.6  | 10   |      | 2.8                |       | 2.4   |        | MHz        | 2.0             | Fig.6, 9, 11 |  |

|                  | frequency                        | 18   | 30   |      | 14                 |       | 12    |        |            | 4.5             | and 12       |  |

|                  | SI, SO using flags or burst mode | 21   | 36   |      | 16                 |       | 14    |        |            | 6.0             |              |  |

| f <sub>max</sub> | maximum pulse                    | 3.6  | 10   |      | 2.8                |       | 2.4   |        | MHz        | 2.0             | Figs 6 and 9 |  |

|                  | frequency                        | 18   | 30   |      | 14                 |       | 12    |        |            | 4.5             |              |  |

|                  | SI, SO cascaded                  | 21   | 36   |      | 16                 |       | 14    |        |            | 6.0             |              |  |

# 4-bit x 16-word FIFO register

# 74HC/HCT40105

## DC CHARACTERISTICS FOR 74HCT

For the DC characteristics see "74HC/HCT/HCU/HCMOS Logic Family Specifications".

Output capability: standard

I<sub>CC</sub> category: MSI

# Note to HCT types

The value of additional quiescent supply current ( $\Delta I_{CC}$ ) for a unit load of 1 is given in the family specifications. To determine  $\Delta I_{CC}$  per input, multiply this value by the unit load coefficient shown in the table below.

| INPUT          | UNIT LOAD COEFFICIENT |

|----------------|-----------------------|

| ŌĒ             | 0.75                  |

| SI             | 0.40                  |

| D <sub>n</sub> | 0.30                  |

| MR             | 1.50                  |

| SO             | 0.40                  |

### **AC CHARACTERISTICS FOR 74HCT**

$GND = 0 V; t_f = t_f = 6 ns; C_L = 50 pF$

|                                     |                                                               |      |      | -    | T <sub>amb</sub> (° | C)   |             |      |      | TEST CONDITIONS |           |  |

|-------------------------------------|---------------------------------------------------------------|------|------|------|---------------------|------|-------------|------|------|-----------------|-----------|--|

| CVMBOL                              |                                                               |      |      |      | 74HC                | Т    |             |      |      |                 | WAVEFORMS |  |

| SYMBOL                              | PARAMETER                                                     | +25  |      |      | -40 to +85          |      | -40 to +125 |      | UNIT | V <sub>CC</sub> | WAVEFORMS |  |

|                                     |                                                               | min. | typ. | max. | min.                | max. | min.        | max. |      | (',             |           |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay<br>MR to DIR, DOR                           |      | 18   | 35   |                     | 44   |             | 53   | ns   | 4.5             | Fig.8     |  |

| t <sub>PHL</sub>                    | propagation delay<br>SI to DIR                                |      | 21   | 42   |                     | 53   |             | 63   | ns   | 4.5             | Fig.6     |  |

| t <sub>PHL</sub>                    | propagation delay SO to DOR                                   |      | 20   | 42   |                     | 53   |             | 63   | ns   | 4.5             | Fig.9     |  |

| t <sub>PHL</sub> / t <sub>PLH</sub> | propagation delay SO to Q <sub>n</sub>                        |      | 40   | 80   |                     | 100  |             | 120  | ns   | 4.5             | Fig.14    |  |

| t <sub>PLH</sub>                    | propagation delay/<br>ripple through delay<br>SI to DOR       |      | 188  | 400  |                     | 500  |             | 600  | ns   | 4.5             | Fig.10    |  |

| t <sub>PLH</sub>                    | propagation delay/<br>bubble-up delay<br>SO to DIR            |      | 244  | 500  |                     | 625  |             | 750  | ns   | 4.5             | Fig.7     |  |

| t <sub>PZH</sub> / t <sub>PZL</sub> | 3-state output enable time<br><del>OE</del> to Q <sub>n</sub> |      | 18   | 35   |                     | 44   |             | 53   | ns   | 4.5             | Fig.16    |  |

| t <sub>PHZ</sub> / t <sub>PLZ</sub> | 3-state output disable time OE to Q <sub>n</sub>              |      | 15   | 30   |                     | 38   |             | 45   | ns   | 4.5             | Fig.16    |  |

| t <sub>THL</sub> / t <sub>TLH</sub> | output transition time                                        |      | 7    | 15   |                     | 19   |             | 22   | ns   | 4.5             | Fig.14    |  |

# 4-bit x 16-word FIFO register

# 74HC/HCT40105

|                  |                                                          |            |      | -    | T <sub>amb</sub> (° | C)    |        |        |      | TEST CONDITIONS |                     |  |

|------------------|----------------------------------------------------------|------------|------|------|---------------------|-------|--------|--------|------|-----------------|---------------------|--|

| SYMBOL           | PARAMETER                                                |            |      |      | 74HC                | Т     |        |        |      |                 | WAVEFORMS           |  |

| STIVIBUL         | PARAMETER                                                |            | +25  |      | −40 t               | o +85 | -40 to | o +125 | UNIT | V <sub>CC</sub> | WAVEFORMS           |  |

|                  |                                                          | min.       | typ. | max. | min.                | max.  | min.   | max.   |      | (,,             |                     |  |

| t <sub>W</sub>   | SI pulse width<br>HIGH or LOW                            | 16         | 6    |      | 20                  |       | 24     |        | ns   | 4.5             | Fig.6               |  |

| t <sub>W</sub>   | SO pulse width<br>HIGH or LOW                            | 16         | 7    |      | 20                  |       | 24     |        | ns   | 4.5             | Fig.9               |  |

| t <sub>W</sub>   | DIR pulse width<br>HIGH or LOW                           | 6          | 20   | 34   | 5                   | 43    | 5      | 51     | ns   | 4.5             | Fig.7               |  |

| t <sub>W</sub>   | DOR pulse width<br>HIGH or LOW                           | 6          | 19   | 34   | 5                   | 43    | 5      | 51     | ns   | 4.5             | Fig.9               |  |

| t <sub>W</sub>   | MR pulse width<br>HIGH                                   | 16         | 7    |      | 20                  |       | 24     |        | ns   | 4.5             | Fig.8               |  |

| t <sub>rem</sub> | removal time<br>MR to SI                                 | 15         | 7    |      | 19                  |       | 22     |        | ns   | 4.5             | Fig.15              |  |

| t <sub>su</sub>  | set-up time<br>D <sub>n</sub> to SI                      | <b>-</b> 5 | -14  |      | -4                  |       | -4     |        | ns   | 4.5             | Fig.13              |  |

| t <sub>h</sub>   | hold time<br>D <sub>n</sub> to SI                        | 27         | 16   |      | 34                  |       | 41     |        | ns   | 4.5             | Fig.13              |  |

| f <sub>max</sub> | maximum pulse frequency SI, SO using flags or burst mode |            | 28   |      | 12                  |       | 10     |        | MHz  | 4.5             | Fig.6, 9, 11 and 12 |  |

| f <sub>max</sub> | maximum pulse frequency SI, SO cascaded                  |            | 28   |      | 12                  |       | 10     |        | MHz  | 4.5             | Figs 6 and 9        |  |

# 4-bit x 16-word FIFO register

# 74HC/HCT40105

#### **AC WAVEFORMS**

#### Shifting in sequence FIFO empty to FIFO full

delay. The SI pulse width and SI maximum pulse frequency.

# Notes to Fig.6

- 1. DIR initially HIGH; FIFO is prepared for valid data.

- 2. SI set HIGH; data loaded into input stage.

- 3. DIR drops LOW, input stage "busy".

- DIR goes HIGH, status flag indicates FIFO prepared for additional data; data from first location "ripple through".

- 5. SI set LOW; necessary to complete shift-in process.

- 6. Repeat process to load 2nd word through to 16th word into FIFO.

- DIR remains LOW: with attempt to shift into full FIFO, no data transfer occurs.

## With FIFO full; SI held HIGH in anticipation of empty location

#### Notes to Fig.7

- 1. FIFO is initially, shift-in is held HIGH.

- SO pulse; data in the output stage is unloaded, "bubble-up process of empty locations begins".

- DIR HIGH; when empty location reached input stage, flag indicates FIFO is prepared for data input.

- 4. DIR returns to LOW; FIFO is full again.

- SI brought LOW; necessary to complete whidt-in process, DIR remains LOW, because FIFO is full.

# 4-bit x 16-word FIFO register

# 74HC/HCT40105

## Master reset applied with FIFO full

# Notes to Fig.8

- 1. DIR LOW, output ready HIGH; assume FIFO is full.

- MR pulse HIGH; clears FIFO.

- 3. DIR goes HIGH; flag indicates input prepared for valid data.

- DOR drops LOW; flag indicates FIFO empty.

#### Shifting out sequence; FIFO full to FIFO empty

delay. The  $\overline{SO}$  pulse width and  $\overline{SO}$  maximum pulse frequency.

- Notes to Fig.9

- DOR HIGH; no data transfer in progress, valid data is present at output stage.

- 2. SO set HIGH.

- 3. SO is set LOW; data in the input stage is unloaded, and new data replaces it as empty location "bubbles-up" to input stage.

- 4. DOR drops LOW; output stage "busy".

- 5. DOR goes HIGH; transfer process completed, valid data present at output after the specified propagation delay.

- 6. Repeat process to unloaded the 3rd through to the 16th word from FIFO.

- 7. DOR remains LOW; FIFO is empty.

1998 Jan 23 12

Fig.9

# 4-bit x 16-word FIFO register

# 74HC/HCT40105

# With FIFO empty; SO is held HIGH in anticipation

Fig.10 Waveforms showing ripple through delay SI input to DOR output and propagation delay from the DOR pulse to the Q<sub>n</sub> output.

### Notes to Fig.10

- FIFO is initially empty, SO is held HIGH.

- SI pulse; loads data into FIFO and initiates ripple through process.

- 3. DOR flag signals the arrival of valid data at the output stage.

- Output transition; data arrives at output stage after the specified propagation delay between the rising edge of the DOR pulse to the Q<sub>n</sub> output.

- SO set LOW; necessary to complete shift-out process. DOR remains LOW, because FIFO is empty.

- 6. DOR goes LOW; FIFO is empty again.

### Shift-in operation; high-speed burst mode

#### Note to Fig.11

In the high-speed mode, the burst-in rate is determined by the minimum shift-in HIGH and shift-in LOW specifications. The DIR status flag is a don't care condition, and a shift-in pulse can be applied regardless of the flag. A SI pulse which would overflow the storage capacity of the FIFO is ignored.

# 4-bit x 16-word FIFO register

# 74HC/HCT40105

## Shift-out operation; high-speed burst mode

Fig.12 Waveforms showing SO minimum pulse width and maximum pulse frequency, in high-speed shift-out burst mode.

# 4-bit x 16-word FIFO register

# 74HC/HCT40105

# 4-bit x 16-word FIFO register

# 74HC/HCT40105

#### **APPLICATION INFORMATION**

# 4-bit x 16-word FIFO register

# 74HC/HCT40105

## **Expanded format**

Fig.19 shows two cascaded FIFOs providing a capacity of 32 words × 4 bits

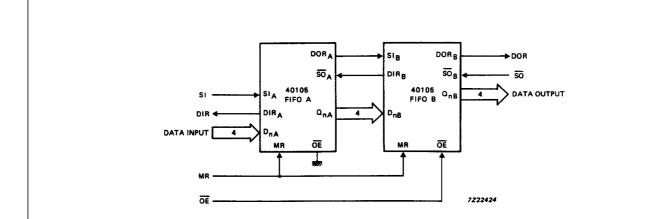

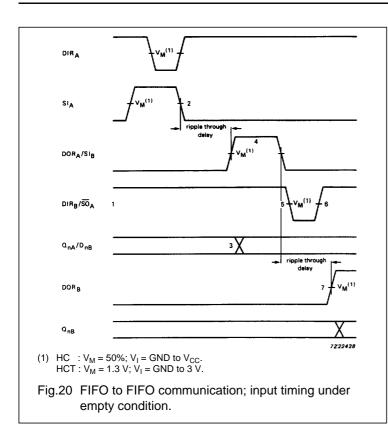

Fig.20 shows the signals on the nodes of both FIFOs after the application of a SI pulse, when both FIFOs are initially empty. After a rippled through delay, date arrives at the output of FIFO<sub>A</sub>. Due to  $\overline{SO}_A$  being HIGH, a DOR pulse is generated. The requirements of SI<sub>B</sub> and D<sub>nB</sub> are satisfied by the DOR<sub>A</sub> pulse width and the timing between the rising edge of DOR<sub>A</sub> and Q<sub>nA</sub>. After a second ripple through delay, data arrives at the output of FIFO<sub>B</sub>.

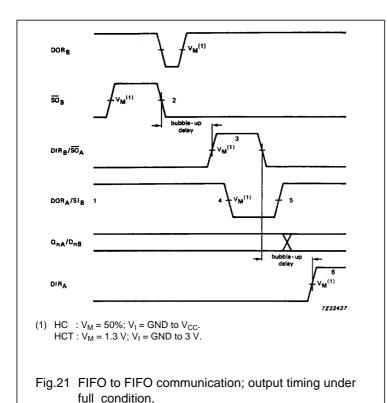

Fig.21 shows the signals on the nodes of both FIFOs after the application of a  $\overline{SO}_R$  pulse, when both FIFOs are initially full. After a bubble-up delay a DIR<sub>R</sub> pulse is generated, which acts as a  $\overline{SO}_A$  pulse for FIFO<sub>A</sub>. One word is transferred from the output of FIFO<sub>A</sub> to the input of FIFO<sub>B</sub>. The requirements of the  $\overline{SO}_A$  pulse for FIFO<sub>A</sub> is satisfied by the pulse width of DOR<sub>B</sub>. After a second bubble-up delay an empty space arrives at D<sub>nA</sub>, at which time DIR<sub>A</sub> goes HIGH. Fig.22 shows the waveforms at all external nodes of both FIFOs during a complete shift-in and shift-out sequence.

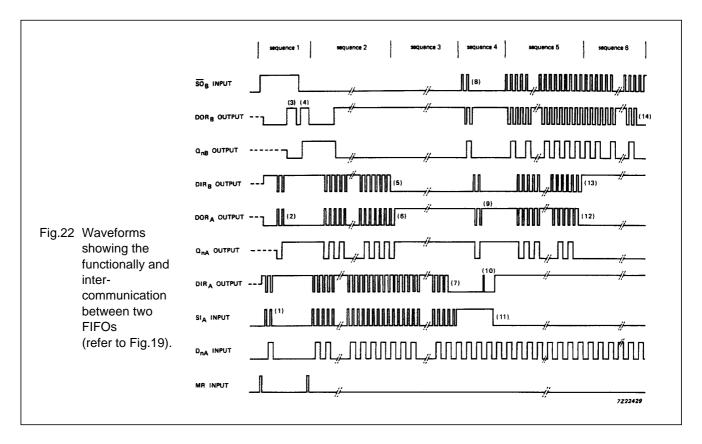

The PC7HC/HCT40105 is easily cascaded to increase word capacity without any external circuitry. In cascaded format, all necessary communications are handled by the FIFOs. Figs 17 and 19 demonstrate the intercommunication timing between FIFO<sub>A</sub> and FIFO<sub>B</sub>. Fig.22 gives an overview of pulse and timing of two cascaded FIFOs, when shifted full and shifted empty again.

Fig.19 Cascading for increased word capacity; 32 words × 4 bits.

# 4-bit x 16-word FIFO register

# 74HC/HCT40105

## Notes to Fig.20

- 1. FIFO<sub>A</sub> and FIFO<sub>B</sub> initially empty,  $\overline{SO}_A$  held HIGH in anticipation of data.

- 2. Load one word into FIFO<sub>A</sub>; SI pulse applied, results in DIR pulse.

- Data out A/data in B transition; valid data arrives at FIFOA output stage after a specified delay of the DOR flag, meeting data input set-up requirements of FIFOB.

- DOR<sub>A</sub> and SI<sub>B</sub> pulse HIGH; (ripple through delay after SI<sub>A</sub> LOW) data is unloaded from FIFO<sub>A</sub> as a result of the data output ready pulse, data is shifted into FIFO<sub>B</sub>.

- DIR<sub>B</sub> and SO<sub>A</sub> go LOW; flag indicates input stage of FIFO<sub>B</sub> is busy, shift-out of FIFO<sub>A</sub> is complete.

- DIR<sub>B</sub> and SO<sub>A</sub> go HIGH automatically; the input stage of FIFO<sub>B</sub> is again able to receive data, SO is held HIGH in anticipation of additional data.

- DOR<sub>B</sub> goes HIGH; (ripple through delay after SI<sub>B</sub> LOW) valid data is present one propagation delay later at the FIFO<sub>B</sub> output stage.

### Notes to Fig.21

- FIFO<sub>A</sub> and FIFO<sub>B</sub> initially empty, SI<sub>B</sub> held HIGH in anticipation of shifting in new data as empty location bubbles-up.

- 2. Unload one word into FIFO<sub>B</sub>; SO pulse applied, results in DOR pulse.

- DIR<sub>B</sub> and SO<sub>A</sub> pulse HIGH; (bubble-up delay after SO<sub>B</sub> LOW) data is loaded into FIFO<sub>B</sub> as a result of the DIR pulse, data is shifted out of FIFO<sub>A</sub>.

- DOR<sub>A</sub> and SI<sub>B</sub> go LOW; flag indicates the output stage of FIFO<sub>A</sub> is busy, shift-in to FIFO<sub>R</sub> is complete.

- DOR<sub>A</sub> and SI<sub>B</sub> go HIGH; flag indicates valid data is again available at FIFO<sub>A</sub> output stage, SI<sub>B</sub> is held HIGH, awaiting bubble-up of empty location.

- DIR<sub>A</sub> goes HIGH; (bubble-up delay after SO<sub>A</sub> LOW) an empty location is present at input stage of FIFO<sub>A</sub>.

# 4-bit x 16-word FIFO register

# 74HC/HCT40105

#### Note to Fig.22

Sequence 1 (Both FIFOs empty, starting shift-in process): After a MR pulse has been applied FIFO<sub>A</sub> and FIFO<sub>B</sub> are empty. The DOR flags of FIFO<sub>A</sub> and FIFO<sub>B</sub> go LOW due to no valid data being present at the outputs. The DIR flags are set HIGH due to the FIFOs being ready to accept data.  $\overline{SO}_B$  is held HIGH and two SI<sub>A</sub> pulses are applied (1). These pulses allow two data words to ripple through to the output stage of FIFO<sub>A</sub> and to the input stage of FIFO<sub>B</sub> (2). When data arrives at the output of FIFO<sub>B</sub>, a DOR<sub>B</sub> pulse is generated (3). When  $\overline{SO}_B$  goes LOW, the first bit is shifted out and a second bit ripples through to the output after which DOR<sub>B</sub> goes HIGH (4).

#### Sequence 2 (FIFO<sub>B</sub> runs full):

After the MR pulse, a series of 16 SI pulses are applied. When 16 words are shifted in,  $DIR_B$  remains LOW due to  $FIFO_B$  being full (5).  $DOR_A$  goes LOW due to  $FIFO_A$  being empty.

#### Sequence 3 (FIFO<sub>A</sub> runs full):

When 17 words are shifted in, DOR<sub>A</sub> remains HIGH due to valid data remaining at the output of FIFO<sub>A</sub>. Q<sub>nA</sub> remains HIGH, being the polarity of the 17th data word (6). After the 32th SI pulse, DIR remains LOW and both FIFOs are full (7). Additional pulses have no effect.

Sequence 4 (Both FIFOs full, starting shift-out process):  $SI_A$  is held HIGH and two  $\overline{SO}_B$  pulses are applied (8). These pulses shift out two words and thus allow empty locations to bubble-up to the input stage of FIFO<sub>B</sub>, and proceed to FIFO<sub>A</sub> (9). When the first empty location arrives at the input of FIFO<sub>A</sub>, a DIR<sub>A</sub> pulse is generated (10) and a new word is shifted into FIFO<sub>A</sub>.  $SI_A$  is made LOW and now the second empty location reaches the input stage of FIFO<sub>A</sub>, after which DIR<sub>A</sub> remains HIGH (11).

#### Sequence 5 (FIFO<sub>A</sub> runs empty):

At the start of sequence 5 FIFO<sub>A</sub> contains 15 valid words due to two words being shifted out and one word being shifted in sequence 4. An additional series of  $\overline{SO}_B$  pulses are applied. After 15  $\overline{SO}_B$  pulses, all words from FIFO<sub>A</sub> are shifted into FIFO<sub>B</sub>. DOR<sub>A</sub> remains LOW (12).

#### Sequence 6 (FIFO<sub>B</sub> runs empty):

After the next  $\overline{SO}_B$  pulse, DIR<sub>B</sub> remains HIGH due to the input stage of FIFO<sub>B</sub> being empty (13). After another 15  $\overline{SO}_B$  pulses, DOR<sub>B</sub> remains LOW due to both FIFOs being empty (14). Additional  $\overline{SO}_B$  pulses have no effect. The last word remains available at the output Q<sub>n</sub>.

# 4-bit x 16-word FIFO register

# 74HC/HCT40105

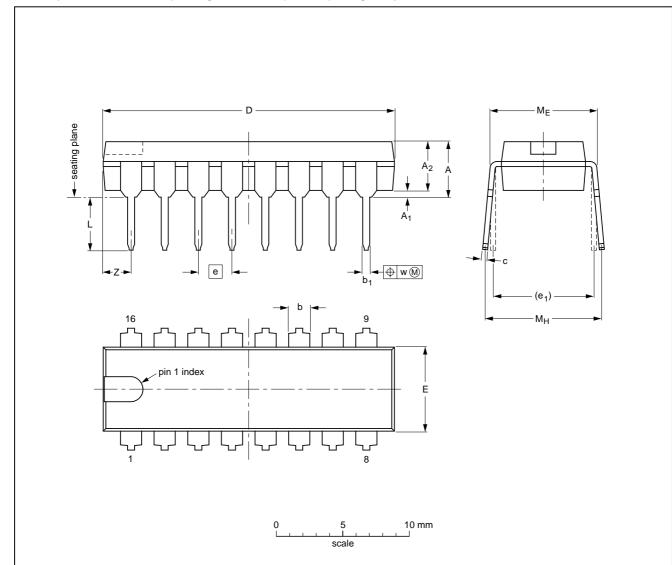

# **PACKAGE OUTLINES**

DIP16: plastic dual in-line package; 16 leads (300 mil); long body

SOT38-1

## DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | A <sub>1</sub><br>min. | A <sub>2</sub><br>max. | b              | b <sub>1</sub> | С              | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | e <sub>1</sub> | L            | M <sub>E</sub> | Мн           | w     | Z <sup>(1)</sup><br>max. |

|--------|-----------|------------------------|------------------------|----------------|----------------|----------------|------------------|------------------|------|----------------|--------------|----------------|--------------|-------|--------------------------|

| mm     | 4.7       | 0.51                   | 3.7                    | 1.40<br>1.14   | 0.53<br>0.38   | 0.32<br>0.23   | 21.8<br>21.4     | 6.48<br>6.20     | 2.54 | 7.62           | 3.9<br>3.4   | 8.25<br>7.80   | 9.5<br>8.3   | 0.254 | 2.2                      |

| inches | 0.19      | 0.020                  | 0.15                   | 0.055<br>0.045 | 0.021<br>0.015 | 0.013<br>0.009 | 0.86<br>0.84     | 0.26<br>0.24     | 0.10 | 0.30           | 0.15<br>0.13 | 0.32<br>0.31   | 0.37<br>0.33 | 0.01  | 0.087                    |

#### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE |        | REFER    | EUROPEAN | ISSUE DATE |            |                                 |

|---------|--------|----------|----------|------------|------------|---------------------------------|

| VERSION | IEC    | JEDEC    | EIAJ     |            | PROJECTION | ISSUE DATE                      |

| SOT38-1 | 050G09 | MO-001AE |          |            |            | <del>92-10-02</del><br>95-01-19 |

# 4-bit x 16-word FIFO register

# 74HC/HCT40105

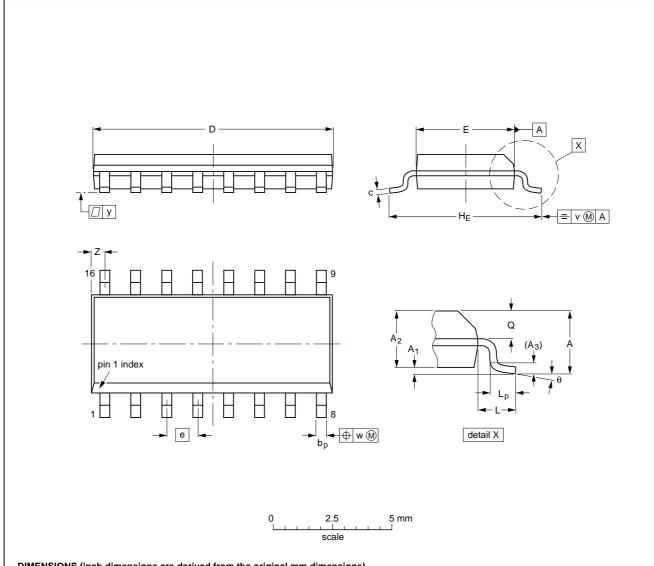

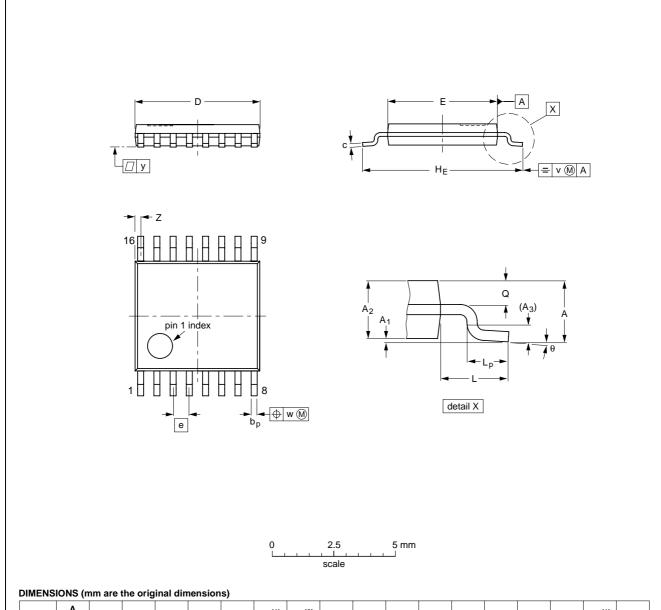

# SO16: plastic small outline package; 16 leads; body width 3.9 mm

SOT109-1

## DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | bp           | С                | D <sup>(1)</sup> | E <sup>(1)</sup> | е     | HE             | L     | Lp             | Q          | v    | w    | у     | Z <sup>(1)</sup> | θ  |

|--------|-----------|----------------|----------------|----------------|--------------|------------------|------------------|------------------|-------|----------------|-------|----------------|------------|------|------|-------|------------------|----|

| mm     | 1.75      | 0.25<br>0.10   | 1.45<br>1.25   | 0.25           | 0.49<br>0.36 | 0.25<br>0.19     | 10.0<br>9.8      | 4.0<br>3.8       | 1.27  | 6.2<br>5.8     | 1.05  | 1.0<br>0.4     | 0.7<br>0.6 | 0.25 | 0.25 | 0.1   | 0.7<br>0.3       | 8° |

| inches | 0.069     | 0.010<br>0.004 | 0.057<br>0.049 | 0.01           |              | 0.0100<br>0.0075 | 0.39<br>0.38     | 0.16<br>0.15     | 0.050 | 0.244<br>0.228 | 0.041 | 0.039<br>0.016 |            | 0.01 | 0.01 | 0.004 | 0.028<br>0.012   | 0° |

1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

| OUTLINE  |         | REFER    | EUROPEAN | ISSUE DATE |            |                                 |  |

|----------|---------|----------|----------|------------|------------|---------------------------------|--|

| VERSION  | IEC     | JEDEC    | EIAJ     |            | PROJECTION | ISSUE DATE                      |  |

| SOT109-1 | 076E07S | MS-012AC |          |            |            | <del>95-01-23</del><br>97-05-22 |  |

# 4-bit x 16-word FIFO register

# 74HC/HCT40105

# SSOP16: plastic shrink small outline package; 16 leads; body width 5.3 mm

SOT338-1

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | b <sub>p</sub> | С            | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | HE         | L    | Lp           | Q          | v   | w    | у   | Z <sup>(1)</sup> | θ        |

|------|-----------|----------------|----------------|----------------|----------------|--------------|------------------|------------------|------|------------|------|--------------|------------|-----|------|-----|------------------|----------|

| mm   | 2.0       | 0.21<br>0.05   | 1.80<br>1.65   | 0.25           | 0.38<br>0.25   | 0.20<br>0.09 | 6.4<br>6.0       | 5.4<br>5.2       | 0.65 | 7.9<br>7.6 | 1.25 | 1.03<br>0.63 | 0.9<br>0.7 | 0.2 | 0.13 | 0.1 | 1.00<br>0.55     | 8°<br>0° |

#### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |     | REFER    | ENCES | EUROPEAN | ISSUE DATE |                                 |  |

|----------|-----|----------|-------|----------|------------|---------------------------------|--|

| VERSION  | IEC | JEDEC    | EIAJ  |          | PROJECTION | ISSUE DATE                      |  |

| SOT338-1 |     | MO-150AC |       |          |            | <del>94-01-14</del><br>95-02-04 |  |

# 4-bit x 16-word FIFO register

# 74HC/HCT40105

TSSOP16: plastic thin shrink small outline package; 16 leads; body width 4.4 mm

SOT403-1

|      |           |                |                |                |              | -,         |                  |            |      |            |     |              |            |     |      |     |                  |          |

|------|-----------|----------------|----------------|----------------|--------------|------------|------------------|------------|------|------------|-----|--------------|------------|-----|------|-----|------------------|----------|

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | A <sub>3</sub> | bp           | С          | D <sup>(1)</sup> | E (2)      | е    | HE         | L   | Lp           | Q          | ٧   | w    | у   | Z <sup>(1)</sup> | θ        |

| mm   | 1.10      | 0.15<br>0.05   | 0.95<br>0.80   | 0.25           | 0.30<br>0.19 | 0.2<br>0.1 | 5.1<br>4.9       | 4.5<br>4.3 | 0.65 | 6.6<br>6.2 | 1.0 | 0.75<br>0.50 | 0.4<br>0.3 | 0.2 | 0.13 | 0.1 | 0.40<br>0.06     | 8°<br>0° |

#### Notes

- 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

- 2. Plastic interlead protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |     | REFER  | EUROPEAN | ISSUE DATE |            |                                 |

|----------|-----|--------|----------|------------|------------|---------------------------------|

| VERSION  | IEC | JEDEC  | EIAJ     |            | PROJECTION | ISSUE DATE                      |

| SOT403-1 |     | MO-153 |          |            |            | <del>94-07-12</del><br>95-04-04 |

# 4-bit x 16-word FIFO register

# 74HC/HCT40105

#### **SOLDERING**

#### Introduction

There is no soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and surface mounted components are mixed on one printed-circuit board. However, wave soldering is not always suitable for surface mounted ICs, or for printed-circuits with high population densities. In these situations reflow soldering is often used.

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our "IC Package Databook" (order code 9398 652 90011).

#### DIP

#### SOLDERING BY DIPPING OR BY WAVE

The maximum permissible temperature of the solder is 260 °C; solder at this temperature must not be in contact with the joint for more than 5 seconds. The total contact time of successive solder waves must not exceed 5 seconds.

The device may be mounted up to the seating plane, but the temperature of the plastic body must not exceed the specified maximum storage temperature (T<sub>stg max</sub>). If the printed-circuit board has been pre-heated, forced cooling may be necessary immediately after soldering to keep the temperature within the permissible limit.

#### REPAIRING SOLDERED JOINTS

Apply a low voltage soldering iron (less than 24 V) to the lead(s) of the package, below the seating plane or not more than 2 mm above it. If the temperature of the soldering iron bit is less than 300  $^{\circ}$ C it may remain in contact for up to 10 seconds. If the bit temperature is between 300 and 400  $^{\circ}$ C, contact may be up to 5 seconds.

#### SO, SSOP and TSSOP

# REFLOW SOLDERING

Reflow soldering techniques are suitable for all SO, SSOP and TSSOP packages.

Reflow soldering requires solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to the printed-circuit board by screen printing, stencilling or pressure-syringe dispensing before package placement.

Several techniques exist for reflowing; for example, thermal conduction by heated belt. Dwell times vary between 50 and 300 seconds depending on heating method.

Typical reflow temperatures range from 215 to 250  $^{\circ}$ C. Preheating is necessary to dry the paste and evaporate the binding agent. Preheating duration: 45 minutes at 45  $^{\circ}$ C.

#### WAVE SOLDERING

Wave soldering can be used for all SO packages. Wave soldering is **not** recommended for SSOP and TSSOP packages, because of the likelihood of solder bridging due to closely-spaced leads and the possibility of incomplete solder penetration in multi-lead devices.

If wave soldering is used - and cannot be avoided for SSOP and TSSOP packages - the following conditions must be observed:

- A double-wave (a turbulent wave with high upward pressure followed by a smooth laminar wave) soldering technique should be used.

- The longitudinal axis of the package footprint must be parallel to the solder flow and must incorporate solder thieves at the downstream end.

#### Even with these conditions:

- Only consider wave soldering SSOP packages that have a body width of 4.4 mm, that is SSOP16 (SOT369-1) or SSOP20 (SOT266-1).

- Do not consider wave soldering TSSOP packages with 48 leads or more, that is TSSOP48 (SOT362-1) and TSSOP56 (SOT364-1).

During placement and before soldering, the package must be fixed with a droplet of adhesive. The adhesive can be applied by screen printing, pin transfer or syringe dispensing. The package can be soldered after the adhesive is cured.

Maximum permissible solder temperature is 260  $^{\circ}$ C, and maximum duration of package immersion in solder is 10 seconds, if cooled to less than 150  $^{\circ}$ C within 6 seconds. Typical dwell time is 4 seconds at 250  $^{\circ}$ C.

A mildly-activated flux will eliminate the need for removal of corrosive residues in most applications.

#### REPAIRING SOLDERED JOINTS

Fix the component by first soldering two diagonally-opposite end leads. Use only a low voltage soldering iron (less than 24 V) applied to the flat part of the lead. Contact time must be limited to 10 seconds at up to 300 °C. When using a dedicated tool, all other leads can be soldered in one operation within 2 to 5 seconds between 270 and 320 °C.

# 4-bit x 16-word FIFO register

# 74HC/HCT40105

#### **DEFINITIONS**

| Data sheet status                                                                                                                                                                                                                                                                                                                                         |                                                                                       |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Objective specification                                                                                                                                                                                                                                                                                                                                   | This data sheet contains target or goal specifications for product development.       |  |  |  |  |  |  |

| Preliminary specification                                                                                                                                                                                                                                                                                                                                 | This data sheet contains preliminary data; supplementary data may be published later. |  |  |  |  |  |  |

| Product specification                                                                                                                                                                                                                                                                                                                                     | This data sheet contains final product specifications.                                |  |  |  |  |  |  |

| Limiting values                                                                                                                                                                                                                                                                                                                                           | Limiting values                                                                       |  |  |  |  |  |  |

| Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification |                                                                                       |  |  |  |  |  |  |

**Application information**

Where application information is given, it is advisory and does not form part of the specification.

is not implied. Exposure to limiting values for extended periods may affect device reliability.

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.