## TDA7391

### 35W BRIDGE CAR RADIO AMPLIFIER

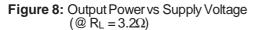

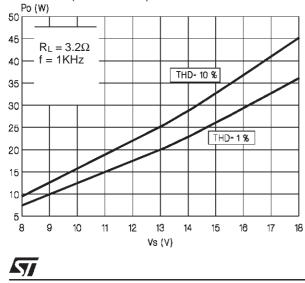

- HIGH POWER CAPABILITY: 40W/4Ω MAX 35W/4Ω EIAJ 45W/3.2Ω MAX 40W/3.2Ω EIAJ 32W/3.2Ω @ Vs = 14.4V, f = 1KHz, d = 10% 26W/4Ω @ Vs = 14.4V, f = 1KHz, d = 10%

- DIFFERENTIAL INPUTS (EITHER SINGLE ENDED OR DIFFERENTIAL INPUT SIGNAL ARE ACCEPTED)

- MINIMUM EXTERNAL COMPONENT COUNT:

- NO BOOTSTRAP CAPACITORS

- NO BOUCHEROT CELLS

- INTERNALLY FIXED GAIN (30dB)

- NO SVR CAPACITOR

- ST.-BY FUNCTION (CMOS COMPATIBLE)

- PROGRAMMABLE TURN-ON/OFF DELAY

- NO AUDIBLE POP DURING MUTE AND ST-BY OPERATIONS

#### **PROTECTIONS:**

- SHORT CIRCUIT (TO GND, TO V<sub>S</sub>, ACROSS THE LOAD)

- VERY INDUCTIVE LOADS

- CHIP OVERTEMPERATURE

- LOAD DUMP

- OPEN GND

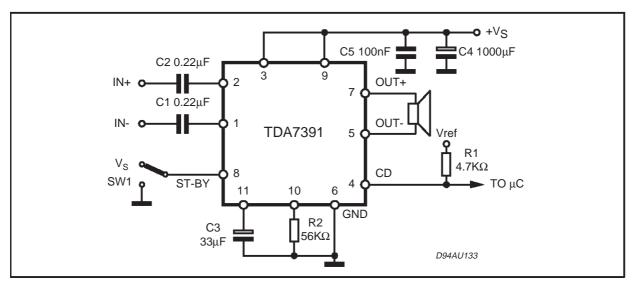

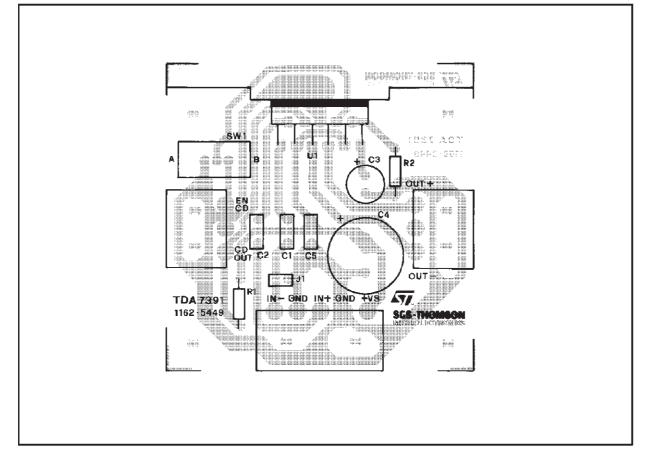

#### Figure 1: Test And Application Circuit

#### ESD

#### DESCRIPTION

The TDA7391 is a BRIDGE class AB audio power amplifier specially intended for car radio High Power applications.

The high power capability together with the possibility to operate either in DIFFERENTIAL INPUT MODE or SINGLE ENDED INPUT MODE makes it suitable for boosters and high end car radio equipments.

The exclusive fully complementary output stage and the internal fixed gain configuration drop the external component count.

The on board clipping detector allows easy implementation of gain compression systems.

#### TDA7391

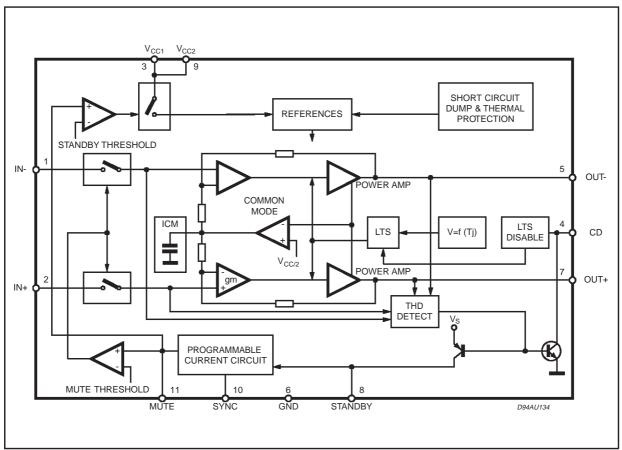

#### Figure 2: Block Diagram

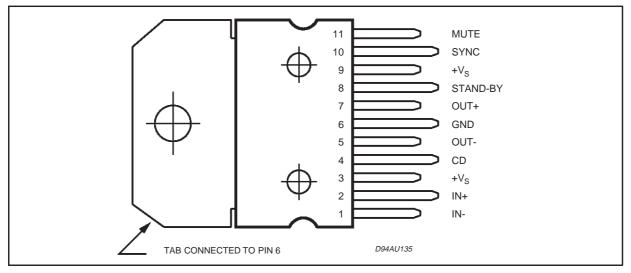

#### PIN CONNECTION (Top view)

#### THERMAL DATA

| Symbol                 | Symbol Description                   |     | Unit |

|------------------------|--------------------------------------|-----|------|

| R <sub>th j-case</sub> | Thermal Resistance Junction-case Max | 1.8 | °C/W |

57

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                            | Parameter                                                                       | Value      | Unit   |

|-----------------------------------|---------------------------------------------------------------------------------|------------|--------|

| Vs                                | DC Supply Voltage                                                               | 28         | V      |

| V <sub>OP</sub>                   | Operating Supply Voltage                                                        | 18         | V      |

| V <sub>PEAK</sub>                 | Peak Supply Voltage (t = 50ms)                                                  | 50         | V      |

| lo                                | Output Peak Current repetitive (f > 10Hz)<br>Output Peak Current non repetitive | 4.5<br>6   | A<br>A |

| P <sub>tot</sub>                  | Power Dissipation (T <sub>CASE</sub> = 85°C)                                    | 43         | W      |

| T <sub>stg</sub> , T <sub>j</sub> | Storage and Junction-Case Temperature                                           | -40 to 150 | °C     |

# **ELECTRICAL CHARACTERISTICS** (Vs = 14.4V; R<sub>L</sub> = 4 $\Omega$ , f = 1KHz, T<sub>amb</sub> = 25°C, unless otherwise specified)

| Symbol               | Parameter                                      | Test Condition                                      | Min. | Тур.           | Max. | Unit        |

|----------------------|------------------------------------------------|-----------------------------------------------------|------|----------------|------|-------------|

| Vs                   | Supply Voltage Range                           |                                                     | 8    |                | 18   | V           |

| lq                   | Total Quiescent Current                        |                                                     |      | 60             | 150  | mA          |

| V <sub>OS</sub>      | Output Offset Voltage                          |                                                     |      |                | 120  | mV          |

| I <sub>SB</sub>      | ST-BY Current                                  | $V_{ST-BY} = 1.5V$                                  |      |                | 100  | μA          |

| I <sub>SBin</sub>    | ST-BY Input Bias Current                       | $V_{ST-BY} = 5V$                                    |      |                | 10   | μA          |

| V <sub>SBon</sub>    | ST-BY On Threshold Voltage                     |                                                     |      |                | 1.5  | V           |

| V <sub>SBoff</sub>   | ST-BY Off threshold Voltage                    |                                                     | 3.5  |                |      | V           |

| ATT <sub>ST-BY</sub> | ST-BY Attenuation                              |                                                     |      | 90             |      | dB          |

| I <sub>M in</sub>    | Mute Input Bias Current                        | $(V_{MUTE} = 5V)$                                   |      |                | 10   | μA          |

| A <sub>M</sub>       | Mute Attenuation                               |                                                     |      | 90             |      | dB          |

| Po                   | Output Power                                   | d = 10%<br>d = 1%<br>d = 10%; R <sub>L</sub> = 3.2Ω | 20   | 26<br>21<br>32 |      | W<br>W<br>W |

| P <sub>O EIAJ</sub>  | EIAJ Output Power (*)                          | VS = 13.7V; R <sub>L</sub> = 3.2Ω                   |      | 40             |      | W           |

| P <sub>O MAX</sub>   | MAX Output Power (*)                           | $VS = 14.4V; R_L = 3.2\Omega$                       |      | 45             |      | W           |

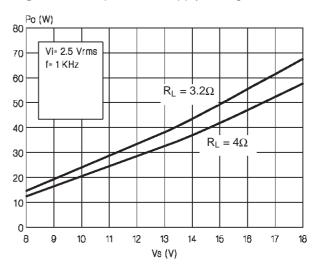

| d                    | Distortion                                     | P <sub>O</sub> = 0.1 to 15W                         |      | 0.06<br>0.03   |      | %<br>%      |

| Gv                   | Voltage Gain                                   |                                                     | 29.5 | 30             | 30.5 | dB          |

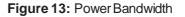

| f <sub>H</sub>       | High Frequency rolloff                         | $P_0 = 1W; -3dB$                                    | 75   |                |      | KHz         |

| R <sub>IN</sub>      | Input Impedance                                | Differential                                        | 36   | 60             |      | KΩ          |

|                      |                                                | Single Ended                                        | 30   | 55             |      | KΩ          |

| EIN                  | Input Noise Voltage                            | $R_g = 0\Omega$ ; f = 22Hz to 22KHz                 |      | 4              |      | mV          |

| CMRR                 | Input Common Mode Rejection                    | $f = 1KHz; V_{IN} = 1Vrms$                          |      | 65             |      | dB          |

| SVR                  | Supply Voltage Rejection                       | $R_g = 0\Omega; V_r = 1Vrms$                        |      | 60             |      | dB          |

| CDL                  | Clipping Detection Level                       |                                                     | 5    | 10             | 15   | %           |

| T <sub>sd</sub>      | Absolute Thermal Shutdown Junction Temperature |                                                     |      | 160            |      | °C          |

(\*) Saturated sqare wave output.

57

#### FUNCTIONAL DESCRIPTION

| Pin  | Function                                                                                                                                                                                                                    | Description                                                                                                                                                                                                                                                                                         |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1, 2 | 2 INPUTS The input stage is a high impedance type also capable of operation in single e with one input capacitively coupled to the signal GND. The impedance seen b inverting and non inverting input pins must be matched. |                                                                                                                                                                                                                                                                                                     |  |

| 3,9  | +V <sub>S</sub>                                                                                                                                                                                                             | Supply Voltage.                                                                                                                                                                                                                                                                                     |  |

| 4    | CD                                                                                                                                                                                                                          | The TDA7391 is equipped with a diagnostic circuitry able to detect the clipping in the Output Signal (distortion = 10%).<br>The CD pin (open collector) gives out low level signal during clipping.                                                                                                 |  |

| 5, 7 | OUTPUTS                                                                                                                                                                                                                     | The output stage is a bridge type able to drive loads as low as $3.2\Omega$ .<br>It consists of two class AB fully complementary PNP/NPN stages fully protected.<br>A rail to rail output voltage swing is achieved without need of bootstrap capacitors.<br>No external compensation is necessary. |  |

| 6    | GND                                                                                                                                                                                                                         | Ground.                                                                                                                                                                                                                                                                                             |  |

| 8    | STAND-BY                                                                                                                                                                                                                    | The device features a ST-BY function which shuts down all the internal bias supplies when the ST-BY pin is low.<br>In ST-BY mode the amplifier sinks a small current (in the range of few $\mu$ A).<br>When the ST-BY pin is high the IC becomes fully operational.                                 |  |

| 10   | SYNC                                                                                                                                                                                                                        | A resistor ( $R_2$ ) has to be connect between pin 10 and GND in order to program the current that flows in the $C_3$ capacitor (pin 11). The values of $C_3$ and $R_2$ determine the time required to bias the amplifier.                                                                          |  |

| 11   | MUTE                                                                                                                                                                                                                        | The pin will have a capacitor ( $C_3$ ) tied to GND to set the MUTE/STAND-BY time. An automatic Mute during turn on/off is provided to prevent noisy transients.                                                                                                                                    |  |

Figure 3: P.C. Board and Component Layout of the Fig. 1 (1:1 scale).

57

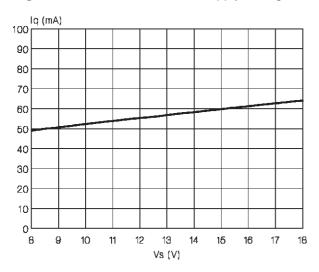

#### Figure 4: Quiescent Current vs Supply Voltage

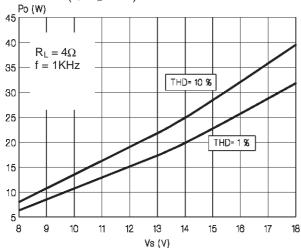

Figure 5: EIAJ power vs Supply Voltage

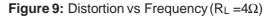

**Figure 7:** Distortion vs Frequency (@  $R_L = 4\Omega$ )

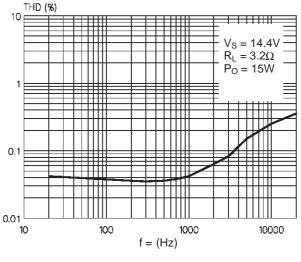

Figure 10: Supply Voltage Rejection vs Frequency

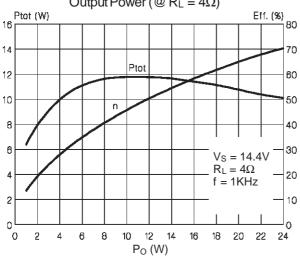

Figure 12: Total Power Dissipation & Efficiency vs. Output Power (@  $R_L = 4\Omega$ )

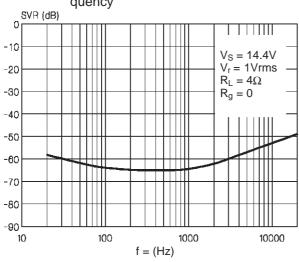

Figure 11: Common Mode Rejection vs. Fre-Quency OMRR (dB) 0 -10  $V_{\rm S} = 14.4V$  $V_{cm} = 1Vrms$  $R_L = 4\Omega$ -20 -30  $R_g = 0$ -40 -50 -60 -70 -80 -90 10 100 1000 10000 f = (Hz)

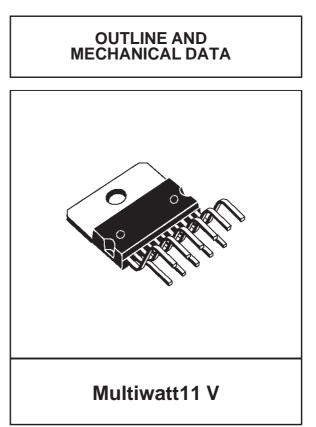

| DIM.  | mm    |      |       | inch  |       |       |

|-------|-------|------|-------|-------|-------|-------|

| DINI. | MIN.  | TYP. | MAX.  | MIN.  | TYP.  | MAX.  |

| А     |       |      | 5     |       |       | 0.197 |

| В     |       |      | 2.65  |       |       | 0.104 |

| С     |       |      | 1.6   |       |       | 0.063 |

| D     |       | 1    |       |       | 0.039 |       |

| Е     | 0.49  |      | 0.55  | 0.019 |       | 0.022 |

| F     | 0.88  |      | 0.95  | 0.035 |       | 0.037 |

| G     | 1.45  | 1.7  | 1.95  | 0.057 | 0.067 | 0.077 |

| G1    | 16.75 | 17   | 17.25 | 0.659 | 0.669 | 0.679 |

| H1    | 19.6  |      |       | 0.772 |       |       |

| H2    |       |      | 20.2  |       |       | 0.795 |

| L     | 21.9  | 22.2 | 22.5  | 0.862 | 0.874 | 0.886 |

| L1    | 21.7  | 22.1 | 22.5  | 0.854 | 0.87  | 0.886 |

| L2    | 17.4  |      | 18.1  | 0.685 |       | 0.713 |

| L3    | 17.25 | 17.5 | 17.75 | 0.679 | 0.689 | 0.699 |

| L4    | 10.3  | 10.7 | 10.9  | 0.406 | 0.421 | 0.429 |

| L7    | 2.65  |      | 2.9   | 0.104 |       | 0.114 |

| М     | 4.25  | 4.55 | 4.85  | 0.167 | 0.179 | 0.191 |

| M1    | 4.73  | 5.08 | 5.43  | 0.186 | 0.200 | 0.214 |

| S     | 1.9   |      | 2.6   | 0.075 |       | 0.102 |

| S1    | 1.9   |      | 2.6   | 0.075 |       | 0.102 |

| Dia1  | 3.65  |      | 3.85  | 0.144 |       | 0.152 |

7/8

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specification mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics. The ST logo is a registered trademark of STMicroelectronics © 1998 STMicroelectronics – Printed in Italy – All Rights Reserved MULTIWATT® is a Registered Trademark of SGS-THOMSON Microelectronics STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - France - Germany - Italy - Japan - Korea - Malaysia - Malta - Mexico - Morocco - The Netherlands -Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.

http://www.st.com