# LED driver series for automotive lamp

# White LED Driver IC for Automotive lamp (Switching regulator type)

Ver. 0.11

### Description

BD8381EFV-M is a white LED driver with the capability of withstanding high input voltage (50V MAX).

A current-mode buck-boost DC/DC controller is also integrated to achieve stable operation against voltage input and also to remove the constraint of the number of LEDs in series connection.

The brightness can be controlled by either PWM or linear. The PWM brightness signal generation circuit is built into, and the control without microcomputer is also possible.

#### Features

- 1) Input voltage range 5.0 30 V

- 2) Integrated buck-boost current-mode DC/DC controller

- 3) Built-in CR timer for PWM brightness

- 4) PWM linear brightness

- 5) Built-in protection functions (UVLO, OVP, TSD, OCP, SCP)

- 6) LED error status detection function (OPEN/ SHORT)

- 7) HTSSOP-B28 package

#### Applications

Headlight and running (DRL) of night of daylight, etc.

## ● Absolute maximum ratings (Ta=25°C)

| Parameter                                                                                               | Symbol                                                                                                                     | Rating             | Unit |

|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------|------|

| Power supply voltage                                                                                    | Vcc                                                                                                                        | 50                 | V    |

| BOOT Voltage                                                                                            | Vвоот                                                                                                                      | 55                 | V    |

| SW,CS,OUTH Voltage                                                                                      | Vsw, Vcs, Vouth                                                                                                            | 50                 | V    |

| BOOT-SW Voltage                                                                                         | VBOOT-SW                                                                                                                   | 7                  | V    |

| VREG,OVP,OUTL,FAIL1,FAIL2,THM,SS,<br>COMP,RT,SYNC,EN,DISC,VTH,FB,LEDR,<br>LEDC,DRLIN, PWMOUT,CT Voltage | VVREG, VOVP, VOUTL, VFAIL1, VFAIL2, VTHM, VSS, VCOMP, VRT, VSYNCVEN, VDISC, VVTH, VFB, VLEDR, VLEDC, , VDRLIN, VPWMOUT VCT | -0.3~7 < Vcc       | V    |

| Power Consumption                                                                                       | Pd                                                                                                                         | 1.45 <sup>×1</sup> | W    |

| Operating temperature range                                                                             | Topr                                                                                                                       | -40 ~ +125         | °C   |

| Storage temperature range                                                                               | Tstg                                                                                                                       | -55 ~ +150         | °C   |

| Junction temperature                                                                                    | Tjmax                                                                                                                      | 150                | °C   |

<sup>\*1</sup> IC mounted on glass epoxy board measuring 70mm×70mm×1.6mm, power dissipated at a rate of 11.6mW/°C at temperatures above 25°C.

## ●Operating conditions (Ta=25°C)

| <u> </u>                                       |        |              |      |

|------------------------------------------------|--------|--------------|------|

| Parameter                                      | Symbol | Target value | Unit |

| Power supply voltage                           | Vcc    | 5.0 ~ 30     | V    |

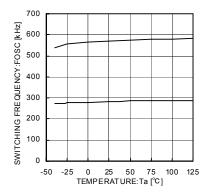

| Oscillating frequency range                    | Fosc   | 100 ~ 600    | kHz  |

| External synchronization frequency range *3 *4 | FSYNC  | fosc ~ 600   | kHz  |

| External synchronization pulse duty range      | FSDUTY | 40 ~ 60      | %    |

<sup>\*3</sup> Connect SYNC to GND or OPEN when not using external frequency synchronization.

<sup>\*2</sup> A radiation is not designed.

<sup>\*4</sup> Do not switch between internal and external synchronization when an external synchronization signal is input to the device.

● Electrical characteristics (unless otherwise specified, VCC=12V Ta=25°C)

| Parameter                                 | Symbol      | Target Value |              | Unit         | Conditions |                                      |

|-------------------------------------------|-------------|--------------|--------------|--------------|------------|--------------------------------------|

| raiailietei                               |             | Min          | Тур          | Max.         | Unit       | Conditions                           |

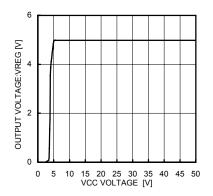

| Circuit current                           | ICC         | -            | 4.5          | 7.0          | mA         | EN=Hi, SYNC=Hi, RT=OPEN,<br>CIN=10µF |

| Standby current                           | IST         | -            | 4            | 8            | μΑ         | EN=Low                               |

| [VREG Block (VREG)]                       |             |              |              |              |            |                                      |

| Reference voltage                         | VREG        | 4.5          | 5.0          | 5.5          | V          | IREG=-5mA, CREG=10µF                 |

| [OUTH Block]                              |             |              |              |              |            |                                      |

| OUTH high-side ON resistance              | RONHH       | 1.5          | 3.5          | 7.0          | Ω          | ION=-10mA                            |

| OUTH low-side ON resistance               | RONHL       | 1.0          | 2.5          | 5.0          | Ω          | ION=10mA                             |

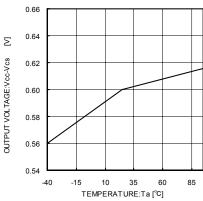

| Over-current protection operating voltage | VOLIMIT     | VCC<br>-0.66 | VCC<br>-0.60 | VCC<br>-0.54 | V          |                                      |

| [OUTL Block]                              |             |              |              |              |            | 1                                    |

| OUTL high-side ON resistance              | RONLH       | 2.0          | 4.0          | 6.0          | Ω          | ION=-10mA                            |

| OUTL low –side ON resistance              | RONLL       | 1.0          | 2.5          | 4.0          | Ω          | ION=10mA                             |

| [SW Block]                                |             | 1            | 11           | 1            | I          | I                                    |

| SW low -side ON resistance                | RONSW       | 2.0          | 4.5          | 9.0          | Ω          | IONSW=10mA                           |

| [PWMOUT Block]                            | ·           |              |              |              |            | •                                    |

| PWMOUT high-side ON resistance            | RONPWMH     | 2.0          | 4.0          | 6.0          | Ω          | IONPWMH=-10mA                        |

| PWMOUT low-side ON resistance             | RONPWML     | 1.0          | 2.5          | 5.0          | Ω          | IONPWML=10mA                         |

| [Error Amplifier Block]                   |             |              |              |              |            |                                      |

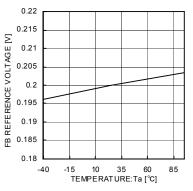

| Reference voltage                         | VREF2       | 0.190        | 0.200        | 0.210        | V          | FB-COMPShort, Ta=-40°C~125°C         |

| COMP sink current                         | ICOMPSINK   | 50           | 75           | 100          | μΑ         | VFB>0.2V, Vcomp=1V                   |

| COMP source current                       | ICOMPSOURCE | -100         | -75          | -50          | μΑ         | VFB <0.2V, Vcomp=1V                  |

| [Oscillator Block]                        |             |              |              |              |            |                                      |

| Oscillating frequency                     | FOSC        | 285          | 300          | 315          | KHz        | RT=100kΩ                             |

| [OVP Block]                               |             |              |              |              |            |                                      |

| Over-voltage detection reference voltage  | VOVP        | 1.9          | 2.0          | 2.1          | V          | VOVP=Sweep up                        |

| OVP hysteresis width                      | VOHYS       | 0.45         | 0.55         | 0.65         | V          | VOVP= Sweep down                     |

| [UVLO Block ]                             |             |              |              |              |            |                                      |

| UVLO voltage                              | VUVLO       | 4.0          | 4.3          | 4.6          | V          | VCC : Sweep down                     |

| UVLO hysteresis width                     | VUHYS       | 50           | 150          | 250          | mV         | VCC : Sweep up                       |

| [PWM Generation circuit Block]            |             |              |              |              |            |                                      |

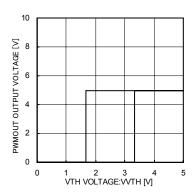

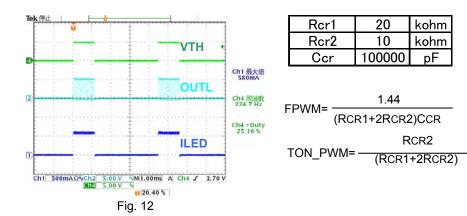

| VTH Threshold voltage                     | VTH1        | 3            | 2/3VREG      | 3.7          | V          |                                      |

| VTH Threshold voltage                     | VTH2        | 1            | 1/3 VREG     | 2            | V          |                                      |

| PWM minimum ON width                      | TPWMON      | 25           | -            | -            | μs         |                                      |

| LED OPEN detection function               | VOPEN       | 30           | 50           | 70           | mV         |                                      |

| LED SHORT detection function              | VSHORT      | 50           | 200          | 400          | mV         | VSHORT≧IVLEDR-VLEDCI                 |

| LED GND short protection timer            | TSHORT      | 100          | 140          | 180          | ms         | CT=0.1uF                             |

| [Logic Inputs]                            |             |              |              |              |            |                                      |

| Input HIGH voltage                        | VINH        | 3.0          | -            | -            | V          |                                      |

| Input LOW voltage                         | VINL        | GND          | -            | 1.0          | V          |                                      |

| Input current 1                           | IIN         | 20           | 35           | 50           | μΑ         | VIN=5V (SYNC/DRLIN)                  |

| Input current 2                           | IEN         | 25           | 40           | 55           | μΑ         | VEN=5V (EN)                          |

| [FAIL Output (open drain) ]               |             |              |              |              |            |                                      |

| FAIL LOW voltage                          | VOL         | _            | 0.1          | 0.2          | V          | IOL=0.1mA                            |

O This product is not designed for use in radioactive environments.

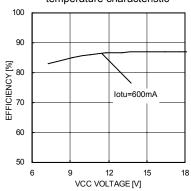

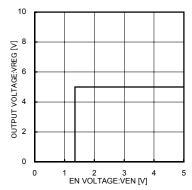

## ●Electrical characteristic curves (Reference data)

(unless otherwise specified, Ta=25°C)

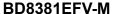

Fig.1 VREG Temperature characteristic

Fig.4 Circuit current (Switching OFF)

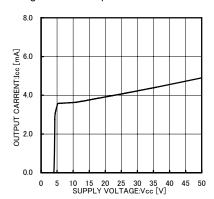

Fig.7 THM Gain

Fig.2 OSC Temperature characteristic

Fig.5 Overcurrent detection voltage temperature characteristic

Fig.8 VTH Threshold voltage

Fig.3 Standard voltage temperature characteristic

Fig.6 Efficiency (Input voltage dependence)

Fig.9 EN Threshold voltage

Technical Note

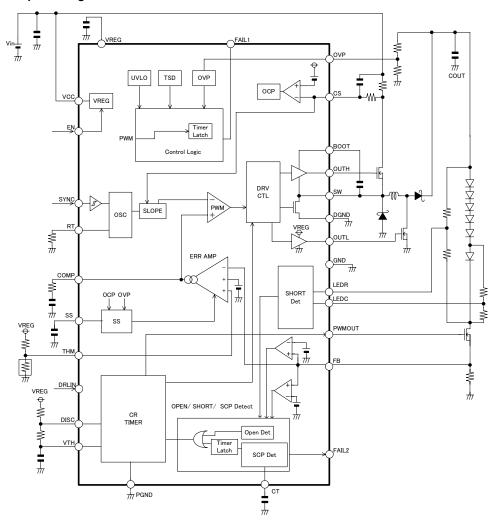

# ●Block diagram and pin configuration

Fig.10 Buck-boost application composition

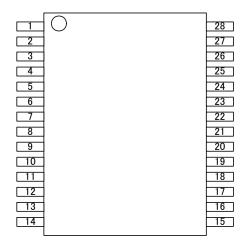

# • Pin layout

BD8381EFV-M (HTSSOP-B28)

## • Pin function table

| Pin | Symbol | Function                                           |

|-----|--------|----------------------------------------------------|

| 1   | COMP   | Error amplifier output                             |

| 2   | SS     | Soft start                                         |

| 3   | VCC    | Input power supply                                 |

| 4   | EN     | Enable input                                       |

| 5   | RT     | Oscillation frequency-setting resistance input     |

| 6   | SYNC   | External synchronization signal input              |

| 7   | GND    | Small-signal GND                                   |

| 8   | THM    | Thermally sensitive resistor connection pin        |

| 9   | FB     | ERRAMP FB signal input pin                         |

| 10  | DISC   | CR Timer discharge pin                             |

| 11  | VTH    | CR Timer threshold pin                             |

| 12  | DRLIN  | DRL switch terminal (Pulse output setting terminal |

| 13  | FAIL1  | Failure signal output                              |

| 14  | FAIL2  | LED open/short detection signal output             |

| 15  | OVP    | Over-voltage detection input                       |

| 16  | LEDC   | LED short detection pin (LED detection side)       |

| 17  | LEDR   | LED short detection pin (Resistor detection side)  |

| 18  | N.C.   | -                                                  |

| 19  | PGND   | PWM brightness source pin                          |

| 20  | PWMOUT | PWM brightness signal output pin                   |

| 21  | СТ     | GND short protection timer setting pin             |

| 22  | OUTL   | Low-side external FET Gate Drive out put           |

| 23  | DGND   | Low-side FET driver source pin                     |

| 24  | SW     | High-side FET Source pin                           |

| 25  | OUTH   | High-side external FET Gate Drive out put          |

| 26  | CS     | DC/DC output current detection pin                 |

| 27  | BOOT   | High-side FET driver source pin                    |

| 28  | VREG   | Internal reference voltage output                  |

Fig.11

Technical Note

$\times 100$

#### • 5V voltage reference (VREG)

5V (Typ.) is generated from the VCC input voltage when the enable pin is set high. This voltage is used to power internal circuitry, as well as the voltage source for device pins that need to be fixed to a logical HIGH.

UVLO protection is integrated into the VREG pin. The voltage regulation circuitry operates uninterrupted for output voltages higher than 4.5 V (Typ.), but if output voltage drops to 4.3 V (Typ.) or lower, UVLO engages and turns the IC off.

Connect a capacitor (Creg = 10uF Typ.) to the VREG terminal for phase compensation. Operation may become unstable if Creg is not connected.

## • About the method of setting the output current

ILED=min[THM / 5 V , 0.2V] / RISET [A]

As for min[THM / 5 V, 0.2V], small one is selected from among THM and VFB=0.2V.

Please input within the range of 0.05-0.2V when controlling the output current with THM. Please connect with VREG when not using THM. There is a possibility that the LED GND short detection malfunctions when THM≦50mV.

As for PWM brightness, the control by the PWM signal from the outside and brightness with the CR timer are possible.

### About Dirating of the LED current that uses THM

It is an ability to set the Dirating curve of the LED current to the temperature as one of the functions to use THM. As for LED, because deterioration at the high temperature is fast, the maximum allowance LED currents and the curve of temperatures is given to the data sheet of LED. The voltage with a negative temperature characteristic in THM the Thermistor resistance is used is input, and the LED current is controlled when the LED current is controlled according to the temperature characteristic. Moreover, external Tr is used, and two input composition is also possible.

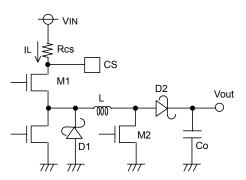

#### • Buck-Boost DC/DC controller

## · Over-voltage protection circuit (OVP)

The output of the DCDC converter should be connected to the OVP pin via a voltage divider. In determining an appropriate trigger voltage of for OVP function, consider the total number of LEDs in series and the maximum variation in VF. Also, bear in mind that over-current protection (OCP) is triggered at 0.85 x OVP trigger voltage. If the OVP function engages, it will not release unless the DCDC voltage drops to 72.5% of the OVP trigger voltage. For example, if ROVP1 (out put voltage side), ROVP2 (GND side), and DCDC voltage VOUT are conditions for OVP, then:  $VOUT \ge (ROVP1 + ROVP2) / ROVP2 \times 2.0 \text{ V}$ . OVP will engage when  $VOUT \ge 32 \text{ V}$  if  $ROVP1 = 330 \text{ k}\Omega$  and  $ROVP2 = 22 \text{ k}\Omega$ .

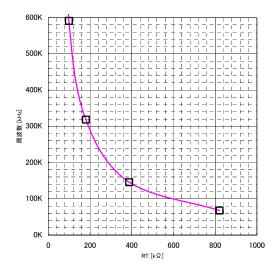

#### Buck-boost DC/DC converter oscillation frequency (FOSC)

The regulator's internal triangular wave oscillation frequency can be set via a resistor connected to the RT pin (pin 5). This resistor determines the charge/discharge current to the internal capacitor, thereby changing the oscillating frequency. Refer to the following theoretical formula when setting RT:

$$fosc = \frac{60 \times 10^6}{RT [\Omega]} \times \alpha [kHz]$$

$60 \times 10^6$  (V/A/S) is a constant (±5%) determined by the internal circuitry, and  $\alpha$  is a correction factor that varies in relation to RT: {RT:  $\alpha$  = 50k $\Omega$ : 0.98, 60k $\Omega$ : 0.985, 70k $\Omega$ : 0.99, 80k $\Omega$ : 0.994, 90k $\Omega$ : 0.996, 100k $\Omega$ : 1.0, 150k $\Omega$ : 1.01, 200k $\Omega$ : 1.02, 300k $\Omega$ : 1.03, 400k $\Omega$ : 1.04, 500k $\Omega$ : 1.045} A resistor in the range of 62.6k $\Omega$  ~ 523k $\Omega$  is recommended. Settings that deviate from the frequency range shown below may cause switching to stop, and proper operation cannot be guaranteed.

Fig.13 RT versus switching frequency

## External DC/DC converter oscillating frequency synchronization (FSYNC)

Do not switch from external to internal oscillation of the DC/DC converter if an external synchronization signal is present on the SYNC pin. When the signal on the SYNC terminal is switched from high to low, a delay of about 30  $\mu$ s (typ.) occurs before the internal oscillation circuitry starts to operate (only the rising edge of the input clock signal on the SYNC terminal is recognized). Moreover, the external synchronizing signal is given to priority when an external input frequency is used. There is a possibility of oscillating when the internal oscillation frequency is low, and an external oscillatory frequency is high. Please set to RT=100kohm when you use an external oscillatory frequency.

#### · Soft Start Function

The soft-start (SS) limits the current and slows the rise-time of the output voltage during the start-up, and hence leads to prevention of the overshoot of the output voltage and the inrush current. The SS voltage is made Low when OVP of the overcurrent and the excess voltage is detected, and the switching is stopped. Resume operation is begun.

6/20

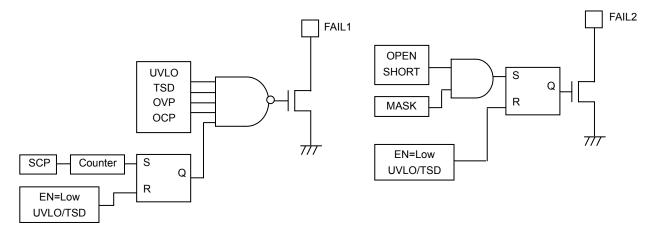

### · Self-diagnostic functions

The operating status of the built-in protection circuitry is propagated to FAIL1 and FAIL2 pins (open-drain outputs). FAIL1 becomes low when UVLO, TSD, OVP, or SCP protection is engaged, whereas FAIL2 becomes low when open or short LED is detected.

### · Operation of the Protection Circuitry

Under-Voltage Lock Out (UVLO)

The UVLO shuts down all the circuits other than REG when VREG ≤ 4.3V (TYP).

· Thermal Shut Down (TSD)

The TSD shuts down all the circuits other than REG when the Tj reaches 175°C (TYP), and releases when the Tj becomes below 150°C (TYP).

· Over Current Protection (OCP)

The OCP detects the current through the power-FET by monitoring the voltage of the high-side resistor, and activates when the CS voltage becomes less than VCC-0.6V (TYP).

When the OCP is activated, the external capacitor of the SS pin becomes discharged and the switching operation of the DCDC turns off.

· Over Voltage Protection (OVP)

The output voltage of the DCDC is detected with the OVP-pin voltage, and the protection activates when the OVP-pin voltage becomes greater than 2.0V (TYP).

When the OVP is activated, the external capacitor of the SS pin becomes discharged and the switching operation of the DCDC turns off.

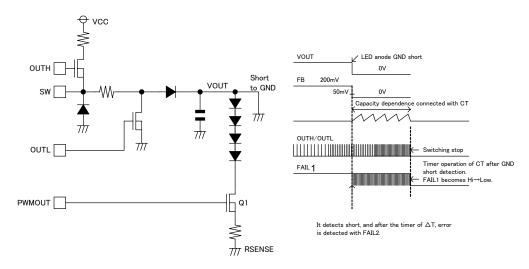

## · Short Circuit Protection (SCP)

When the FB-pin voltage becomes less than 0.05V (TYP), the internal counter starts operating and latches off the circuit approximately after 140ms (when CT = 0.1uF). If the FB-pin voltage becomes over 0.05V before 140ms, then the counter resets.

When the LED anode (i.e. DCDC output voltage) is shorted to ground, then the LED current becomes off and the FB-pin voltage becomes low. Furthermore, the LED current also becomes off when the LED cathode is shorted to ground. Hence in summary, the SCP works with both cases of the LED anode and the cathode being shorted.

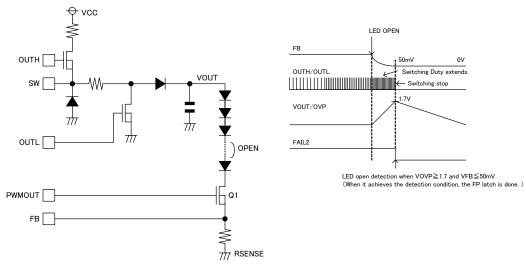

#### LED Open Detection

When the LED-pin voltage  $\leq$  0.05V (TYP) as well as OVP-pin voltage  $\geq$  1.7V (TYP) simultaneously, the device detects as LED open and latches off that particular channel.

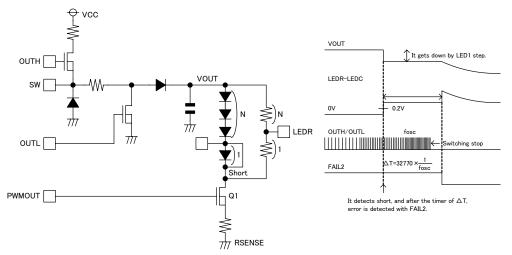

## · LED Short Detection

When the voltage between LEDR-pin and LEDC-pin  $\geq 0.2$  (TYP), the internal counter starts operating, and approximately after 100ms (when FOSC = 300kHz) the operation latches off. With the PWM brightness control, the detecting operation is processed only when PWMOUT-pin = High. If the condition of the detection operation is released before 100ms (when FOSC = 300kHz), then the internal counter resets.

There is a possibility that the LED short detection malfunctions when the difference of Vf is large. Therefore, please adjust external resistance for connected Vf. It is recommended 2V-3V to the input range of LEDR and LEDC.

\* The counter frequency is the DCDC switching frequency determined by the RT. The latch proceeds at the count of 32770.

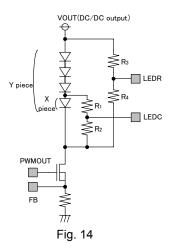

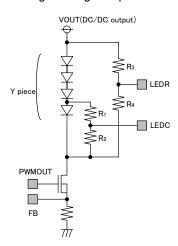

## •High luminance LED (multichip) with built-in LED of X piece in 1chip when using Y piece

Setting method R1 : R2 = X : 1

R3 : R4 = (X + 1)Y - 1 : 1

## •When using the single chip

Fig. 15

Setting method

R1 : R2 = 1 : 1

R3 : R4 = 2Y - 1 : 1

# •Error all condition

| Drataation | Detecting C                                             | Operation offer detect |                                                                 |

|------------|---------------------------------------------------------|------------------------|-----------------------------------------------------------------|

| Protection | [Detect]                                                | [Release]              | Operation after detect                                          |

| UVLO       | VREG<4.3V                                               | VREG>4.45V             | All blocks (but except REG) shut down                           |

| TSD        | Tj>175°C                                                | Tj<150°C               | All blocks (but except REG) shut down                           |

| OVP        | VOVP>2.0V                                               | VOVP<1.45V             | SS discharged                                                   |

| OCP        | VCS≦ VCC-0.6V                                           | VCS>VCC-0.6V           | SS discharged                                                   |

| SCP        | VFB<0.05V<br>(140ms delay when<br>CT=0.1uF)             | EN or UVLO             | Counter starts and then latches off all blocks (but except REG) |

| LED open   | VFB<0.05V<br>& VOVP>1.7V                                | EN or UVLO             | Counter starts and then latches off all blocks (but except REG) |

| LED short  | IVLEDR-VLEDCI>0.2V<br>(100ms delay when<br>FOSC=300kHz) | EN or UVLO             | Counter starts and then latches off all blocks (but except REG) |

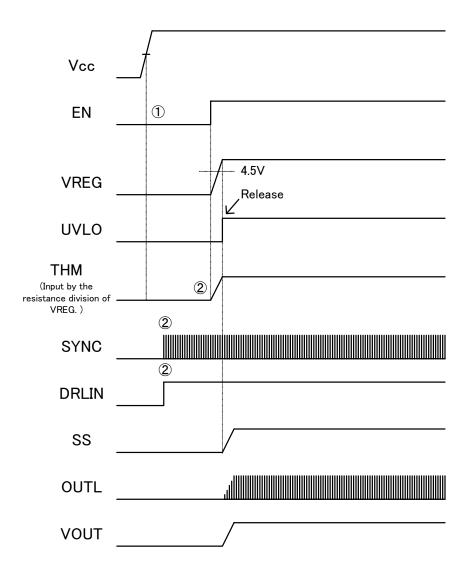

## Protection sequence

Fig.16

Power supply turning on sequence

- ① Please turn on EN with Vcc≥4.5V or more after impressing Vcc.

- 2 Please fix the potential of DRLIN and THM before turning on EN.

- ③ A soft start operates at the same time as turning on EN, and the switching is output.

- After turning on VCC, the order is not related to other input when inputting external PWM from VTH.)

%It leads to the destruction of IC and external parts because it doesn't error output according to an external constant of adjacent pin 24pin SW terminal, 25pin OUTH terminal, 26pin CS terminal and 27pin BOOT terminal.

## Operation in error circumstances of LED

## ① LED open detection

Fig.17

## **2**LED short detection

Fig.18

## 3 LED anode/cathode land GND short detection

Fig.19

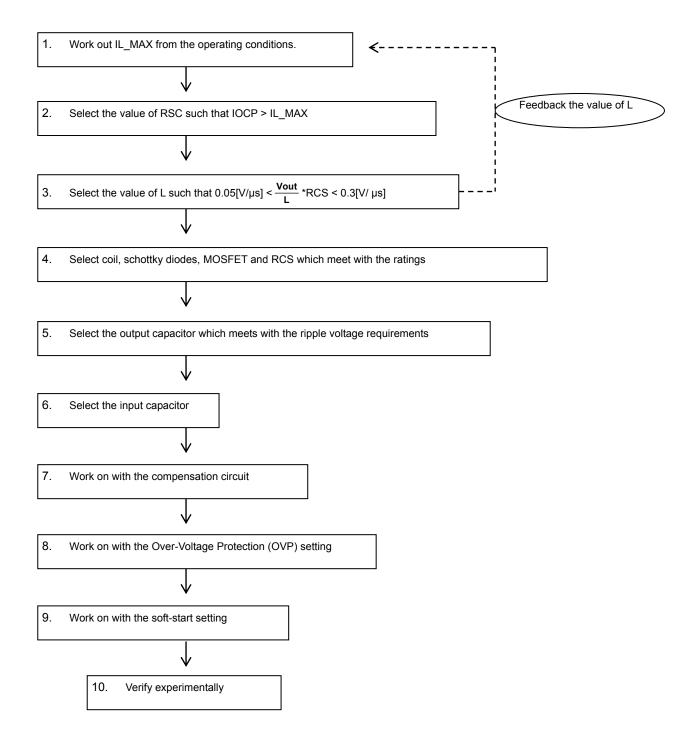

## • Procedure for external components selection

Follow the steps as shown below for selecting the external components

- Computation of the Input Peak Current and IL MAX

- Calculation of the maximum output voltage (Vout\_max)

To calculate the Vout max, it is necessary to take into account of the VF variation and the number of LED connection in

Vout max =  $(VF + \Delta VF) \times N + 0.2 + RPWMON \times lout$

Δ VF: VF Variation N: Number of LED connection in series RPWMON: PWMOUT FET Ron

② Calculation of the output current lout

D: FB standard voltage variation

M: Output current resistance variation

Calculation of the input peak current IL MAX

$$IL_MAX = IL_AVG + 1/2\Delta IL$$

$$IL\_AVG = (VIN + Vout) \times Iout / (n \times VIN)$$

$$\Delta \text{ IL=} \frac{\text{VIN}}{\text{L}} \times \frac{1}{\text{Fosc}} \times \frac{\text{Vout}}{\text{VIN+Vout}}$$

n: efficiency Fosc: switching frequency

- · The worst case scenario for VIN is when it is at the minimum, and thus the minimum value should be applied in the equation.

- · The L value of 10μF ~ 47μF is recommended. The current-mode type of DC/DC conversion is adopted for BD8381EFV-M, which is optimized with the use of the recommended L value in the design stage. This recommendation is based upon the efficiency as well as the stability. The L values outside this recommended range may cause irregular switching waveform and hence deteriorate stable operation.

- n (efficiency) is approximately 80%

Fig.20 External Application Circuit

The setting of over-current protection

Choose Rcs with the use of the equation Vocp\_min (=0.54V) / Rcs > IL\_MAX

When investigating the margin, it is worth noting that the L value may vary by approximately ±30%.

The selection of the L

In order to achieve stable operation of the current-mode DC/DC converter, we recommend selecting the L value in the range indicated below:

$$0.05 \text{ [V/µs]} < \frac{\text{Vout} \times \text{Rcs}}{\text{L}} < 0.3 \text{ [V/µs]}$$

The smaller  $\frac{\text{Vout} \times \text{Rcs}}{\text{I}}$  allows stability improvement but slows down the response time.

Selection of coil L, diode D1 and D2, MOSFET M1 and M2, and Rcs 4.

|           | Current rating | Voltage rating | Heat loss                 |

|-----------|----------------|----------------|---------------------------|

| Coil L    | > IL_MAX       | _              |                           |

| Diode D1  | > locp         | > VIN_MAX      |                           |

| Diode D2  | > locp         | > Vout         |                           |

| MOSFET M1 | > locp         | > VIN_MAX      |                           |

| MOSFET M2 | > locp         | > Vout         |                           |

| Rcs       | _              | _              | > locp <sup>2</sup> × Rcs |

- Allow some margin, such as the tolerance of the external components, when selecting. Ж

- In order to achieve fast switching, choose the MOSFETs with the smaller gate-capacitance. Ж

#### 5. Selection of the output capacitor

Select the output capacitor Cout based on the requirement of the ripple voltage Vpp.

$$Vpp = \frac{lout}{Cout} \times \frac{Vout}{Vout+VIN} \times \frac{1}{Fosc} + IL_MIN \times RESR$$

Choose Cout that allows the Vpp to settle within the requirement. Allow some margin also, such as the tolerance of the external components.

### 6. Selection of the input capacitor

A capacitor at the input is also required as the peak current flows between the input and the output in DC/DC conversion. We recommend an input capacitor greater than  $10\mu F$  with the ESR smaller than  $100m\Omega$ . The input capacitor outside of our recommendation may cause large ripple voltage at the input and hence lead to malfunction.

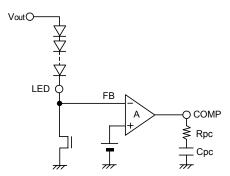

#### 7. Phase Compensation Guidelines

In general, the negative feedback loop is stable when the following condition is met:

• Overall gain of 1 (0dB) with a phase lag of less than 150° (i.e., a phase margin of 30° or more)

However, as the DC/DC converter constantly samples the switching frequency, the gain-bandwidth (GBW) product of the entire series should be set to 1/10 the switching frequency of the system. Therefore, the overall stability characteristics of the application are as follows:

- Overall gain of 1 (0dB) with a phase lag of less than 150° (i.e., a phase margin of 30° or more)

- GBW (frequency at gain 0dB) of 1/10 the switching frequency

Thus, to improve response within the GBW product limits, the switching frequency must be increased.

The key for achieving stability is to place fz near to the GBW. GBW is decided by phase delay fp1 by COUT and output impedance RL. Of each becomes like the next expression.

Phase-lead fz =

$$\frac{1}{2\pi \text{ CpcRpc}}$$

[Hz]

Phase-lag fp1 =  $\frac{1}{2\pi \text{ RLCout}}$  [Hz]

Good stability would be obtained when the fz is set between 1kHz ~ 10kHz.

Please substitute the value at the maximum load for RL.

In buck-boost applications, Right-Hand-Plane (RHP) Zero exists. This Zero has no gain but a pole characteristic in terms of phase. As this Zero would cause instability when it is in the control loop, so it is necessary to bring this zero before the GBW.

It is important to keep in mind that these are very loose guidelines, and adjustments may have to be made to ensure stability in the actual circuitry. It is also important to note that stability characteristics can change greatly depending on factors such as substrate layout and load conditions. Therefore, when designing for mass-production, stability should be thoroughly investigated and confirmed in the actual physical design.

Technical Note

## 8. Setting of the soft-start

The soft-start allows minimization of the coil current as well as the overshoot of the output voltage at the start-up.

For the capacitance we recommend in the range of  $0.001 \sim 0.1 uF$ . For the capacitance less than 0.001 uF may cause overshoot of the output voltage. For the capacitance greater than 0.1 uF may cause massive reverse current through the parasitic elements of the IC and damage the whole device. In case it is necessary to use the capacitance greater than 0.1 uF, ensure to have a reverse current protection diode at the Vcc or a bypass diode placed between the SS-pin and the Vcc.

Soft-start time TSS

TSS = CSSX0.7V / 5uA [s] CSS: The capacitance at the SS-pin

## 9. Verification of the operation by taking measurements

The overall characteristic may change by load current, input voltage, output voltage, inductance, load capacitance, switching frequency, and the PCB layout. We strongly recommend verifying your design by taking the actual measurements.

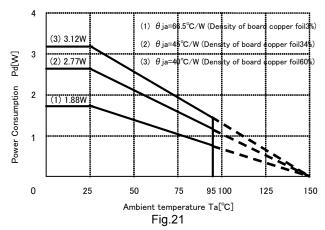

## Power consumption calculation

$Pc(N) = ICC*VCC + \frac{1}{2}*Ciss*VREG*Fsw*VREG \times 2 \times 2 + \frac{1}{2} \times Ciss \times VREG \times F_{PWM} \times VREG \times 2$

ICC: Current of the maximum circuit

VCC : Power-supply voltage

Ciss : External FET capacity

Vsw : SW gate voltage

Fsw : SW frequency

FPWM : PWM frequency

## <Calculation example>

When assuming

$Pc(4) = 10mA \times 30V + 500pF \times 5V \times 300kHz \times 5V \times 2 \times 2 + \frac{1}{2} \times 1500pF \times 5 \times 200 \times 5 \times 2,$

#### it becomes

Pc = about 300mW.

Note 1 : The value of Power consumption : on glass epoxy board measuring  $70\text{mm} \times 70\text{mm} \times 1.6\text{mm}$

(1 layer board ∕ Copper foil thickness 18µm)

Note 2: The value changes depending on the density of the board copper foil.

However, this value is an actual measurement value and no guarantee value.

Pd=2200mW (968mW) : Density of the board copper foil 3% Pd=3200mW (1408mW) : Density of the board copper foil 34%

Pd=3500mW (1540mW): Density of the board copper foil 60% The value in () is a Power consumption of the Ta=125°C.

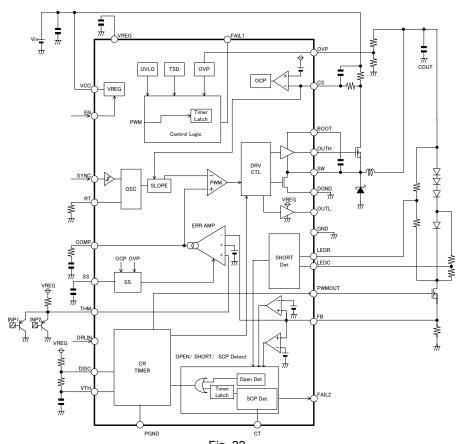

## Application circuit 1

$\label{eq:Fig.22} \textit{Buck application composition (It is INP1, INP2, and two input selector function.)}$

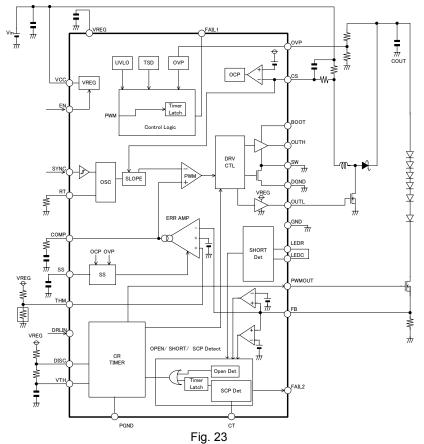

# Application circuit 2

Boost application composition (When invalidating short detection.)

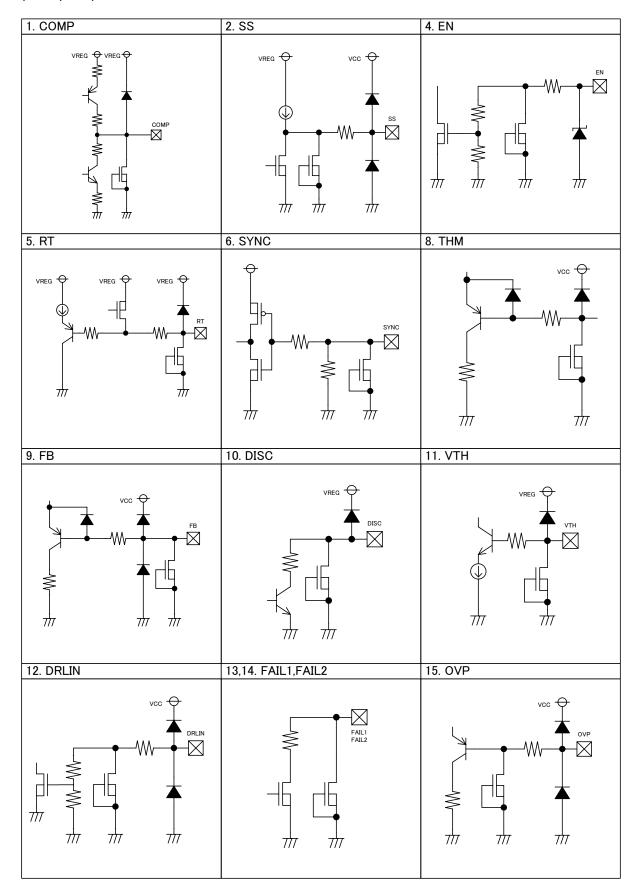

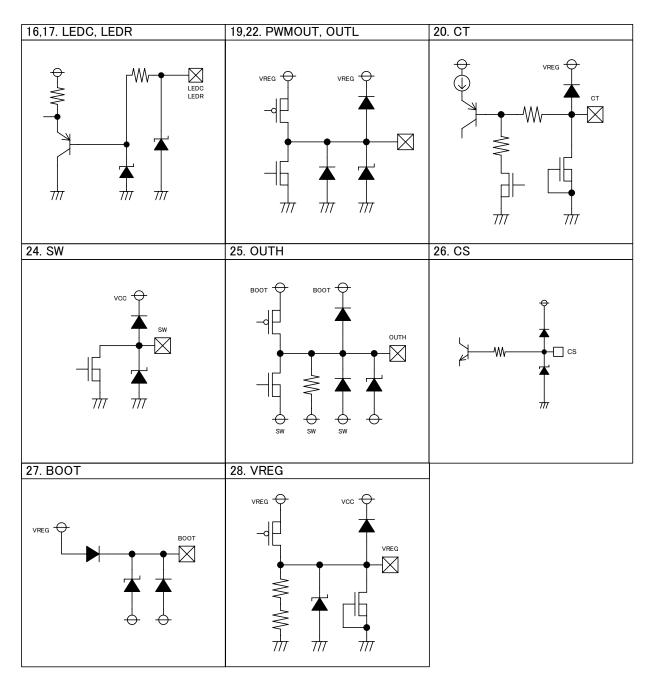

# ●Input/output Equivalent Circuits

%The values are all Typ. value.

# ●Input/output Equivalent Circuits(Continuation)

XThe values are all Typ. value.

#### Notes for use

#### 1. Absolute maximum ratings

We are careful enough for quality control about this IC. So, there is no problem under normal operation, excluding that it exceeds the absolute maximum ratings. However, this IC might be destroyed when the absolute maximum ratings, such as impressed voltages or the operating temperature range(Topr), is exceeded, and whether the destruction is short circuit mode or open circuit mode cannot be specified. Please take into consideration the physical countermeasures for safety, such as fusing, if a particular mode that exceeds the absolute maximum rating is assumed.

#### 2. Reverse polarity connection

Connecting the power line to the IC in reverse polarity (from that recommended) will damage the part. Please utilize the direction protection device as a diode in the supply line.

#### 3. Power supply line

Due to return of regenerative current by reverse electromotive force, using electrolytic and ceramic suppress filter capacitors (0.1µF) close to the IC power input terminals (Vcc and GND) are recommended. Please note the electrolytic capacitor value decreases at lower temperatures and examine to dispense physical measures for safety.

And, for ICs with more than one power supply, it is possible that rush current may flow instantaneously due to the internal powering sequence and delays. Therefore, give special consideration to power coupling capacitance, width of power wiring, GND wiring, and routing of wiring. Please make the power supply lines (where large current flow) wide enough to reduce the resistance of the power supply patterns, because the resistance of power supply pattern might influence the usual operation.

#### 4. GND line

The ground line is where the lowest potential and transient voltages are connected to the IC.

#### 5. Thermal design

Do not exceed the power dissipation (Pd) of the package specification rating under actual operation, and please design enough temperature margins.

#### 6. Short circuit mode between terminals and wrong mounting

Do not mount the IC in the wrong direction and be careful about the reverse-connection of the power connector. Moreover, this IC might be destroyed when the dust short the terminals between them or power supply, GND.

#### 7. Radiation

Strong electromagnetic radiation can cause operation failures.

#### 8. ASO(Area of Safety Operation.)

Do not exceed the maximum ASO and the absolute maximum ratings of the output driver.

#### 9. TSD(Thermal shut-down)

The TSD is activated when the junction temperature (Tj) reaches 175°C(with 25°C hysteresis), and the output terminal is switched to Hi-z. The TSD circuit aims to intercept IC from high temperature. The guarantee and protection of IC are not purpose. Therefore, please do not use this IC after TSD circuit operates, nor use it for assumption that operates the TSD circuit.

#### 10. Inspection by the set circuit board

The stress might hang to IC by connecting the capacitor to the terminal with low impedance. Then, please discharge electricity in each and all process. Moreover, in the inspection process, please turn off the power before mounting the IC, and turn on after mounting the IC. In addition, please take into consideration the countermeasures for electrostatic damage, such as giving the earth in assembly process, transportation or preservation.

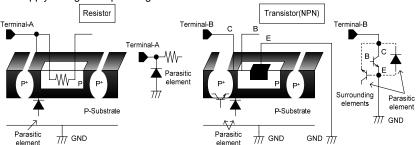

## 11. IC terminal input

This IC is a monolithic IC, and has P<sup>+</sup> isolation and P substrate for the element separation. Therefore, a parasitic PN junction is firmed in this P-layer and N-layer of each element. For instance, the resistor or the transistor is connected to the terminal as shown in the figure below. When the GND voltage potential is greater than the voltage potential at Terminals A or B, the PN junction operates as a parasitic diode. In addition, the parasitic NPN transistor is formed in said parasitic diode and the N layer of surrounding elements close to said parasitic diode. These parasitic elements are formed in the IC because of the voltage relation. The parasitic element operating causes the wrong operation and destruction. Therefore, please be careful so as not to operate the parasitic elements by impressing to input terminals lower voltage than GND(P substrate). Please do not apply the voltage to the input terminal when the power-supply voltage is not impressed. Moreover, please impress each input terminal lower than the power-supply voltage or equal to the specified range in the guaranteed voltage when the power-supply voltage is impressing.

Simplified structure of IC

## 12. Earth wiring pattern

Use separate ground lines for control signals and high current power driver outputs. Because these high current outputs that flows to the wire impedance changes the GND voltage for control signal. Therefore, each ground terminal of IC must be connected at the one point on the set circuit board. As for GND of external parts, it is similar to the above-mentioned