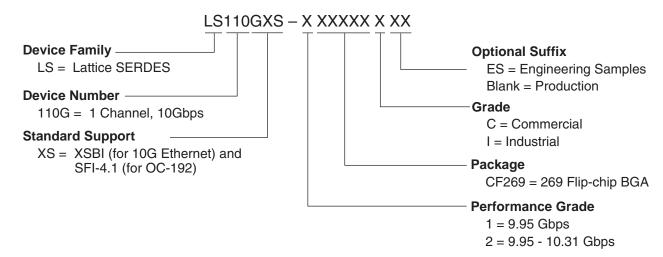

## XPIO 110GXS

Fully Integrated 10Gbps Serializer/Deserializer Device

August 2004 Data Sheet

### **Features**

- Single chip SERDES solution with integrated transmitter and receiver

- Continuous serial operation range from 9.95 Gbps to 10.31 Gbps

- Parallel LVDS data range from 622 Mbps to 644 Mbps

- Low power consumption (800 mW typical)

- Performs 16:1 serialization and 1:16 deserialization

- Embedded Limiting Amplifier enhances receiver sensitivity

- Low-jitter PLL for clock generation

- On-chip Clock Data Recovery circuit

- On-chip FIFO to decouple transmit clocks

- Bit order swap for 10GE operations

- Programmable 4-phase LVDS clock output for easy system design

- Repeating serial data output

- Line loopback, diagnostic loopback, and simultaneous loopback modes

- **■** Frequency Lock Alarm Output

- Programmable differential output swing on both Serial driver and Parallel LVDS driver

- 1.3V core voltage and 2.5V I/O voltage

- Supports 10GE (10-Gigabit Ethernet), OC-192, XFP, XSBI and SFI-4.1 interfaces

- 269-pin flip-chip BGA (15 x 15 mm body size, 0.8 mm pitch)

- -40 to 85°C operating temperature

### **General Description**

The XPIO<sup>™</sup> 110GXS is a fully integrated 10 Gbps serializer/deserializer device designed for high-speed switches and routers that require very low power budget and a small footprint as well. Centering on 10 Gbps speed, the XPIO 110GXS is a versatile chip that is capable of handling applications in various standards, such as OC-192 (9.95 Gbps) and 10GE (10.31 Gbps).

An on-chip low jitter PLL generates all required clocks based on an external reference clock at 1/16 or 1/64 frequency of the serial data rate, which is 622.08 MHz or 155.52 MHz, respectively, for OC-192 applications. An Integrated Limiting Amplifier allows flexibility in placement and reduced bit-error rates (BER).

Fabricated with state-of-the-art CMOS technology, the XPIO 110GXS performs all necessary functions for serial-to-parallel and parallel-to-serial conversions, and consumes less than one third of the power consumed by the more conventional SiGe Bi-CMOS designs.

### **Overview**

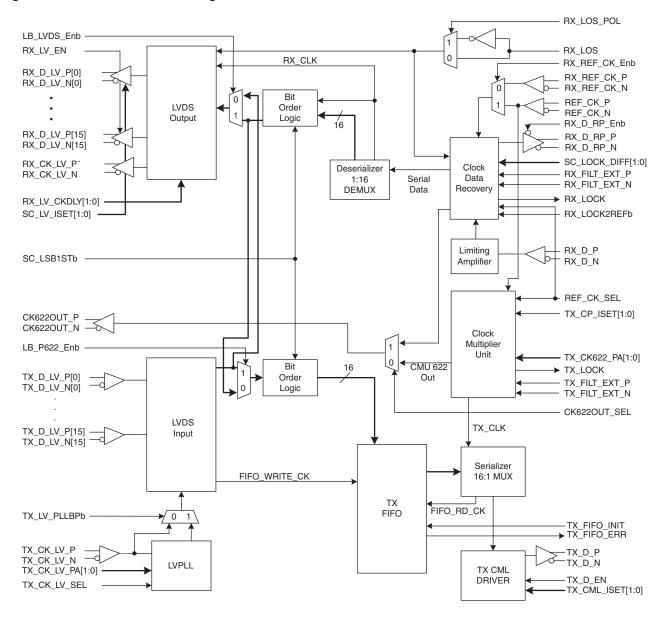

The XPIO 110GXS consists primarily of blocks of parallel-to-serial and serial-to-parallel functions plus system timing. Low Voltage Differential Signaling (LVDS) is used for parallel signal input and output while Current Mode Logic (CML) is used for serial transmission and reception. A limiting amplifier is designed into the chip to improve serial receiver sensitivity. The system timing blocks consist of the clock-multiplier-unit (CMU), LVPLL (LVDS interface timing Phase-Lock-Loop) and CDR (clock-data-recovery) units, which generate clocks for the chip. Figure 1 shows the XPIO 110GXS chip block diagram.

Table 1. XPIO 110GXS Supported Protocols

| Device      | Standards Supported | Data Rate               |

|-------------|---------------------|-------------------------|

| XPIO 110GXS | OC-192<br>10GE      | 9.95 Gbps<br>10.31 Gbps |

Figure 1. XPIO 110GXS Block Diagram

The XPIO 110GXS is divided into a transmitter section and a receiver section. The major operations performed by the chip are:

### **Transmitter Operation**

- 1. Low jitter clock generation via the Clock-Multiplier-Unit (CMU)

- 2. 16-bit LVDS parallel data input

- 3. Parallel-to-serial conversion

10Gbps CML serial data output

### **Receiver Operation**

- 1. CML serial input to a limiting amplifier

- 2. Clock and data recovery

- 3. Serial-to-parallel conversion

- 4. 16-bit LVDS parallel data output, with a synchronizing clock output

- 5. Built-in LVDS line loopback, and LVDS diagnostic loopback modes for testing and network diagnosis

### **Functional Description**

The XPIO 110GXS transceiver is a low power, low jitter, and fully integrated serializer/deserializer chip. It operates in the data rate range of 9.95-10.31 Gbps, performs all necessary parallel-to-serial and serial-to-parallel conversions. The chip is suitable for applications utilizing OC-192 and 10GE. The serial interface I/O uses the CML standard while the low speed parallel I/O is based on the LVDS standard. These standards are compliant to both the Optical Interface Forum's SFI-4 standard and the 10GE's XSBI standard. The LVDS parallel I/O can be directly connected to Multi-Standard-Agreement (MSA) 300 systems.

To accommodate bit order differences between OC-192 and 10GE, the XPIO 110GXS provides the capability of bit swapping. The data presented on TX\_D\_LV\_P/N[15] or MSB is transmitted first, followed in order by TX\_D\_LV\_P/N[14] to TX\_D\_LV\_P/N[0] when SC\_LSB1STb is not connected or is connected to a logic high. TX\_D\_LV\_P/N[0] or LSB is transmitted first followed in order by TX\_D\_LV\_P/N[1] to TX\_D\_LV\_P/N[15] when SC\_LSB1STb is connected to a logic low. The parallel receive bus mirrors this behavior. The SC\_LSB1STb unconnected, or at logic high, the first serial bit received is presented on RX\_D\_LV\_P/N[15]. Conversely the first bit received is presented on RX\_D\_LV\_P/N[0] when SC\_LSB1STb is pulled low.

### **Transmitter**

The transmitter performs the serialization process, converting the 16-bit parallel LVDS data stream to a serial data stream at approximately a 10 Gbps data rate. The transmitter consists of a LVDS data receiver, a FIFO, a 16:1 serializer, a low jitter CMU, and a 10Gbps output data driver.

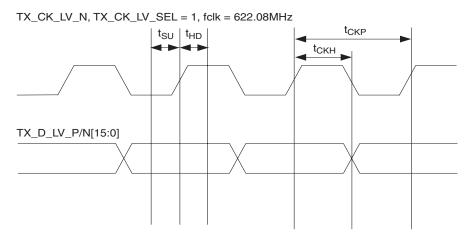

#### LVDS Data Receiver

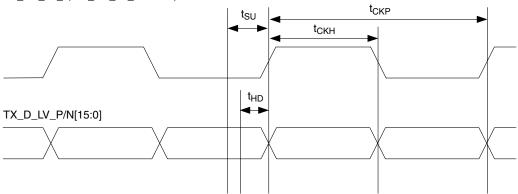

The Input and Analog Pin Assignments and Descriptions table in this document shows the 16 LVDS differential data input pairs (TX\_D\_LV\_P/N [15:0]). Data applied at the transmit data pairs is aligned to the LVDS input clock (TX\_CK\_LV\_P/N), which can be either 1/16th or 1/32nd the transmit data rate (622.08 or 311.04 nominally for OC-192). The clock rate is selected through the assertion or deassertion of the TX\_CK\_LV\_SEL pin. Figure 13 describes the LVDS data relationship to the LVDS input clock.

The LVDS input receivers convert the LVDS signals to CMOS signals. The converted signals are latched based on an internal clock that is generated from the TX\_CK\_LV\_P/N input clock through a phase-lock-loop (LVPLL). In order to achieve optimal latch timing, the phase relationship between the internal clock and the TX\_CK\_LV\_P/N clock can be adjusted by programming TX\_CK\_LV\_PA[1:0]. The LVDS PLL can also be bypassed by the assertion of the TX\_LV\_PLLBPb pin, which is a desirable feature in some applications. When the LVPLL is bypassed it is up to the system designer to manage the TX\_CK\_LV\_P/N input.

### **Transmitter FIFO**

A 16 bit wide and 8-word deep FIFO is designed into the XPIO 110GXS to decouple the LVDS clock from the serial transmission clock. In addition, the FIFO also improves the tolerance to minor phase differences between the FIFO write clock and read clock due to phase drift or phase wander.

The FIFO circuitry indicates an overflow or underflow condition by asserting TX\_FIFO\_ERR high. The TX\_FIFO\_ERR only provides status information about an overflow or underflow. It does not indicate which of the two events actually occurred. During the period of time when the TX\_FIFO\_ERR signal is asserted, the TX\_D\_P/N pins toggle at a constant rate. This prevents the AC coupling capacitors from becoming blocking capacitors.

The transmit FIFO's read and write pointers can be recentered by asserting the TX\_FIFO\_INIT pin high. Thus, one way to automatically recenter the FIFO read/write pointers after TX\_FIFO\_ERR is asserted is to connect TX\_FIFO\_INIT and TX\_FIFO\_ERR together.

The FIFO read/write pointers are re-centered after:

- Device power on reset

- Transmitter reset (asserting RESET\_TXb low)

- CMU PLL is out of lock

#### Serialization

The output data bus from the FIFO feeds a 16:1 serializer to generate a 9.953 Gbps (OC-192 rate) data stream. The high-speed clock (TX\_CLK) is a low jitter clock generated by the CMU. The serializer uses TX\_CLK to clock out high-speed data.

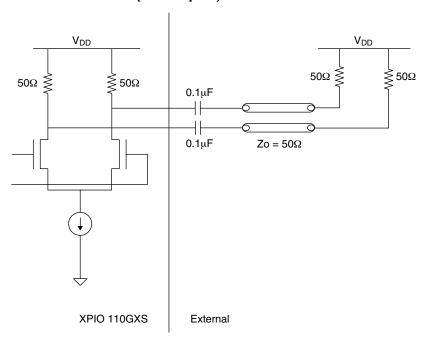

#### TX CML Driver

The serial data stream in turn becomes an input to a differential high-speed CML data driver. The TX\_D CML driver incorporates an internal 50-ohm termination resistor on both P and N branches for impedance matching with the PCB transmission line. The CML output may require AC coupling (as in Figure 5). The output current of the CML driver can be adjusted using two configuration pins, TX\_CML\_ISET[1:0]. These configuration pins are used to balance power consumption and performance.

In normal operation, the data presented at the LVDS TX inputs requires about nine clocks to transit the various logic blocks before being presented at the TX CML driver output.

#### Clock-Multiplier-Unit (CMU)

The CMU consists of a differential PLL that is capable of producing a very low jitter serial clock. The clock is generated through a reference clock (REF\_CLK\_P/N) at either 1/16<sup>th</sup> or 1/64<sup>th</sup> the data transmission rate (This is nominally 622.08 or 155.52 MHz for OC-192 data rates). This reference clock must be generated from a differential crystal oscillator that has a frequency accuracy of better than ±20ppm for SONET applications.

The CMU PLL can provide a phase-adjustable parallel data rate clock (CK622OUT\_P/N) that is 1/16<sup>th</sup> the transmit data rate to clock other devices or systems. The output of CK622OUT\_P/N meets the LVDS signaling specifications. Using the TX\_CK622\_PA[1:0] configuration pins, the phase can be adjusted in T/4 increments, where T is the period of the clock for the parallel interface.

### Receiver

### **Limiting Amplifier**

The XPIO 110GXS 10 Gbps CMOS receiver integrates a highly sensitive limiting amplifier. The XPIO 110GXS also implements an amplifier offset compensation technology that works in conjunction with the limiting amplifier to achieve superior amplifier input sensitivity. Sufficient gain is designed into the limiting amplifier to detect a peak-to-peak differential input as small as 50mV. This attenuated signal can be properly detected and amplified to saturation.

### Clock and Data Recovery (CDR)

One of the most critical circuits in the receiver is the clock and data recovery (CDR) block. The CDR block extracts the clock from an incoming high-speed, non-return to zero (NRZ) data, and retimes the data based on an external reference clock. Extraction of the clock embedded in the serial data-stream is performed through comparison of the phase relationship between transitions of the data and the external reference clock.

The external reference clock is essential for the CDR block. The reference clock provides two functions: One function is training the VCO in the CDR PLL to the serial data-stream frequency. The other is to generate a stable clock when the input serial data is absent. The CDR PLL creates an internal reference frequency. The reference frequency is monitored, and a loss of lock is asserted when it goes out of specification.

#### **Lock Detect**

The XPIO 110GXS implements a CDR lock detector circuit that monitors the frequency of the internal clock. RX\_LOCK is asserted whenever a REF\_CK or RX\_REF\_CK are operating within specification. RX\_LOCK is deasserted under some specific circumstances:

- 1. When RX\_RESETb is asserted (i.e. '0')

- 2. When the REF\_CK (or RX\_REF\_CK) is not present.

- 3. When the clock recovered from the incoming datastream falls outside the range specified by the SC\_LOCK\_DIFF input pins. When the recovered clock is out of range, RX\_LOCK will deassert briefly and then be reasserted as it relocks to the REF\_CK (RX\_REF\_CK). This effectively leaves the RX\_LOCK signal toggling as it attempts to reacquire the clock embedded in the RX\_D\_P/N data inputs.

### Deserialization

The XPIO 110GXS uses a 1:16 demultiplexer to deserialize the high speed data from the CDR. The demultiplexer generates the 16 bit parallel data stream. The bit order presented on the RX\_D\_LV\_P/N[0..15] LVDS outputs mirrors the order on the TX\_D\_LV[0..15]P/N LVDS inputs. The first data bit received by the CDR is present on RX\_D\_LV\_P/N[15] when SC\_LSB1STb is connected to a logic high, and it is present on RX\_D\_LV\_P/N[0] when SC\_LSB1STb is connected to a logic low.

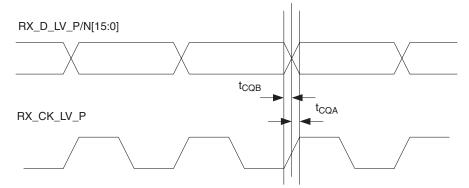

#### **LVDS Data Transmitter**

The 16-bit parallel data and clock are sent out via the RX\_D\_LV\_P/N[0..15] and RX\_LV\_CK\_P/N LVDS pins, respectively. Data on the RX\_D\_LV\_P/N pins is synchronous to the RX\_LV\_CK\_P/N output pins. The data coming in on the RX\_D\_P/N pins requires around five clocks to arrive at the RX\_D\_LV\_P/N outputs. The output current of the LVDS outputs is adjustable using the SC\_LV\_ISET[1:0] configuration pins. System designers can use these pins to optimize the LVDS receive data performance.

#### **XFP Module Considerations**

The XPIO110GXS was conceived and implemented prior to the finalization of the XFP specification. The implication of this is the CML TX voltage swing is typically higher than that specified in the XFP MSA documents.

The XFP MSA specification indicates a XFP module should accept a maximum of 800mV input swing. In practice it is the individual XFP module internal architecture that defines the maximum range. However, most XFP modules simply rate themselves to the 800mV specification regardless of the likelihood they may operate beyond the range specified in the XFP MSA.

Actual operation of the XPIO110GXS with existing XFP modules shows these still operate with the CML swing set to the default TX\_CML\_ISET[1:0] = "11". In order to more closely match the XFP specification a TX\_CML\_ISET[1:0] = "01" configuration is recommended. This places the typical output swing from the CML TX outputs at 650mV to 1100mV.

### **Loopback Operation**

The XPIO 110GXS supports several loopback operations to provide diagnostic functions and to aid in performing SONET/SDH functional tests.

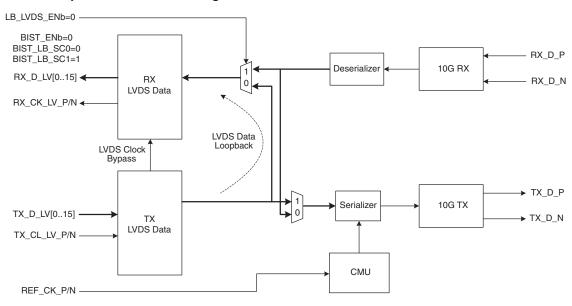

#### LVDS Diagnostic Loopback

In LVDS loopback mode, 16 bit-wide data is fed into the TX LVDS input. The XPIO 110GXS routes data from the LVDS transmit interface to the internal receiver interface, and then repeats the data at the LVDS RX output.

To enable this mode of operation set BIST\_ENb=0, LB\_LVDS\_ENb=0, and BIST\_LB\_SC[1:0]=10.

Figure 2. LVDS Loopback Mode Block Diagram

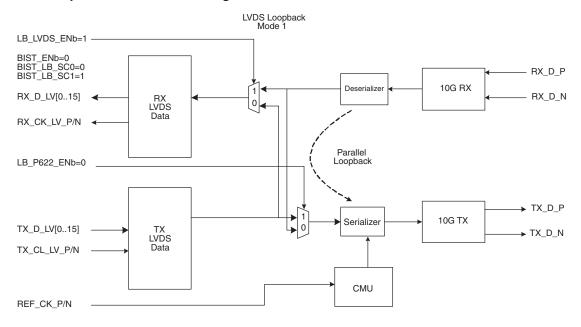

### LVDS Line Loopback

Line loopback is a diagnostic mode that establishes a parallel connection between the output of the deserializer and the input to the serializer. When this mode is active, serial receive data is deserialized, and internally looped back to the serializer. The data provided at the serializer is transmitted via the CML output. Line loopback is activated by setting the LB\_P622\_Enb pin to a logic low.

**Mode 1: Synchronous line loopback without clock clean-up.** Driving LB\_P622\_Enb low enables line loopback mode. Connecting the LVDS output clock, RX\_CK\_LV\_P/N, to REF\_CK\_P/N makes the loopback mode synchronous. In addition, a separate reference clock is input to RX\_REF\_CKP/N for use by the CDR logic. The data transmitted across the TX\_D\_P/N pins is now timed to the LVDS clock making the RX and TX data synchronous. However, the RX\_CK\_LV\_P/N does not require SONET/SDH tolerance in order to transmit the parallel LVDS data. This means the data repeated on TX\_D\_P/N will have significant jitter.

Figure 3. Line Loopback Mode 1 Block Diagram

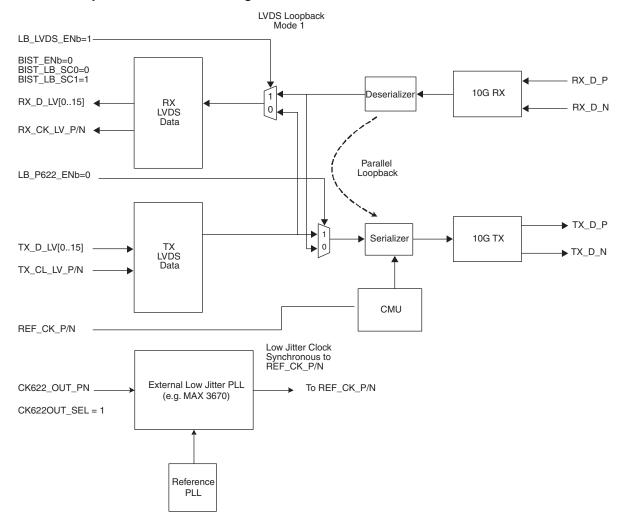

Mode 2: Synchronous line loopback with clock clean-up. Driving LB\_P622\_Enb low enables line loopback mode. In order to make this loopback mode SONET/SDH compliant the CK622OUT\_P/N must be connected to a VCXO-powered PLL chip (e.g. MAX3670), and CK622OUT\_SEL pulled/driven high. The output of the PLL provides a low jitter reference clock that is in phase with the data presented at the LVDS parallel outputs. This reference clock is connected to REF\_CK\_P/N. As in Mode 1 a separate reference clock is input to RX\_REF\_CK\_P/N to drive the CDR logic. Data on the TX\_D\_P/N and RX\_D\_P/N pins are now synchronous, and the data repeated on TX\_D\_P/N meets SONET/SDH line loopback application requirements.

Figure 4. Line Loopback Mode 2 Block Diagram

### Reference Clocks

There are two AC coupled reference clock input pairs, REF\_CK\_P/N, and RX\_REF\_CK\_P/N. The CDR block is driven by either REF\_CK\_P/N or RX\_REF\_CK\_P/N. The CMU block is only driven by REF\_CK\_P/N. The reference clock input frequency for REF\_CK\_P/N can be either 1/16<sup>th</sup> (622MHz) or 1/64<sup>th</sup> (155MHz) the transmitter/receiver data rate. Likewise, RX\_REF\_CK\_P/N can be 1/16<sup>th</sup> or 1/64<sup>th</sup> the 10Gbps receiver rate. RX\_REF\_CK\_P/N and REF\_CK\_P/N are configured in tandem to 1/16<sup>th</sup> or 1/64<sup>th</sup> by REF\_CK\_SEL. They cannot be configured independently. AC coupling for all reference clocks is recommended.

Driving RX\_REF\_CK\_P/N is only necessary when:

- The transmitter and receiver run at independent data rates

- Line Loopback Mode 1 is active

- Line Loopback Mode 2 is active

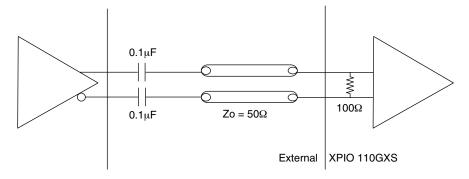

Figure 5 shows how a reference clock is input to the XPIO 110GXS using an AC coupling scheme.

Figure 5. CML Output Driver Termination (AC Coupled)

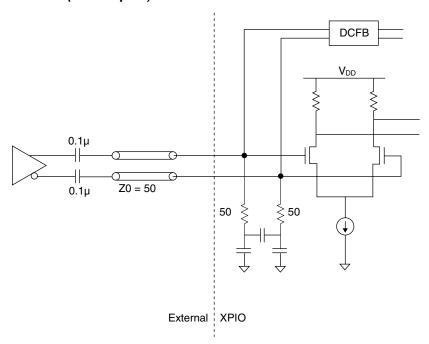

Figure 6. CML Input Receiver (AC Coupled)

Figure 7. Differential Oscillator Driving to XPIO 110GXS Clock Input (AC Coupled)

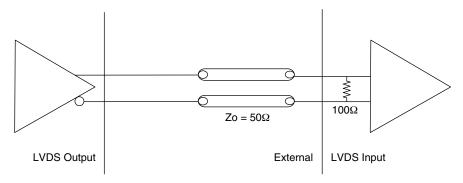

Figure 8. LVDS Output and Input Connection

Figure 9. External Loop Filter Components

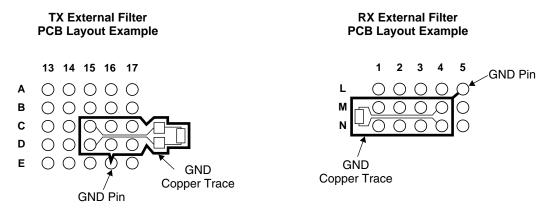

### **PCB Layout Recommendations**

The TX/RX filter components should be small form factor capacitors and resistors. They should be placed as close as possible to the XPIO 110 device.

The TX filter components should be surrounded by a copper trace to GND. As shown below, the RX filter components should be enclosed by the GND.

Figure 10. PCB Layout Examples

**Bottom View**

These diagrams for example purposes only.

## **Electrical Specifications**

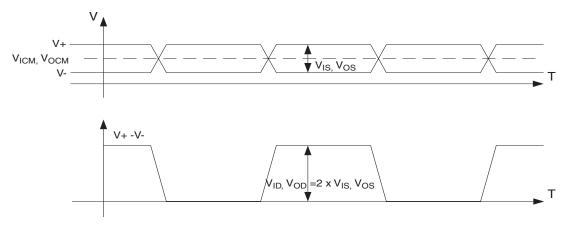

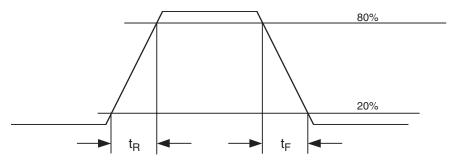

### **AC Signaling Definitions**

Figure 11. Differential Voltage Measurements

Figure 12. Rise and Fall Time Measurements

Figure 13. LVDS Data to Clock Relationship of Transmitter, 1/16<sup>th</sup> of Frequency (622.08MHz for OC-192)

Note: TX\_D\_LV\_P/N[15:0] is latched using the rising edge of TX\_CK\_LV\_N.

Figure 14. LVDS Data to Clock Relationship of Transmitter, 1/32<sup>nd</sup> of Frequency (311.04MHz for OC-192)

$TX\_CK\_LV\_P, TX\_CK\_LV\_SEL = 0, fclk = 311.04MHz$

Figure 15. LVDS Data to Clock Relationship of Receiver

## **Configuration Pin Descriptions**

| Transmitter Controls  TX_D_EN  TX_LV_PLLBPb  TX_FIFO_INIT  TX_CML_ISET[1:0] | 1<br>0<br>1<br>0                | TX_D_P/N output is active  TX_D_P/N output is inactive.  The internal LVDS PLL is active  The internal LVDS PLL is bypassed. External clock management and phase adjustment is required when this pin is 0.  Initialize the TXFIFO |

|-----------------------------------------------------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX_LV_PLLBPb  TX_FIFO_INIT                                                  | 0<br>1<br>0                     | TX_D_P/N output is inactive.  The internal LVDS PLL is active  The internal LVDS PLL is bypassed. External clock management and phase adjustment is required when this pin is 0.                                                   |

| TX_LV_PLLBPb  TX_FIFO_INIT                                                  | 1<br>0<br>1                     | The internal LVDS PLL is active  The internal LVDS PLL is bypassed. External clock management and phase adjustment is required when this pin is 0.                                                                                 |

| TX_FIFO_INIT                                                                | 0                               | The internal LVDS PLL is bypassed. External clock management and phase adjustment is required when this pin is 0.                                                                                                                  |

| TX_FIFO_INIT                                                                | 1                               | phase adjustment is required when this pin is 0.                                                                                                                                                                                   |

|                                                                             |                                 | Initialize the TXFIFO                                                                                                                                                                                                              |

|                                                                             | 0                               |                                                                                                                                                                                                                                    |

| TX_CML_ISET[1:0]                                                            |                                 | No action                                                                                                                                                                                                                          |

| TX_CML_ISET[1:0]                                                            | 11                              |                                                                                                                                                                                                                                    |

| TA_GWIL_IGET[1.0]                                                           | 10                              | See V <sub>OD</sub> in the High Speed Input/Output Specifications section of this                                                                                                                                                  |

|                                                                             | 01                              | data sheet.                                                                                                                                                                                                                        |

| +                                                                           | 00                              |                                                                                                                                                                                                                                    |

|                                                                             | 11                              | 3T/4 <sup>2</sup>                                                                                                                                                                                                                  |

| TV CK622 DA[4:0] <sup>1</sup>                                               | 10                              | Adjust T/2                                                                                                                                                                                                                         |

| TX_CK622_PA[1:0] <sup>1</sup>                                               | 01                              | Adjust T/4                                                                                                                                                                                                                         |

|                                                                             | 00                              | No Adjust                                                                                                                                                                                                                          |

| DECET TVh                                                                   | 1                               | Transmitter in normal operation                                                                                                                                                                                                    |

| RESET_TXb                                                                   | 0                               | Resets the transmitter                                                                                                                                                                                                             |

| DWDN TVb                                                                    | 1                               | Transmitter is operating                                                                                                                                                                                                           |

| PWDN_TXb                                                                    | 0                               | Transmitter is powered down                                                                                                                                                                                                        |

| TV OK IV OF                                                                 | 1                               | TX_CK_LV is 1/16 of frequency                                                                                                                                                                                                      |

| TX_CK_LV_SEL —                                                              | 0                               | TX_CK_LV is 1/32 of frequency                                                                                                                                                                                                      |

| T                                                                           | X_CK_LV_SEL = 1/16 <sup>t</sup> | <sup>h</sup> of Frequency                                                                                                                                                                                                          |

|                                                                             | 11                              | Clock delay = 0                                                                                                                                                                                                                    |

|                                                                             | 10                              | Clock delay = -T/16                                                                                                                                                                                                                |

|                                                                             | 01                              | Clock delay = T/16                                                                                                                                                                                                                 |

| TV OK IV DAI4-01                                                            | 00                              | Clock delay = T/8                                                                                                                                                                                                                  |

| TX_CK_LV_PA[1:0]                                                            | X_CK_LV_SEL = 1/32              | of Frequency                                                                                                                                                                                                                       |

|                                                                             | 11                              | Clock delay = T/4                                                                                                                                                                                                                  |

|                                                                             | 10                              | Clock delay = T/4-T/32                                                                                                                                                                                                             |

|                                                                             | 01                              | Clock delay = T/4+T/32                                                                                                                                                                                                             |

|                                                                             | 00                              | Clock delay = T/4+T/16                                                                                                                                                                                                             |

|                                                                             | 11                              | 622MHz clock (default using internal pull-ups)                                                                                                                                                                                     |

| TV 0D 105T(4.0)                                                             | 10                              | Invalid                                                                                                                                                                                                                            |

| TX_CP_ISET[1:0]                                                             | 01                              | Invalid                                                                                                                                                                                                                            |

|                                                                             | 00                              | 155MHz clock                                                                                                                                                                                                                       |

| Receiver Controls                                                           |                                 |                                                                                                                                                                                                                                    |

| DV DEE OK EV                                                                | 1                               | RX_REF_CK is disabled                                                                                                                                                                                                              |

| RX_REF_CK_ENb —                                                             | 0                               | RX_REF_CK is enabled                                                                                                                                                                                                               |

|                                                                             | 11                              | LVDS output clock is delayed: 90ps                                                                                                                                                                                                 |

| <br>                                                                        | 10                              | LVDS output clock is delayed: 180ps                                                                                                                                                                                                |

| RX_LV_CKDLY[1:0] —                                                          | 01                              | LVDS output clock is delayed: 270ps                                                                                                                                                                                                |

|                                                                             | 00                              | LVDS output clock is delayed: 360ps                                                                                                                                                                                                |

## **Configuration Pin Descriptions (Continued)**

|                                                            | 1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>11<br>10<br>01      | RX_LOS_POL = 0  Asserted by the receiver to indicate it has lost the data signal.  Receiver OK  RX_LOS is an active-low input  RX_LOS is an active-high input.  RX_D_RP_P/N signals are inactived in the recovered received in the receiver received in the receiver to indicate the receiver the receiver to indicate the receiver to indic | eceive data clock.  RX_REF_CK input                                                                       |  |  |  |

|------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|--|--|

| RX_LOS_POL  RX_D_RP_ENb  RX_LOCK2REFb³  SC_LOCK_DIFF[1:0]³ | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>11<br>10<br>01 | cate it has lost the data signal.  Receiver OK  RX_LOS is an active-low input  RX_LOS is an active-high input.  RX_D_RP_P/N signals are inactive  RX_D_RP_P/N signals are active  RX_PLL locks to the recovered re  RX_PLL locks to the REF_CK or  See LOCK_TOL in the High Speed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Asserted by the receiver to indicate it has lost the data signal.  ve eceive data clock.  RX_REF_CK input |  |  |  |

| RX_LOS_POL  RX_D_RP_ENb  RX_LOCK2REFb³  SC_LOCK_DIFF[1:0]³ | 1<br>0<br>1<br>0<br>1<br>0<br>1<br>1<br>0<br>11<br>10<br>01 | RX_LOS is an active-low input RX_LOS is an active-high input. RX_D_RP_P/N signals are inactive. RX_D_RP_P/N signals are active. RX_PLL locks to the recovered re. RX_PLL locks to the REF_CK or. See LOCK_TOL in the High Speed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ve eceive data clock.  RX_REF_CK input                                                                    |  |  |  |

| RX_D_RP_ENb  RX_LOCK2REFb³  SC_LOCK_DIFF[1:0]³             | 0<br>1<br>0<br>1<br>0<br>1<br>1<br>1<br>10<br>01            | RX_LOS is an active-high input.  RX_D_RP_P/N signals are inactive.  RX_D_RP_P/N signals are active.  RX_PLL locks to the recovered recovered recovered recovered recovered.  RX_PLL locks to the REF_CK or  See LOCK_TOL in the High Speed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | eceive data clock.  RX_REF_CK input                                                                       |  |  |  |

| RX_D_RP_ENb  RX_LOCK2REFb³  SC_LOCK_DIFF[1:0]³             | 1<br>0<br>1<br>0<br>11<br>11<br>10                          | RX_D_RP_P/N signals are inactive RX_D_RP_P/N signals are active RX_PLL locks to the recovered re RX_PLL locks to the REF_CK or  See LOCK_TOL in the High Speed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | eceive data clock.  RX_REF_CK input                                                                       |  |  |  |

| RX_LOCK2REFb³  SC_LOCK_DIFF[1:0]³                          | 0<br>1<br>0<br>11<br>10<br>01                               | RX_D_RP_P/N signals are active RX_PLL locks to the recovered re RX_PLL locks to the REF_CK or  See LOCK_TOL in the High Speed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | eceive data clock.  RX_REF_CK input                                                                       |  |  |  |

| RX_LOCK2REFb³  SC_LOCK_DIFF[1:0]³                          | 1<br>0<br>11<br>10<br>01                                    | RX_PLL locks to the recovered re RX_PLL locks to the REF_CK or  See LOCK_TOL in the High Speed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | eceive data clock.  RX_REF_CK input                                                                       |  |  |  |

| SC_LOCK_DIFF[1:0] <sup>3</sup>                             | 0<br>11<br>10<br>01                                         | RX_PLL locks to the REF_CK or  See LOCK <sub>TOL</sub> in the High Speed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | RX_REF_CK input                                                                                           |  |  |  |

| SC_LOCK_DIFF[1:0] <sup>3</sup>                             | 11<br>10<br>01                                              | See LOCK <sub>TOL</sub> in the High Speed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ·                                                                                                         |  |  |  |

|                                                            | 10<br>01                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Input/Output Specifications section of                                                                    |  |  |  |

|                                                            | 01                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Input/Output Specifications section of                                                                    |  |  |  |

|                                                            |                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | p b atpat oppositionio doction of                                                                         |  |  |  |

|                                                            | 00                                                          | T. Control of the Con |                                                                                                           |  |  |  |

|                                                            |                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                           |  |  |  |

| 1                                                          | 11                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                           |  |  |  |

| 10                                                         |                                                             | See VOS in the Low Speed Input/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Output Specifications section of this data                                                                |  |  |  |

| SC_LV_ISET[1:0]                                            | 01                                                          | sheet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                           |  |  |  |

|                                                            | 00                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                           |  |  |  |

| 57.17.57                                                   | 1                                                           | RX_D_LV_P/N[15:0] are enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                           |  |  |  |

| RX_LV_EN                                                   | 0                                                           | RX_D_LV_P/N[15:0] are disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                           |  |  |  |