# **Floating-Point Digital Signal Processor**

Check for Samples: SM320C6727B-EP

### 1 SM320C6727B DSP

### 1.1 Features

- C672x: 32-/64-Bit 250-MHz Floating-Point DSPs

- Upgrades to C67x+ CPU From C67x<sup>™</sup> DSP Generation:

- 2X CPU Registers [64 General-Purpose]

- New Audio-Specific Instructions

- Compatible With the C67x CPU

- Enhanced Memory System

- 256K-Byte Unified Program/Data RAM

- 384K-Byte Unified Program/Data ROM

- Single-Cycle Data Access From CPU

- Large Program Cache (32K Byte) Supports RAM, ROM, and External Memory

- External Memory Interface (EMIF) Supports

- 100-MHz SDRAM (16- or 32-Bit)

- Asynchronous NOR Flash, SRAM (8-,16-, or 32-Bit)

- NAND Flash (8- or 16-Bit)

- Enhanced I/O System

- High-Performance Crossbar Switch

- Dedicated McASP DMA Bus

- Deterministic I/O Performance

- dMAX (Dual Data Movement Accelerator) Supports:

- 16 Independent Channels

- Concurrent Processing of Two Transfer Requests

- 1-, 2-, and 3-Dimensional Memory-to-Memory and Memory-to-Peripheral Data Transfers

- Circular Addressing Where the Size of a Circular Buffer (FIFO) is not Limited to 2<sup>n</sup>

- Table-Based Multi-Tap Delay Read and Write Transfers From/To a Circular Buffer

- Three Multichannel Audio Serial Ports

- Transmit/Receive Clocks up to 50 MHz

- Six Clock Zones and 16 Serial Data Pins

- Supports TDM, I2S, and Similar Formats

- DIT-Capable (McASP2)

- Universal Host-Port Interface (UHPI)

- 32-Bit-Wide Data Bus for High Bandwidth

- Muxed and Non-Muxed Address and Data

- Two 10-MHz SPI Ports With 3-, 4-, and 5-Pin Options

- Two Inter-Integrated Circuit (I2C) Ports

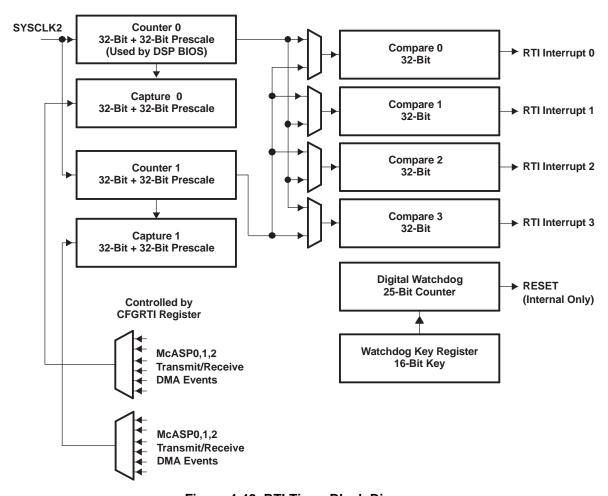

- Real-Time Interrupt Counter/Watchdog

- Oscillator- and Software-Controlled PLL

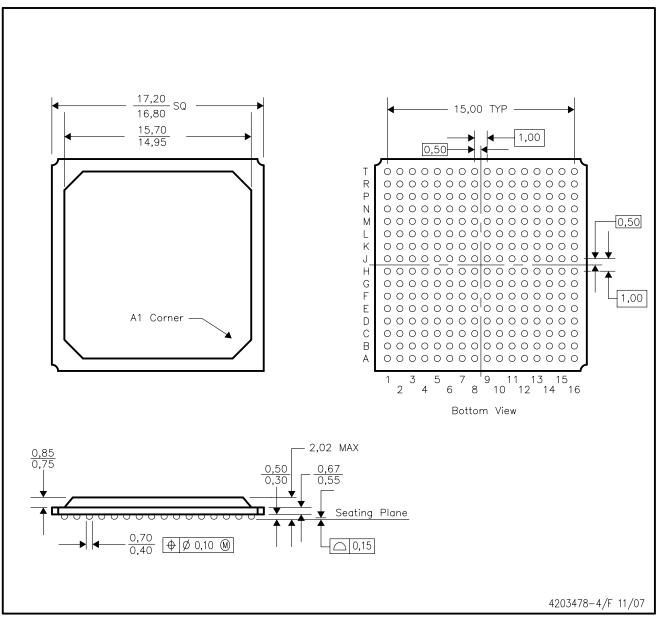

- 256-Terminal, 1.0-mm, 16x16 Array Plastic Ball Grid Array (PBGA)

- Applications

- · Professional Audio

- Mixers

- Effects Boxes

- Audio Synthesis

- Instrument/Amp Modeling

- Audio Conferencing

- Audio Broadcast

- Audio Encoder

- Emerging Audio Applications

- Biometrics

- Medical

- Industrial

- Supports Defense, Aerospace, and Medical Applications

- Controlled Baseline

- One Assembly/Test Site

- One Fabrication Site

- Available in Military (-55°C/125°C)

Temperature Range

- Extended Product Life Cycle

- Extended Product-Change Notification

- Product Traceability

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

C67x, TMS320C6000, C6000, DSP/BIOS, XDS, TMS320 are trademarks of Texas Instruments.

Philips is a registered trademark of Koninklijki Philips Electronics N.V.

All other trademarks are the property of their respective owners.

## 1.2 Description

The SM320C6727B is the next generation of Texas Instruments' C67x generation of high-performance 32-/64-bit floating-point digital signal processor.

**Enhanced C67x+ CPU.** The C67x+ CPU is an enhanced version of the C67x CPU used on the C671x DSPs. It is compatible with the C67x CPU but offers significant improvements in speed, code density, and floating-point performance per clock cycle. At 300 MHz, the CPU is capable of a maximum performance of 2400 MIPS/1800 MFLOPS by executing up to eight instructions (six of which are floating-point instructions) in parallel each cycle. The CPU natively supports 32-bit fixed-point, 32-bit single-precision floating-point, and 64-bit double-precision floating-point arithmetic.

**Efficient Memory System.** The memory controller maps the large on-chip 256K-byte RAM and 384K-byte ROM as unified program/data memory. Development is simplified since there is no fixed division between program and data memory size as on some other devices.

The memory controller supports single-cycle data accesses from the C67x+ CPU to the RAM and ROM. Up to three parallel accesses to the internal RAM and ROM from three of the following four sources are supported:

- Two 64-bit data accesses from the C67x+ CPU

- One 256-bit program fetch from the core and program cache

- One 32-bit data access from the peripheral system (either dMAX or UHPI)

The large (32K-byte) program cache translates to a high hit rate for most applications. This prevents most program/data access conflicts to the on-chip memory. It also enables effective program execution from an off-chip memory such as an SDRAM.

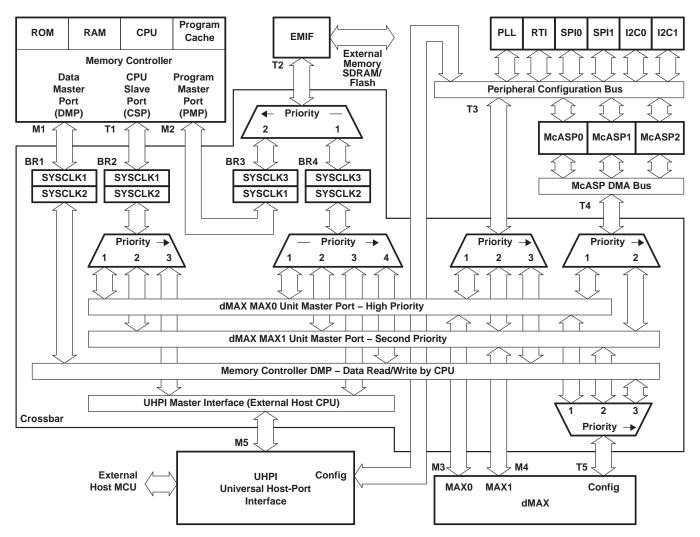

**High-Performance Crossbar Switch.** A high-performance crossbar switch acts as a central hub between the different bus masters (CPU, dMAX, UHPI) and different targets (peripherals and memory). The crossbar is partially connected; some connections are not supported (for example, UHPI-to-peripheral connections).

Multiple transfers occur in parallel through the crossbar as long as there is no conflict between bus masters for a particular target. When a conflict does occur, the arbitration is a simple and deterministic fixed-priority scheme.

The dMAX is given highest-priority since it is responsible for the most time-critical I/O transfers, followed next by the UHPI, and finally by the CPU.

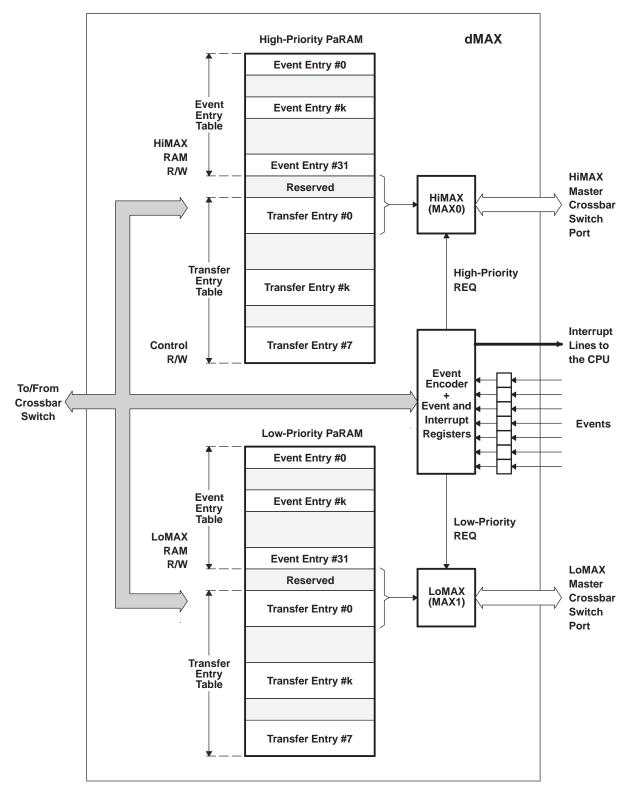

**dMAX Dual Data Movement Accelerator.** The dMAX is a module designed to perform Data Movement Acceleration. The Data Movement Accelerator (dMAX) controller handles user-programmed data transfers between the internal data memory controller and the device peripherals on the C672x DSP. The dMAX allows movement of data to/from any addressable memory space including internal memory, peripherals, and external memory.

The dMAX controller includes features such as the capability to perform three-dimensional data transfers for advanced data sorting, and the capability to manage a section of the memory as a circular buffer/FIFO with delay-tap based reading and writing of data. The dMAX controller is capable of concurrently processing two transfer requests (provided that they are to/from different source/destinations).

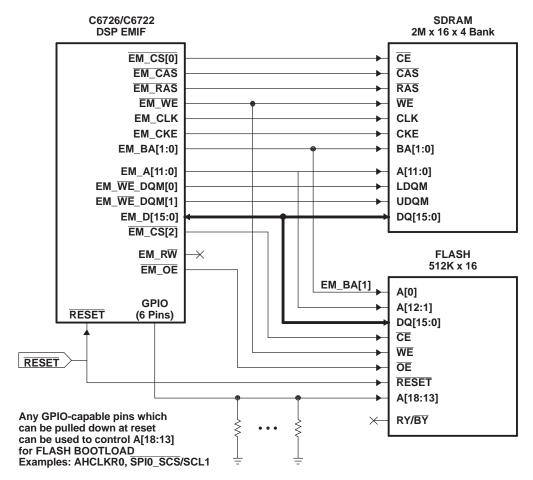

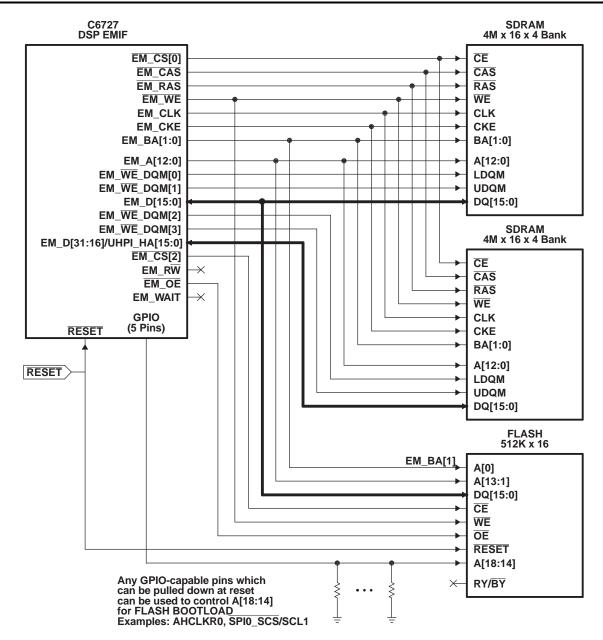

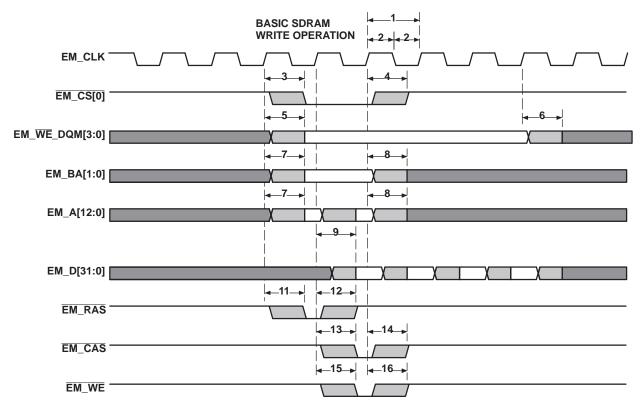

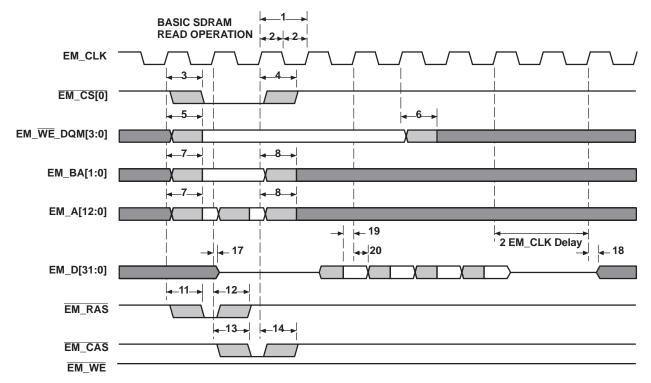

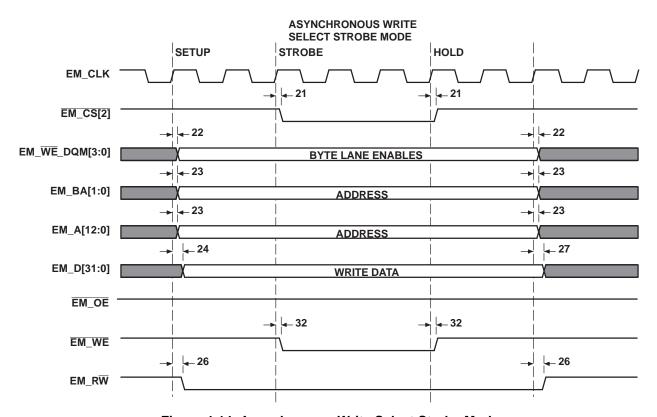

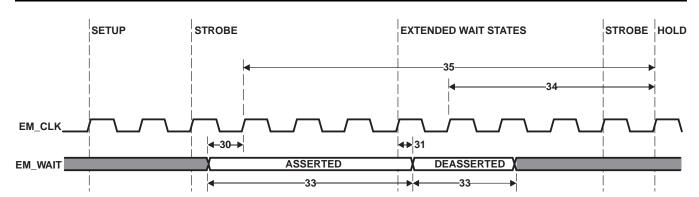

**External Memory Interface (EMIF) for Flexibility and Expansion.** The external memory interface on the C672x supports a single bank of SDRAM and a single bank of asynchronous memory. The EMIF data width is 16 bits wide on the C6726 and C6722, and 32 bits wide on the C6727.

SDRAM support includes x16 and x32 SDRAM devices with 1, 2, or 4 banks.

The C6726 and C6722 support SDRAM devices up to 128M bits.

The C6727 extends SDRAM support to 256M-bit and 512M-bit devices.

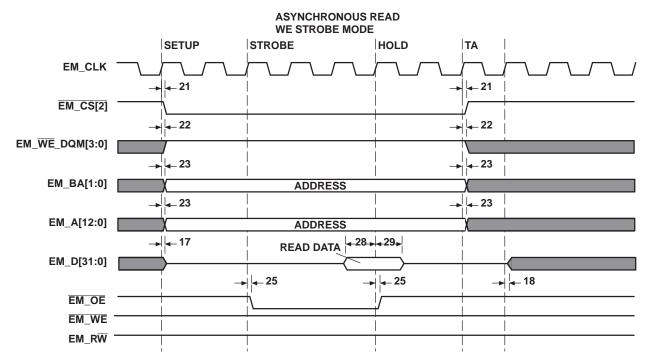

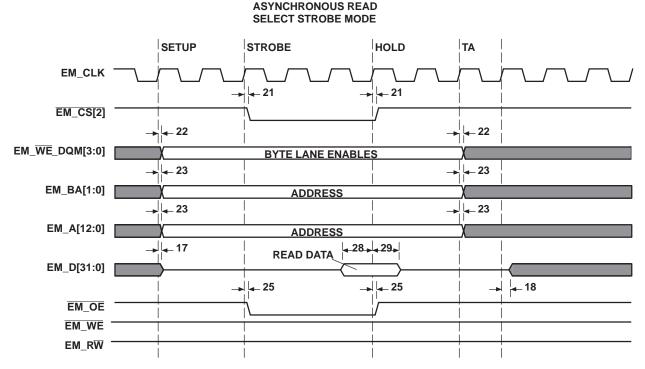

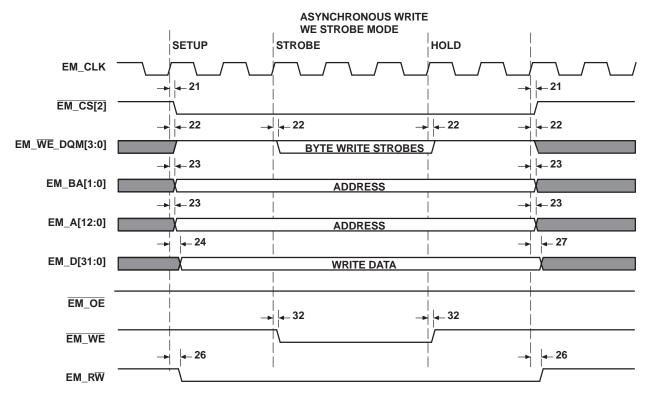

Asynchronous memory support is typically used to boot from a parallel non-multiplexed NOR flash device that can be 8, 16, or 32 bits wide. Booting from larger flash devices than are natively supported by the dedicated EMIF address lines is accomplished by using general-purpose I/O pins for upper address lines.

The asynchronous memory interface can also be configured to support 8- or 16-bit-wide NAND flash. It includes a hardware ECC calculation (for single-bit errors) that can operate on blocks of data up to 512 bytes.

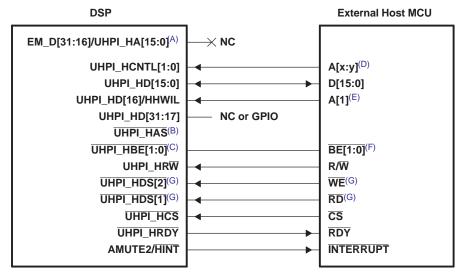

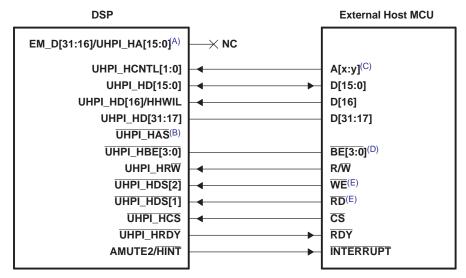

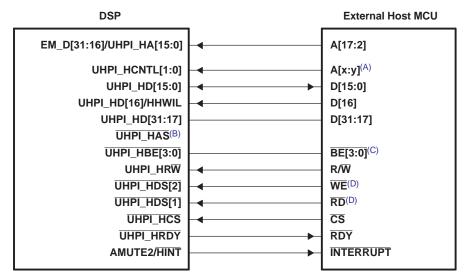

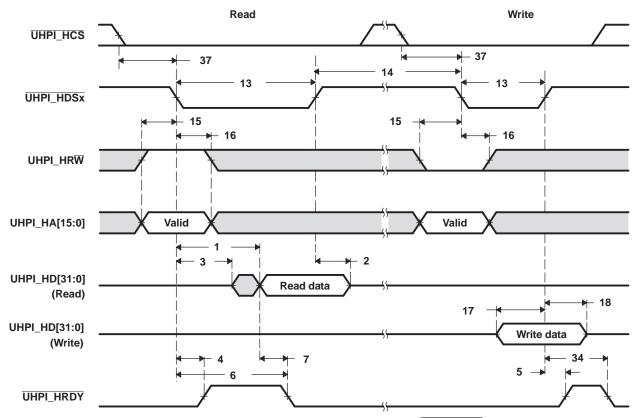

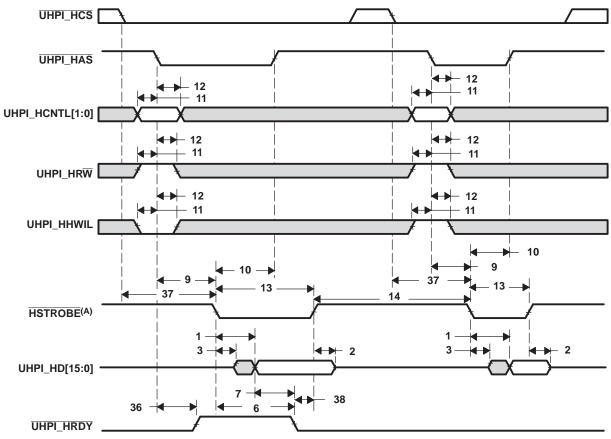

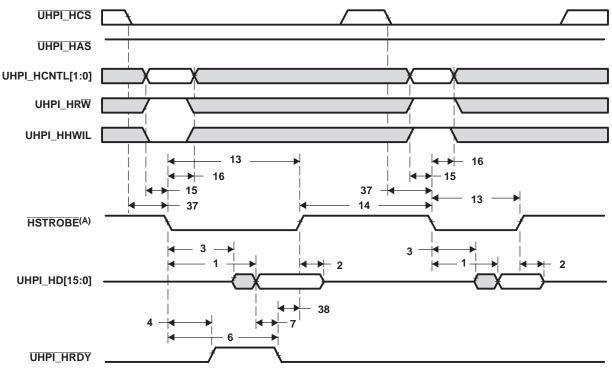

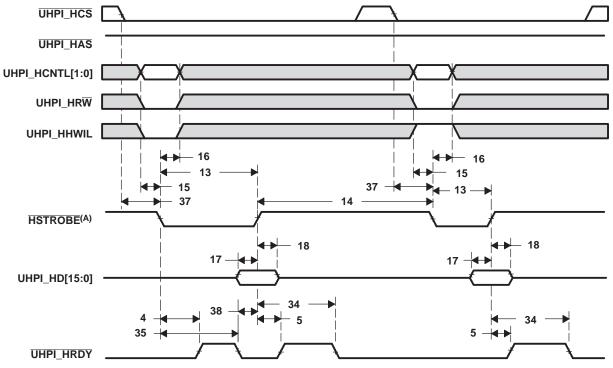

**Universal Host-Port Interface (UHPI) for High-Speed Parallel I/O.** The Universal Host-Port Interface (UHPI) is a parallel interface through which an external host CPU can access memories on the DSP. Three modes are supported by the C672x UHPI:

- Multiplexed Address/Data Half-Word (16-bit-wide) Mode (similar to C6713)

- Multiplexed Address/Data Full Word (32-bit-wide) Mode

- · Non-Multiplexed Mode 16-bit Address and 32-bit Data Bus

The UHPI can also be restricted to accessing a single page (64K bytes) of memory anywhere in the address space of the C672x; this page can be changed, but only by the C672x CPU. This feature allows the UHPI to be used for high-speed data transfers even in systems where security is an important requirement.

The UHPI is only available on the C6727.

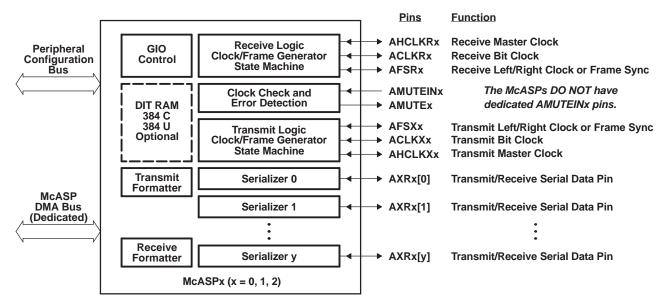

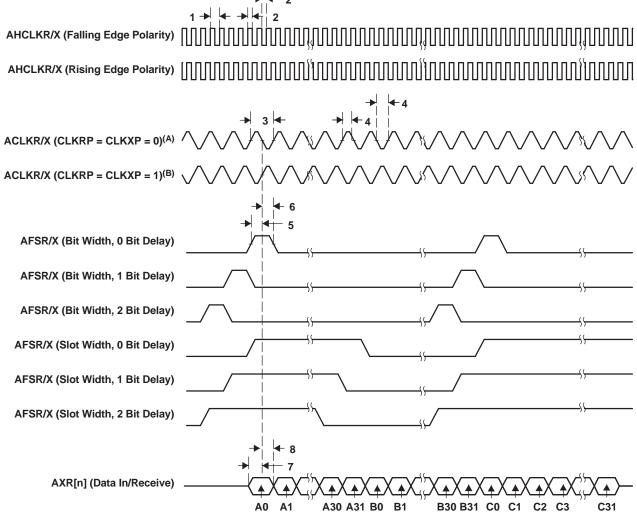

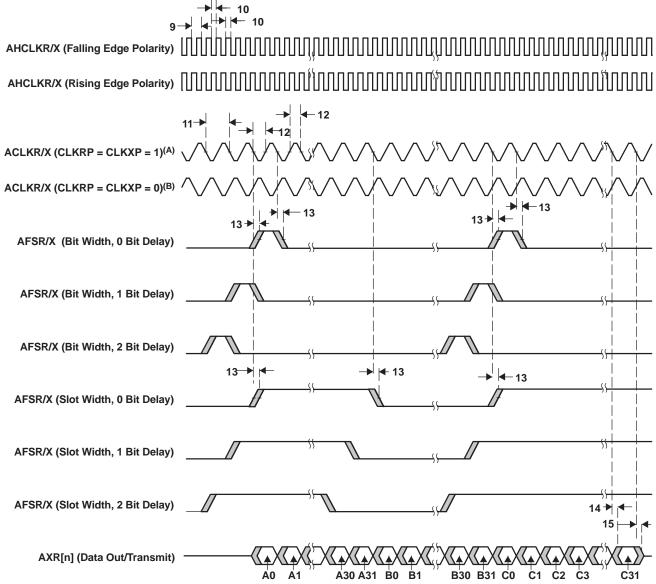

Multichannel Audio Serial Ports (McASP0, McASP1, and McASP2) - Up to 16 Stereo Channels I2S. The multichannel audio serial port (McASP) seamlessly interfaces to CODECs, DACs, ADCs, and other devices. It supports the ubiquitous IIS format as well as many variations of this format, including time division multiplex (TDM) formats with up to 32 time slots.

Each McASP includes a transmit and receive section which may operate independently or synchronously; furthermore, each section includes its own flexible clock generator and extensive error-checking logic.

As data passes through the McASP, it can be realigned so that the fixed-point representation used by the application code can be independent of the representation used by the external devices without requiring any CPU overhead to make the conversion.

The McASP is a configurable module and supports between 2 and 16 serial data pins. It also has the option of supporting a Digital Interface Transmitter (DIT) mode with a full 384 bits of channel status and user data memory.

McASP2 is not available on the C6722.

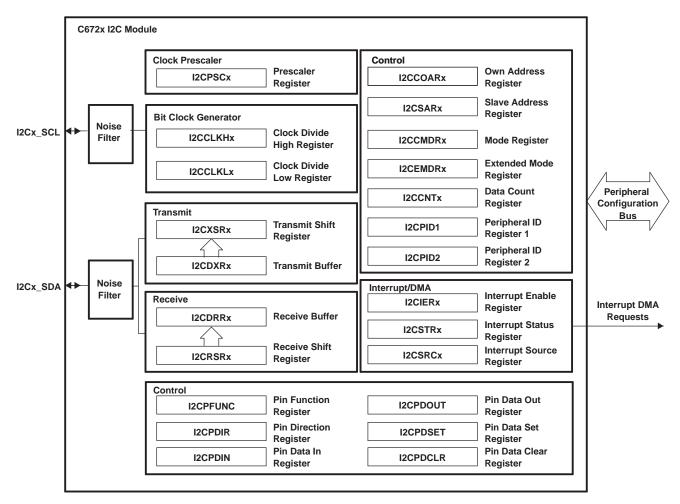

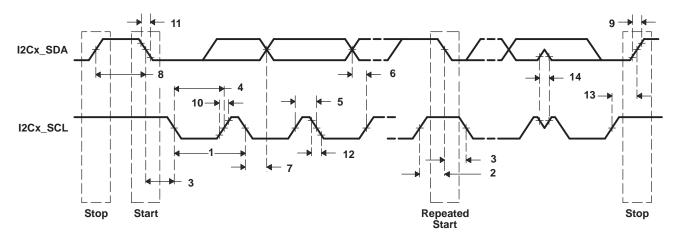

Inter-Integrated Circuit Serial Ports (I2C0, I2C1). The C672x includes two inter-integrated circuit (I2C) serial ports. A typical application is to configure one I2C serial port as a slave to an external user-interface microcontroller. The other I2C serial port may then be used by the C672x DSP to control external peripheral devices, such as a CODEC or network controller, which are functionally peripherals of the DSP device.

The two I2C serial ports are pin-multiplexed with the SPI0 serial port.

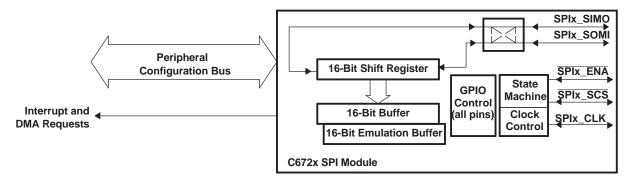

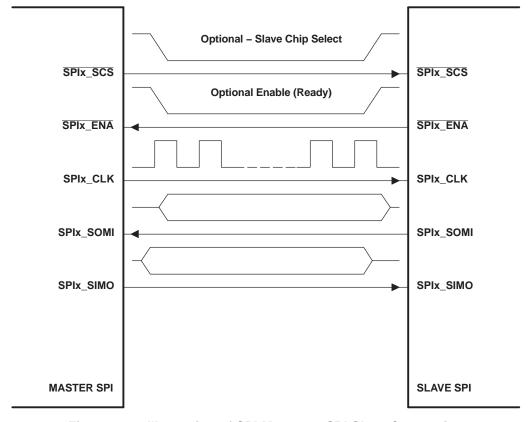

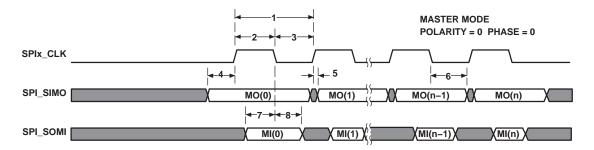

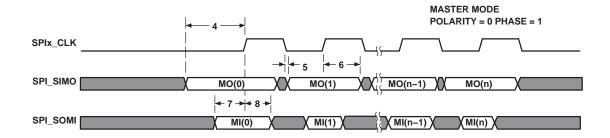

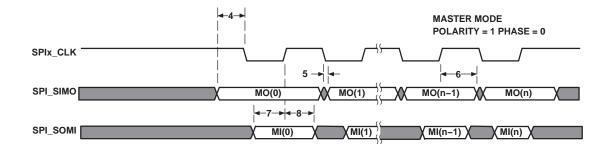

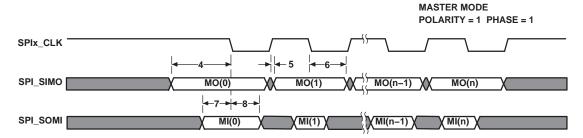

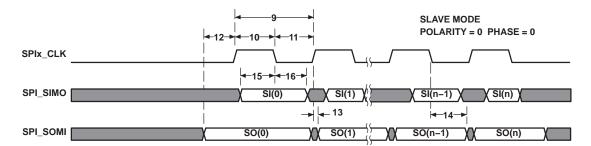

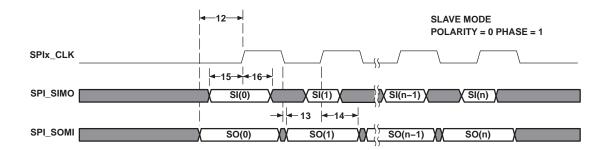

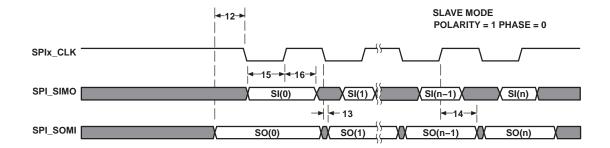

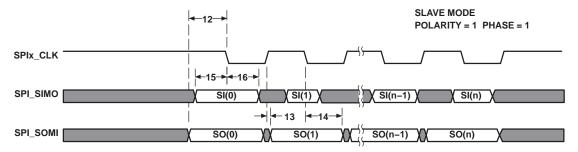

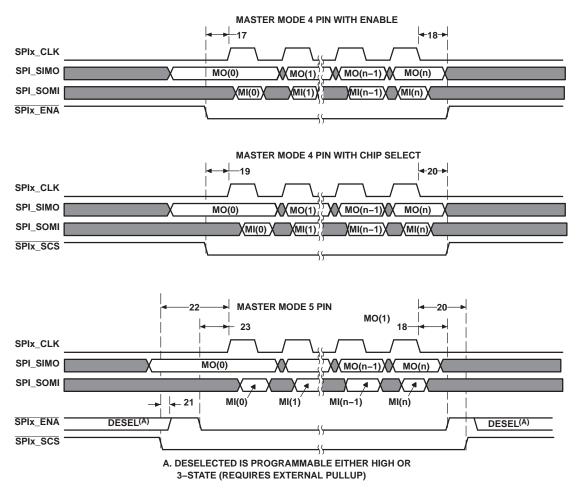

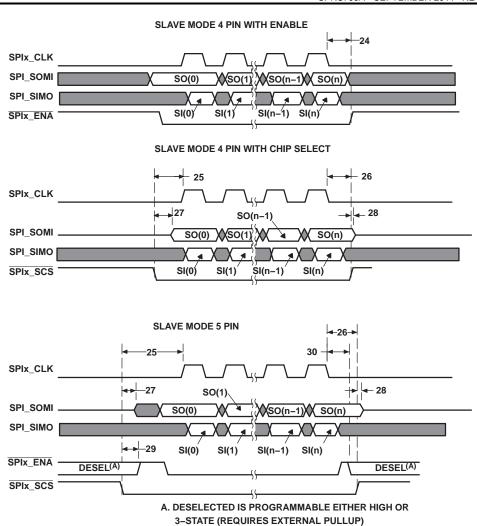

**Serial Peripheral Interface Ports (SPI0, SPI1).** As in the case of the I2C serial ports, the C672x DSP also includes two serial peripheral interface (SPI) serial ports. This allows one SPI port to be configured as a slave to control the DSP while the other SPI serial port is used by the DSP to control external peripherals.

The SPI ports support a basic 3-pin mode as well as optional 4- and 5-pin modes. The optional pins include a slave chip-select pin and an enable pin which implements handshaking automatically in hardware for maximum SPI throughput.

The SPI0 port is pin-multiplexed with the two I2C serial ports (I2C0 and I2C1). The SPI1 serial port is pin-multiplexed with five of the serial data pins from McASP0 and McASP1.

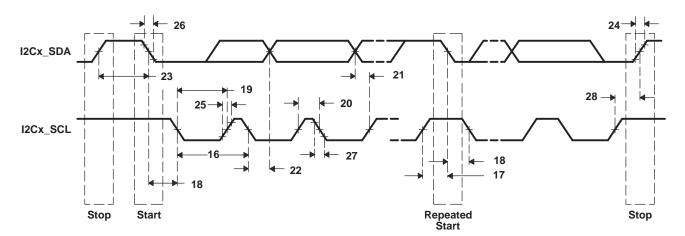

Real-Time Interrupt Timer (RTI). The real-time interrupt timer module includes:

- Two 32-bit counter/prescaler pairs

- · Two input captures (tied to McASP direct memory access [DMA] events for sample rate measurement)

- · Four compares with automatic update capability

- Digital Watchdog (optional) for enhanced system robustness

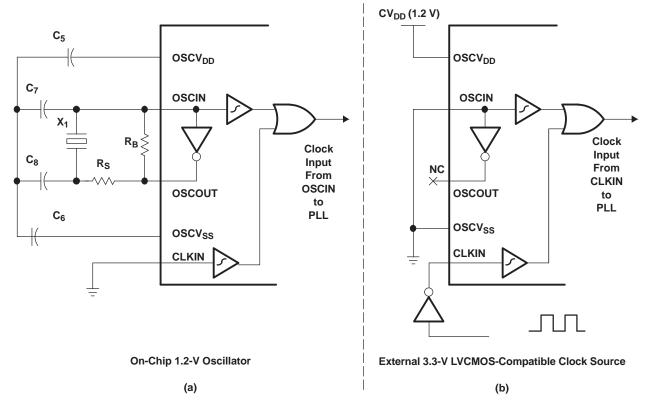

**Clock Generation (PLL and OSC).** The C672x DSP includes an on-chip oscillator that supports crystals in the range of 12 MHz to 25 MHz. Alternatively, the clock can be provided externally through the CLKIN pin.

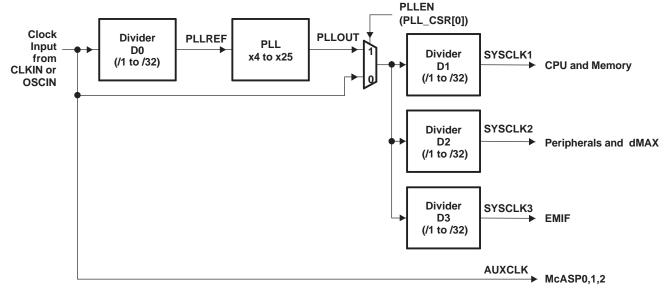

The DSP includes a flexible, software-programmable phase-locked loop (PLL) clock generator. Three different clock domains (SYSCLK1, SYSCLK2, and SYSCLK3) are generated by dividing down the PLL output. SYSCLK1 is the clock used by the CPU, memory controller, and memories. SYSCLK2 is used by the peripheral subsystem and dMAX. SYSCLK3 is used exclusively for the EMIF.

# 1.2.1 Device Compatibility

The SM320C6727B floating-point digital signal processor is based on the new C67x+ CPU. This core is code-compatible with the C67x CPU core used on the TMS320C671x DSPs, but with significant enhancements including additional floating-point instructions. See Section 2.2

## 1.3 Functional Block Diagram

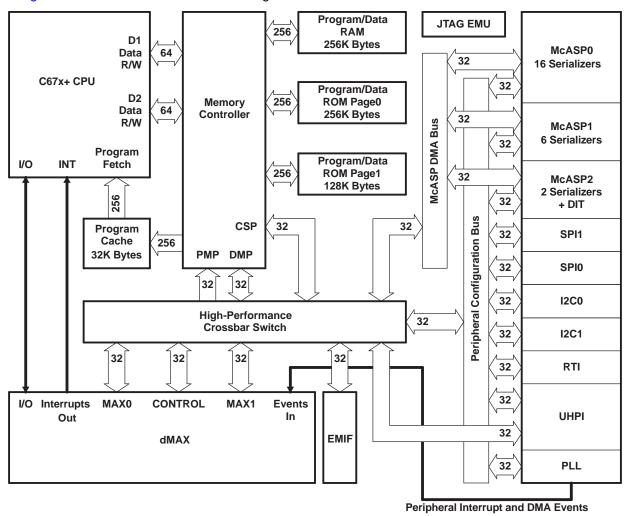

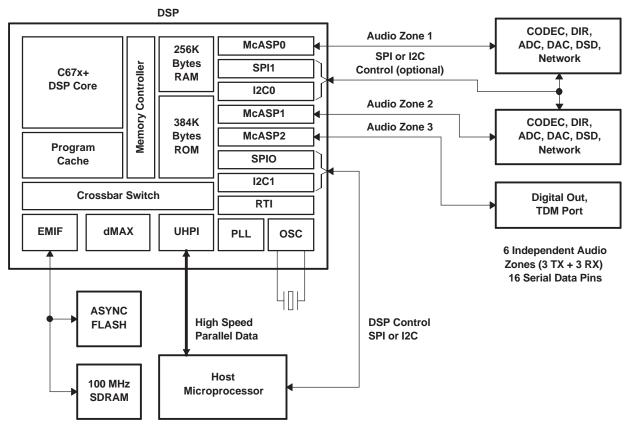

Figure 1-1 shows the functional block diagram of the C672x device.

A. UHPI is available only on the C6727. McASP2 is not available on the C6722.

Figure 1-1. C672x DSP Block Diagram

# SPRS793A - SEPTEMBER 2011-REVISED OCTOBER 2011

| 1 | SM3   | 20C6727B DSP <u>1</u>                   | 4.2  | Absolute Maximum Ratings                                     | 32  |

|---|-------|-----------------------------------------|------|--------------------------------------------------------------|-----|

|   | 1.1   | Features <u>1</u>                       | 4.3  | Recommended Operating Conditions                             | 32  |

|   | 1.2   | Description 2                           | 4.4  | Electrical Characteristics                                   | 33  |

|   | 1.3   | Functional Block Diagram 5              | 4.5  | Parameter Information                                        | _   |

| 2 | Devi  | ce Overview                             | 4.6  | Timing Parameter Symbology                                   | 35  |

|   | 2.1   | Device Characteristics 7                | 4.7  | Power Supplies                                               | _   |

|   | 2.2   | Enhanced C67x+ CPU 8                    | 4.8  | Reset                                                        | 37  |

|   | 2.3   | CPU Interrupt Assignments               | 4.9  | Dual Data Movement Accelerator (dMAX)                        | 38  |

|   | 2.4   | Internal Program/Data ROM and RAM 10    | 4.10 | External Interrupts                                          | 43  |

|   | 2.5   | Program Cache                           | 4.11 | External Memory Interface (EMIF)                             | 44  |

|   | 2.6   | High-Performance Crossbar Switch        | 4.12 | Universal Host-Port Interface (UHPI) [C6727 Only]            |     |

|   |       | _                                       | 4 40 | Multiphonnal Audio Corial Dorto (MAACDO MAACDA               | _   |

|   | 2.7   | Memory Map Summary                      | 4.13 | Multichannel Audio Serial Ports (McASP0, McASP1, and McASP2) |     |

|   | 2.8   | Boot Modes                              | 4.14 | •                                                            | _   |

|   | 2.9   | Pin Assignments                         | 4.15 | Inter-Integrated Circuit Serial Ports (I2C0, I2C1)           |     |

|   | 2.10  | <u>26</u>                               |      |                                                              | 92  |

|   | 2.11  | ORDERING INFORMATION                    | 4.16 | 3 4 7 7 7                                                    | 07  |

|   | 2.12  | Documentation Support                   | 4.17 | Watchdog  External Clock Input From Oscillator or CLKIN Pin  | 91  |

| 3 | Devi  | ce Configurations 29                    | 4.17 | •                                                            | 100 |

|   | 3.1   | Device Configuration Registers          | 4.18 | Phase-Locked Loop (PLL)                                      |     |

|   | 3.2   | Peripheral Pin Multiplexing Options 29  | Appl | lication Example                                             | 105 |

|   | 3.3   | Peripheral Pin Multiplexing Control     |      | -                                                            | 106 |

| 4 | Perip | oheral and Electrical Specifications 32 | 6.1  | -                                                            | 106 |

|   | 4.1   | Electrical Specifications               | 6.2  | Packaging Information                                        |     |

|   |       |                                         |      |                                                              |     |

# 2 Device Overview

## 2.1 Device Characteristics

Table 2-1 provides an overview of the C672x DSP. The table shows significant features of each device, including the capacity of on-chip memory, the peripherals, the execution time, and the package type with pin count.

Table 2-1. Characteristics of the C672x Processor

| HARDWARE FEATURES                                                |                                       | C6727B                                       |

|------------------------------------------------------------------|---------------------------------------|----------------------------------------------|

|                                                                  | dMAX                                  | 1                                            |

|                                                                  | EMIF                                  | 1 (32-bit)                                   |

| Peripherals                                                      | UHPI                                  | 1                                            |

| Not all peripheral pins are available at the same                | McASP                                 | 3                                            |

| time. (For more details, see the Device Configurations section.) | SPI                                   | 2                                            |

| Comigarations contain,                                           | I2C                                   | 2                                            |

|                                                                  | RTI                                   | 1                                            |

| On-Chip Memory                                                   | Size (kB)                             | 32KB Program Cache<br>256KB RAM<br>384KB ROM |

| CPU ID + CPU Rev ID                                              | Control Status Register (CSR.[31:16]) | 0x0300                                       |

| Frequency                                                        | MHz                                   | 250                                          |

| Cycle Time                                                       | ns                                    | 4 ns                                         |

| Valtaria                                                         | Core (V)                              | 1.2 V                                        |

| Voltage                                                          | I/O (V)                               | 3.3 V                                        |

|                                                                  | Prescaler                             | /1, /2, /3,, /32                             |

| Clock Generator Options                                          | Multiplier                            | x4, x5, x6,, x25                             |

|                                                                  | Postscaler                            | /1, /2, /3,, /32                             |

| Process Technology                                               | μm                                    | 0.13 µm                                      |

#### 2.2 Enhanced C67x+ CPU

The SM320C6727B floating-point digital signal processor is based on the new C67x+ CPU. This core is code-compatible with the C67x CPU core used on the TMS320C671x DSPs, but with significant enhancements including an increase in core operating frequency from 225 MHz to 300 MHz <sup>(1)</sup> while operating at 1.2 V.

The CPU fetches 256-bit-wide advanced very-long instruction word (VLIW) fetch packets that are composed of variable-length execute packets. The execute packets can supply from one to eight 32-bit instructions to the eight functional units during every clock cycle. The variable-length execute packets are a key memory-saving feature, distinguishing the C67x CPU from other VLIW architectures. Additionally, execute packets can now span fetch packets, providing a code size improvement over the C67x CPU core.

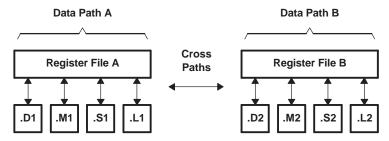

The CPU features two data paths, shown in Figure 2-1, each composed of four functional units (.D, .M, .S, and .L) and a register file. The .D unit in each data path is a data-addressing unit that is responsible for all data transfers between the register files and the memory. The .M functional units are dedicated for multiplies, and the .S and .L functional units perform a general set of arithmetic, logical, and branch functions. All instructions operate on registers as opposed to data in memory, but results stored in the 32-bit registers can be subsequently moved to memory as bytes, half-words, or words.

Figure 2-1. CPU Data Paths

The register file in each data path contains 32 32-bit registers for a total of 64 general-purpose registers. This doubles the number of registers found on the C67x CPU core, allowing the optimizing C compiler to pipeline more complex loops by decreasing register pressure significantly.

The four functional units in each data path of the CPU can freely share the 32 registers belonging to that data path. Each data path also features a single cross path connected to the register file on the opposing data path. This allows each data path to source one cross-path operand per cycle from the opposing register file. On the C67x+ CPU, this single cross-path operand can be used by two functional units per cycle, an improvement over the C67x CPU in which only one functional unit could use the cross-path operand. In addition, the cross-path register read(s) are not counted as part of the limit of four reads of the same register in a single cycle.

The C67x+ CPU executes all C67x instructions plus new floating-point instructions to improve performance specifically during audio processing. These new instructions are listed in Table 2-2.

(1) CPU speed is device-dependent. See Table 2-1.

### Table 2-2. New Floating-Point Instructions for C67x+ CPU

| INSTRUCTION                 | FLOATING-POINT<br>OPERATION <sup>(1)</sup> | IMPROVES                                                               |

|-----------------------------|--------------------------------------------|------------------------------------------------------------------------|

| MPYSPDP                     | $SP \times DP \rightarrow DP$              | Faster than MPYDP. Improves high Q biquads (bass management) and FFT.  |

| MPYSP2DP                    | $SP \times SP \rightarrow DP$              | Faster than MPYDP.<br>Improves Long FIRs (EQ).                         |

| ADDSP (new to CPU "S" Unit) | $SP + SP \rightarrow SP$                   |                                                                        |

| ADDDP (new to CPU "S" Unit) | $DP + DP \rightarrow DP$                   | Now up to four floating-point add and subtract operations in parallel. |

| SUBSP (new to CPU "S" Unit) | $SP - SP \rightarrow SP$                   | Improves FFT performance and symmetric FIR.                            |

| SUBDP (new to CPU "S" Unit) | $DP - DP \to DP$                           |                                                                        |

<sup>(1)</sup> SP means IEEE Single-Precision (32-bit) operations and DP means IEEE Double-Precision (64-bit) operations.

Finally, two new registers, which are dedicated to communication with the dMAX unit, have been added to the C67x+ CPU. These registers are the dMAX Event Trigger Register (DETR) and the dMAX Event Status Register (DESR). They allow the CPU and dMAX to communicate without requiring any accesses to the memory system.

# 2.3 CPU Interrupt Assignments

Table 2-3 lists the interrupt channel assignments on the C672x device. If more than one source is listed, the interrupt channel is shared and an interrupt on this channel could have come from any of the enabled peripherals on that channel.

The dMAX peripheral has two CPU interrupts dedicated to reporting FIFO status (INT7) and transfer completion (INT8). In addition, the dMAX can generate interrupts to the CPU on lines INT9–13 and INT15 in response to peripheral events. To enable this functionality, the associated Event Entry within the dMAX can be programmed so that a CPU interrupt is generated when the peripheral event is received.

**Table 2-3. CPU Interrupt Assignments**

| CPU INTERRUPT | INTERRUPT SOURCE                                             |

|---------------|--------------------------------------------------------------|

| INT0          | RESET                                                        |

| INT1          | NMI (From dMAX or EMIF Interrupt)                            |

| INT2          | Reserved                                                     |

| INT3          | Reserved                                                     |

| INT4          | RTI Interrupt 0                                              |

| INT5          | RTI Interrupts 1, 2, 3, and RTI Overflow Interrupts 0 and 1. |

| INT6          | UHPI CPU Interrupt (from External Host MCU)                  |

| INT7          | FIFO status notification from dMAX                           |

| INT8          | Transfer completion notification from dMAX                   |

| INT9          | dMAX event (0x2 specified in the dMAX interrupt event entry) |

| INT10         | dMAX event (0x3 specified in the dMAX interrupt event entry) |

| INT11         | dMAX event (0x4 specified in the dMAX interrupt event entry) |

| INT12         | dMAX event (0x5 specified in the dMAX interrupt event entry) |

| INT13         | dMAX event (0x6 specified in the dMAX interrupt event entry) |

| INT14         | I2C0, I2C1, SPI0, SPI1 Interrupts                            |

| INT15         | dMAX event (0x7 specified in the dMAX interrupt event entry) |

# 2.4 Internal Program/Data ROM and RAM

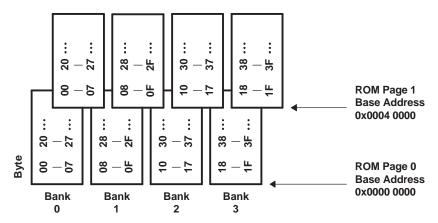

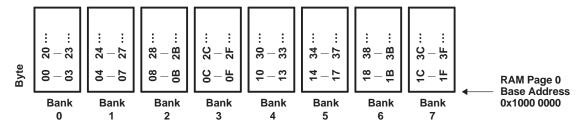

The organization of program/data ROM and RAM on C672x is simple and efficient. ROM is organized as two 256-bit-wide pages with four 64-bit-wide banks. RAM is organized as a single 256-bit-wide page with eight 32-bit-wide banks.

The internal memory organization is illustrated in Figure 2-2 (ROM) and Figure 2-3 (RAM).

Figure 2-2. Program/Data ROM Organization

Figure 2-3. Program/Data RAM Organization

The C672x memory controller supports up to three parallel accesses to the internal RAM and ROM from three of the following four sources as long as there are no bank conflicts:

- Two 64-bit data accesses from the C67x+ CPU

- One 256-bit-wide program fetch from the program cache

- One 32-bit data access from the peripheral system (either dMAX or UHPI)

A program cache miss is 256 bits wide and conflicts only with data accesses to the same page. Multiple data accesses to different pages, or to the same page but different banks will occur without conflict.

The organization of the C672x internal memory system into multiple pages (3 total) and a large number of banks (16 total) means that it is straightforward to optimize DSP code to avoid data conflicts. Several factors, including the large program cache and the partitioning of the memory system into multiple pages, minimize the number of program versus data conflicts.

The result is an efficient memory system which allows easy tuning towards the maximum possible CPU performance.

The C672x ROM consists of a software bootloader plus additional software. Please refer to the C9230C100 TMS320C672x Floating-Point Digital Signal Processors ROM Data Manual (literature number SPRS277) for more details on the ROM contents.

## 2.5 Program Cache

The C672x DSP executes code directly from a large on-chip 32K-byte program cache. The program cache has these key features:

- Wide 256-bit path to internal ROM/RAM

- · Single-cycle access on cache hits

- 2-cycle miss penalty to internal ROM/RAM

- Caches external memory as well as ROM/RAM

- Direct-mapped

- Modes: Enable, Freeze, Bypass

- Software invalidate to support code overlay

The program cache line size is 256 bits wide and is matched with a 256-bit-wide path between cache and internal memory. This allows the program cache to fill an entire line (corresponding to eight C67x+ CPU instructions) with only a single miss penalty of 2 cycles.

The program cache control registers are listed in Table 2-4.

**Table 2-4. Program Cache Control Registers**

| REGISTER NAME | BYTE ADDRESS | DESCRIPTION                     |

|---------------|--------------|---------------------------------|

| L1PISAR       | 0x2000 0000  | L1P Invalidate Start Address    |

| L1PICR        | 0x2000 0004  | L1P Invalidate Control Register |

#### **CAUTION**

Any application which modifies the contents of program RAM (for example, a program overlay) must invalidate the addresses from program cache to maintain coherency by explicitly writing to the L1PISAR and L1PICR registers.

The Cache Mode (Enable, Freeze, Bypass) is configured through a CPU internal register (CSR, bits 7:5). These options are listed in Table 2-5. Typically, only the Cache Enable Mode is used. But advanced users may utilize Freeze and Bypass modes to tune performance.

Table 2-5. Cache Modes Set Through PCC Field of CSR CPU Register on C672x

| CPU CSR[7:5] | CACHE MODE                                                          |

|--------------|---------------------------------------------------------------------|

| 000b         | Enable (Deprecated - Means direct mapped RAM on some C6000 devices) |

| 010b         | Enable - Cache is enabled, cache misses cause a line fill.          |

| 011b         | Freeze - Cache is enabled, but contents are unchanged by misses.    |

| 100b         | Bypass - Forces cache misses, cache contents frozen.                |

| Other Values | Reserved - Not Supported                                            |

### **CAUTION**

Although the reset value of CSR[7:5] (PCC field) is 000b, the value may be modified during the boot process by the ROM code. Refer to the appropriate ROM data sheet for more details. However, note that the cache may be **disabled** when control is actually passed to application code. Therefore, it may be necessary to write '010b' to the PCC field to explicitly enable the cache at the start of application code.

## **CAUTION**

Changing the cache mode through CSR[7:5] does not invalidate any lines already in the cache. To invalidate the cache after modifications are made to program space, the control registers L1PISAR and L1PICR must be used.

# 2.6 High-Performance Crossbar Switch

The C672x DSP includes a high-performance crossbar switch that acts as a central hub between bus masters and targets. Figure 2-4 illustrates the connectivity of the crossbar switch.

Figure 2-4. Block Diagram of Crossbar Switch

As shown in Figure 2-4, there are five bus masters:

| M1 | Memory controller DMP for CPU data accesses to peripherals and EMIF.          |

|----|-------------------------------------------------------------------------------|

| M2 | Memory controller PMP for program cache fills from the EMIF.                  |

| M3 | dMAX HiMAX master port for high-priority DMA accesses.                        |

| M4 | dMAX LoMAX master port for lower-priority DMA accesses.                       |

| M5 | UHPI master port for an external MCU to access on-chip and off-chip memories. |

The five bus masters arbitrate for five different target groups:

| T1 | On-chip memories through the CPU Slave Port (CSP).             |

|----|----------------------------------------------------------------|

| T2 | Memories on the external memory interface (EMIF).              |

| Т3 | Peripheral registers through the peripheral configuration bus. |

| T4 | McASP serializers through the dedicated McASP DMA bus.         |

| T5 | dMAX registers.                                                |

The crossbar switch supports parallel accesses from different bus masters to different targets. When two or more bus masters contend for the same target beginning at the same cycle, then the highest-priority master is given ownership of the target while the other master(s) are stalled. However, once ownership of the target is given to a bus master, it is allowed to complete its access before ownership is arbitrated again. Following are two examples.

### **Example 1:** Simultaneous accesses without conflict

- dMAX HiMAX accesses McASP Data Port for transfer of audio data.

- dMAX LoMAX accesses SPI port for control processing.

- · UHPI accesses internal RAM through the CSP.

- · CPU fills program cache from EMIF.

## **Example 2:** Conflict over a shared resource

- dMAX HiMAX accesses RTI port for McASP sample rate measurement.

- dMAX LoMAX accesses SPI port for control processing.

In Example 2, both masters contend for the same target, the peripheral configuration bus. The HiMAX access will be given priority over the LoMAX access.

The master priority is illustrated in Figure 2-4 by the numbers 1 through 4 in the bus arbiter symbols. Note that the EMIF arbitration is distributed so that only one bridge crossing is necessary for PMP accesses. The effect is that PMP has 5th priority to the EMIF but lower latency.

A bus bridge is needed between masters and targets which run at different clock rates. The bus bridge contains a small FIFO to allow the bridge to accept an incoming (burst) access at one clock rate and pass it through the bridge to a target running at a different rate. Table 2-6 lists the FIFO properties of the four bridges (BR1, BR2, BR3, and BR4) in Figure 2-4.

Table 2-6. Bus Bridges

| LABEL | BRIDGE DESCRIPTION                    | MASTER CLOCK | TARGET CLOCK |

|-------|---------------------------------------|--------------|--------------|

| BR1   | DMP Bridge to peripherals, dMAX, EMIF | SYSCLK1      | SYSCLK2      |

| BR2   | dMAX, UHPI to ROM/RAM (CSP)           | SYSCLK2      | SYSCLK1      |

| BR3   | PMP to EMIF                           | SYSCLK1      | SYSCLK3      |

| BR4   | CPU, UHPI, and dMAX to EMIF           | SYSCLK2      | SYSCLK3      |

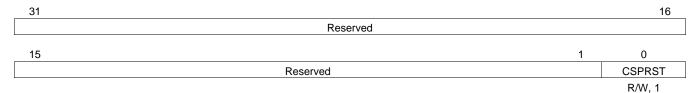

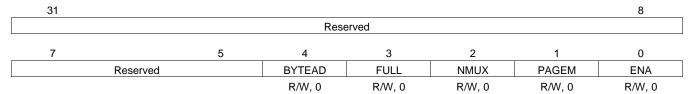

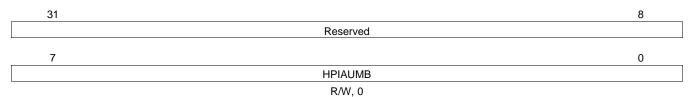

Figure 2-5 shows the bit layout of the device-level bridge control register (CFGBRIDGE) and Table 2-7 contains a description of the bits.

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Figure 2-5. CFGBRIDGE Register Bit Layout (0x4000 0024)

Table 2-7. CFGBRIDGE Register Bit Field Description (0x4000 0024)

| BIT NO. | NAME     | RESET VALUE | READ WRITE | DESCRIPTION                                                                                    |

|---------|----------|-------------|------------|------------------------------------------------------------------------------------------------|

| 31:1    | Reserved | N/A         | N/A        | Reads are indeterminate. Only 0s should be written to these bits.                              |

| 0       | CSPRST   | 1           | R/W        | Resets the CSP Bridge (BR2 in Figure 2-4). 1 = Bridge Reset Asserted 0 = Bridge Reset Released |

## **CAUTION**

The CSPRST bit must be asserted after any change to the PLL that affects SYSCLK1 and SYSCLK2 and must be released before any accesses to the CSP bridge occur from either the dMAX or the UHPI.

# 2.7 Memory Map Summary

A high-level memory map of the C672x DSP appears in Table 2-8. The base address of each region is listed. *Any address past the end address must not be read or written.* The table also lists whether the regions are word-addressable or byte- and word-addressable.

Table 2-8. C672x Memory Map

| DESCRIPTION                                    | BASE ADDRESS | END ADDRESS | BYTE- OR WORD-ADDRESSABLE |

|------------------------------------------------|--------------|-------------|---------------------------|

| Internal ROM Page 0 (256K Bytes)               | 0x0000 0000  | 0x0003 FFFF | Byte and Word             |

| Internal ROM Page 1 (128K Bytes)               | 0x0004 0000  | 0x0005 FFFF | Byte and Word             |

| Internal RAM Page 0 (256K Bytes)               | 0x1000 0000  | 0x1003 FFFF | Byte and Word             |

| Memory and Cache Control Registers             | 0x2000 0000  | 0x2000 001F | Word Only                 |

| Emulation Control Registers (Do Not Access)    | 0x3000 0000  | 0x3FFF FFFF | Word Only                 |

| Device Configuration Registers                 | 0x4000 0000  | 0x4000 0083 | Word Only                 |

| PLL Control Registers                          | 0x4100 0000  | 0x4100 015F | Word Only                 |

| Real-time Interrupt (RTI) Control Registers    | 0x4200 0000  | 0x4200 00A3 | Word Only                 |

| Universal Host-Port Interface (UHPI) Registers | 0x4300 0000  | 0x4300 0043 | Word Only                 |

| McASP0 Control Registers                       | 0x4400 0000  | 0x4400 02BF | Word Only                 |

| McASP1 Control Registers                       | 0x4500 0000  | 0x4500 02BF | Word Only                 |

| McASP2 Control Registers                       | 0x4600 0000  | 0x4600 02BF | Word Only                 |

| SPI0 Control Registers                         | 0x4700 0000  | 0x4700 007F | Word Only                 |

| SPI1 Control Registers                         | 0x4800 0000  | 0x4800 007F | Word Only                 |

| I2C0 Control Registers                         | 0x4900 0000  | 0x4900 007F | Word Only                 |

| I2C1 Control Registers                         | 0x4A00 0000  | 0x4A00 007F | Word Only                 |

| McASP0 DMA Port (any address in this range)    | 0x5400 0000  | 0x54FF FFFF | Word Only                 |

| McASP1 DMA Port (any address in this range)    | 0x5500 0000  | 0x55FF FFFF | Word Only                 |

| McASP2 DMA Port (any address in this range)    | 0x5600 0000  | 0x56FF FFFF | Word Only                 |

| dMAX Control Registers                         | 0x6000 0000  | 0x6000 008F | Word Only                 |

| MAX0 (HiMAX) Event Entry Table                 | 0x6100 8000  | 0x6100 807F | Byte and Word             |

| Reserved                                       | 0x6100 8080  | 0x6100 809F |                           |

| MAX0 (HiMAX) Transfer Entry Table              | 0x6100 80A0  | 0x6100 81FF | Byte and Word             |

| MAX1 (LoMAX) Event Entry Table                 | 0x6200 8000  | 0x6200 807F | Byte and Word             |

| Reserved                                       | 0x6200 8080  | 0x6200 809F |                           |

| MAX1 (LoMAX) Transfer Entry Table              | 0x6200 80A0  | 0x6200 81FF | Byte and Word             |

| External SDRAM space on EMIF                   | 0x8000 0000  | 0x8FFF FFFF | Byte and Word             |

| External Asynchronous / Flash space on EMIF    | 0x9000 0000  | 0x9FFF FFFF | Byte and Word             |

| EMIF Control Registers                         | 0xF000 0000  | 0xF000 00BF | Word Only <sup>(1)</sup>  |

<sup>(1)</sup> The upper byte of the EMIF's SDRAM Configuration Register (SDCR[31:24]) is byte-addressable to support placing the EMIF into the Self-Refresh State without triggering the SDRAM Initialization Sequence.

#### 2.8 Boot Modes

The C672x DSP supports only one hardware bootmode option, this is to boot from the internal ROM starting at address 0x0000 0000. Other bootmode options are implemented by a software bootloader stored in ROM. The software bootloader uses the CFGPIN0 and CFGPIN1 registers, which capture the state of various device pins at reset, to determine which mode to enter. Note that in practice, only a few pins are used by the software.

#### **CAUTION**

Only an externally applied RESET causes the CFGPIN0 and CFGPIN1 registers to recapture their associated pin values. Neither an emulator reset nor a RTI reset causes these registers to update.

#### The ROM bootmodes include:

- Parallel Flash on EM CS[2]

- SPI0 or I2C1 master mode from serial EEPROM

- SPI0 or I2C1 slave mode from external MCU

- UHPI from an external MCU

Table 2-9 describes the required boot pin settings at device reset for each bootmode.

Table 2-9. Required Boot Pin Settings at Device Reset

| BOOT MODE      | UHPI_HCS | SPI0_SOMI             | SPI0_SIMO           | SPI0_CLK            |

|----------------|----------|-----------------------|---------------------|---------------------|

| UHPI           | 0        | BYTEAD <sup>(1)</sup> | FULL <sup>(1)</sup> | NMUX <sup>(1)</sup> |

| Parallel Flash | 1        | 0                     | 1                   | 0                   |

| SPI0 Master    | 1        | 0                     | 0                   | 1                   |

| SPI0 Slave     | 1        | 0                     | 1                   | 1                   |

| I2C1 Master    | 1        | 1                     | 0                   | 1                   |

| I2C1 Slave     | 1        | 1                     | 1                   | 1                   |

<sup>(1)</sup> When UHPI\_HCS is 0, the state of the SPI0\_SOMI, SPI0\_SIMO, and SPI0\_CLK pins is copied into the specified bits in the CFGHPI register described in Table 4-12.

Refer to the C9230C100 TMS320C672x Floating-Point Digital Signal Processor ROM Data Manual (literature number SPRS277) for details on supported bootmodes and their implementation.

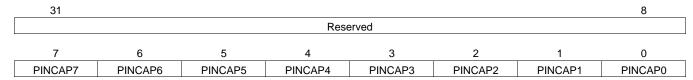

Figure 2-6 shows the bit layout of the CFGPIN0 register and Table 2-10 contains a description of the bits.

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

# Figure 2-6. CFGPIN0 Register Bit Layout (0x4000 0000)

# Table 2-10. CFGPIN0 Register Bit Field Description (0x4000 0000)

| BIT NO. | NAME     | DESCRIPTION                                                               |

|---------|----------|---------------------------------------------------------------------------|

| 31:8    | Reserved | Reads are indeterminate. Only 0s should be written to these bits.         |

| 7       | PINCAP7  | SPI0_SOMI/I2C0_SDA pin state captured on rising edge of RESET pin.        |

| 6       | PINCAP6  | SPI0_SIMO pin state captured on rising edge of RESET pin.                 |

| 5       | PINCAP5  | SPI0_CLK/I2C0_SCL pin state captured on rising edge of RESET pin.         |

| 4       | PINCAP4  | SPI0_SCS/I2C1_SCL pin state captured on rising edge of RESET pin.         |

| 3       | PINCAP3  | SPI0_ENA/I2C1_SDA pin state captured on rising edge of RESET pin.         |

| 2       | PINCAP2  | AXR0[8]/AXR1[5]/SPI1_SOMI pin state captured on rising edge of RESET pin. |

| 1       | PINCAP1  | AXR0[9]/AXR1[4]/SPI1_SIMO pin state captured on rising edge of RESET pin. |

| 0       | PINCAP0  | AXR0[7]/SPI1_CLK pin state captured on rising edge of RESET pin.          |

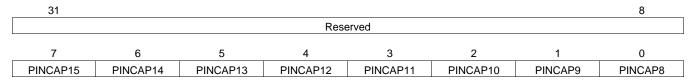

Figure 2-7 shows the bit layout of the CFGPIN1 register and Table 2-11 contains a description of the bits.

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

# Figure 2-7. CFGPIN1 Register Bit Layout (0x4000 0004)

# Table 2-11. CFGPIN1 Register Bit Field Description (0x4000 0004)

| BIT NO. | NAME     | DESCRIPTION                                                         |

|---------|----------|---------------------------------------------------------------------|

| 31:8    | Reserved | Reads are indeterminate. Only 0s should be written to these bits.   |

| 7       | PINCAP15 | AXR0[5]/SPI1_SCS pin state captured on rising edge of RESET pin.    |

| 6       | PINCAP14 | AXR0[6]/SPI1_ENA pin state captured on rising edge of RESET pin.    |

| 5       | PINCAP13 | UHPI_HCS pin state captured on rising edge of RESET pin.            |

| 4       | PINCAP12 | UHPI_HD[0] pin state captured on rising edge of RESET pin.          |

| 3       | PINCAP11 | EM_D[16]/UHPI_HA[0] pin state captured on rising edge of RESET pin. |

| 2       | PINCAP10 | AFSX0 pin state captured on rising edge of RESET pin.               |

| 1       | PINCAP9  | AFSR0 pin state captured on rising edge of RESET pin.               |

| 0       | PINCAP8  | AXR0[0] pin state captured on rising edge of RESET pin.             |

# 2.9 Pin Assignments

# 2.9.1 Pin Maps

Figure 2-8 shows the pin assignments on the 256-terminal GDH package.

| Т | V <sub>SS</sub>           | DV <sub>DD</sub>            | EM_WE                       | EM_D[7]                     | EM_D[5]                     | EM_D[3]                     | V <sub>SS</sub>              | EM_D[0]                      | EM_D[14]                              | V <sub>SS</sub>              | EM_D[11]                    | EM_D[9]          | EM_WE_<br>DQM[1] | EM_CKE                         | DV <sub>DD</sub>          | V <sub>SS</sub>           |

|---|---------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|------------------------------|------------------------------|---------------------------------------|------------------------------|-----------------------------|------------------|------------------|--------------------------------|---------------------------|---------------------------|

| R | DV <sub>DD</sub>          | EM_D[23]<br>/UHPI_<br>HA[7] | EM_CAS                      | EM_WE_<br>DQM[0]            | EM_D[6]                     | EM_D[4]                     | EM_D[2]                      | EM_D[1]                      | EM_D[15]                              | EM_D[13]                     | EM_D[12]                    | EM_D[10]         | EM_D[8]          | EM_CLK                         | EM_WE_<br>DQM[3]          | DV <sub>DD</sub>          |

| Р | TCK                       | UHPI_<br>HD[24]             | EM_D[21]<br>/UHPI_<br>HA[5] | EM_D[20]<br>/UHPI_<br>HA[4] | EM_D[19]<br>/UHPI_<br>HA[3] | EM_D[17]<br>/UHPI_<br>HA[1] | EM_D[31]<br>/UHPI_<br>HA[15] | DV <sub>DD</sub>             | EM_D[28]<br>/UHPI_<br>HA[12]          | EM_D[26]<br>/UHPI_<br>HA[10] | EM_D[24]<br>/UHPI_<br>HA[8] | EM_A[12]         | EM_WE_<br>DQM[2] | UHPI_<br>HD[7]                 | EM_A[11]                  | EM_A[9]                   |

| N | EMU[1]                    | UHPI_<br>HD[25]             | UHPI_<br>HD[26]             | EM_D[22]<br>/UHPI_<br>HA[6] | DV <sub>DD</sub>            | EM_D[18]<br>/UHPI_<br>HA[2] | EM_D[16]<br>/UHPI_<br>HA[0]  | EM_D[30]<br>/UHPI_<br>HA[14] | EM_D[29]<br>/UHPI_<br>HA[13]          | EM_D[27]<br>/UHPI<br>HA[11]  | EM_D[25]<br>/UHPI_<br>HA[9] | DV <sub>DD</sub> | UHPI_<br>HD[5]   | UHPI_<br>HD[6]                 | EM_A[8]                   | EM_A[7]                   |

| М | EMU[0]                    | TDO                         | UHPI_<br>HD[27]             | DV <sub>DD</sub>            | V <sub>SS</sub>             | CV <sub>DD</sub>            | CV <sub>DD</sub>             | CV <sub>DD</sub>             | CV <sub>DD</sub>                      | CV <sub>DD</sub>             | CV <sub>DD</sub>            | V <sub>SS</sub>  | DV <sub>DD</sub> | UHPI_<br>HD[2]                 | EM_A[6]                   | EM_A[5]                   |

| L | TDI                       | UHPI_<br>HD[30]             | UHPI_<br>HD[28]             | UHPI_<br>HD[29]             | V <sub>SS</sub>             | V <sub>SS</sub>             | V <sub>SS</sub>              | V <sub>SS</sub>              | V <sub>SS</sub>                       | V <sub>SS</sub>              | V <sub>SS</sub>             | V <sub>SS</sub>  | UHPI_<br>HD[3]   | UHPI_<br>HD[4]                 | EM_A[4]                   | EM_A[3]                   |

| K | V <sub>SS</sub>           | PLLHV                       | TMS                         | TRST                        | CV <sub>DD</sub>            | V <sub>SS</sub>             | V <sub>SS</sub>              | V <sub>SS</sub>              | V <sub>SS</sub>                       | V <sub>SS</sub>              | V <sub>SS</sub>             | CV <sub>DD</sub> | UHPI_<br>HD[0]   | UHPI_<br>HD[1]                 | EM_A[2]                   | V <sub>SS</sub>           |

| J | OSCV <sub>SS</sub>        | OSCIN                       | OSCOUT                      | OSCV <sub>DD</sub>          | CV <sub>DD</sub>            | V <sub>SS</sub>             | V <sub>SS</sub>              | V <sub>SS</sub>              | V <sub>SS</sub>                       | V <sub>SS</sub>              | V <sub>SS</sub>             | CV <sub>DD</sub> | UHPI<br>HD[15]   | DV <sub>DD</sub>               | EM_A[1]                   | EM_A[0]                   |

| Н | UHPI_<br>HD[16]<br>/HHWIL | CLKIN                       | V <sub>SS</sub>             | UHPI_<br>HD[31]             | CV <sub>DD</sub>            | V <sub>SS</sub>             | V <sub>SS</sub>              | V <sub>SS</sub>              | V <sub>SS</sub>                       | V <sub>SS</sub>              | V <sub>SS</sub>             | CV <sub>DD</sub> | UHPI_<br>HD[14]  | UHPI_<br>HD[13]                | EM_A[10]                  | EM_BA[1]                  |

| G | V <sub>SS</sub>           | RESET                       | UHPI_<br>HD[17]             | UHPI_<br>HD[18]             | CV <sub>DD</sub>            | V <sub>SS</sub>             | V <sub>SS</sub>              | V <sub>SS</sub>              | V <sub>SS</sub>                       | V <sub>SS</sub>              | V <sub>SS</sub>             | CV <sub>DD</sub> | UHPI_<br>HD[12]  | UHPI_<br>HD[11]                | EM_BA[0]                  | V <sub>SS</sub>           |

| F | AFSR1                     | AFSX1                       | UHPI_<br>HD[19]             | UHPI_<br>HD[20]             | V <sub>SS</sub>             | V <sub>SS</sub>             | V <sub>SS</sub>              | V <sub>SS</sub>              | V <sub>SS</sub>                       | V <sub>SS</sub>              | V <sub>SS</sub>             | V <sub>SS</sub>  | UHPI_<br>HD[10]  | UHPI_<br>HD[9]                 | EM_CS[0]                  | EM_RAS                    |

| Е | ACLKR1                    | ACLKX1                      | UHPI_<br>HD[21]             | DV <sub>DD</sub>            | V <sub>SS</sub>             | CV <sub>DD</sub>            | CV <sub>DD</sub>             | CV <sub>DD</sub>             | CV <sub>DD</sub>                      | CV <sub>DD</sub>             | CV <sub>DD</sub>            | V <sub>SS</sub>  | DV <sub>DD</sub> | UHPI_<br>HD[8]                 | EM_CS[2]                  | EM_RW                     |

| D | AHCLKX1                   | AMUTE1                      | UHPI_<br>HD[22]             | DV <sub>DD</sub>            | DV <sub>DD</sub>            | UHPI<br>HRDÝ                | UHPI_<br>HDS[1]              | UHPI_<br>HRW                 | UHPI_<br>HCNTL[0]                     | AMUTE2/<br>HINT              | ACLKX2                      | DV <sub>DD</sub> | DV <sub>DD</sub> | EM_WAIT                        | EM_OE                     | SPIO_ENA<br>/I2C1_<br>SDA |

| С | AMUTE0                    | AHCLKX0<br>/AHCLKX2         | UHPI_<br>HD[23]             | UHPI_<br>HBE[2]             | UHPI<br>HBE[1]              | UHPI_<br>HBE[0]             | UHPI_<br>HDS[2]              | UHPI_<br>HCS                 | UHPI_<br>HAS                          | UHPI_<br>HCNTL[1]            | AFSX2                       | AFSR2            | ACLKR2           | AHCLKR2                        | SPI0_SCS<br>/I2C1_<br>SCL | SPI0_CLK<br>/I2C0_<br>SCL |

| В | DV <sub>DD</sub>          | UHPI_<br>HBE[3]             | AHCLKR0<br>/AHCLKR1         | AFSR0                       | AXR0[15]<br>/AXR2[0]        | AXR0[13]<br>/AXR1[0]        | AXR0[12]<br>/AXR1[1]         | AXR0[10]<br>/AXR1[3]         | AXR0[8]<br>/AXR1[5]<br>/SPI1_<br>SOMI | AXR0[7]<br>/SPI1_<br>CLK     | AXR0[5]<br>/SPI1_<br>SCS    | AXR0[3]          | AXR0[1]          | SPI0_<br>SOMI<br>/I2C0_<br>SDA | SPI0_<br>SIMO             | DV <sub>DD</sub>          |

| Α | V <sub>SS</sub>           | DV <sub>DD</sub>            | AFSX0                       | ACLKX0                      | ACLKR0                      | AXR0[14]<br>/AXR2[1]        | V <sub>SS</sub>              | AXR0[11]<br>/AXR1[2]         | AXR0[9]<br>/AXR1[4]<br>/SPI1_<br>SIMO | V <sub>SS</sub>              | AXR0[6]<br>/SPI1<br>ENA     | AXR0[4]          | AXR0[2]          | AXR0[0]                        | DV <sub>DD</sub>          | V <sub>SS</sub>           |

|   | 1                         | 2                           | 3                           | 4                           | 5                           | 6                           | 7                            | 8                            | 9                                     | 10                           | 11                          | 12               | 13               | 14                             | 15                        | 16                        |

Figure 2-8. 256-Terminal Ball Grid Array (GDH Suffix)—Bottom View

### 2.9.2 Terminal Functions

Table 2-12, the Terminal Functions table, identifies the external signal names, the associated pin/ball numbers along with the mechanical package designator, the pin type (I, O, IO, OZ, or PWR), whether the pin/ball has any internal pullup/pulldown resistors, whether the pin/ball is configurable as an IO in GPIO mode, and a functional pin description.

**Table 2-12. Terminal Functions**

| SIGNAL NAME  | PIN | TYPE <sup>(1)</sup> | PULL <sup>(2)</sup> | GPIO <sup>(3)</sup> | DESCRIPTION                                                                           |

|--------------|-----|---------------------|---------------------|---------------------|---------------------------------------------------------------------------------------|

|              |     | External Me         | emory Interfa       | ace (EMIF)          | Address and Control                                                                   |

| EM_A[0]      | J16 | 0                   | -                   | N                   |                                                                                       |

| EM_A[1]      | J15 | 0                   | -                   | N                   |                                                                                       |

| EM_A[2]      | K15 | 0                   | -                   | N                   |                                                                                       |

| EM_A[3]      | L16 | 0                   | -                   | N                   |                                                                                       |

| EM_A[4]      | L15 | 0                   | -                   | N                   |                                                                                       |

| EM_A[5]      | M16 | 0                   | -                   | N                   |                                                                                       |

| EM_A[6]      | M15 | 0                   | -                   | N                   | EMIF Address Bus                                                                      |

| EM_A[7]      | N16 | 0                   | -                   | N                   |                                                                                       |

| EM_A[8]      | N15 | 0                   | -                   | N                   |                                                                                       |

| EM_A[9]      | P16 | 0                   | -                   | N                   |                                                                                       |

| EM_A[10]     | H15 | 0                   | -                   | N                   |                                                                                       |

| EM_A[11]     | P15 | 0                   | -                   | N                   |                                                                                       |

| EM_A[12]     | P12 | 0                   | IPD                 | N                   |                                                                                       |

| EM_BA[0]     | G15 | 0                   | -                   | N                   | SDRAM Bank Address and Asynchronous Memory                                            |

| EM_BA[1]     | H16 | 0                   | -                   | N                   | Low-Order Address                                                                     |

| EM_CS[0]     | F15 | 0                   | -                   | N                   | SDRAM Chip Select                                                                     |

| EM_CS[2]     | E15 | 0                   | -                   | N                   | Asynchronous Memory Chip Select                                                       |

| EM_CAS       | R3  | 0                   | -                   | N                   | SDRAM Column Address Strobe                                                           |

| EM_RAS       | F16 | 0                   | -                   | N                   | SDRAM Row Address Strobe                                                              |

| EM_WE        | Т3  | 0                   | -                   | N                   | SDRAM/Asynchronous Write Enable                                                       |

| EM_CKE       | T14 | 0                   | -                   | N                   | SDRAM Clock Enable                                                                    |

| EM_CLK       | R14 | 0                   | -                   | N                   | EMIF Output Clock                                                                     |

| EM_WE_DQM[0] | R4  | 0                   | -                   | N                   | Write Enable or Byte Enable for EM_D[7:0]                                             |

| EM_WE_DQM[1] | T13 | 0                   | -                   | N                   | Write Enable or Byte Enable for EM_D[15:8]                                            |

| EM_WE_DQM[2] | P13 | 0                   | IPU                 | N                   | Write Enable or Byte Enable for EM_D[23:16]                                           |

| EM_WE_DQM[3] | R15 | 0                   | IPU                 | N                   | Write Enable or Byte Enable for EM_D[31:24]                                           |

| EM_OE        | D15 | 0                   | -                   | N                   | SDRAM/Asynchronous Output Enable                                                      |

| EM_RW        | E16 | 0                   | -                   | N                   | Asynchronous Memory Read/not Write                                                    |

| EM_WAIT      | D14 | 1                   | IPU                 | N                   | Asynchronous Wait Input ( <i>Programmable Polarity</i> ) or Interrupt ( <i>NAND</i> ) |

<sup>(1)</sup> TYPE column refers to pin direction in functional mode. If a pin has more than one function with different directions, the functions are separated with a slash (/).

<sup>(2)</sup> PULL column:

IPD = Internal Pulldown resistor

IPU = Internal Pullup resistor

<sup>(3)</sup> If the GPIO column is 'Y', then in GPIO mode, the pin is configurable as an IO unless otherwise marked.

| SIGNAL NAME          | PIN         | TYPE <sup>(1)</sup> | PULL <sup>(2)</sup> | GPIO <sup>(3)</sup> | DESCRIPTION                                 |

|----------------------|-------------|---------------------|---------------------|---------------------|---------------------------------------------|

| External Mem         | ory Interfa | ace (EMIF) D        | Data Bus / U        | niversal Hos        | st-Port Interface (UHPI) Address Bus Option |

| EM_D[0]              | T8          | Ю                   | -                   | N                   |                                             |

| EM_D[1]              | R8          | Ю                   | -                   | N                   |                                             |

| EM_D[2]              | R7          | Ю                   | -                   | N                   |                                             |

| EM_D[3]              | T6          | Ю                   | -                   | N                   |                                             |

| EM_D[4]              | R6          | Ю                   | -                   | N                   |                                             |

| EM_D[5]              | T5          | Ю                   | -                   | N                   |                                             |

| EM_D[6]              | R5          | Ю                   | -                   | N                   |                                             |

| EM_D[7]              | T4          | Ю                   | -                   | N                   | FAME Data Date Name 40 Dital                |

| EM_D[8]              | R13         | Ю                   | -                   | N                   | EMIF Data Bus [Lower 16 Bits]               |

| EM_D[9]              | T12         | Ю                   | -                   | N                   |                                             |

| EM_D[10]             | R12         | Ю                   | -                   | N                   |                                             |

| EM_D[11]             | T11         | Ю                   | -                   | N                   |                                             |

| EM_D[12]             | R11         | Ю                   | -                   | N                   |                                             |

| EM_D[13]             | R10         | Ю                   | -                   | N                   |                                             |

| EM_D[14]             | Т9          | Ю                   | -                   | N                   |                                             |

| EM_D[15]             | R9          | Ю                   | -                   | N                   |                                             |

| EM_D[16]/UHPI_HA[0]  | N7          | IO/I                | IPD                 | N                   |                                             |

| EM_D[17]/UHPI_HA[1]  | P6          | IO/I                | IPD                 | N                   |                                             |

| EM_D[18]/UHPI_HA[2]  | N6          | IO/I                | IPD                 | N                   |                                             |

| EM_D[19]/UHPI_HA[3]  | P5          | IO/I                | IPD                 | N                   |                                             |

| EM_D[20]/UHPI_HA[4]  | P4          | IO/I                | IPD                 | N                   |                                             |

| EM_D[21]/UHPI_HA[5]  | P3          | IO/I                | IPD                 | N                   |                                             |

| EM_D[22]/UHPI_HA[6]  | N4          | IO/I                | IPD                 | N                   |                                             |

| EM_D[23]/UHPI_HA[7]  | R2          | IO/I                | IPD                 | N                   | EMIF Data Bus [Upper 16 Bits (IO)] or       |

| EM_D[24]/UHPI_HA[8]  | P11         | IO/I                | IPD                 | N                   | UHPI Address Input (I)                      |

| EM_D[25]/UHPI_HA[9]  | N11         | IO/I                | IPD                 | N                   |                                             |

| EM_D[26]/UHPI_HA[10] | P10         | IO/I                | IPD                 | N                   |                                             |

| EM_D[27]/UHPI_HA[11] | N10         | IO/I                | IPD                 | N                   |                                             |

| EM_D[28]/UHPI_HA[12] | P9          | IO/I                | IPD                 | N                   |                                             |

| EM_D[29]/UHPI_HA[13] | N9          | IO/I                | IPD                 | N                   |                                             |

| EM_D[30]/UHPI_HA[14] | N8          | IO/I                | IPD                 | N                   |                                             |

| EM_D[31]/UHPI_HA[15] | P7          | IO/I                | IPD                 | N                   |                                             |

| SIGNAL NAME       | PIN | TYPE <sup>(1)</sup> | PULL <sup>(2)</sup> | GPIO <sup>(3)</sup> | DESCRIPTION                                                                                         |  |

|-------------------|-----|---------------------|---------------------|---------------------|-----------------------------------------------------------------------------------------------------|--|

| SIGNAL NAME       | FIN |                     | 1                   |                     | PI) Data and Control                                                                                |  |

| UHPI_HD[0]        | K13 | IO                  | IPD                 | Y                   | Fi) Data and Control                                                                                |  |

|                   | K13 | 10                  | IPD                 | Y                   |                                                                                                     |  |

| UHPI_HD[1]        | M14 | 10                  | IPD                 | Y                   |                                                                                                     |  |

| UHPI_HD[2]        |     |                     |                     | Y                   |                                                                                                     |  |

| UHPI_HD[3]        | L13 | 10                  | IPD                 |                     |                                                                                                     |  |

| UHPI_HD[4]        | L14 | 10                  | IPD                 | Y                   | _                                                                                                   |  |

| UHPI_HD[5]        | N13 | 10                  | IPD                 | Y                   |                                                                                                     |  |

| UHPI_HD[6]        | N14 | 10                  | IPD                 | Y                   |                                                                                                     |  |

| UHPI_HD[7]        | P14 | Ю                   | IPD                 | Υ                   | UHPI Data Bus [Lower 16 Bits]                                                                       |  |

| UHPI_HD[8]        | E14 | IO                  | IPD                 | Y                   |                                                                                                     |  |

| UHPI_HD[9]        | F14 | Ю                   | IPD                 | Υ                   |                                                                                                     |  |

| UHPI_HD[10]       | F13 | Ю                   | IPD                 | Υ                   |                                                                                                     |  |

| UHPI_HD[11]       | G14 | Ю                   | IPD                 | Υ                   |                                                                                                     |  |

| UHPI_HD[12]       | G13 | Ю                   | IPD                 | Υ                   |                                                                                                     |  |

| UHPI_HD[13]       | H14 | Ю                   | IPD                 | Υ                   |                                                                                                     |  |

| UHPI_HD[14]       | H13 | Ю                   | IPD                 | Υ                   |                                                                                                     |  |

| UHPI_HD[15]       | J13 | Ю                   | IPD                 | Υ                   |                                                                                                     |  |

| UHPI_HD[16]/HHWIL | H1  | IO/I                | IPD                 | Υ                   |                                                                                                     |  |

| UHPI_HD[17]       | G3  | Ю                   | IPD                 | Υ                   |                                                                                                     |  |

| UHPI_HD[18]       | G4  | Ю                   | IPD                 | Υ                   |                                                                                                     |  |

| UHPI_HD[19]       | F3  | Ю                   | IPD                 | Υ                   |                                                                                                     |  |

| UHPI_HD[20]       | F4  | Ю                   | IPD                 | Υ                   | LILIDI Data Dua II Innar 16 Dita (IO)) in the following modes:                                      |  |

| UHPI_HD[21]       | E3  | Ю                   | IPD                 | Υ                   | UHPI Data Bus [Upper 16 Bits (IO)] in the following modes:  • Fullword Multiplexed Address and Data |  |

| UHPI_HD[22]       | D3  | Ю                   | IPD                 | Υ                   | Fullword Non-Multiplexed                                                                            |  |

| UHPI_HD[23]       | C3  | Ю                   | IPD                 | Υ                   | UHPI_HHWIL (I) on pin UHPI_HD[16]/HHWIL and GPIO on                                                 |  |

| UHPI_HD[24]       | P2  | IO                  | IPD                 | Υ                   | other pins in the following mode:                                                                   |  |

| UHPI_HD[25]       | N2  | IO                  | IPD                 | Υ                   | Half-word Multiplexed Address and Data                                                              |  |

| UHPI_HD[26]       | N3  | Ю                   | IPD                 | Υ                   | In this mode, UHPI_HHWIL indicates whether the high or                                              |  |

| UHPI_HD[27]       | M3  | 10                  | IPD                 | Y                   | low half-word is being addressed.                                                                   |  |

| UHPI_HD[28]       | L3  | 10                  | IPD                 | Y                   |                                                                                                     |  |

| UHPI_HD[29]       | L4  | 10                  | IPD                 | Y                   | _                                                                                                   |  |

| UHPI_HD[30]       | L2  | 10                  | IPD                 | Y                   | _                                                                                                   |  |

| UHPI_HD[31]       | H4  | 10                  | IPD                 | Y                   |                                                                                                     |  |

| 0111 [110[31]     | 114 |                     | -                   |                     | (UHPI) Control                                                                                      |  |

| UHPI_HBE[0]       | C6  | I                   | IPD                 | Y                   | UHPI Byte Enable for UHPI_HD[7:0]                                                                   |  |

| UHPI_HBE[1]       | C5  | ı                   | IPD                 | Y                   | UHPI Byte Enable for UHPI_HD[15:8]                                                                  |  |

|                   | C3  | 1                   | IPD                 | Y                   | <del>                                     </del>                                                    |  |

| UHPI_HBE[2]       |     |                     |                     |                     | UHPI Byte Enable for UHPI_HD[23:16]                                                                 |  |

| UHPI_HBE[3]       | B2  | <u>l</u>            | IPD                 | Y                   | UHPI Byte Enable for UHPI_HD[31:24]                                                                 |  |

| UHPI_HCNTL[0]     | D9  | <u>l</u>            | IPD                 | Y                   | UHPI Control Inputs Select Access Mode                                                              |  |

| UHPI_HCNTL[1]     | C10 | I                   | IPD                 | Y                   |                                                                                                     |  |

| UHPI_HAS          | C9  | I                   | IPD                 | Y                   | UHPI Host Address Strobe for Hosts with Multiplexed Address/Data bus  UHPI Read/not Write Input     |  |

| UHPI_HRW          | D8  | I                   | IPD                 | Υ                   |                                                                                                     |  |

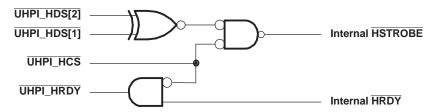

| UHPI_HDS[1]       | D7  | I                   | IPU                 | Υ                   | UHPI Select Signals which create the internal HSTROBE                                               |  |

| UHPI_HDS[2]       | C7  | I                   | IPU                 | Υ                   | active when:                                                                                        |  |

| UHPI_HCS          | C8  | I                   | IPU                 | Υ                   | $(\overline{UHPI\_HCS} == '0') \& (\overline{UHPI\_HDS[1]} != \overline{UHPI\_HDS[2]})$             |  |

| UHPI_HRDY         | D6  | 0                   | IPD                 | Υ                   | UHPI Ready Output                                                                                   |  |

| SIGNAL NAME                   | PIN | TYPE <sup>(1)</sup> | PULL <sup>(2)</sup> | GPIO <sup>(3)</sup> | DESCRIPTION                                                                                     |

|-------------------------------|-----|---------------------|---------------------|---------------------|-------------------------------------------------------------------------------------------------|

|                               |     | McASP0.             |                     | cASP2. and          | SPI1 Serial Ports                                                                               |

| AHCLKR0/AHCLKR1               | В3  | IO .                | -                   | Y                   | McASP0 and McASP1 Receive Master Clock                                                          |

| ACLKR0                        | A5  | IO                  | -                   | Υ                   | McASP0 Receive Bit Clock                                                                        |

| AFSR0                         | B4  | Ю                   | -                   | Υ                   | McASP0 Receive Frame Sync (L/R Clock)                                                           |

| AHCLKX0/AHCLKX2               | C2  | IO                  | -                   | Y                   | McASP0 and McASP2 Transmit Master Clock <sup>(4)</sup>                                          |

| ACLKX0                        | A4  | Ю                   | -                   | Υ                   | McASP0 Transmit Bit Clock                                                                       |

| AFSX0                         | А3  | Ю                   | -                   | Υ                   | McASP0 Transmit Frame Sync (L/R Clock)                                                          |

| AMUTE0                        | C1  | 0                   | -                   | Υ                   | McASP0 MUTE Output                                                                              |

| AXR0[0]                       | A14 | Ю                   | ē                   | Υ                   | McASP0 Serial Data 0                                                                            |

| AXR0[1]                       | B13 | Ю                   | ē                   | Υ                   | McASP0 Serial Data 1                                                                            |

| AXR0[2]                       | A13 | Ю                   | -                   | Υ                   | McASP0 Serial Data 2                                                                            |

| AXR0[3]                       | B12 | Ю                   | -                   | Y                   | McASP0 Serial Data 3                                                                            |

| AXR0[4]                       | A12 | Ю                   | -                   | Υ                   | McASP0 Serial Data 4                                                                            |

| AXR0[5]/SPI1_SCS              | B11 | Ю                   | -                   | Y                   | McASP0 Serial Data 5 or SPI1 Slave Chip Select                                                  |

| AXR0[6]/SPI1_ENA              | A11 | Ю                   | -                   | Υ                   | McASP0 Serial Data 6 or SPI1 Enable (Ready)                                                     |

| AXR0[7]/SPI1_CLK              | B10 | Ю                   | -                   | Υ                   | McASP0 Serial Data 7 or SPI1 Serial Clock                                                       |