- Advanced Multibus Architecture With Three Separate 16-Bit Data Memory Buses and One Program Memory Bus

- 40-Bit Arithmetic Logic Unit (ALU) Including a 40-Bit Barrel Shifter and Two Independent 40-Bit Accumulators

- 17- × 17-Bit Parallel Multiplier Coupled to a 40-Bit Dedicated Adder for Non-Pipelined Single-Cycle Multiply/Accumulate (MAC) Operation

- Compare, Select, and Store Unit (CSSU) for the Add/Compare Selection of the Viterbi Operator

- Exponent Encoder to Compute an Exponent Value of a 40-Bit Accumulator Value in a Single Cycle

- Two Address Generators With Eight Auxiliary Registers and Two Auxiliary Register Arithmetic Units (ARAUs)

- Data Bus With a Bus Holder Feature

- Address Bus With a Bus Holder Feature

- Extended Addressing Mode for 8M × 16-Bit Maximum Addressable External Program Space

- 192K × 16-Bit Maximum Addressable Memory Space (64K Words Program, 64K Words Data, and 64K Words I/O)

- On-Chip ROM with Some Configurable to Program/Data Memory

- Dual-Access On-Chip RAM

- Single-Access On-Chip RAM

- Single-Instruction Repeat and Block-Repeat Operations for Program Code

- Block-Memory-Move Instructions for Better Program and Data Management

- Instructions With a 32-Bit Long Word Operand

- Instructions With Two- or Three-Operand Reads

- Arithmetic Instructions With Parallel Store and Parallel Load

- Conditional Store Instructions

- Fast Return From Interrupt

- On-Chip Peripherals

- Software-Programmable Wait-State Generator and Programmable Bank Switching

- On-Chip Phase-Locked Loop (PLL) Clock Generator With Internal Oscillator or External Clock Source

- Time-Division Multiplexed (TDM) Serial Port

- Buffered Serial Port (BSP)

- 8-Bit Parallel Host Port Interface (HPI)

- One 16-Bit Timer

- External-Input/Output (XIO) Off Control to Disable the External Data Bus,

Address Bus and Control Signals

- Power Consumption Control With IDLE1, IDLE2, and IDLE3 Instructions With Power-Down Modes

- CLKOUT Off Control to Disable CLKOUT

- On-Chip Scan-Based Emulation Logic, IEEE Std 1149.1<sup>†</sup> (JTAG) Boundary Scan Logic

- 12.5-ns Single-Cycle Fixed-Point Instruction Execution Time (80 MIPS) for 3.3-V Power Supply)

- 10-ns Single-Cycle Fixed-Point Instruction Execution Time (100 MIPS) for 3.3-V Power Supply (2.5-V Core)

- 8.3-ns Single-Cycle Fixed-Point Instruction Execution Time (120 MIPS) for 3.3-V Power Supply (2.5-V Core)

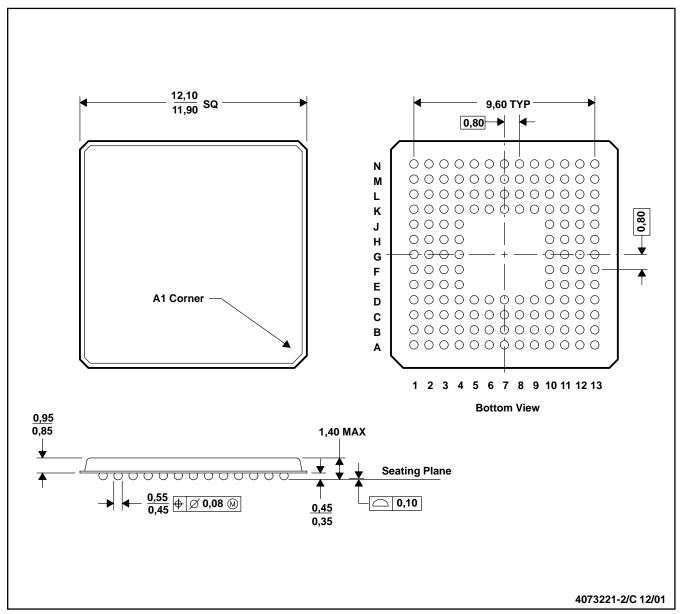

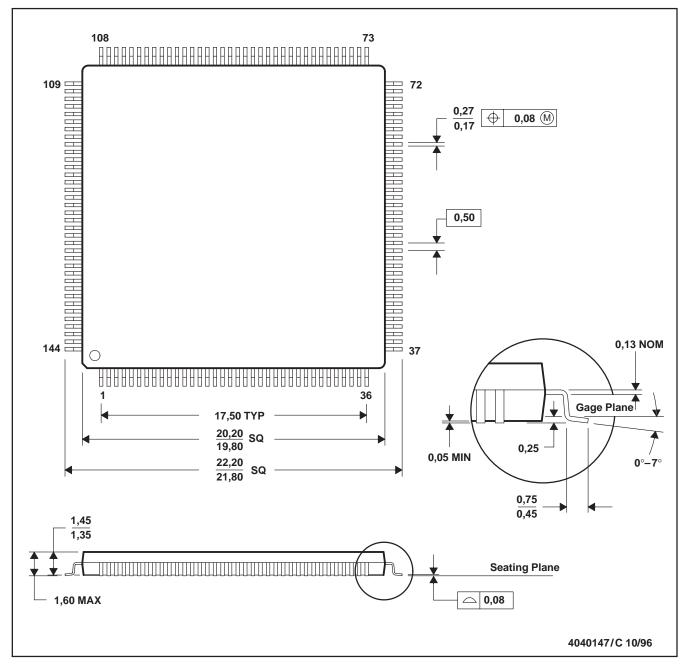

- Available in a 144-Pin Plastic Thin Quad Flatpack (TQFP) (PGE Suffix) and a 144-Pin Ball Grid Array (BGA) (GGU Suffix)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor's and disclaimers thereto appears at the end of this data sheet.

† IEEE Standard 1149.1-1990 Standard-Test-Access Port and Boundary Scan Architecture. All trademarks are the property of their respective owners.

| Table of Contents                            |                                                      |  |  |  |  |  |

|----------------------------------------------|------------------------------------------------------|--|--|--|--|--|

| Revision History                             | Multiply-By-N Clock Option                           |  |  |  |  |  |

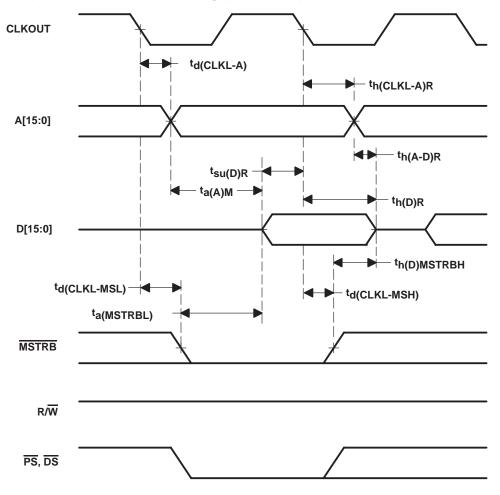

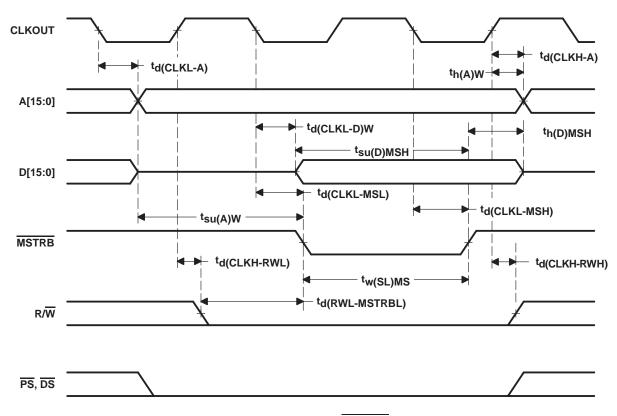

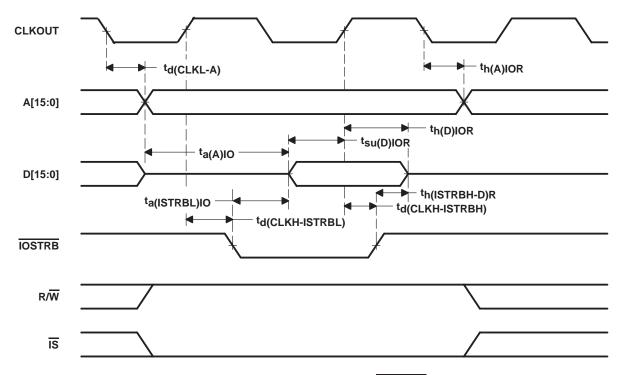

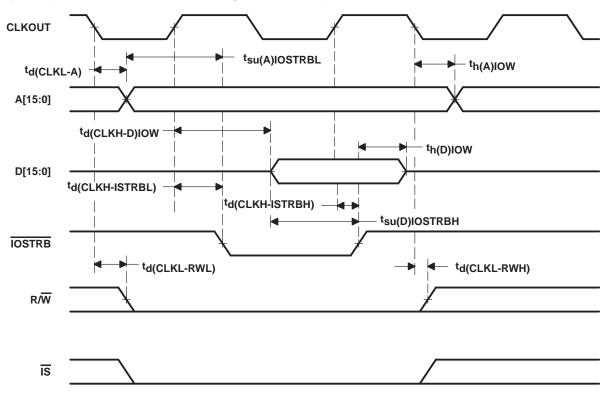

| Description 3                                | Memory and Parallel I/O Interface Timing 20          |  |  |  |  |  |

| Pin Assignments 6                            | SPICE Simulation Results                             |  |  |  |  |  |

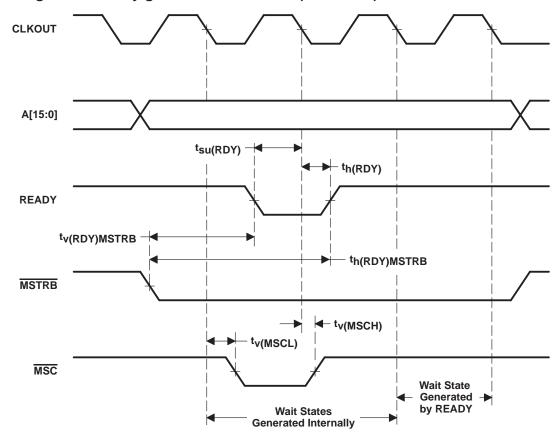

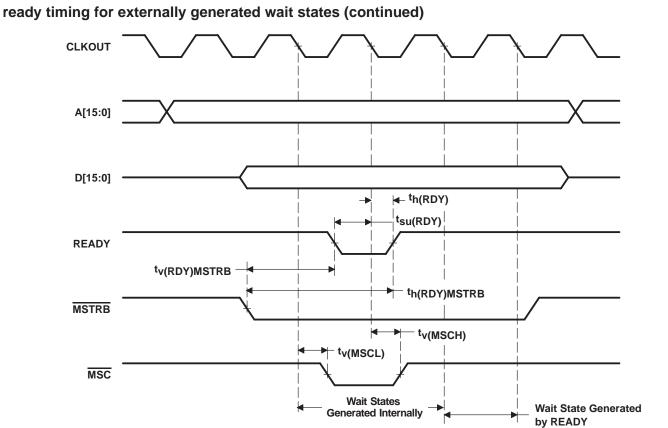

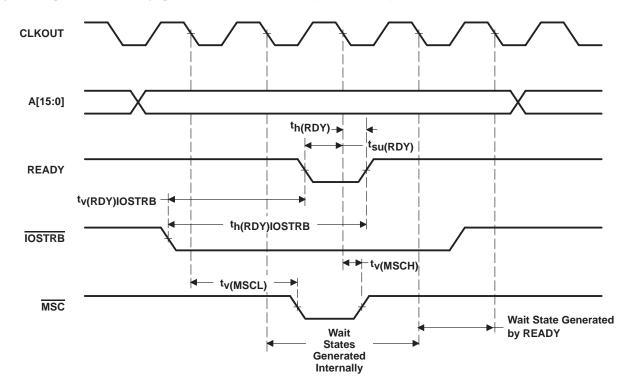

| Signal Descriptions                          | Ready Timing for Externally Generated Wait States 31 |  |  |  |  |  |

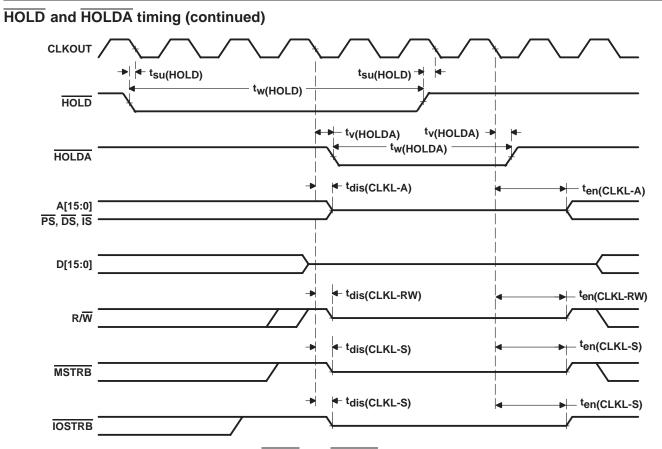

| Absolute Maximum Ratings                     | HOLD and HOLDA Timing                                |  |  |  |  |  |

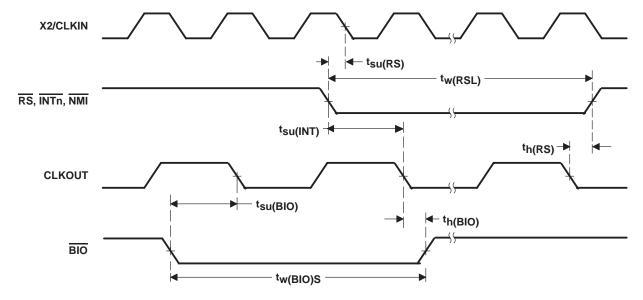

| Recommended Operating Conditions 12          | Reset, BIO, Interrupt, and MP/MC Timings 38          |  |  |  |  |  |

| Electrical Characteristics                   | Serial Port Receive Timing 42                        |  |  |  |  |  |

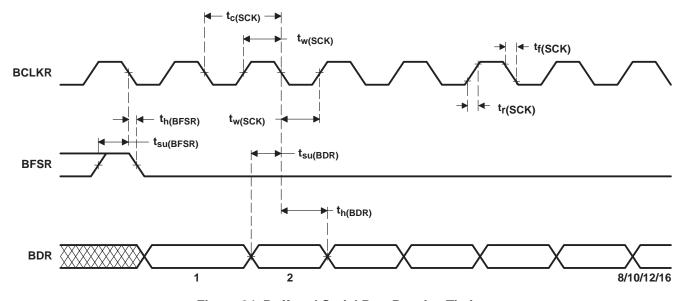

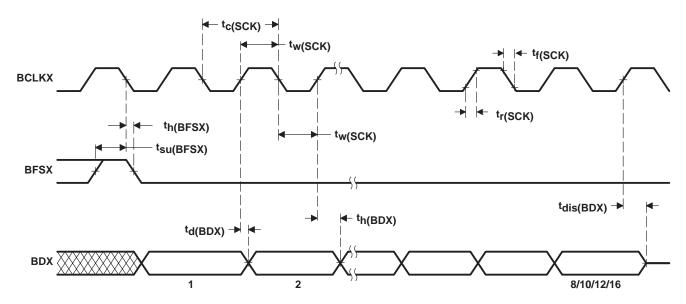

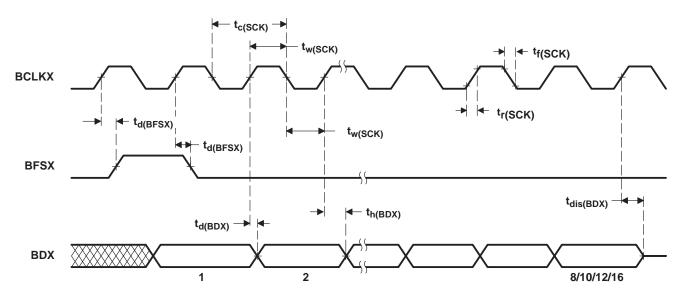

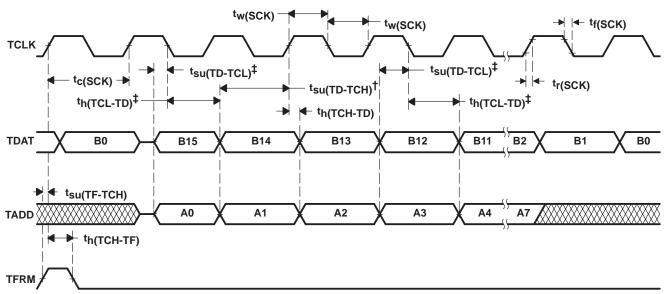

| Parameter Measurement Information            | Buffered Serial Port Receive Timing 45               |  |  |  |  |  |

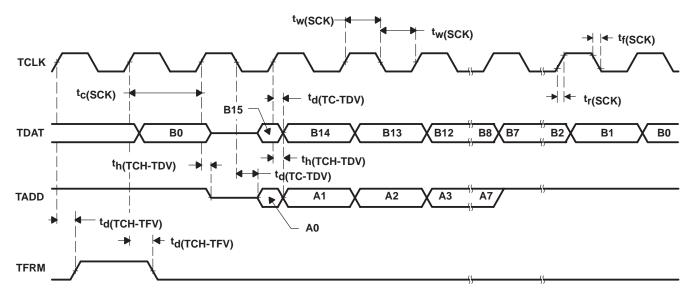

| Timing Parameter Symbology 14                | Serial-Port Receive Timing in TDM Mode 49            |  |  |  |  |  |

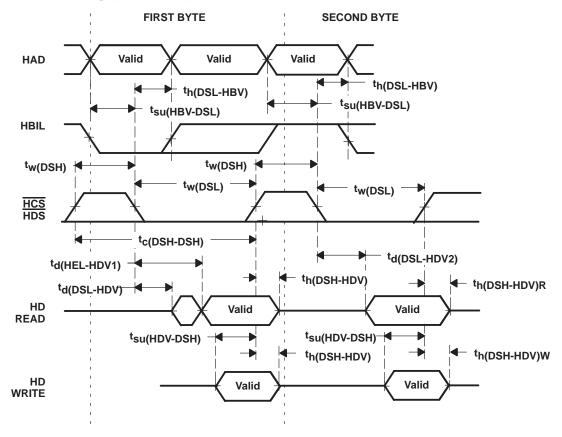

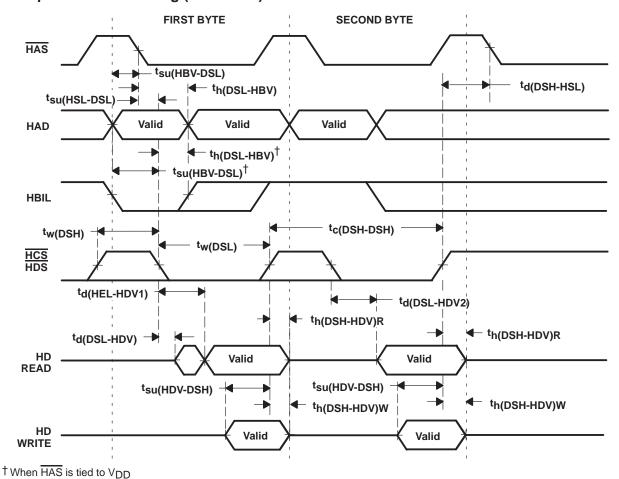

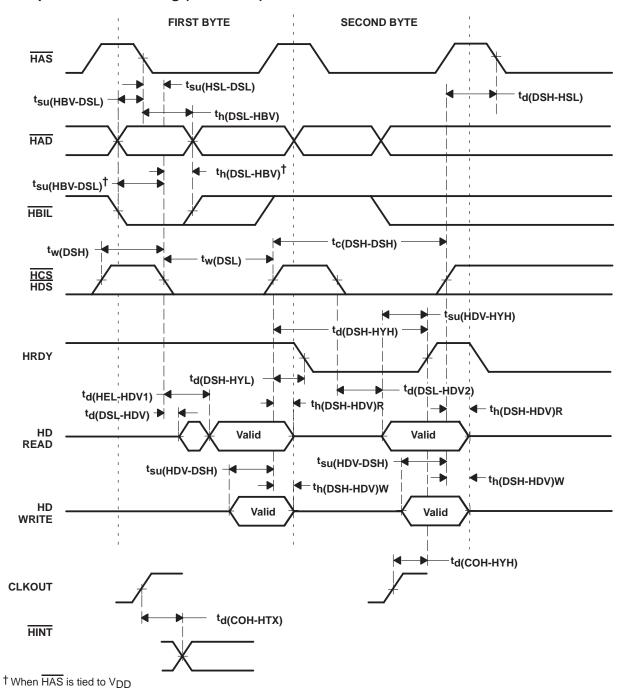

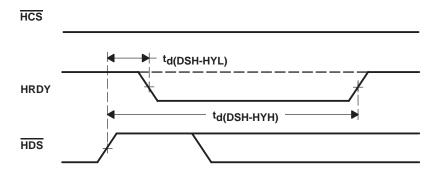

| Signal Transition Reference Points           | Host-Port Interface Timing 53                        |  |  |  |  |  |

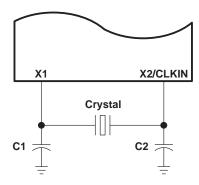

| Internal Oscillator With External Crystal 15 | Mechanical Data59                                    |  |  |  |  |  |

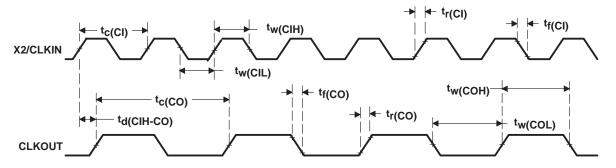

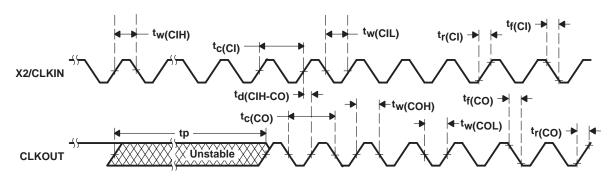

| Divide-By-Two/Divide-By-Four Clock Option 16 |                                                      |  |  |  |  |  |

#### **REVISION HISTORY**

This data sheet revision history highlights the technical changes made to the SPRS078F device-specific data sheet to make it an SPRS078G revision.

Scope: Applicable updates to the C5x device family, specifically relating to the C549 device, have been incorporated. Updated the device-specific information supporting the VC549, 8.3-ns, 120 MIPS device, which is now in the production data (PD) state of development.

| PAGE(S)<br>NO. | ADDITIONS/CHANGES/DELETIONS                                                                                                                                                                                                                                                                                                                                                      |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | Features: Deleted "(Product Preview Data)" from the "8.3-ns Single-Cycle Fixed-Point Instruction Execution Time (120 MIPS) for 3.3-V Power Supply (2.5-V Core)" feature Deleted NOTE about data for the 8.3-ns, 120 MIPS device being Product Preview data                                                                                                                       |

| 11             | $^{\circ}$ 549 Signal Descriptions table, IEEE1149.1 TEST PINS: Added "This pin should be pulled high with a separate 4.7-k $\Omega$ resistor" to the EMU0 pin DESCRIPTION Added "This pin should be pulled high with a separate 4.7-k $\Omega$ resistor" to the EMU1/OFF pin DESCRIPTION                                                                                        |

| 13             | Electrical Characteristics Over Recommended Operating Case Temperature Range table: I <sub>DD</sub> , Supply current, standby, IDLE3 (VC549-120 only): Deleted the <b>TYP</b> value of "170" μA Added the <b>TYP</b> value of "5" mA for "25°C" TEST CONDITIONS Added the <b>TYP</b> value of "50" mA for "100°C" TEST CONDITIONS                                                |

| 42             | Serial Port Receive Timing section: Timing Requirements Over Recommended Operating Conditions for Serial Port Receive table: Changed the <b>MIN</b> value of "th(FSR), Hold time, FSR after CLKR falling edge" <b>from</b> "4" <b>to</b> "6" ns Changed the <b>MIN</b> value of "t <sub>SU(DR)</sub> , Setup time, DR before CLKR falling edge" <b>from</b> "6" <b>to</b> "4" ns |

| 59             | Mechanical Data section:  Deleted the "PGE (S-PQFP-G144)" and GGU "(S-PBGA-N144)" mechanical data package diagrams; now an automated merge process  Added lead-in sentences for the thermal resistance characteristics table(s) and the "merged" mechanical data packages                                                                                                        |

#### TMS320VC549 FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS078G - SEPTEMBER 1998 - REVISED OCTOBER 2004

#### description

The TMS320VC549 fixed-point, digital signal processor (DSP) (hereafter referred to as the 549) is based on an advanced modified Harvard architecture that has one program memory bus and three data memory buses. The processor also provides an arithmetic logic unit (ALU) that has a high degree of parallelism, application-specific hardware logic, on-chip memory, and additional on-chip peripherals. The 549 also utilizes a highly specialized instruction set, which is the basis of its operational flexibility and speed.

Separate program and data spaces allow simultaneous access to program instructions and data, providing the high degree of parallelism. Two reads and one write operation can be performed in a single cycle. Instructions with parallel store and application-specific instructions can fully utilize this architecture. In addition, data can be transferred between data and program spaces. Such parallelism supports a powerful set of arithmetic, logic, and bit-manipulation operations that can all be performed in a single machine cycle. In addition, the 549 includes the control mechanisms to manage interrupts, repeated operations, and function calls.

This data sheet contains the pin layouts, signal descriptions, and electrical specifications for the TMS320VC549 DSP. For additional information, see the *TMS320C54x*, *TMS320LC54x*, *TMS320VC54x* Fixed-Point Digital Signal Processors data sheet (literature number SPRS039). The SPRS039 is considered a family functional overview and should be used in conjunction with this data sheet.

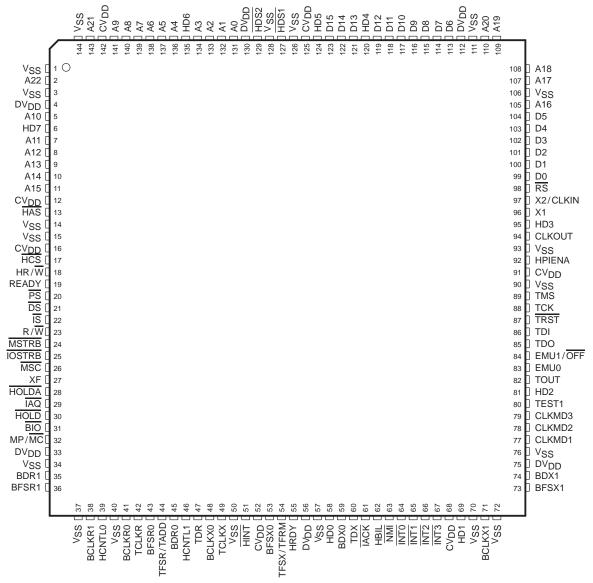

### PGE PACKAGE†‡ (TOP VIEW)

<sup>†</sup> NC = No connection

For the 144-pin TQFP, the letter B in front of CLKRn, FSRn, DRn, CLKXn, FSXn, and DXn pin names denotes buffered serial port (BSP), where n = 0 or 1 port. The letter T in front of CLKR, FSR, DR, CLKX, FSX, and DX pin names denotes time-division multiplexed (TDM) serial port.

<sup>&</sup>lt;sup>‡</sup> DV<sub>DD</sub> is the power supply for the I/O pins while CV<sub>DD</sub> is the power supply for the core CPU, and V<sub>SS</sub> is the ground for both the I/O pins and the core CPU.

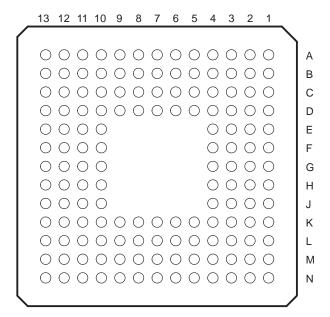

### GGU PACKAGE (BOTTOM VIEW)

The pin assignments table to follow lists each signal quadrant and BGA ball pin number for the 144-pin BGA package.

The Signal Descriptions table lists each terminal name, function, and operating mode(s).

#### Pin Assignments for the 144-Pin GGU Package<sup>†</sup>

| SIGNAL<br>QUADRANT 1 | BGA BALL# | SIGNAL<br>QUADRANT 2 | BGA BALL# | SIGNAL<br>QUADRANT 3 | BGA BALL# | SIGNAL<br>QUADRANT 4 | BGA BALL# |

|----------------------|-----------|----------------------|-----------|----------------------|-----------|----------------------|-----------|

| V <sub>SS</sub>      | A1        | BFSX1                | N13       | V <sub>SS</sub>      | N1        | A19                  | A13       |

| A22                  | B1        | BDX1                 | M13       | BCLKR1               | N2        | A20                  | A12       |

| VSS                  | C2        | DV <sub>DD</sub>     | L12       | HCNTL0               | M3        | V <sub>SS</sub>      | B11       |

| $DV_DD$              | C1        | Vss                  | L13       | Vss                  | N3        | $DV_DD$              | A11       |

| A10                  | D4        | CLKMD1               | K10       | BCLKR0               | K4        | D6                   | D10       |

| HD7                  | D3        | CLKMD2               | K11       | TCLKR                | L4        | D7                   | C10       |

| A11                  | D2        | CLKMD3               | K12       | BFSR0                | M4        | D8                   | B10       |

| A12                  | D1        | TEST1                | K13       | TFSR/TADD            | N4        | D9                   | A10       |

| A13                  | E4        | HD2                  | J10       | BDR0                 | K5        | D10                  | D9        |

| A14                  | E3        | TOUT                 | J11       | HCNTL1               | L5        | D11                  | C9        |

| A15                  | E2        | EMU0                 | J12       | TDR                  | M5        | D12                  | В9        |

| CV <sub>DD</sub>     | E1        | EMU1/OFF             | J13       | BCLKX0               | N5        | HD4                  | A9        |

| HAS                  | F4        | TDO                  | H10       | TCLKX                | K6        | D13                  | D8        |

| V <sub>SS</sub>      | F3        | TDI                  | H11       | V <sub>SS</sub>      | L6        | D14                  | C8        |

| Vss                  | F2        | TRST                 | H12       | HINT                 | M6        | D15                  | B8        |

| CV <sub>DD</sub>     | F1        | TCK                  | H13       | CVDD                 | N6        | HD5                  | A8        |

| HCS                  | G2        | TMS                  | G12       | BFSX0                | M7        | CV <sub>DD</sub>     | B7        |

| HR/W                 | G1        | Vss                  | G13       | TFSX/TFRM            | N7        | Vss                  | A7        |

| READY                | G3        | CV <sub>DD</sub>     | G11       | HRDY                 | L7        | HDS1                 | C7        |

| PS                   | G4        | HPIENA               | G10       | DV <sub>DD</sub>     | K7        | Vss                  | D7        |

| DS                   | H1        | V <sub>SS</sub>      | F13       | V <sub>SS</sub>      | N8        | HDS2                 | A6        |

| ĪS                   | H2        | CLKOUT               | F12       | HD0                  | M8        | $DV_DD$              | В6        |

| R/W                  | Н3        | HD3                  | F11       | BDX0                 | L8        | A0                   | C6        |

| MSTRB                | H4        | X1                   | F10       | TDX                  | K8        | A1                   | D6        |

| IOSTRB               | J1        | X2/CLKIN             | E13       | IACK                 | N9        | A2                   | A5        |

| MSC                  | J2        | RS                   | E12       | HBIL                 | M9        | А3                   | B5        |

| XF                   | J3        | D0                   | E11       | NMI                  | L9        | HD6                  | C5        |

| HOLDA                | J4        | D1                   | E10       | ĪNT0                 | K9        | A4                   | D5        |

| ĪAQ                  | K1        | D2                   | D13       | ĪNT1                 | N10       | A5                   | A4        |

| HOLD                 | K2        | D3                   | D12       | ĪNT2                 | M10       | A6                   | B4        |

| BIO                  | K3        | D4                   | D11       | ĪNT3                 | L10       | A7                   | C4        |

| MP/MC                | L1        | D5                   | C13       | CV <sub>DD</sub>     | N11       | A8                   | A3        |

| DV <sub>DD</sub>     | L2        | A16                  | C12       | HD1                  | M11       | A9                   | В3        |

| V <sub>SS</sub>      | L3        | V <sub>SS</sub>      | C11       | V <sub>SS</sub>      | L11       | CV <sub>DD</sub>     | C3        |

| BDR1                 | M1        | A17                  | B13       | BCLKX1               | N12       | A21                  | A2        |

| BFSR1                | M2        | A18                  | B12       | VSS                  | M12       | V <sub>SS</sub>      | B2        |

<sup>†</sup>DV<sub>DD</sub> is the power supply for the I/O pins while CV<sub>DD</sub> is the power supply for the core CPU, and V<sub>SS</sub> is the ground for both the I/O pins and the core CPU.

#### **Signal Descriptions**

| N                                                                                                                                                   | TERMIN.                                        | AL<br>TYPEŤ | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                                                                                                                                     | DATA SIGNALS                                   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| A22<br>A21<br>A20<br>A19<br>A18<br>A17<br>A16<br>A15<br>A14<br>A13<br>A12<br>A11<br>A10<br>A9<br>A8<br>A7<br>A6<br>A5<br>A4<br>A3<br>A2<br>A1<br>A0 | (MSB)                                          | O/Z         | Parallel port address bus A22 (MSB) through A0 (LSB). The sixteen LSBs (A15–A0) are multiplexed to address external data/program memory or I/O. A15–A0 are placed in the high-impedance state in the hold mode. A15–A0 also go into the high-impedance state when EMU1/OFF is low. The seven MSBs (A22 to A16) are used for extended program memory addressing.  The address bus have a feature called bus holder that eliminates passive components and the power dissipation associated with it. The bus holders keep the address bus at the previous logic level when the bus goes into a high-impedance state. The bus holders on the address bus are always enabled.            |  |  |  |  |

| D15<br>D14<br>D13<br>D12<br>D11<br>D10<br>D9<br>D8<br>D7<br>D6<br>D5<br>D4<br>D3<br>D2<br>D1<br>D0                                                  | (MSB)                                          | I/O/Z       | Parallel port data bus D15 (MSB) through D0 (LSB). D15–D0 are multiplexed to transfer data between the core CPU and external data/program memory or I/O devices. D15–D0 are placed in the high-impedance state when not output or when RS or HOLD is asserted. D15–D0 also go into the high-impedance state when EMU1/OFF is low.  The data bus has a feature called bus holder that eliminates passive components and the power dissipation associated with it. The bus holders keep the data bus at the previous logic level when the bus goes into a high-impedance state. These bus holders are enabled or disabled by the BH bit in the bank switching control register (BSCR). |  |  |  |  |

|                                                                                                                                                     | INITIALIZATION, INTERRUPT AND RESET OPERATIONS |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

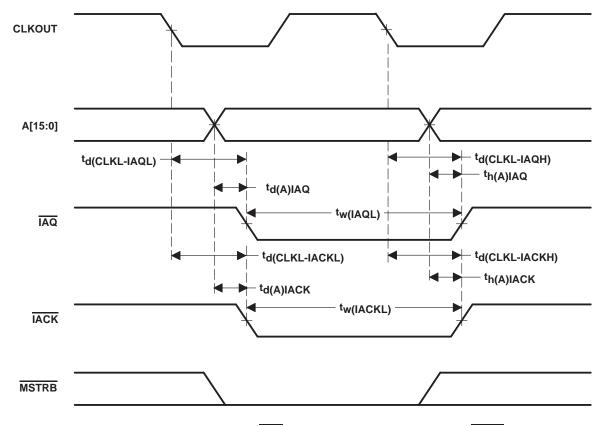

| IACK                                                                                                                                                |                                                | O/Z         | Interrupt acknowledge signal. IACK indicates the receipt of an interrupt and that the program counter is fetching the interrupt vector location designated by A15–0. IACK also goes into the high-impedance state when EMU1/OFF is low.                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

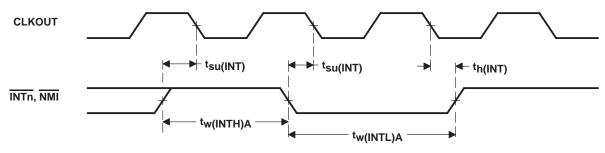

| INTO<br>INT1<br>INT2<br>INT3                                                                                                                        |                                                | I           | External user interrupt inputs. INT0-INT3 are prioritized and are maskable by the interrupt mask register and the interrupt mode bit. INT0 -INT3 can be polled and reset by the interrupt flag register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

<sup>†</sup> I = Input, O = Output, Z = High impedance

| TERMINAL .     |       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME           | TYPET | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                           |

|                |       | INITIALIZATION, INTERRUPT AND RESET OPERATIONS (CONTINUED)                                                                                                                                                                                                                                                                                                                                            |

| NMI            | I     | Nonmaskable interrupt. NMI is an external interrupt that cannot be masked by way of the INTM or the IMR. When NMI is activated, the processor traps to the appropriate vector location.                                                                                                                                                                                                               |

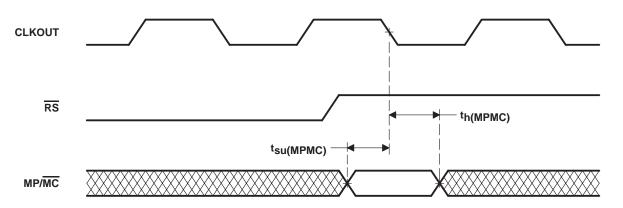

| RS             | I     | Reset input. $\overline{\text{RS}}$ causes the DSP to terminate execution and forces the program counter to $\overline{\text{OFF80h}}$ . When $\overline{\text{RS}}$ is brought to a high level, execution begins at location OFF80h of the program memory. $\overline{\text{RS}}$ affects various registers and status bits.                                                                         |

| MP/MC          | I     | Microprocessor/microcomputer mode-select pin. If active-low at reset (microcomputer mode), MP/MC causes the internal program ROM to be mapped into the upper program memory space. In the microprocessor mode, off-chip memory and its corresponding addresses (instead of internal program ROM) are accessed by the DSP.                                                                             |

| CNT            | I     | I/O level select. With CMOS-compatible I/O interface levels, CNT is pulled to a high level.                                                                                                                                                                                                                                                                                                           |

|                |       | MULTIPROCESSING SIGNALS                                                                                                                                                                                                                                                                                                                                                                               |

| BIO            | I     | Branch control input. A branch can be conditionally executed when $\overline{\text{BIO}}$ is active. If low, the processor executes the conditional instruction. The $\overline{\text{BIO}}$ condition is sampled during the decode phase of the pipeline for the XC instruction, and all other instructions sample $\overline{\text{BIO}}$ during the read phase of the pipeline.                    |

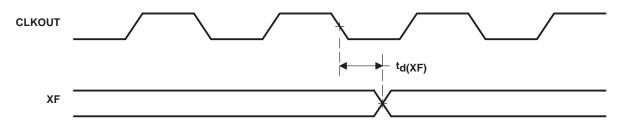

| XF             | O/Z   | External flag output (latched software-programmable signal). XF is set high by the SSBX XF instruction, set low by RSBX XF instruction or by loading the ST1 status register. XF is used for signaling other processors in multiprocessor configurations or as a general-purpose output pin. XF goes into the high-impedance state when OFF is low, and is set high at reset.                         |

|                |       | MEMORY CONTROL SIGNALS                                                                                                                                                                                                                                                                                                                                                                                |

| DS<br>PS<br>IS | O/Z   | Data, program, and I/O space select signals. DS, PS, and IS are always high unless driven low for communicating to a particular external space. Active period corresponds to valid address information. Placed into a high-impedance state in hold mode. DS, PS, and IS also go into the high-impedance state when EMU1/OFF is low.                                                                   |

| MSTRB          | O/Z   | Memory strobe signal. MSTRB is always high unless low-level asserted to indicate an external bus access to data or program memory. Placed in high-impedance state in hold mode. MSTRB also goes into the high-impedance state when OFF is low.                                                                                                                                                        |

| READY          | I     | Data-ready input. READY indicates that an external device is prepared for a bus transaction to be completed. If the device is not ready (READY is low), the processor waits one cycle and checks READY again. Note that the processor performs ready-detection if at least two software wait states are programmed. The READY signal is not sampled until the completion of the software wait states. |

| R/W            | O/Z   | Read/write signal. $R\overline{W}$ indicates transfer direction during communication to an external device and is normally high (in read mode), unless asserted low when the DSP performs a write operation. Placed in the high-impedance state in hold mode, $R\overline{W}$ also goes into the high-impedance state when EMU1/ $\overline{OFF}$ is low.                                             |

| IOSTRB         | O/Z   | I/O strobe signal. IOSTRB is always high unless low level asserted to indicate an external bus access to an I/O device. Placed in high-impedance state in hold mode. IOSTRB also goes into the high-impedance state when EMU1/OFF is low.                                                                                                                                                             |

| HOLD           | I     | Hold input. HOLD is asserted to request control of the address, data, and control lines. When acknowledged, these lines go into high-impedance state.                                                                                                                                                                                                                                                 |

| HOLDA          | O/Z   | Hold acknowledge signal. HOLDA indicates to the external circuitry that the processor is in a hold state and that the address, data, and control lines are in a high-impedance state, allowing them to be available to the external circuitry. HOLDA also goes into the high-impedance state when EMU1/OFF is low.                                                                                    |

| MSC            | O/Z   | Microstate complete signal. Goes low on CLKOUT falling at the start of the first software wait state. Remains low until one CLKOUT cycle before the last programmed software wait state. If connected to the READY line, MSC forces one external wait state after the last internal wait state has been completed. MSC also goes into the high-impedance state when EM1/OFF is low.                   |

<sup>†</sup> I = Input, O = Output, Z = High impedance

| TERMINAL                   |       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                       | TYPET | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                            |       | MEMORY CONTROL SIGNALS (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ĪĀQ                        | O/Z   | Instruction acquisition signal. $\overline{IAQ}$ is asserted (active low) when there is an instruction address on the address bus and goes into the high-impedance state when EMU1/ $\overline{OFF}$ is low.                                                                                                                                                                                                                                                                                                              |

|                            |       | OSCILLATOR/TIMER SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CLKOUT                     | O/Z   | Master clock output signal. CLKOUT cycles at the machine-cycle rate of the CPU. The internal machine cycle is bounded by the falling edges of this signal. CLKOUT also goes into the high-impedance state when EMU1/OFF is low.                                                                                                                                                                                                                                                                                           |

| CLKMD1<br>CLKMD2<br>CLKMD3 | I     | Clock mode external/internal input signals. CLKMD1, CLKMD2, and CLKMD3 allow you to select and configure different clock modes, such as crystal, external clock, and various PLL factors. Refer to PLL section for a detailed functional description of these pins.                                                                                                                                                                                                                                                       |

| X2/CLKIN                   | I     | Input pin to internal oscillator from the crystal. If the internal (crystal) oscillator is not being used, a clock can become input to the device using this pin. The internal machine cycle time is determined by the clock operating-mode pins (CLKMD1, CLKMD2 and CLKMD3).                                                                                                                                                                                                                                             |

| X1                         | 0     | Output pin from the internal oscillator for the crystal. If the internal oscillator is not used, X1 should be left unconnected. X1 does not go into the high-impedance state when EMU1/OFF is low.                                                                                                                                                                                                                                                                                                                        |

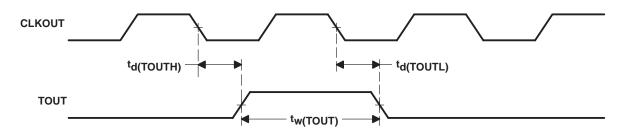

| TOUT                       | O/Z   | Timer output. TOUT signals a pulse when the on-chip timer counts down past zero. The pulse is a CLKOUT-cycle wide. TOUT also goes into the high-impedance state when EMU1/OFF is low.                                                                                                                                                                                                                                                                                                                                     |

|                            |       | BUFFERED SERIAL PORT 0 AND BUFFERED SERIAL PORT 1 SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| BCLKR0<br>BCLKR1           | 1     | Receive clocks. External clock signal for clocking data from the data-receive (DR) pin into the buffered serial port receive shift registers (RSRs). Must be present during buffered serial port transfers. If the buffered serial port is not being used, BCLKR0 and BCLKR1 can be sampled as an input by way of IN0 bit of the SPC register.                                                                                                                                                                            |

| BCLKX0<br>BCLKX1           | I/O/Z | Transmit clock. Clock signal for clocking data from the serial port transmit shift register (XSR) to the data transmit (DX) pin. BCLKX can be an input if MCM in the serial port control register is cleared to 0. It also can be driven by the device at 1/(CLKDV + 1) where CLKDV range is 0–31 CLKOUT frequency when MCM is set to 1. If the buffered serial port is not used, BCLKX can be sampled as an input by way of IN1 of the SPC register. BCLKX0 and BCLKX1 go into the high-impedance state when OFF is low. |

| BDR0<br>BDR1               | I     | Buffered serial-data-receive input. Serial data is received in the RSR by BDR0/BDR1.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BDX0<br>BDX1               | O/Z   | Buffered serial-port-transmit output. Serial data is transmitted from the XSR by way of BDX. BDX0 and BDX1 are placed in the high-impedance state when not transmitting and when EMU1/OFF is low.                                                                                                                                                                                                                                                                                                                         |

| BFSR0<br>BFSR1             | I     | Frame synchronization pulse for receive input. The falling edge of the BFSR pulse initiates the data-receive process, beginning the clocking of the RSR.                                                                                                                                                                                                                                                                                                                                                                  |

| BFSX0<br>BFSX1             | I/O/Z | Frame synchronization pulse for transmit input/output. The falling edge of the BFSX pulse initiates the data-transmit process, beginning the clocking of the XSR. Following reset, the default operating condition of BFSX is an input. BFSX0 and BFSX1 can be selected by software to be an output when TXM in the serial control register is set to 1. This pin goes into the high-impedance state when EMU1/OFF is low.                                                                                                |

|                            |       | SERIAL PORT 0 AND SERIAL PORT 1 SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

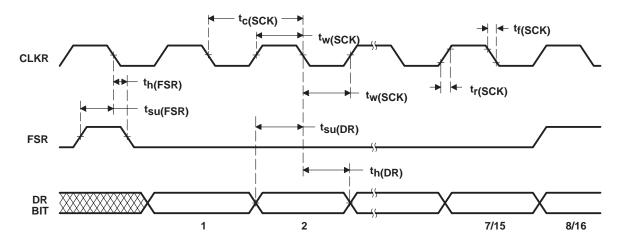

| CLKR0<br>CLKR1             | I     | Receive clocks. External clock signal for clocking data from the data receive (DR) pin into the serial port receive shift register (RSR). Must be present during serial port transfers. If the serial port is not being used, CLKR0 and CLKR1 can be sampled as an input via IN0 bit of the SPC register.                                                                                                                                                                                                                 |

| CLKX0<br>CLKX1             | I/O/Z | Transmit clock. Clock signal for clocking data from the serial port transmit shift register (XSR) to the data transmit (DX) pin. CLKX can be an input if MCM in the serial port control register is cleared to 0. It also can be driven by the device at 1/4 CLKOUT frequency when MCM is set to 1. If the serial port is not used, CLKX can be sampled as an input via IN1 of the SPC register. CLKX0 and CLKX1 go into the high-impedance state when EMU1/OFF is low.                                                   |

| DR0<br>DR1                 | I     | Serial-data-receive input. Serial data is received in the RSR by DR.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

$<sup>\</sup>dagger$  I = Input, O = Output, Z = High impedance

| TERMINAL<br>NAME TYPET |                                                     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                        | SERIAL PORT 0 AND SERIAL PORT 1 SIGNALS (CONTINUED) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

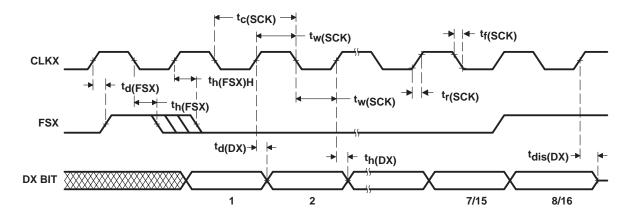

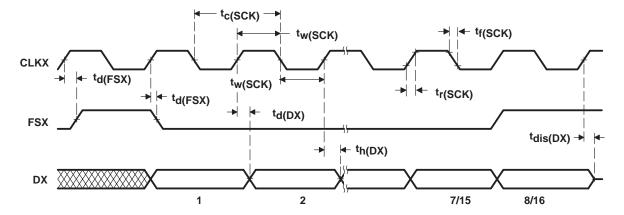

| DX0<br>DX1             | O/Z                                                 | Serial port transmit output. Serial data is transmitted from the XSR via DX. DX0 and DX1 are placed in the high-impedance state when not transmitting and when EMU1/OFF is low.                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| FSR0<br>FSR1           | I                                                   | Frame synchronization pulse for receive input. The falling edge of the FSR pulse initiates the data-receive process, beginning the clocking of the RSR.                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| FSX0<br>FSX1           | I/O/Z                                               | Frame synchronization pulse for transmit input/output. The falling edge of the FSX pulse initiates the data transmit process, beginning the clocking of the XSR. Following reset, the default operating condition of FSX is an input. FSX0 and FSX1 can be selected by software to be an output when TXM in the serial control register is set to 1. This pin goes into the high-impedance state when EMU1/OFF is low.                                                                                                                                 |  |  |  |  |

|                        |                                                     | TDM SERIAL PORT SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| TCLKR                  | 1                                                   | TDM receive clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| TDR                    | I                                                   | TDM serial data-receive input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| TFSR/TADD              | I/O                                                 | TDM receive frame synchronization or TDM address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| TCLKX                  | I/O/Z                                               | TDM transmit clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| TDX                    | O/Z                                                 | TDM serial data-transmit output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| TFSX/TFRM              | I/O/Z                                               | TDM transmit frame synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                        |                                                     | HOST PORT INTERFACE SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| HD0-HD7                | I/O/Z                                               | Parallel bidirectional data bus. HD0–HD7 are placed in the high-impedance state when not outputting data. The signals go into the high-impedance state when EMU1/OFF is low. These pins each have bus holders similar to those on the address/data bus, but which are always enabled.                                                                                                                                                                                                                                                                  |  |  |  |  |

| HCNTL0<br>HCNTL1       | I                                                   | Control inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| HBIL                   | 1                                                   | Byte-identification input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| HCS                    | I                                                   | Chip-select input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| HDS1<br>HDS2           | I                                                   | Data strobe inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| HAS                    | 1                                                   | Address strobe input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| HR/W                   | I                                                   | Read/write input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| HRDY                   | O/Z                                                 | Ready output. This signal goes into the high-impedance state when EMU1/OFF is low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| HINT                   | O/Z                                                 | Interrupt output. When the DSP is in reset, this signal is driven high. The signal goes into the high-impedance state when EMU1/OFF is low.                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| HPIENA                 | I                                                   | HPI module select input. This signal must be tied to a logic 1 state to have HPI selected. If this input is left open or connected to ground, the HPI module will not be selected, internal pullup for the HPI input pins are enabled, and the HPI data bus has keepers set. This input is provided with an internal pull-down resistor which is active only when RS is low. HPIENA is sampled when RS goes high and ignored until RS goes low again. Refer to the Electrical Characteristics section for the input current requirements for this pin. |  |  |  |  |

|                        | SUPPLY PINS                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| CV <sub>DD</sub>       | Supply                                              | +V <sub>DD</sub> . CV <sub>DD</sub> is the dedicated power supply for the core CPU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| $DV_DD$                | Supply                                              | +V <sub>DD</sub> . DV <sub>DD</sub> is the dedicated power supply for I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| VSS                    | Supply                                              | Ground. VSS is the dedicated power ground for the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

<sup>†</sup> I = Input, O = Output, Z = High impedance

| TERN<br>NAME | IINAL<br>TYPE <sup>†</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |                            | IEEE1149.1 TEST PINS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TCK          | I                          | IEEE standard 1149.1 test clock. Pin with internal pullup device. This is normally a free-running clock signal with a 50% duty cycle. The changes on the test-access port (TAP) of input signals TMS and TDI are clocked into the TAP controller, instruction register, or selected test data register on the rising edge of TCK. Changes at the TAP output signal (TDO) occur on the falling edge of TCK.                                                                                                                                                                                                                                                     |

| TDI          | I                          | IEEE standard 1149.1 test data input. Pin with internal pullup device. TDI is clocked into the selected register (instruction or data) on a rising edge of TCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TDO          | O/Z                        | IEEE standard 1149.1 test data output. The contents of the selected register (instruction or data) is shifted out of TDO on the falling edge of TCK. TDO is in the high-impedance state except when the scanning of data is in progress. TDO also goes into the high-impedance state when EMU1/OFF is low.                                                                                                                                                                                                                                                                                                                                                     |

| TMS          | 1                          | IEEE standard 1149.1 test mode select. Pin with internal pullup device. This serial control input is clocked into the TAP controller on the rising edge of TCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TRST         | 1                          | IEEE standard 1149.1 test reset. TRST, when high, gives the IEEE standard 1149.1 scan system control of the operations of the device. If TRST is not connected or driven low, the device operates in its functional mode, and the IEEE standard 1149.1 signals are ignored. Pin with internal pulldown device.                                                                                                                                                                                                                                                                                                                                                 |

| EMU0         | I/O/Z                      | Emulator interrupt 0 pin. When $\overline{\text{TRST}}$ is driven low, EMU0 must be high for the activation of the EMU1/ $\overline{\text{OFF}}$ condition. When $\overline{\text{TRST}}$ is driven high, EMU0 is used as an interrupt to or from the emulator system and is defined as input/output by way of IEEE standard 1149.1 scan system. This pin should be pulled high with a separate 4.7-k $\Omega$ resistor.                                                                                                                                                                                                                                       |

| EMU1/OFF     | I/O/Z                      | Emulator interrupt 1 pin/disable all outputs. When TRST is driven high, EMU1/OFF is used as an interrupt to or from the emulator system and is defined as input/output by way of IEEE standard 1149.1 scan system. When TRST is driven low, EMU1/OFF is configured as OFF. The EMU1/OFF signal, when active low, puts all output drivers into the high-impedance state. This pin should be pulled high with a separate 4.7-kΩ resistor. Note that OFF is used exclusively for testing and emulation purposes (not for multiprocessing applications). Therefore, for the OFF condition, the following conditions apply:  TRST = low, EMU0 = high EMU1/OFF = low |

|              |                            | DEVICE TEST PIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TEST1        | I                          | Test1 – Reserved for internal use only. This pin must not be connected (NC).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

$<sup>\</sup>dagger$  I = Input, O = Output, Z = High impedance

### TMS320VC549 FIXED-POINT DIGITAL SIGNAL PROCESSOR

SPRS078G - SEPTEMBER 1998 - REVISED OCTOBER 2004

#### absolute maximum ratings over specified temperature range (unless otherwise noted)†

| Supply voltage I/O range, DV <sub>DD</sub> ‡             | 0.3 V to 4.6 V                       |

|----------------------------------------------------------|--------------------------------------|

| Supply voltage core range, CV <sub>DD</sub> <sup>‡</sup> | . $-0.3$ V to 3.75 V                 |

| Input voltage range                                      |                                      |

| Output voltage range                                     | $\dots$ -0.3 V to 4.6 V              |

| Operating case temperature range, T <sub>C</sub>         | . $-40^{\circ}$ C to $100^{\circ}$ C |

| Storage temperature range, T <sub>stg</sub>              | 55°C to 150°C                        |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### recommended operating conditions

|                  |                                         |                                                                      | MIN  | NOM | MAX                    | UNIT |

|------------------|-----------------------------------------|----------------------------------------------------------------------|------|-----|------------------------|------|

| $DV_{DD}$        | Device supply voltage, I/O <sup>†</sup> |                                                                      | 3    | 3.3 | 3.6                    | V    |

| CV <sub>DD</sub> | Device supply voltage, core†            |                                                                      | 2.4  | 2.5 | 2.75                   | V    |

| VSS              | Supply voltage, GND                     |                                                                      |      | 0   |                        | V    |

| VIH              | High-level input voltage, I/O           | Schmitt trigger inputs, $DV_{DD} = 3.3 \pm 0.3 \text{ V}^{\ddagger}$ | 2.5  |     | DV <sub>DD</sub> + 0.3 | V    |

|                  |                                         | All other inputs                                                     | 2    |     | DV <sub>DD</sub> + 0.3 |      |

| VIL              | Low-level input voltage                 |                                                                      | -0.3 |     | 0.8                    | V    |

| ІОН              | High-level output current               |                                                                      |      |     | -300                   | μΑ   |

| l <sub>OL</sub>  | Low-level output current                |                                                                      |      |     | 1.5                    | mA   |

| TC               | Operating case temperature              |                                                                      | -40  |     | 100                    | °C   |

Texas Instrument DSPs do not require specific power sequencing between the core supply and the I/O supply. However, systems should be designed to ensure that neither supply is powered up for extended periods of time if the other supply is below the proper operating voltage. Excessive exposure to these conditions can adversely affect the long term reliability of the devices. System-level concerns such as bus contention may require supply sequencing to be implemented. In this case, the core supply should be powered up at the same time as, or prior to (and powered down after), the I/O buffers. For additional power sequencing information, see the *Power Supply Sequencing Solutions for Dual Supply Voltage DSPs* application report (literature number SLVA073).

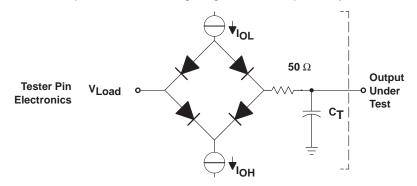

See Figure 1 for 3.3-V device test load circuit values.

<sup>‡</sup> All voltage values are with respect to VSS.

<sup>‡</sup> On the VC549 devices, the following pins have schmitt trigger inputs: RS, INTn, NMI, X2/CLKIN, CLKMDn, TCK, HAS, HCS, HDSn, BCLKRn, TCLKR, BCLKXn, and TCLKX

### electrical characteristics over recommended operating case temperature range (unless otherwise noted)

|                  | PARAMETER                                   |                                                                                 | TEST CONDITIONS                                                             |                                          | MIN  | TYP† | MAX  | UNIT |  |

|------------------|---------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------|------|------|------|------|--|

| Vон              | High-level                                  | high-level output voltage‡ V <sub>DD</sub> = 3.3 ± 0.3 V, I <sub>OH</sub> = MAX |                                                                             | 2.4                                      |      |      | V    |      |  |

| VOL              | Low-level                                   | output voltage <sup>‡</sup>                                                     | I <sub>OL</sub> = MAX                                                       |                                          |      |      | 0.4  | V    |  |

|                  | Input<br>current in                         | A[22:0]                                                                         | V <sub>DD</sub> = MAX☆                                                      |                                          | -150 |      | 250  | 4    |  |

| l IZ             | high<br>impedan<br>ce                       | All other pins                                                                  | $V_{DD} = MAX$ , $V_{I} = V_{SS}$ to $V_{DD}$                               | $V_{DD} = MAX, V_I = V_{SS}$ to $V_{DD}$ |      |      | 10   | μΑ   |  |

|                  |                                             | TRST                                                                            | With internal pulldown                                                      |                                          | -10  |      | 800  |      |  |

|                  | Input                                       | HPIENA                                                                          | With internal pulldown, $\overline{RS} = 0$                                 |                                          | -10  |      | 400  | μΑ   |  |

| ١.               | current                                     | TMS, TCK, TDI, HPI                                                              | With internal pullups                                                       |                                          | -400 |      | 10   |      |  |

| li l             | $(V_I = V_{SS})$                            | D[15:0], HD[7:0]                                                                | Bus holders enabled, V <sub>DD</sub> = MAX☆                                 |                                          | -150 |      | 250  |      |  |

|                  | to V <sub>DD</sub> )                        | X2/CLKIN                                                                        | Oscillator enabled                                                          |                                          | -40  |      | 40   |      |  |

|                  |                                             | All other input-only pins                                                       |                                                                             |                                          | -10  |      | 10   |      |  |

| IDDC             | Supply cur                                  | rent, core CPU                                                                  | $CV_{DD} = 2.5 \text{ V}, f_X = 40 \text{ MHz}, \ T_C = 25^{\circ}\text{C}$ |                                          |      | 20¶  |      | mA   |  |

| I <sub>DDP</sub> | Supply cui                                  | rent, pins                                                                      | $DV_{DD} = 3.3 \text{ V}, f_X = 40 \text{ MHz}, \ T_C = 25^{\circ}\text{C}$ |                                          |      | 12#  |      | mA   |  |

|                  |                                             | IDLE2                                                                           | PLL × 1 mode, 40 MHz input                                                  |                                          |      | 2    |      | mA   |  |