EVALUATION KIT AVAILABLE

# **Quad Serial UART with 128-Word FIFOs**

# **General Description**

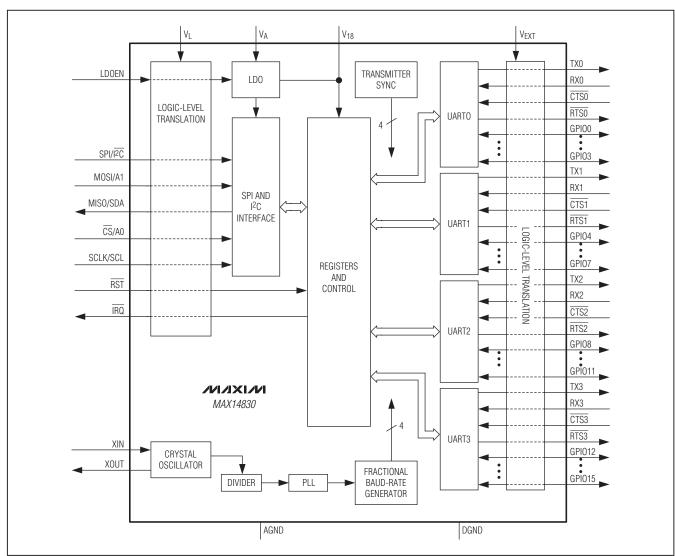

The MAX14830 is an advanced quad universal asynchronous receiver-transmitter (UART), each UART having 128 words of receive and transmit first-in/first-out (FIFO) and a high-speed serial peripheral interface (SPI<sup>™</sup>) or I<sup>2</sup>C controller interface. A PLL and fractional baud-rate generators allow a high degree of flexibility in baud-rate programming and reference clock selection.

Each of the four UARTs is selected by in-band SPI/I<sup>2</sup>C addressing. Logic-level translation on the transceiver and controller interfaces allows ease of interfacing to microcontrollers, FPGAs, and transceivers that are powered by differing supply voltages.

Extensive features simplify transceiver control in halfduplex communication applications. The MAX14830 features the ability to synchronize the start of individual UART's transmission by SPI-based triggering. On-board timers allow programming of delays between transmitters as well as clock generation on GPIOs.

The 128-word FIFOs have advanced FIFO control reducing host processor data flow management.

The MAX14830 is available in a 48-pin TQFN (7mm x 7mm) package and is specified to operate over the extended -40°C to +85°C temperature range.

# **Applications**

Industrial Control Systems

Programmable Logic Controllers (PLC)

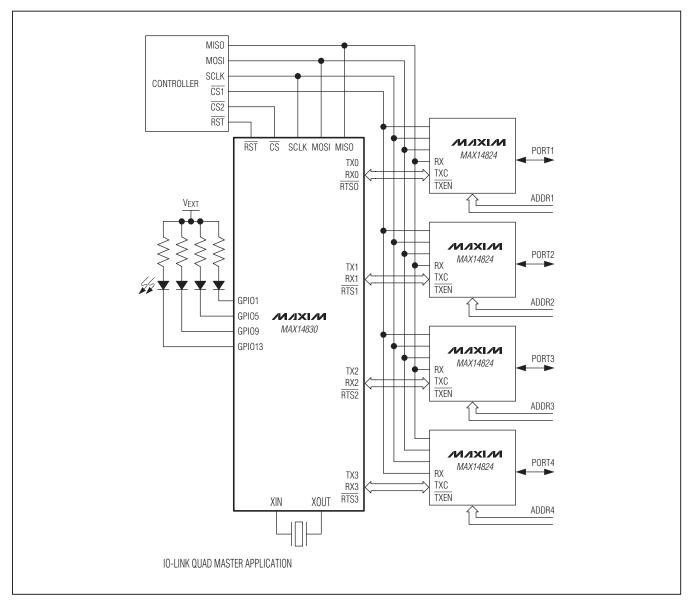

**IO-Link Master Controllers**

Automotive Infotainment Systems

- Medical Systems

- Point-of-Sales Systems

- Airplane Communication Buses

# \_Features

- ◆ SPI Up to 26MHz Clock Rate

- Fast-Mode Plus (Fm+) I<sup>2</sup>C Interface Up to 1MHz

- 128-Word Transmit and Receive FIFOs Per UART

- 6Mbaud (max) Data Rate in 16x Sampling Mode

- ◆ 12/24Mbaud (max) Data Rate in 2x/4x Rate Modes

- Fractional Baud-Rate Generators, Predivider, and Phase-Locked Loop (PLL)

- Transmitter Synchronization Through SPI Commands

- Four Timers Routed to GPIOs

- Automatic Hardware Flow Control Using <u>RTS</u> and <u>CTS</u> Outputs and Inputs

- Automatic Software Flow Control (XON/XOFF)

- Auto Transceiver Direction Control

- Programmable Setup and Hold Times for Transceiver Control

- Auto Transmitter Disable

- Half-Duplex Echo Suppression

- Special Character Detection

- 9-Bit Multidrop Mode Address Detection and Filtering

- ♦ SIR- and MIR-Compliant IrDA<sup>®</sup> Encoder/Decoders

- 16 Flexible GPIOs with 20mA Drive Capability

- + +2.35V to +3.6V Supply Range

- Logic-Level Translation Down to 1.61V on Controller and Transceiver Interfaces

- Small TQFN (7mm x 7mm) Package

# **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE |

|--------------|----------------|-------------|

| MAX14830ETM+ | -40°C to +85°C | 48 TQFN-EP* |

Typical Operating Circuits appear at end of data sheet.

+Denotes a lead(Pb)-free/RoHS-compliant package. \*EP = Exposed pad.

SPI is a trademark of Motorola, Inc.

IrDA is a registered service mark of Infrared Data Association Corporation.

# M/X/W

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

# **TABLE OF CONTENTS**

| General Description                        |    |

|--------------------------------------------|----|

| Applications                               |    |

| Features                                   |    |

| Ordering Information                       |    |

| Functional Diagram                         |    |

| Absolute Maximum Ratings                   |    |

| Package Thermal Characteristics            |    |

| DC Electrical Characteristics              |    |

| AC Electrical Characteristics              |    |

| Test Circuits/Timing Diagrams              |    |

| Typical Operating Characteristics          |    |

| Pin Configuration                          |    |

| Pin Description                            |    |

| Detailed Description                       |    |

| Receive and Transmit FIFOs                 |    |

| Transmitter Operation                      |    |

| Receiver Operation                         |    |

| Line Noise Indication.                     |    |

| Clocking and Baud-Rate Generation          |    |

| Crystal Oscillator                         |    |

| External Clock Source                      |    |

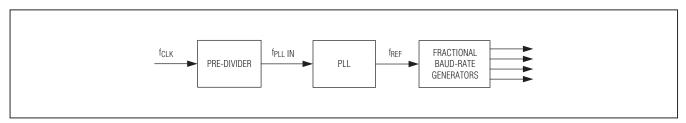

| PLL and Predivider                         |    |

| Fractional Baud-Rate Generators            | 21 |

| 2x and 4x Rate Modes                       |    |

| Low-Frequency Timer                        | 22 |

| UART Clock to GPIO.                        |    |

| Multidrop Mode                             | 22 |

| Auto Data Filtering in Multidrop Mode      | 22 |

| Auto Transceiver Direction Control         | 22 |

| Transmitter Triggering and Synchronization | 23 |

| Transmitter Synchronization                | 23 |

| Intrachip and Interchip Synchronization.   | 23 |

| Delayed Triggering                         | 23 |

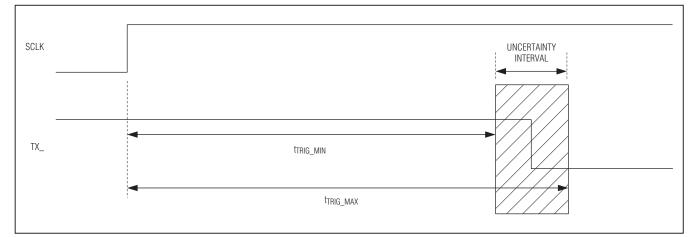

| Trigger Accuracy                           | 24 |

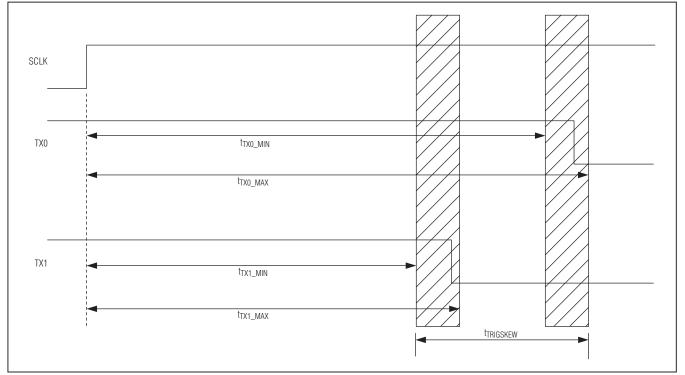

| Synchronization Accuracy                   | 24 |

| Auto Transmitter Disable                   | 24 |

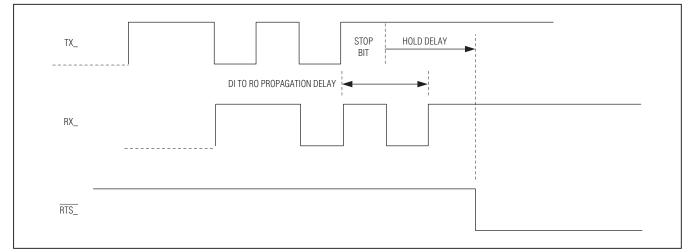

| Echo Suppression                           | 24 |

| Auto Hardware Flow Control                 | 26 |

| TABLE OF CONTENTS (continued)              |

|--------------------------------------------|

| AutoRTS Control                            |

| AutoCTS Control                            |

| FIFO Interrupt Triggering                  |

| Auto Software (XON/XOFF) Flow Control      |

| Transmitter Flow Control                   |

| Receiver Overflow Control                  |

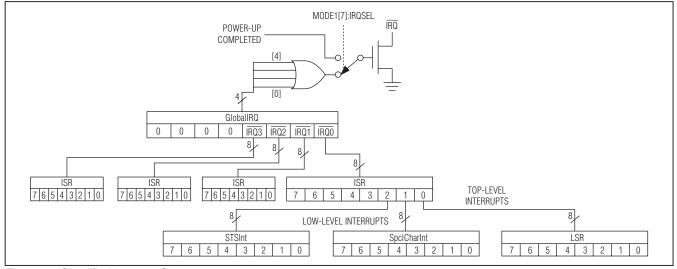

| Power-Up and IRQ                           |

| Shutdown Mode                              |

| Interrupt Structure                        |

| Interrupt Enabling                         |

| Interrupt Clearing                         |

| Register Map                               |

| Detailed Register Description              |

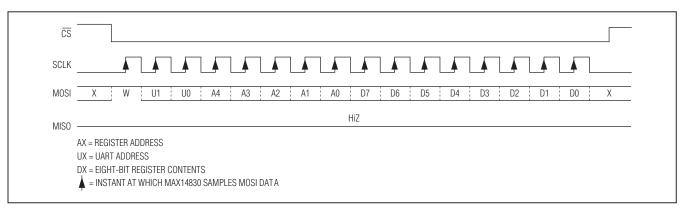

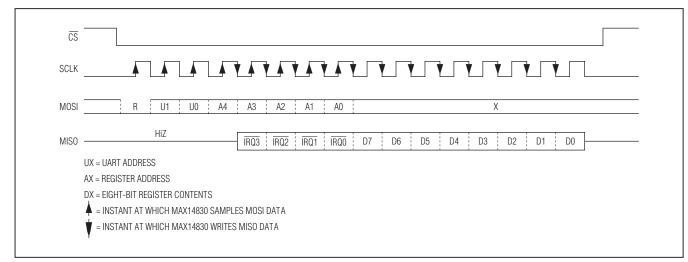

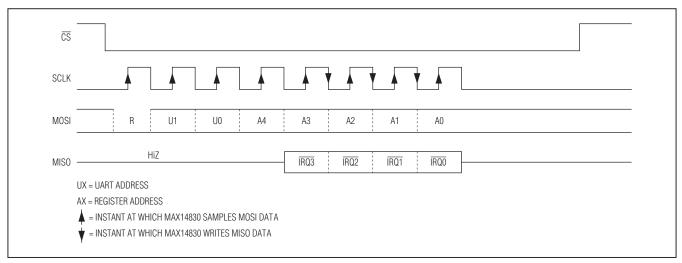

| Serial Controller Interface                |

| SPI Interface                              |

| MISO Operation                             |

| SPI Burst Access                           |

| Fast Read Cycle                            |

| I <sup>2</sup> C Interface                 |

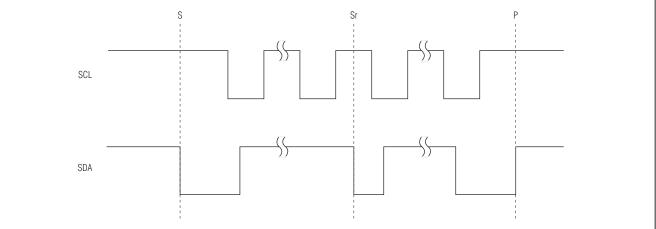

| START, STOP, and Repeated START Conditions |

| Slave Address                              |

| Bit Transfer                               |

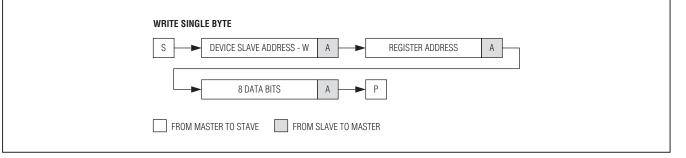

| Single-Byte Write                          |

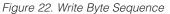

| Burst Write                                |

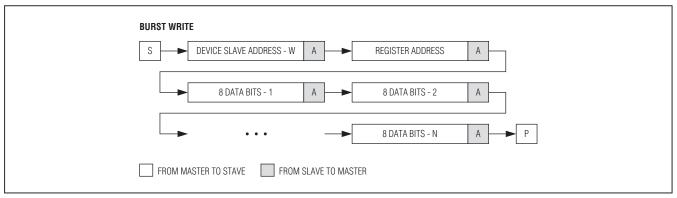

| Single-Byte Read                           |

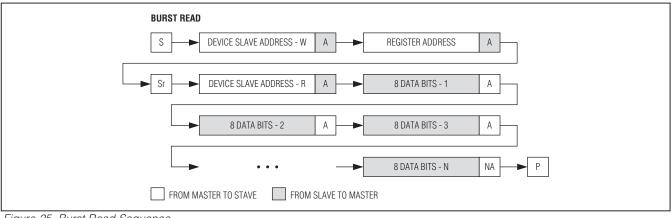

| Burst Read                                 |

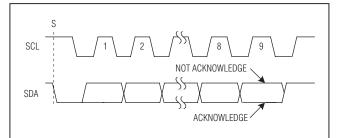

| Acknowledge Bits                           |

| Applications Information                   |

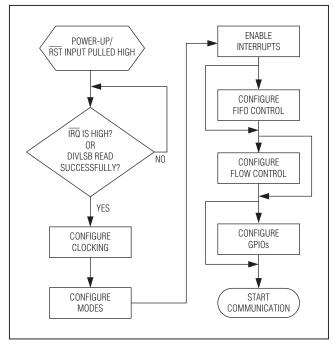

| Startup and Initialization                 |

| Low-Power Operation                        |

| Interrupts and Polling                     |

| Logic-Level Translation                    |

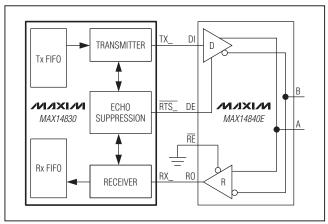

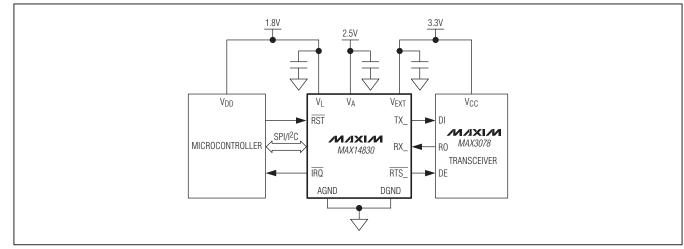

| IO-Link Application                        |

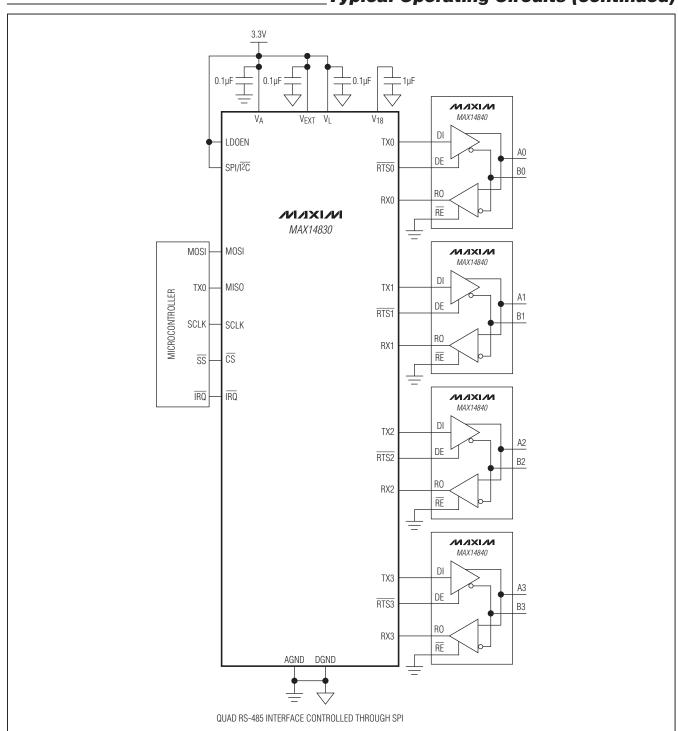

| Typical Operating Circuit                  |

| Chip Information                           |

| Package Information                        |

| Revision History                           |

# MAX14830

| _ |

|---|

| 0 |

| 3 |

| 0 |

| 4 |

|   |

|   |

|   |

| 4 |

|   |

|   |

# LIST OF FIGURES

| Figure 1. I <sup>2</sup> C Timing Diagram                              | 13 |

|------------------------------------------------------------------------|----|

| Figure 2. SPI Timing Diagram 1                                         | 13 |

| Figure 3. Transmit FIFO Signals 1                                      | 18 |

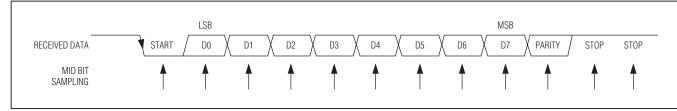

| Figure 4. Receive Data Format                                          | 19 |

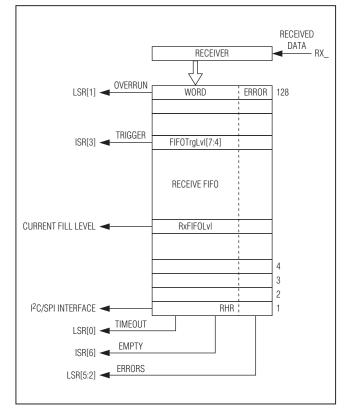

| Figure 5. Receive FIFO                                                 | 19 |

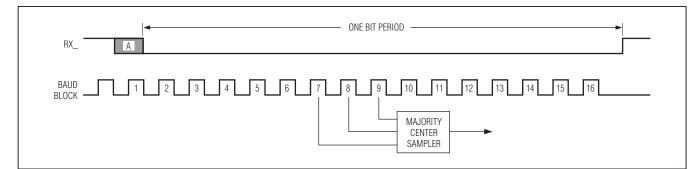

| Figure 6. Midbit Sampling 1                                            | 19 |

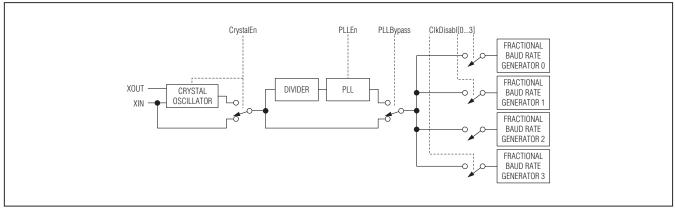

| Figure 7. Clock Selection Diagram                                      | 20 |

| Figure 8. 2x and 4x Baud Rates                                         | 21 |

| Figure 9. GPIO_ Clock Pulse Generator                                  | 22 |

| Figure 10. Auto Transceiver Direction Control 2                        | 23 |

| Figure 11. Setup and Hold times in Auto Transceiver Direction Control  | 23 |

| Figure 12. Single Transmitter Trigger Accuracy 2                       | 24 |

| Figure 13. Multiple Transmitter Synchronization Accuracy 2             | 25 |

| Figure 14. Echo Suppression Timing                                     | 25 |

| Figure 15. Half-Duplex with Echo Suppression 2                         | 26 |

| Figure 16. Simplified Interrupt Structure                              | 27 |

| Figure 17. PLL Signal Path                                             | 51 |

| Figure 18. SPI Write Cycle                                             | 58 |

| Figure 19. SPI Read Cycle                                              | 59 |

| Figure 20. SPI Fast Read Cycle                                         | 59 |

| Figure 21. I <sup>2</sup> C START, STOP, and Repeated START Conditions | 30 |

| Figure 22. Write Byte Sequence.                                        | 31 |

| Figure 23. Burst Write Sequence                                        | 31 |

| Figure 24. Read Byte Sequence                                          | 32 |

| Figure 25. Burst Read Sequence                                         | 32 |

| Figure 26. Acknowledge Bits                                            | 33 |

| Figure 27. Startup and Initialization Flow Chart 6                     | 33 |

| Figure 28. Logic-Level Translation                                     | 34 |

| Figure 29. Interchip Synchronization                                   | 34 |

| LIST OF TABLES                                                  |

|-----------------------------------------------------------------|

| Table 1. UART GPIO Assignments for GPIO Interrupts       38     |

| Table 2. StopBits Truth Table                                   |

| Table 3. Length_ Truth Table                                    |

| Table 4. SwFlow_ Truth Table                                    |

| Table 5. UART GPIO Assignments for GPIO Configuration    49     |

| Table 6. UART GPIO Assignments for GPIO Input/Output Data    50 |

| Table 7. PLLFactor_ Selector Guide    51                        |

| Table 8. GloblComnd Command Descriptions    54                  |

| Table 9. Extended Mode Addressing (SPI only)    54              |

| Table 10. SPI Command Byte Configuration    58                  |

| Table 11. SPI U1, U0 UART Selection    58                       |

| Table 12. I <sup>2</sup> C Address Map    60                    |

MAX14830

# LIST OF REGISTERS

| RHR—Receive Hold Register                                | С |

|----------------------------------------------------------|---|

| THR—Transmit Hold Register                               | С |

| IRQEn—IRQ Enable Register                                | 1 |

| ISR—Interrupt Status Register                            | 2 |

| LSRIntEn—Line Status Interrupt Enable Register           | 3 |

| LSR—Line Status Register                                 | 4 |

| SpclChrIntEn—Special Character Interrupt Enable Register | ō |

| SpclCharInt—Special Character Interrupt Register         | ô |

| STSIntEn—STS Interrupt Enable Register                   | 7 |

| STSInt—Status Interrupt Register                         | 3 |

| MODE1 Register                                           | 9 |

| MODE2 Register 40                                        | C |

| LCR—Line Control Register                                | 1 |

| RxTimeOut—Receiver Timeout Register                      | 2 |

| HDplxDelay Register                                      | 2 |

| IrDA Register                                            | 3 |

| FlowLvI—Flow Level Register                              | 4 |

| FIFOTrigLvI—FIFO Interrupt Trigger Level Register 44     | 4 |

| TxFIFOLvI—Transmit FIFO Level Register                   | 5 |

| RxFIFOLvI—Receive FIFO Level Register                    | 5 |

| FlowCtrl—Flow Control Register                           |   |

| XON1 Register                                            | 7 |

| XON2 Register                                            | 7 |

| XOFF1 Register                                           | 3 |

| XOFF2 Register                                           |   |

| GPIOConfg—GPIO Configuration Register                    |   |

| GPIOData—GPIO Data Register                              |   |

| PLLConfig—PLL Configuration Register                     | 1 |

| BRGConfig—Baud-Rate Generator Configuration Register     | 2 |

| DIVLSB—Baud-Rate Generator LSB Divisor Register          |   |

| DIVMSB—Baud-Rate Generator MSB Divisor Register          |   |

| CLKSource—Clock Source Register                          |   |

| GlobalIRQ—Global IRQ Register                            |   |

| GloblComnd—Global Command Register                       |   |

| TxSynch—Transmitter Synchronization Register             | 5 |

| SynchDelay1—Synchronization Delay Register 1 56          | 3 |

| SynchDelay2—Synchronization Delay Register 2 56          |   |

| TIMER1—Timer Register 1                                  |   |

| TIMER2—Timer Register 2                                  |   |

| RevID—Revision Identification Register                   | 7 |

# \_Functional Diagram

# ABSOLUTE MAXIMUM RATINGS

(Voltages referenced to AGND.)

| (Voltages foreforefore to / (artb.)                  |

|------------------------------------------------------|

| VL, VA, VEXT, XIN                                    |

| V18, XOUT0.3V to the lesser of (VA + 0.3V) and +2.0V |

| RST, IRQ, MOSI/A1, CS/A0, SCLK/SCL,                  |

| MISO/SDA, LDOEN, SPI/ $\overline{12C}$               |

| TX0, RX0, CTS0, GPIO0, GPIO1,                        |

| GPIO2, GPIO30.3V to (VEXT + 0.3V)                    |

| TX1, RX1, CTS1, GPIO4, GPIO5,                        |

| GPIO6, GPIO70.3V to (VEXT + 0.3V)                    |

| TX2, RX2, CTS2, GPIO8, GPIO9,                        |

| GPIO10, GPIO110.3V to (VEXT + 0.3V)                  |

|                                                      |

| TX3, RX3, CTS3, GPIO12, GPIO13,<br>GPIO14, GPIO150.3V to (VEXT + 0.3V)<br>DGND                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)<br>TQFN (derate 38.5mW/°C above +70°C)3076.9mW                                                                                                 |

| Operating Temperature Range       -40°C to +85°C         Maximum Junction Temperature       +150°C         Storage Temperature Range       -65°C to +150°C         Lead Temperature (soldering, 10s) |

# PACKAGE THERMAL CHARACTERISTICS (Note 1)

TQFN

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to <u>www.maxim-ic.com/thermal-tutorial</u>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **DC ELECTRICAL CHARACTERISTICS**

$(V_A = +2.35V \text{ to } +3.6V, V_L = +1.71V \text{ to } +3.6V, V_{EXT} = +1.71V \text{ to } +3.6V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at } V_A = +2.5V, V_L = +1.8V, V_{EXT} = +2.8V, T_A = +25^{\circ}C.)$  (Notes 2, 3)

| PARAMETER                                          | SYMBOL           | CONDITIONS                                                                                                                                               | MIN  | ТҮР | MAX  | UNITS |

|----------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|-------|

| Digital Interface Supply Voltage                   | VL               |                                                                                                                                                          | 1.71 |     | 3.6  | V     |

| Analog Supply Voltage                              | VA               |                                                                                                                                                          | 2.35 |     | 3.6  | V     |

| UART Interface Logic Supply<br>Voltage             | V <sub>EXT</sub> |                                                                                                                                                          | 1.71 |     | 3.6  | V     |

| Logic Supply Voltage                               | V <sub>18</sub>  |                                                                                                                                                          | 1.65 |     | 1.95 | V     |

| CURRENT CONSUMPTION                                |                  |                                                                                                                                                          |      |     |      |       |

| VA Supply Current                                  | IA               | 1.8MHz crystal oscillator active, PLL dis-<br>abled, SPI/I <sup>2</sup> C interface idle, UART inter-<br>faces idle, V <sub>LDOEN</sub> = V <sub>L</sub> |      |     | 400  | μΑ    |

|                                                    |                  | Baud rate = 1Mbps, 20MHz external clock,<br>SPI/I <sup>2</sup> C interface idle, PLL disabled, all<br>UARTs in loopback mode, V <sub>LDOEN</sub> = 0V    |      |     | 0.5  | mA    |

| VA Shutdown Supply Current                         | IASHDN           | Shutdown mode, $V_{LDOEN} = 0V$ , $V_{\overline{RST}} = 0V$ , all inputs and outputs are idle                                                            |      |     | 35   | μA    |

| V <sub>L</sub> Shutdown or Sleep Supply<br>Current | ١L               | Shutdown mode, $V_{LDOEN} = 0V$ , $V_{\overline{RST}} = 0V$ , all inputs and outputs are idle                                                            |      |     | 12   | μA    |

| VEXT Shutdown Supply Current                       | IEXT             | Shutdown mode, $V_{LDOEN} = 0V$ , $V_{\overline{RST}} = 0V$ , all inputs and outputs are idle                                                            |      |     | 8    | μA    |

# DC ELECTRICAL CHARACTERISTICS (continued)

$(V_A = +2.35V \text{ to } +3.6V, V_L = +1.71V \text{ to } +3.6V, V_{EXT} = +1.71V \text{ to } +3.6V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $V_A = +2.5V$ ,  $V_L = +1.8V$ ,  $V_{EXT} = +2.8V$ ,  $T_A = +25^{\circ}\text{C}$ .) (Notes 2, 3)

| PARAMETER                                                      | SYMBOL              | CONDITIONS                                                                                                                | MIN                    | ΤΥΡ       | MAX              | UNITS |

|----------------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------|-----------|------------------|-------|

| V <sub>18</sub> Input Power-Supply Current<br>in Shutdown Mode | I <sub>18SHDN</sub> | Shutdown mode, $V_{LDOEN} = 0V$ , $V_{\overline{RST}} = 0V$ , all inputs and outputs are idle                             |                        |           | 200              | μA    |

| V <sub>18</sub> Input Power-Supply Current                     | l18                 | Baud rate = 1Mbps, 20MHz external clock,<br>PLL disabled, all UARTs in loopback mode,<br>V <sub>LDOEN</sub> = 0V (Note 4) |                        |           | 5                | mA    |

| SCLK/SCL, MISO/SDA                                             |                     |                                                                                                                           |                        |           |                  |       |

| MISO/SDA Output Low Voltage                                    | Vol 100             | $I_{LOAD} = -3mA, V_L > 2V$                                                                                               |                        |           | 0.4              | V     |

| in I <sup>2</sup> C Mode                                       | Vol,12C             | $I_{LOAD} = -3mA, V_L < 2V$                                                                                               |                        |           | $0.2 \times V_L$ | V     |

| MISO/SDA Output Low Voltage<br>in SPI Mode                     | Vol,spi             | ILOAD = -2mA                                                                                                              |                        |           | 0.4              | V     |

| MISO/SDA Output High Voltage in SPI Mode                       | Voh,spi             | ILOAD = 2mA                                                                                                               |                        |           | VL -<br>0.4      | V     |

| Input Low Voltage                                              | VIL                 | SPI and I <sup>2</sup> C mode                                                                                             |                        |           | 0.3 x VL         | V     |

| Input High Voltage                                             | VIH                 | SPI and I <sup>2</sup> C mode                                                                                             | 0.7 x VL               |           |                  | V     |

| Input Hysteresis                                               | VHYST               | SPI and I <sup>2</sup> C mode                                                                                             | (                      | 0.05 x VL | -                | V     |

| Input Leakage Current                                          | Ι <sub>Ι</sub>      | $V_{IN} = 0$ to $V_L$ , SPI and I <sup>2</sup> C mode                                                                     | -1                     |           | +1               | μΑ    |

| Input Capacitance                                              | CIN                 | SPI and I <sup>2</sup> C mode                                                                                             |                        | 5         |                  | рF    |

| SPI/I2C, CS/A0, MOSI/A1 INPUT                                  | S                   |                                                                                                                           |                        |           |                  |       |

| Input Low Voltage                                              | VIL                 | SPI and I <sup>2</sup> C mode                                                                                             |                        |           | $0.3 \times V_L$ | V     |

| Input High Voltage                                             | VIH                 | SPI and I <sup>2</sup> C mode                                                                                             | $0.7 \times V_L$       |           |                  | V     |

| Input Hysteresis                                               | VHYST               | SPI and I <sup>2</sup> C mode                                                                                             |                        | 50        |                  | mV    |

| Input Leakage Current                                          | ١ <sub>١</sub>      | $V_{IN} = 0$ to $V_{L}$ , SPI and I <sup>2</sup> C mode                                                                   | -1                     |           | +1               | μΑ    |

| Input Capacitance                                              | CIN                 | SPI and I <sup>2</sup> C mode                                                                                             |                        | 5         |                  | рF    |

| <b>IRQ</b> OUTPUT (OPEN DRAIN)                                 |                     |                                                                                                                           |                        |           |                  |       |

| Output Low Voltage                                             | Vol                 | $I_{LOAD} = -2mA$                                                                                                         |                        |           | 0.4              | V     |

| Output Leakage Current                                         | ILK                 | $V_{\overline{IRQ}} = 0$ to $V_L$ , $\overline{IRQ}$ is not asserted                                                      | -1                     |           | +1               | μΑ    |

| LDOEN AND RST INPUTS                                           |                     |                                                                                                                           |                        |           |                  |       |

| Input Low Voltage                                              | VIL                 |                                                                                                                           |                        |           | $0.3 \times V_L$ | V     |

| Input High Voltage                                             | VIH                 |                                                                                                                           | 0.7 x VL               |           |                  | V     |

| Input Hysteresis                                               | VHYST               |                                                                                                                           |                        | 50        |                  | mV    |

| Input Leakage Current                                          | lin                 | $V_{IN} = 0$ to $V_L$                                                                                                     | -1                     |           | +1               | μΑ    |

| UART INTERFACE                                                 |                     |                                                                                                                           |                        |           |                  |       |

| RTS0, RTS1, RTS2, RTS3, TX0,                                   | TX1, TX2, TX        | (3 OUTPUTS                                                                                                                |                        |           |                  |       |

| Output Low Voltage                                             | Vol                 | ILOAD = -2mA                                                                                                              |                        |           | 0.4              | V     |

| Output High Voltage                                            | Voh                 | $I_{LOAD} = 2mA$                                                                                                          | V <sub>EXT</sub> - 0.4 | 4         |                  | V     |

| Input Leakage Current                                          | lin                 | Output is three-stated, $V_{\overline{RTS}} = 0$ to $V_{EXT}$                                                             | -1                     |           | +1               | μΑ    |

| Input Capacitance                                              | CIN                 | High-Z mode                                                                                                               |                        | 5         |                  | pF    |

# DC ELECTRICAL CHARACTERISTICS (continued)

$(V_A = +2.35V \text{ to } +3.6V, V_L = +1.71V \text{ to } +3.6V, V_{EXT} = +1.71V \text{ to } +3.6V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $V_A = +2.5V$ ,  $V_L = +1.8V$ ,  $V_{EXT} = +2.8V$ ,  $T_A = +25^{\circ}\text{C}$ .) (Notes 2, 3)

| PARAMETER                                       | SYMBOL       | CONDITIONS                                                      | MIN                  | TYP  | MAX                    | UNITS |

|-------------------------------------------------|--------------|-----------------------------------------------------------------|----------------------|------|------------------------|-------|

| RX0, RX1, RX2, RX3, CTS0, CTS                   | 51, CTS2, CT | S3 INPUTS                                                       |                      |      |                        |       |

| Input Low Voltage                               | VIL          |                                                                 |                      | 0    | .3 x V <sub>EXT</sub>  | V     |

| Input High Voltage                              | VIH          |                                                                 | 0.7 x V <sub>E</sub> | XT   |                        | V     |

| Input Hysteresis                                | VHYST        |                                                                 |                      | 50   |                        | mV    |

| CTS0, CTS1, CTS2, CTS3 Input<br>Leakage Current | IIN_CTS      | $V_{\overline{CTS}} = 0$ to $V_{EXT}$                           | -1                   |      | +1                     | μA    |

| RX0, RX1, RX2, RX3 Pullup<br>Current            | IIN_RX_      | V <sub>RX</sub> _= 0V                                           | -7.5                 | -5.5 | -3.5                   | μΑ    |

| Input Capacitance                               | CIN_UART     |                                                                 |                      | 5    |                        | рF    |

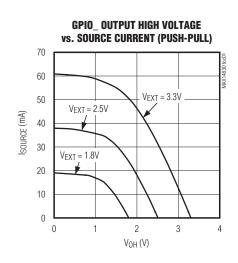

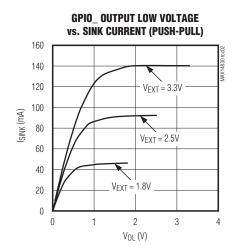

| GPIO0-GPIO15 INPUTS/OUTPU                       | TS           |                                                                 |                      |      |                        |       |

|                                                 |              | $I_{LOAD} = -20$ mA, $V_{EXT} > 2.3$ V, push-pull or open drain |                      |      | 0.45                   | — V   |

| Output Low Voltage                              | Vol          | $I_{LOAD}$ = -20mA, $V_{EXT}$ < 2.3V, push-pull or open drain   |                      |      | 0.55                   |       |

| Output High Voltage                             | Voh          | I <sub>LOAD</sub> = 5mA, push-pull                              |                      | V    | / <sub>EXT</sub> - 0.4 | V     |

| Input Low Voltage                               | VIL          | GPIO_ is configured as an input                                 |                      |      | 0.4                    | V     |

| Input High Voltage                              | VIH          | GPIO_ is configured as an input                                 | 2/3 x V <sub>E</sub> | XT   |                        | V     |

| Pulldown Current                                | IPD          | GPIO_ = V <sub>EXT</sub>                                        | 3.5                  | 5.5  | 7.5                    | μΑ    |

| XIN                                             |              |                                                                 |                      |      |                        |       |

| Input Low Voltage                               | VIL          |                                                                 |                      |      | 0.2                    | V     |

| Input High Voltage                              | VIH          |                                                                 | 1.2                  |      |                        | V     |

| Input Capacitance                               | CXIN         |                                                                 |                      | 16   |                        | pF    |

| XOUT                                            |              |                                                                 |                      |      |                        |       |

| Input Capacitance                               | Схоит        |                                                                 |                      | 16   |                        | рF    |

# **AC ELECTRICAL CHARACTERISTICS**

$(V_A = +2.35V \text{ to } +3.6V, V_L = +1.71V \text{ to } +3.6V, V_{EXT} = +1.71V \text{ to } +3.6V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $V_A = +2.8V$ ,  $V_L = +1.8V$ ,  $V_{EXT} = +2.5V$ ,  $T_A = +25^{\circ}\text{C}$ .) (Notes 2, 3)

| PARAMETER                          | SYMBOL | CONDITIONS | MIN | TYP | MAX | UNITS |

|------------------------------------|--------|------------|-----|-----|-----|-------|

| INTERNAL OSCILLATOR                |        |            |     |     |     |       |

| External Crystal Frequency         | fxosc  |            | 1   |     | 4   | MHz   |

| External Clock Frequency           | fCLK   |            | 0.5 |     | 35  | MHz   |

| External Clock Duty Cycle          |        | (Note 5)   | 45  |     | 55  | %     |

| Baud-Rate Generator Clock<br>Input | fREF   | (Note 5)   |     |     | 96  | MHz   |

# AC ELECTRICAL CHARACTERISTICS (continued)

$(V_A = +2.35V \text{ to } +3.6V, V_L = +1.71V \text{ to } +3.6V, V_{EXT} = +1.71V \text{ to } +3.6V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $V_A = +2.8V$ ,  $V_L = +1.8V$ ,  $V_{EXT} = +2.5V$ ,  $T_A = +25^{\circ}\text{C}$ .) (Notes 2, 3)

| PARAMETER                                     | SYMBOL     | CONDITIONS                                                                | MIN           | TYP | MAX  | UNITS |  |  |  |

|-----------------------------------------------|------------|---------------------------------------------------------------------------|---------------|-----|------|-------|--|--|--|

| I <sup>2</sup> C BUS: TIMING CHARACTERIS      | STICS (SEE | FIGURE 1)                                                                 |               |     |      |       |  |  |  |

|                                               |            | Standard mode                                                             |               |     | 100  |       |  |  |  |

| SCL Clock Frequency                           | fscl       | Fast mode                                                                 |               |     | 400  | kHz   |  |  |  |

|                                               |            | Fast mode plus                                                            |               |     | 1000 | 1     |  |  |  |

|                                               |            | Standard mode                                                             | 4.7           |     |      |       |  |  |  |

| Bus Free Time Between a STOP                  | tBUF       | Fast mode                                                                 | 1.3           |     |      | μs    |  |  |  |

| and START Condition                           |            | Fast mode plus                                                            | 0.5           |     |      |       |  |  |  |

|                                               |            | Standard mode                                                             | 4.0           |     |      |       |  |  |  |

| Hold Time for START Condition                 | thd:sta    | Fast mode                                                                 | 0.6           |     |      | μs    |  |  |  |

| and Repeated START Condition                  |            | Fast mode plus                                                            | 0.26          |     |      |       |  |  |  |

|                                               |            | Standard mode                                                             | 4.7           |     |      |       |  |  |  |

| Low Period of the SCL Clock                   | tLOW       | Fast mode                                                                 | 1.3           |     |      | μs    |  |  |  |

|                                               |            | Fast mode plus                                                            | 0.5           |     |      |       |  |  |  |

|                                               |            | Standard mode                                                             | 4.0           |     |      |       |  |  |  |

| High Period of the SCL Clock                  | thigh      | Fast mode                                                                 | 0.6           |     |      | μs    |  |  |  |

| C                                             |            | Fast mode plus                                                            | 0.26          |     | -    |       |  |  |  |

|                                               |            | Standard mode                                                             | 0             |     | 0.9  |       |  |  |  |

| Data Hold Time                                | thd:dat    | Fast mode                                                                 | 0             |     | 0.9  | μs    |  |  |  |

|                                               | 11010711   | Fast mode plus                                                            | 0             |     |      | 1 '   |  |  |  |

|                                               |            | Standard mode                                                             | 250           |     |      |       |  |  |  |

| Data Setup Time                               | tsu:dat    | Fast mode                                                                 | 100           |     |      | ns    |  |  |  |

|                                               |            | Fast mode plus                                                            | 50            |     |      |       |  |  |  |

|                                               |            | Standard mode                                                             | 4.7           |     |      |       |  |  |  |

| Setup Time for Repeated START                 | tsu:sta    | Fast mode                                                                 | 0.6           |     |      | μs    |  |  |  |

| Condition                                     |            | Fast mode plus                                                            | 0.26          |     |      |       |  |  |  |

|                                               |            | Standard mode (0.3 x V <sub>L</sub> to 0.7 x V <sub>L</sub> )             | 20 +          |     |      |       |  |  |  |

|                                               |            | (Note 6)                                                                  | 0.1Cb         |     | 1000 |       |  |  |  |

| Rise Time of SDA and SCL<br>Signals Receiving | tR         | Fast mode (0.3 × V <sub>L</sub> to 0.7 × V <sub>L</sub> ) (Note 6)        | 20 +<br>0.1Cb |     | 300  | ns    |  |  |  |

|                                               |            | Fast mode plus                                                            |               |     | 120  | 1     |  |  |  |

|                                               |            | Standard mode (0.7 x V <sub>L</sub> to 0.3 x V <sub>L</sub> )<br>(Note 6) | 20 +<br>0.1Cb |     | 300  |       |  |  |  |

| Fall Time of SDA and SCL<br>Signals           | t⊨         | Fast mode (0.7 × V <sub>L</sub> to 0.3 × V <sub>L</sub> ) (Note 6)        | 20 +<br>0.1Cb |     | 300  | ns    |  |  |  |

|                                               |            | Fast mode plus                                                            |               | -   | 120  | 1     |  |  |  |

|                                               |            | Standard mode                                                             | 4.7           |     |      |       |  |  |  |

| Setup Time for STOP Condition                 | tsu:sto    | Fast mode                                                                 | 0.6           |     |      | μs    |  |  |  |

|                                               |            | Fast mode plus                                                            | 0.26          |     |      |       |  |  |  |

|                                               |            | Standard mode                                                             | 1             |     | 400  | pF    |  |  |  |

| Capacitive Load for SDA and                   | Cb         | Fast mode                                                                 |               |     | 400  |       |  |  |  |

| SCL (Note 4)                                  |            | Fast mode plus                                                            | 1             |     | 550  | -     |  |  |  |

# AC ELECTRICAL CHARACTERISTICS (continued)

$(V_A = +2.35V \text{ to } +3.6V, V_L = +1.71V \text{ to } +3.6V, V_{EXT} = +1.71V \text{ to } +3.6V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $V_A = +2.8V$ ,  $V_L = +1.8V$ ,  $V_{EXT} = +2.5V$ ,  $T_A = +25^{\circ}\text{C}$ .) (Notes 2, 3)

| PARAMETER                          | SYMBOL     | CONDITIONS | MIN  | TYP | MAX | UNITS |

|------------------------------------|------------|------------|------|-----|-----|-------|

| SCL and SDA I/O Capacitance        | CI/O       | (Note 5)   |      |     | 10  | pF    |

| Pulse Width of Spike<br>Suppressed | tsp        |            |      |     | 50  | ns    |

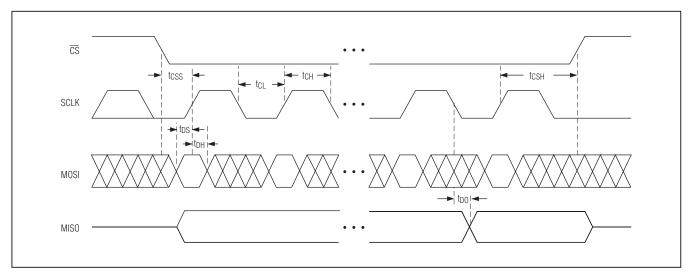

| SPI BUS: TIMING CHARACTERI         | STICS (SEE | FIGURE 2)  | ·    |     |     |       |

| SCLK Clock Period                  | tCH+CL     |            | 38.4 |     |     | ns    |

| SCLK Pulse Width High              | tСН        |            | 16   |     |     | ns    |

| SCLK Pulse Width Low               | tCL        |            | 16   |     |     | ns    |

| CS Fall to SCLK Rise Time          | tcss       |            | 0    |     |     | ns    |

| MOSI Hold Time                     | tDН        |            | 3    |     |     | ns    |

| MOSI Setup Time                    | tDS        |            | 5    |     |     | ns    |

| Output Data Propagation Delay      | tDO        |            |      |     | 20  | ns    |

| MISO Rise and Fall Times           | tFT        |            |      |     | 10  | ns    |

| CS Hold Time                       | tCSH       |            | 30   |     |     | ns    |

Note 2: All devices are production tested at TA = +25°C. Specifications over temperature are guaranteed by design.

Note 3: Currents entering the IC are negative, and currents exiting the IC are positive.

Note 4: When V18 is powered by an external voltage regulator, the external power supply must have current capability above or

equal to 118.

Note 5: Not production tested. Guaranteed by design.

Note 6: Cb is the total capacitance of either the clock or data line of the synchronous bus in pF.

# \_Test Circuits/Timing Diagrams

Figure 1. I<sup>2</sup>C Timing Diagram

Figure 2. SPI Timing Diagram

**MAX14830**

# **Typical Operating Characteristics**

(T<sub>A</sub> = +25°C, unless otherwise noted.)

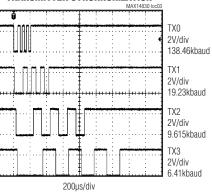

TRANSMITTER SYNCHRONIZATION

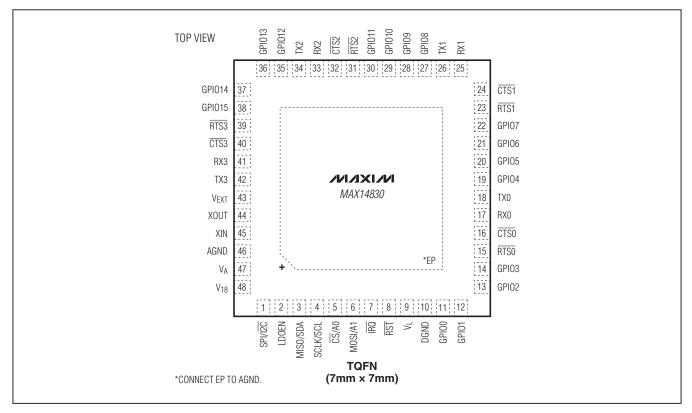

# Pin Configuration

MAX14830

# **Pin Description**

| PIN | NAME     | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SPI/I2C  | SPI or Active-Low I <sup>2</sup> C Selector Input. Drive SPI/I2C high to enable SPI. Drive SPI/I2C low to enable I <sup>2</sup> C.                                                                                                                                                                                                                                                                       |

| 2   | LDOEN    | LDO Enable Input. Drive LDOEN high to enable the internal 1.8V LDO. Drive LDOEN low to disable the internal LDO. When LDOEN is low, V18 can be supplied by an external voltage source.                                                                                                                                                                                                                   |

| 3   | MISO/SDA | Serial-Data Output. When SPI/I2C is high, MISO/SDA functions as the MISO, SPI serial-data output. When SPI/I2C is low, MISO/SDA functions as the SDA, I <sup>2</sup> C serial-data input/output.                                                                                                                                                                                                         |

| 4   | SCLK/SCL | Serial-Clock Input. When SPI/I2C is high, SCLK/SCL functions as the SCLK, SPI serial-clock input (up to 26MHz). When SPI/I2C is low, SCLK/SCL functions as the SCL, I <sup>2</sup> C serial-clock input (up to 1MHz).                                                                                                                                                                                    |

| 5   | CS/A0    | Active-Low Chip-Select and Address 0 Input. When SPI/ $\overline{I2C}$ is high, $\overline{CS}/A0$ functions as the $\overline{CS}$ , SPI active-low chip-select input. When SPI/ $\overline{I2C}$ is low, $\overline{CS}/A0$ functions as the A0, I <sup>2</sup> C device address programming input. Connect $\overline{CS}/A0$ to SDA, SCL, DGND, or V <sub>L</sub> when SPI/ $\overline{I2C}$ is low. |

| 6   | MOSI/A1  | Serial-Data and Address 1 Input. When SPI/ $\overline{I2C}$ is high, MOSI/A1 functions as the MOSI, SPI serial-data input. When SPI/ $\overline{I2C}$ is low, MOSI/A1 functions as the A1, I <sup>2</sup> C device address programming input. Connect MOSI/A1 to SDA, SCL, DGND, or V <sub>L</sub> when SPI/ $\overline{I2C}$ is low.                                                                    |

| 7   | ĪRQ      | Active-Low Interrupt Open-Drain Output. IRQ is asserted when an interrupt is pending.                                                                                                                                                                                                                                                                                                                    |

| 8   | RST      | Active-Low Reset Input. Drive RST low to force all of the UARTs into hardware reset mode. In hardware reset mode, the oscillator and the internal PLL are shut down and there is no clock activity.                                                                                                                                                                                                      |

# \_\_\_\_\_Pin Description (continued)

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                          |

|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9   | VL    | Digital Interface Logic-Level Supply. V <sub>L</sub> powers the internal logic-level translators for $\overline{RST}$ , $\overline{IRQ}$ , MOSI/A1, $\overline{CS}$ /A0, SCLK/SCL, MISO/SDA, LDOEN, and SPI/I2C. Bypass V <sub>L</sub> with a 0.1µF ceramic capacitor to DGND.                                                                    |

| 10  | DGND  | Digital Ground                                                                                                                                                                                                                                                                                                                                    |

| 11  | GPIO0 | General-Purpose Input/Output 0. GPIO0 is user-programmable as an input or output (push-pull or open drain) or external event interrupt source. GPIO0 has a weak pulldown resistor to ground. GPIO0 is the reference clock output when bit 7 of the TxSynch register is set to 1 (see the UART Clock to GPIO section for more information).        |

| 12  | GPIO1 | General-Purpose Input/Output 1. GPIO1 is user-programmable as an input or output (push-pull or open drain) or external event interrupt source. GPIO1 has a weak pulldown resistor to ground. GPIO1 is the TIMER output when bit 7 of the TIMER2 register is set to 1.                                                                             |

| 13  | GPIO2 | General-Purpose Input/Output 2. GPIO2 is user-programmable as an input or output (push-pull or open drain) or external event interrupt source. GPIO2 has a weak pulldown resistor to ground.                                                                                                                                                      |

| 14  | GPIO3 | General-Purpose Input/Output 3. GPIO3 is user-programmable as an input or output (push-pull or open drain) or external event interrupt source. GPIO3 has a weak pulldown resistor to ground.                                                                                                                                                      |

| 15  | RTSO  | Active-Low Request-to-Send Output for UART0. RTSO can be set high or low by programming the LCR register. RTSO is the UART system clock/fractional divider output when bit 7 of the CLKSource register is set to 1.                                                                                                                               |

| 16  | CTSO  | Active-Low Clear-to-Send Input for UARTO. CTSO is a flow control status input.                                                                                                                                                                                                                                                                    |

| 17  | RX0   | Serial Receiving Data Input for UARTO. RXO has a weak pullup to VEXT.                                                                                                                                                                                                                                                                             |

| 18  | TX0   | Serial Transmitting Data Output for UART0                                                                                                                                                                                                                                                                                                         |

| 19  | GPIO4 | General-Purpose Input/Output 4. GPIO4 is user-programmable as an input or output (push-pull or open drain) or external event interrupt source. GPIO4 has a weak pulldown resistor to ground. GPIO4 is the reference clock output when bit 7 of the TxSynch register is set to 1 (see the UART Clock to GPIO section for more information).        |

| 20  | GPIO5 | General-Purpose Input/Output 5. GPIO5 is user-programmable as an input or output (push-pull or open drain) or external event interrupt source. GPIO5 has a weak pulldown resistor to ground. GPIO5 is the TIMER output when bit 7 of the TIMER2 register is set to 1.                                                                             |

| 21  | GPIO6 | General-Purpose Input/Output 6. GPIO6 is user-programmable as an input or output (push-pull or open drain) or external event interrupt source. GPIO6 has a weak pulldown resistor to ground.                                                                                                                                                      |

| 22  | GPIO7 | General-Purpose Input/Output 7. GPIO7 is user-programmable as an input or output (push-pull or open drain) or external event interrupt source. GPIO7 has a weak pulldown resistor to ground.                                                                                                                                                      |

| 23  | RTS1  | Active-Low Request-to-Send Output for UART1. RTS1 can be set high or low by programming the LCR register. RTS1 is the UART system clock/fractional divider output when bit 7 of the CLKSource register is set to 1.                                                                                                                               |

| 24  | CTS1  | Active-Low Clear-to-Send Input for UART1. CTS1 is a flow control status input.                                                                                                                                                                                                                                                                    |

| 25  | RX1   | Serial Receiving Data Input for UART1. RX1 has a weak pullup to VEXT.                                                                                                                                                                                                                                                                             |

| 26  | TX1   | Serial Transmitting Data Output for UART1                                                                                                                                                                                                                                                                                                         |

| 27  | GPIO8 | General-Purpose Input/Output 8. GPIO8 is user-programmable as an input or output (push-pull or open drain) or external event interrupt source. GPIO8 has a weak pulldown resistor to ground. GPIO8 is the reference clock output when bit 7 of the TxSynch register is set to 1 (see the <i>UART Clock to GPIO</i> section for more information). |

# \_\_Pin Description (continued)

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                       |

|-----|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28  | GPIO9           | General-Purpose Input/Output 9. GPIO9 is user-programmable as an input or output (push-pull or open drain) or external event interrupt source. GPIO9 has a weak pulldown resistor to ground. GPIO9 is the TIMER output when bit 7 of the TIMER2 register is set to 1.                                                                          |

| 29  | GPIO10          | General-Purpose Input/Output 10. GPIO10 is user-programmable as an input or output (push-pull or open drain) or external event interrupt source. GPIO10 has a weak pulldown resistor to ground.                                                                                                                                                |

| 30  | GPIO11          | General-Purpose Input/Output 11. GPIO11 is user-programmable as an input or output (push-pull or open drain) or external event interrupt source. GPIO11 has a weak pulldown resistor to ground.                                                                                                                                                |

| 31  | RTS2            | Active-Low Request-to-Send Output for UART2. RTS2 can be set high or low by programming the LCR register. RTS2 is the UART system clock/fractional divider output when bit 7 of the CLKSource register is set to 1.                                                                                                                            |

| 32  | CTS2            | Active-Low Clear-to-Send Input for UART2. CTS2 is a flow control status input.                                                                                                                                                                                                                                                                 |

| 33  | RX2             | Serial Receiving Data Input for UART2. RX2 has a weak pullup to VEXT.                                                                                                                                                                                                                                                                          |

| 34  | TX2             | Serial Transmitting Data Output for UART2                                                                                                                                                                                                                                                                                                      |

| 35  | GPIO12          | General-Purpose Input/Output 12. GPIO12 is user-programmable as an input or output (push-pull or open drain) or external event interrupt source. GPIO12 has a weak pulldown resistor to ground. GPIO12 is the reference clock output when bit 7 of the TxSynch register is set to 1 (see the UART Clock to GPIO section for more information). |

| 36  | GPIO13          | General-Purpose Input/Output 13. GPIO13 is user-programmable as an input or output (push-pull or open drain) or external event interrupt source. GPIO13 has a weak pulldown resistor to ground. GPIO13 is the TIMER output if bit 7 of the TIMER2 register is set to 1.                                                                        |

| 37  | GPIO14          | General-Purpose Input/Output 14. GPIO14 is user-programmable as an input or output (push-pull or open drain) or external event interrupt source. GPIO14 has a weak pulldown resistor to ground.                                                                                                                                                |

| 38  | GPIO15          | General-Purpose Input/Output 15. GPIO15 is user-programmable as an input or output (push-pull or open drain) or external event interrupt source. GPIO15 has a weak pulldown resistor to ground.                                                                                                                                                |

| 39  | RTS3            | Active-Low Request-to-Send Output for UART3. RTS3 can be set high or low by programming the LCR register. RTS3 is the UART system clock/fractional divider output when bit 7 of the CLKSource register is set to 1.                                                                                                                            |

| 40  | CTS3            | Active-Low Clear-to-Send Input for UART3. CTS3 is a flow control status input.                                                                                                                                                                                                                                                                 |

| 41  | RX3             | Serial Receiving Data Input for UART3. RX3 has a weak pullup to VEXT.                                                                                                                                                                                                                                                                          |

| 42  | TX3             | Serial Transmitting Data Output for UART3                                                                                                                                                                                                                                                                                                      |

| 43  | VEXT            | Transceiver Interface Level Supply. VEXT powers the internal logic-level translators for RX_, TX_, RTS_, CTS_, and GPIO Bypass VEXT with a 0.1µF ceramic capacitor to DGND.                                                                                                                                                                    |

| 44  | XOUT            | Crystal Output. When using an external crystal, connect one end of the crystal to XOUT and the other to XIN. When using an external clock source, leave XOUT unconnected.                                                                                                                                                                      |

| 45  | XIN             | Crystal/Clock Input. When using an external crystal, connect one end of the crystal to XIN and the other one to XOUT. When using an external clock source, drive XIN with the external clock.                                                                                                                                                  |

| 46  | AGND            | Analog Ground                                                                                                                                                                                                                                                                                                                                  |

| 47  | VA              | Analog Supply. V <sub>A</sub> powers the PLL, and the internal LDO. Bypass V <sub>A</sub> with a $0.1\mu$ F ceramic capacitor to AGND.                                                                                                                                                                                                         |

| 48  | V <sub>18</sub> | Internal 1.8V LDO Output and 1.8V Logic Supply Input. Bypass V <sub>18</sub> with a 1µF ceramic capacitor to DGND.                                                                                                                                                                                                                             |

| _   | EP              | Exposed Paddle. Connect EP to AGND. Do not use EP as the main AGND connection.                                                                                                                                                                                                                                                                 |

# **Detailed Description**

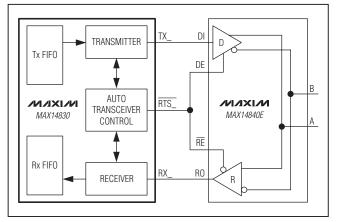

The MAX14830 guad UART bridges an SPI/MICROWIRE™ or I<sup>2</sup>C microprocessor bus to an asynchronous interface like RS-485, RS-232, or IrDA, The MAX14830 contains advanced UARTs and baud-rate generators with a synchronous serial-data interface and an interrupt generator. The MAX14830 is configured by writing an 8-bit word to the configuration registers through either SPI or I<sup>2</sup>C. These registers are organized by related function as shown in the Register Map.

The host controller loads transmit data into the THR register through SPI or I<sup>2</sup>C. This data is automatically pushed into the Transmit FIFOs, formatted, and sent out at TX\_. The MAX14830 adds START and STOP and parity bits to the data and sends the data out at the selected baud rates. The clock configuration registers determine the baud rates, clock source selection, clock frequency prescaling, and fractional baud-rate generators.

The MAX14830 receiver detects a START bit as a highto-low RX transition. An internal clock samples this data at 16 times the data rate. The received data is automatically placed in the Receive FIFOs and can then be read out of the RxFIFOs through the RHRs.

The MAX14830 features four identical UARTS. Text in this data sheet references individual UART operation. unless otherwise noted.

# **Receive and Transmit FIFOs**

The UART's receiver and the transmitter each have a 128-word deep FIFO reducing the intervals that the host processor needs to dedicate for high-speed, highvolume data transfer. As the data rates of the asynchronous RX\_ and TX\_ interfaces increase and get closer to those of the host controller's SPI/I<sup>2</sup>C data rates, UART management and flow control can make up a significant portion of the host's activity. By increasing FIFO size, the host is interrupted less often and can utilize SPI and I<sup>2</sup>C burst data block transfers to/from the FIFOs.

FIFO trigger levels can generate interrupts to the host controller, signaling that programmed FIFO fill levels have been reached. The transmitter and receiver trigger levels are programmed through FIFOTrigLvI with a resolution of eight FIFO locations. When a Receive FIFO trigger is generated, the host knows that the Receive FIFO has a defined number of words waiting to be read out or that a known number of vacant FIFO locations are available, ready to be filled. The Transmit FIFO trigger

MICROWIRE is a trademark of National Semiconductor Corp.

generates an interrupt when the Transmit FIFO level is above the programmed trigger level. The host then knows to throttle data writing to the Transmit FIFO.

The host can read out the number of words present in each of the FIFOs at any time through the TxFIFOLvI and RxFIFOLvl registers.

# **Transmitter Operation**

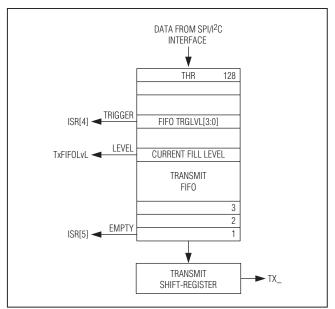

Figure 3 shows the structure of the transmitter with the TxFIFO. The Transmit FIFO can hold up to 128 words that are written to it through the Transmit Hold Register (THR).

The current number of words in the TxFIFO can be read out through the TxFIFOLvI register. The Transmit FIFO can be programmed to generate an interrupt when a programmed number of words are present in the TxFIFO through the FIFOTrgLvl register. The TxFIFO interrupt trigger level is selectable through FIFOTrgLvI[3:0]. When the Transmit FIFO fill level reaches the programmed trigger level, the ISR[4] interrupt is set.

The Transmit FIFO is empty when ISR[5]:TFifoEmptyInt is set. ISR[5] turns high when the transmitter starts transmitting the last word in the TxFIFO. Hence the transmitter is completely empty after ISR[5] is set with an additional delay equal to the length of a complete character (including START, parity, and STOP bits).

Figure 3. Transmit FIFO Signals

Figure 4. Receive Data Format

Figure 5. Receive FIFO

The contents of the TxFIFO and RxFIFOs are both cleared through MODE2[1]: FIFORst.

To halt transmission, set MODE1[1]: TxDisabl to 1. After MODE1[1] is set, the transmitter completes transmission of the current character and then ceases transmission.

The TX\_ output logic can be inverted through IrDA[5]: TxInv. If not stated otherwise, all transmitter logic described in this data sheet assumes that IrDA[5] is 0.

# **Receiver Operation**

The receiver expects the format of the data at RX\_ to be as shown in Figure 4. The quiescent logic state is high and the first bit (the START bit) is logic-low. The receiver samples the data near the midbit instant (Figure 4). The received words and their associated errors are deposited into the Receive FIFO. Errors and status information are stored for every received word (Figure 5). The host reads the data out of the Receive FIFO through the Receive Hold Register (RHR), oldest data first. The status information of the most recently read word in the RHR is located in the Line Status Register (LSR). After a word is read out of the RHR, the LSR contains the status information for that word.

The following three error conditions are determined for each received word: parity error, framing error, and noise on the line. Line noise is detected by checking the consistency of the logic of the three samples (Figure 6).

Figure 6. Midbit Sampling

The receiver can be turned off through MODE1[0]: RxDisabl. When this bit is set to 1, the MAX14830 turns the receiver off immediately following the current word and does not receive any further data.

The RX\_ input logic can be inverted through IrDA[4]: RxInv.

# **Line Noise Indication**

When operating in standard or 2x (i.e. not 4x) rate mode, the MAX14830 checks that the binary logic level of the three samples per received bit are identical. If any of the three samples have differing logic levels, then noise on the transmission line has affected the received data and is considered to be noisy. This noise indication is reflected in the LSR[5]: RxNoise bit for each received byte. Parity errors are another indication of noise, but are not as sensitive.

### **Clocking and Baud-Rate Generation**

The MAX14830 can be clocked by an external crystal, or an external clock source. Figure 7 shows a simplified diagram of the clocking circuitry. When the MAX14830 is clocked by a crystal, the STSInt[5]: ClockReady indicates when the clocks have settled and the baud-rate generator is ready for stable operation.

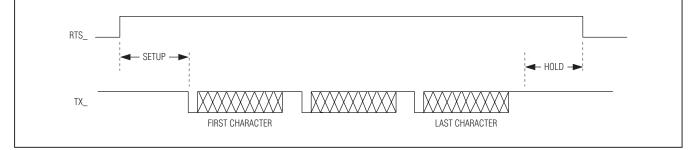

Each UART baud rate can be individually programmed. To achieve fast baud rate changes, first disable the UART's clock by setting CLKDisabl to 1. Then change the baud rate divisor and subsequently enable the clock via CLKDisabl. To check that the UART's clocking is programmed as expected, route the baud rate clock to  $\overline{\text{RTS}}$  using the CLKtoRTS bit. The clock rate of this is 16x the baud rate in standard operating mode and 8x the baud rate in 2x rate mode. In 4x rate mode, the CLKOUT frequency is 4x the programmed baud rate. If the fractional portion of the baud-rate generator is used, the clock is not regular and exhibits jitter.

### Crystal Oscillator

Set BRGConfig[6]: CLKDisabl to 0 and CLKSource[1]: CrystalEn to 1 to enable and select the crystal oscillator. The on-chip crystal oscillator circuit has load capacitances of 16pF (typ) integrated in both XIN and XOUT. Connect an external crystal or ceramic oscillator between XIN and XOUT.

### External Clock Source

Connect an external clock source to XIN when not using a crystal oscillator. Leave XOUT unconnected. Set CLKSource[1]: CrystalEn to 0 to select external clocking.

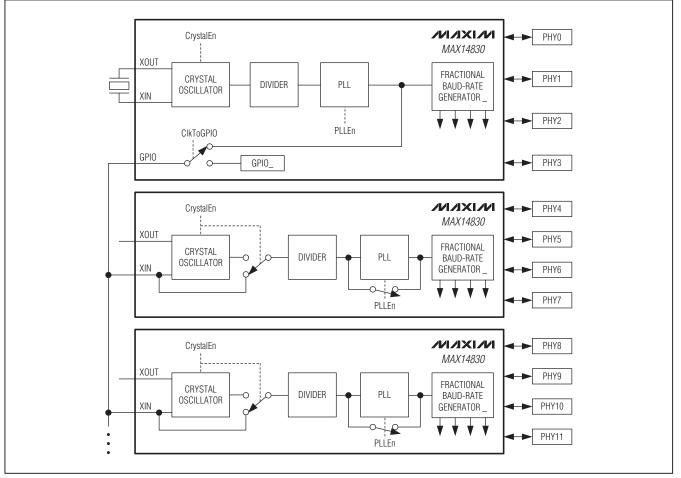

# **PLL and Predivider**

The internal predivider and PLL allow for a wide range of external clock frequencies and baud rates. The PLL can be configured to multiply the input clock rate by a factor of 6, 48, 96, or 144 through the PLLConfig register. The predivider, located between the input clock and the PLL, allows division of the input clock by a factor between 1 and 63 by writing to PLLConfig[5:0]. See the *PLLConfig* register description for more information.

Figure 7. Clock Selection Diagram

### **Fractional Baud-Rate Generators**

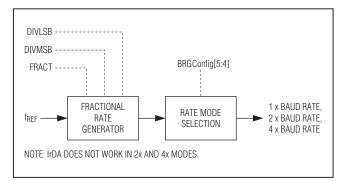

The internal fractional baud-rate generator provides a high degree of flexibility and high resolution in baudrate programming. The baud-rate generator has a 16-bit integer divisor and a 4-bit word for the fractional divisor. The fractional baud-rate generator can be used with the external crystal or clock source.

The integer and fractional divisors are calculated through the divisor, D:

$$D = \frac{t_{REF}}{16 \times BaudRate}$$

where fREF is the reference frequency input to the baudrate generator and D is the ideal divisor. In 2x and 4x rate modes, replace the divisor 16 by 8 or 4, respectively.

The integer divisor portion, DIV, of the divisor, D, is obtained by truncating D:

# DIV = TRUNC(D)

DIV can be a maximum of 16 bits wide and is programmed into the 2-byte-wide registers DIVMSB and DIVLSB. The minimum allowed value for DIVLSB is 1.

The fractional portion of the divisor, FRACT, is a 4-bit nibble, which is programmed into BRGConfig[3:0]. The maximum value is 15, allowing the divisor to be programmed with a resolution of 0.0625. FRACT is calculated as:

$FRACT = ROUND(16 \times (D-DIV)).$

The following is an example of calculating the divisor. It is based on a required baud rate of 190kbaud and a reference input frequency of 28.23MHz and default rate mode.

The ideal divisor is calculated as:

hence DIV = 9.

$$FRACT = ROUND(4.579) = 0x05$$

so that DIVMSB = 0x00, DIVLSB = 0x09, and BRGConfig[3:0] = 0x05.

The resulting actual baud rate can be calculated as:

$$BR_{ACTUAL} = \frac{f_{REF}}{16 \times D_{ACTUAL}}$$

For this example:  $D_{ACTUAL} = 9 + 5/16 = 9.313$ , where  $D_{ACTUAL} = DIV + (FRACT/16)$  and

BR<sub>ACTUAL</sub>= 28,230,000 / (16 x 9.3125) = 189,463.087 baud.

Thus the baud rate is within 0.28% of the ideal rate.

# 2x and 4x Rate Modes

To support higher baud rates than possible with standard (16x sampling) operation, the MAX14830 offers 2x and 4x rate modes. In this case, the reference clock rate only needs to be either 8x or 4x of the baud rate, respectively. In 4x mode only, the bits are only sampled once, at the midbit instant, instead of the usual three samples to determine the logic value of the bits. This reduces the tolerance to line noise on the received data. The 2x and 4x modes are selectable through BRGConfig[5:4]. Note that IrDA encoding and decoding does not operate in 2x and 4x modes.

When 2x rate mode is selected, the actual baud rate is twice the rate programmed into the baud-rate generator. If 4x rate mode is enabled, the actual baud rate on the line is quadruple that of the programmed baud rate (Figure 8).

Figure 8. 2x and 4x Baud Rates

Figure 9. GPIO\_ Clock Pulse Generator

### **Low-Frequency Timer**

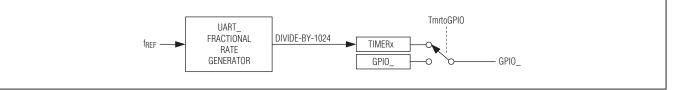

The general-purpose timer can be used to generate a low-frequency clock at a GPIO output and can, for example, be used to drive external LEDs. The low-frequency clock is a divided replica of a given UART baud-rate clock. The timer is internally routed to the GPIO\_ outputs when enabled in the TIMER2 register as follows:

- UARTO: GPIO1

- UART1: GPIO5

- UART2: GPIO9

- UART3: GPIO13

The clock pulses at the GPIOs are generated at a rate defined by the baud-rate generator and the timer divider (Figure 9). The baud-rate generator clock is divided by (1024 x TIMERx), where TIMERx is a 15-bit integer programmed into the TIMER1 and TIMER2 registers. The timer output is a 50% duty cycle clock.

# **UART Clock to GPIO**

The MAX14830 reference clock can be routed to the GPIO0, GPIO4, GPIO8, and/or GPIO12 outputs in case a synchronous high-frequency clock is needed by another device. Enable routing a UART clock to GPIO0, GPIO4, GPIO8, and/or GPIO12 in the TxSynch register. This output clock could, for example, be used to clock another UART device (Figure 29).

# **Multidrop Mode**