SCAS862D-NOVEMBER 2008-REVISED AUGUST 2011

## Five/Ten Output Clock Generator/Jitter Cleaner With Integrated Dual VCOs

Check for Samples: CDCE62005

## FEATURES

- Frequency Synthesizer With PLL/VCO and Partially Integrated Loop Filter.

- Fully Configurable Outputs Including Frequency, Output Format, and Output Skew.

- Smart Input Multiplexer Automatically Switches Between One of Three Reference Inputs.

- Multiple Operational Modes Include Clock Generation via Crystal, SERDES Startup Mode, Jitter Cleaning, and Oscillator Holdover Mode

- Integrated EEPROM Determines Device Configuration at Power-up

- Excellent Jitter Performance

- Integrated Frequency Synthesizer including

PLL, Multiple VCOs, and Loop Filter:

- Full Programmability Facilitates Phase Noise Performance Optimization Enabling Jitter Cleaner Mode.

- Programmable Charge Pump Gain and Loop Filter Settings

- Unique Dual-VCO Architecture Supports a Wide Tuning Range 1.750 GHz–2.356 GHz

- Universal Output Blocks Support up to 5 Differential, 10 Single-ended, or Combinations of Differential or Single-ended:

- 0.35 ps RMS (10 kHz to 20 MHz) Output Jitter Performance

- Low Output Phase Noise: -130 dBc/Hz at 1 MHz offset,  $F_c = 491.52 \text{ MHz}$

- Output Frequency Ranges From 4.25 MHz to 1.175 GHz in Synthesizer Mode

- Output Frequency up to 1.5 GHz in Fan-Out Mode

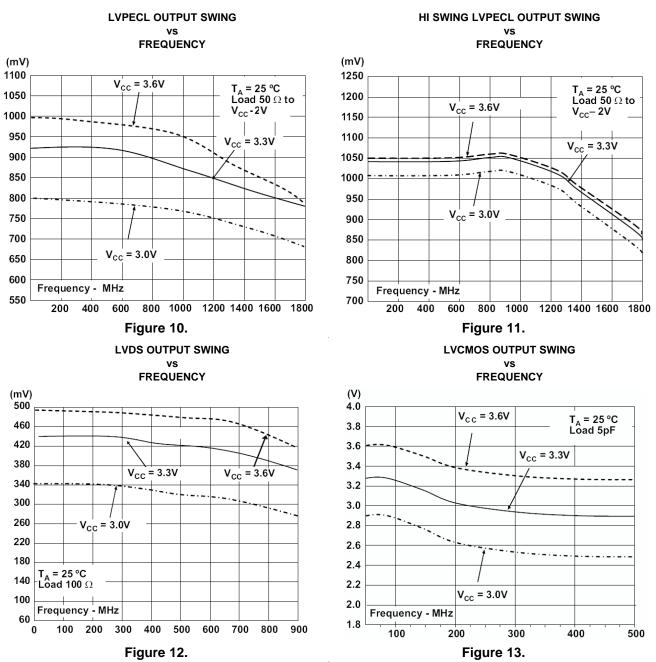

- LVPECL, LVDS, LVCMOS, and Special High Output Swing Modes

- Independent Output Dividers Support Divide Ratios from 1–80, Non-Continuous Values Supported

- Independent Coarse Skew Control on all Outputs, Coarse Skew Control Does Not Operate for Reference Input Frequencies < 1 MHz

- Flexible Inputs With Innovative Smart Multiplexer Feature:

- Two Universal Differential Inputs Accept Frequencies in the Range of 40 kHz to 1500 MHz (LVPECL), 800 MHz (LVDS), or 250 MHz (LVCMOS)

- One Auxiliary Input Accepts Crystals in the Range of 2 MHz–42 MHz

- Clock Generator Mode Using Crystal Input

- Smart Input Multiplexer can be Configured to Automatically Switch Between Highest Priority Clock Source Available Allowing for Fail-safe Operation and Holdover Modes

- Typical Power Consumption 1.7W (See Table 48) at 3.3V

- Integrated EEPROM Stores Default Settings; Therefore, The Device Can Power up in a Known, Predefined State

- Offered in QFN-48 Package

- ESD Protection Exceeds 2kV HBM

- Industrial Temperature Range –40°C to 85°C

## APPLICATIONS

- Data Converter and Data Aggregation Clocking

- Wireless Infrastructure

- Switches and Routers

- Medical Electronics

- Military and Aerospace

- Industrial

- Clock Generation and Jitter Cleaning

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

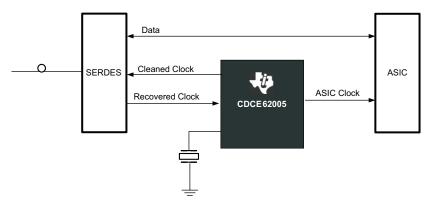

## DESCRIPTION

The CDCE62005 is a high performance clock generator and distributor featuring low output jitter, a high degree of configurability via a SPI interface, and programmable start up modes determined by on-chip EEPROM. Specifically tailored for clocking data converters and high-speed digital signals, the CDCE62005 achieves jitter performance well under 1 ps RMS<sup>(1)</sup>. It incorporates a synthesizer block with partially integrated loop filter, a clock distribution block including programmable output formats, and an input block featuring an innovative smart multiplexer. The clock distribution block includes five individually programmable outputs that can be configured to provide different combinations of output formats (LVPECL, LVDS, LVCMOS). Each output can also be programmed to a unique output frequency (up to 1.5 GHz<sup>(2)</sup>) and skew relationship via a programmable delay block. If all outputs are configured in single-ended mode (e.g., LVCMOS), the CDCE62005 supports up to ten outputs. Each output can select one of four clock sources to condition and distribute including any of the three clock inputs or the output of the frequency synthesizer. The input block includes two universal differential inputs which support frequencies in the range of 40 kHz to 500 MHz and an auxiliary input that can be configured to connect to an external crystal via an on chip oscillator block. The smart input multiplexer has two modes of operation, manual and automatic. In manual mode, the user selects the synthesizer reference via the SPI interface. In automatic mode, the input multiplexer will automatically select between the highest priority input clock available.

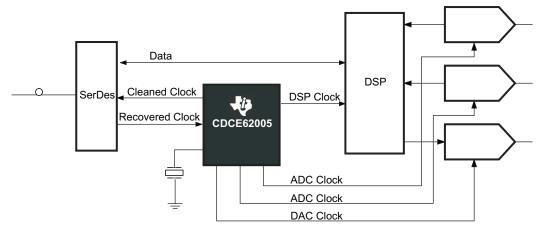

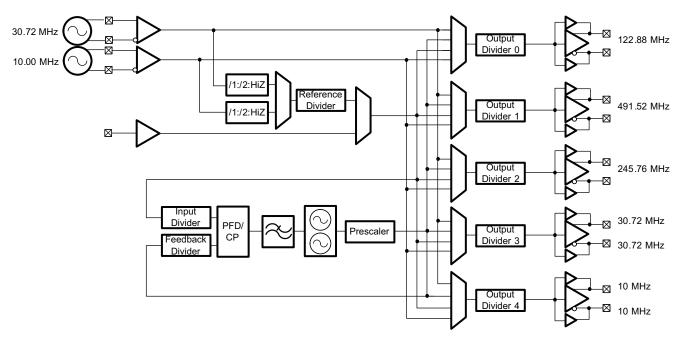

Figure 1. CDCE62005 Application Example

(1) 10 kHz to 20 MHz integration bandwidth.

(2) Frequency range depends on operational mode and output format selected.

www.ti.com

www.ti.com

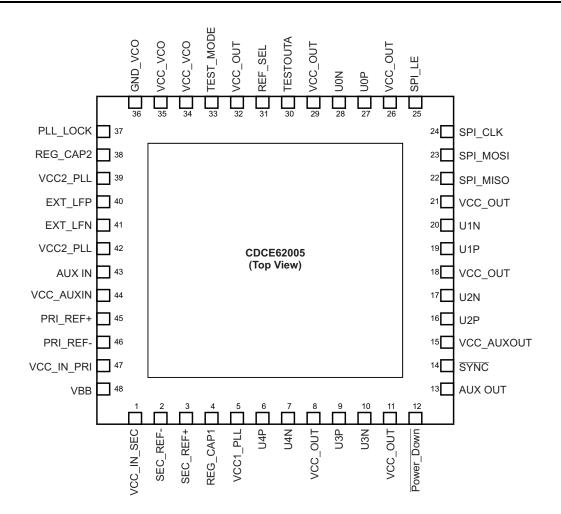

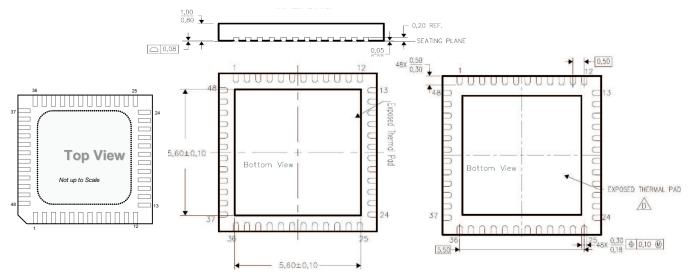

### **DEVICE INFORMATION**

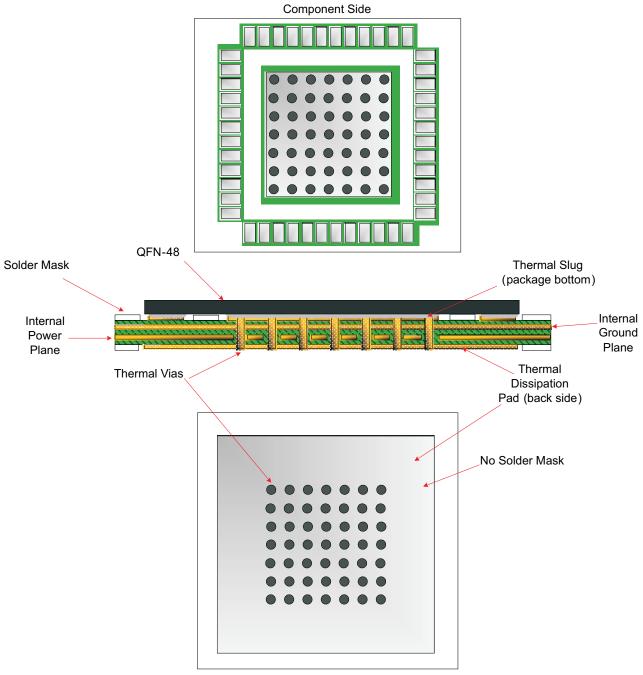

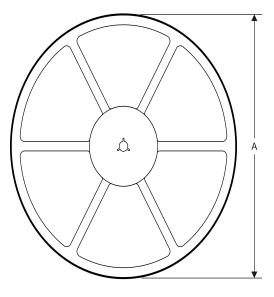

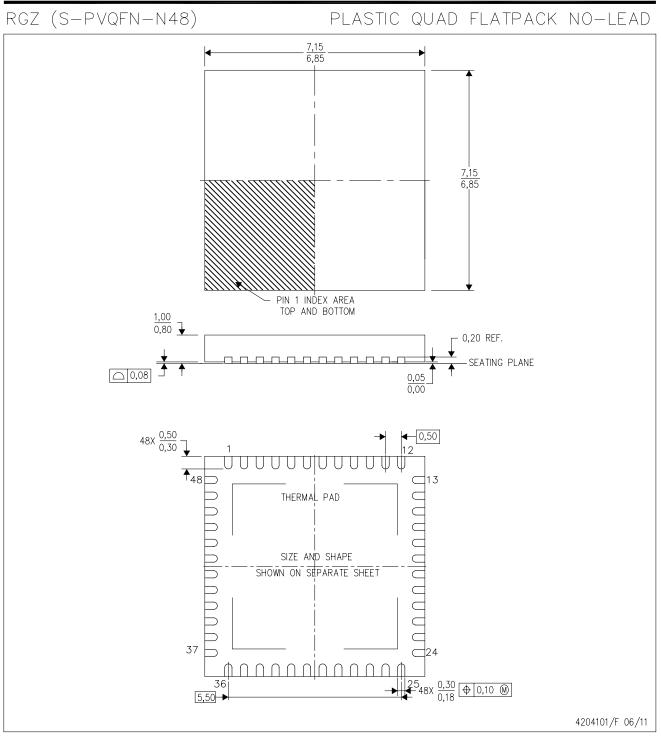

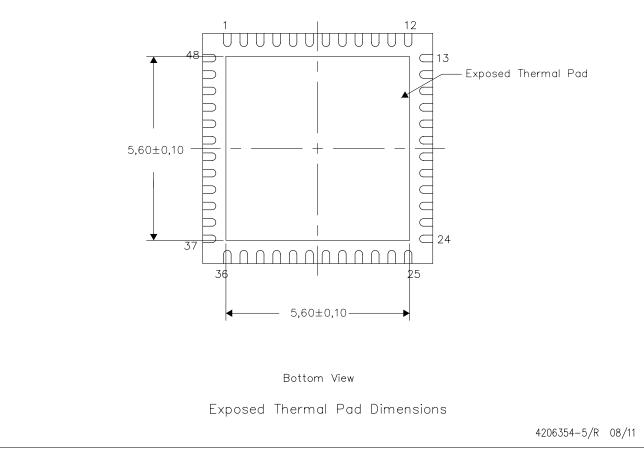

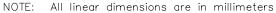

### PACKAGE

The CDCE62005 is packaged in a 48-Pin Plastic Quad Flatpack Package with enhanced bottom thermal pad for heat dissipation. The Texas Instruments Package Designator is: **RGZ (S-PQFP-N48)**

Figure 2. 48-Pin QFN Package Outline

| PIN | FU | NCT | ION | IS <sup>(1)</sup> |

|-----|----|-----|-----|-------------------|

|-----|----|-----|-----|-------------------|

| PIN TYPE   |                                    | TYPE     | DECODIDION                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------|------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME       | QFN                                | ITPE     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VCC_OUT    | 8, 11, 18,<br>21,<br>26, 29,<br>32 | Power    | 3.3V Supply for the Output Buffers and Output Dividers                                                                                                                                                                                                                                                                                                                                                                                                  |

| VCC_AUXOUT | 15                                 | Power    | 3.3V to Power the AUX_OUT circuitry                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VCC1_PLL   | 5                                  | A. Power | 3.3V PLL Supply Voltage for the PLL circuitry. (Filter Required)                                                                                                                                                                                                                                                                                                                                                                                        |

| VCC2_PLL   | 39, 42                             | A. Power | 3.3V PLL Supply Voltage for the PLL circuitry. (Filter Required)                                                                                                                                                                                                                                                                                                                                                                                        |

| VCC_VCO    | 34, 35                             | A. Power | 3.3V VCO Input Buffer and Circuitry Supply Voltage. (Filter Required)                                                                                                                                                                                                                                                                                                                                                                                   |

| VCC_IN_PRI | 47                                 | A. Power | 3.3V References Input Buffer and Circuitry Supply Voltage.                                                                                                                                                                                                                                                                                                                                                                                              |

| VCC_IN_SEC | 1                                  | A. Power | 3.3V References Input Buffer and Circuitry Supply Voltage.                                                                                                                                                                                                                                                                                                                                                                                              |

| VCC_AUXIN  | 44                                 | A. Power | 3.3V Crystal Oscillator Input Circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                |

| GND_VCO    | 36                                 | Ground   | Ground that connects to VCO Ground. (VCO_GND is shorted to GND)                                                                                                                                                                                                                                                                                                                                                                                         |

| GND        | PAD                                | Ground   | Ground is on Thermal PAD. See Layout recommendation                                                                                                                                                                                                                                                                                                                                                                                                     |

| SPI_MISO   | 22                                 | 0        | 3-state LVCMOS Output that is enabled when SPI_LE is asserted low. It is the serial Data Output to the SPI bus interface                                                                                                                                                                                                                                                                                                                                |

| SPI_LE     | 25                                 | I        | LVCMOS input, control Latch Enable for Serial Programmable Interface (SPI), with Hysteresis in SPI Mode. The input has an internal 150-k $\Omega$ pull-up resistor if left unconnected it will default to logic level "1". The SPI_LE status also impacts whether the device loads the EEPROM into the device registers at power up. SPI_LE has to be logic "1" before the Power_Down pin toggles low-to-high in order for the EEPROM to load properly. |

| SPI_CLK    | 24                                 | I        | LVCMOS input, serial Control Clock Input for the SPI bus interface, with Hysteresis. The input has an internal $150 \cdot k\Omega$ pull-up resistor if left unconnected it will default to logic level "1".                                                                                                                                                                                                                                             |

| SPI_MOSI   | 23                                 | I        | LVCMOS input, Master Out Slave In as a serial Control Data Input to <b>CDCE62005</b> for the SPI bus interface. The input has an internal 150- $k\Omega$ pull-up resistor if left unconnected it will default to logic level "1".                                                                                                                                                                                                                       |

(1) Note: The internal memory (EEPROM and RAM) are sourced from various power pins. All VCC connections must be powered for proper functionality of the device.

#### SCAS862D - NOVEMBER 2008 - REVISED AUGUST 2011

## PIN FUNCTIONS<sup>(1)</sup> (continued)

| PIN                                                 |                                            |        | DECODIDEION                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|-----------------------------------------------------|--------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                                                | QFN                                        | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| TEST_MODE                                           | 33                                         | I      | This pin should be tied high or left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| REF_SEL                                             | 31                                         | I      | If Auto Reference Select Mode is OFF this Pin acts as External Input Reference Select Pin;<br>The REF_SEL signal selects one of the two input clocks:<br>REF_SEL [1]: PRI_REF is selected; REF_SEL [0]: SEC_REF is selected;<br>The input has an internal 150-k $\Omega$ pull-up resistor if left unconnected it will default to logic level<br>"1". If Auto Reference Select Mode in ON (e.g. EECLKSEL bit (Register 5 Bit 5) is "1"), then<br>REF_SEL pin input setting is ignored. |  |  |

| Power_Down                                          | 12                                         | I      | Active Low. Power down mode can be activated via this pin. See Table 15 for more details. The input has an internal $150-k\Omega$ pull-up resistor if left unconnected it will default to logic level "1". SPI_LE has to be HIGH in order for the rising edge of Power_Down signal to load the EEPROM.                                                                                                                                                                                |  |  |

| SYNC                                                | 14                                         | I      | Active Low. Sync mode can be activated via this pin. See Table 15 for more details. The input has an internal $150-k\Omega$ , pull-up resistor if left unconnected it will default to logic level "1".                                                                                                                                                                                                                                                                                |  |  |

| AUX IN                                              | 43                                         | I      | Auxiliary Input is a single ended input including an on-board oscillator circuit so that a crystal may be connected.                                                                                                                                                                                                                                                                                                                                                                  |  |  |

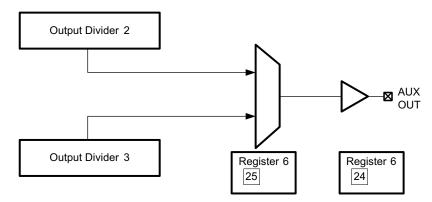

| AUX OUT                                             | 13                                         | 0      | Auxiliary Output LVCMOS level that can be programmed via SPI interface to be driven by<br>Output 2 or Output 3.                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| PRI_REF+                                            | 45                                         | I      | Universal Input Buffer (LVPECL, LVDS, LVCMOS) positive input for the Primary Reference Clock.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| PRI_REF-                                            | 46                                         | I      | Universal Input Buffer (LVPECL, LVDS) negative input for the Primary Reference Clock. In case of LVCMOS input on PRI_REF+, connect this pin through 1 k $\Omega$ resistor to GND.                                                                                                                                                                                                                                                                                                     |  |  |

| SEC_REF+                                            | 3                                          | I      | Universal Input Buffer (LVPECL, LVDS, LVCMOS) positive input for the Secondary Reference Clock.                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| SEC_REF-                                            | 2                                          | I      | Universal Input Buffer (LVPECL, LVDS,) negative input for the Secondary Reference Clock. In case of LVCMOS input on SEC_REF+, connect this pin through 1 k $\Omega$ resistor to GND.                                                                                                                                                                                                                                                                                                  |  |  |

| TESTOUTA                                            | 30                                         | Analog | Reserved. Pull Down to GND Via a $1k\Omega$ Resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| REG_CAP1                                            | 4                                          | Analog | Capacitor for the internal Regulator. Connect to a 10uF Capacitor (X5R or X7R)                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| REG_CAP2                                            | 38                                         | Analog | Capacitor for the internal Regulator. Connect to a 10uF Capacitor (X5R or X7R)                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| VBB                                                 | 48                                         | Analog | Capacitor for the internal termination Voltage. Connect to a 1uF Capacitor (X5R or X7R)                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

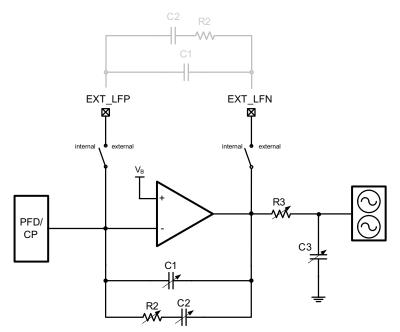

| EXT_LFP                                             | 40                                         | Analog | External Loop Filter Input Positive                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| EXT_LFN                                             | 41                                         | Analog | External Loop Filter Input Negative.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

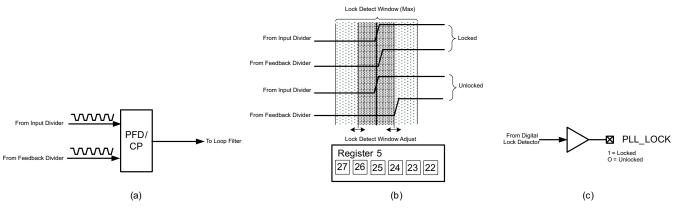

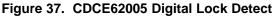

| PLL_LOCK                                            | 37                                         | 0      | Output that indicates PLL Lock Status. See Figure 37.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| U0P:U0N<br>U1P:U1N<br>U2P:U2N<br>U3P:U3N<br>U4P:U4N | 27, 28<br>19, 20<br>16,17<br>9, 10<br>6, 7 | 0      | The Main outputs of <b>CDCE62005</b> are user definable and can be any combination of up to 5 LVPECL outputs, 5 LVDS outputs or up to 10 LVCMOS outputs. The outputs are selectable via SPI interface. The power-up setting is EEPROM configurable.                                                                                                                                                                                                                                   |  |  |

www.ti.com

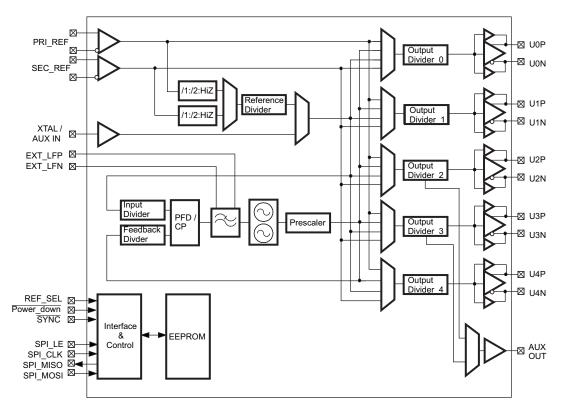

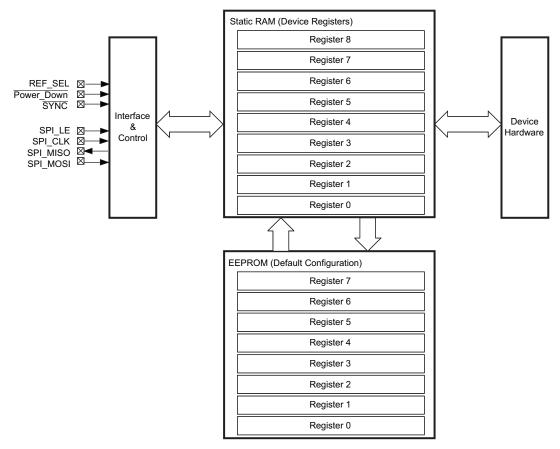

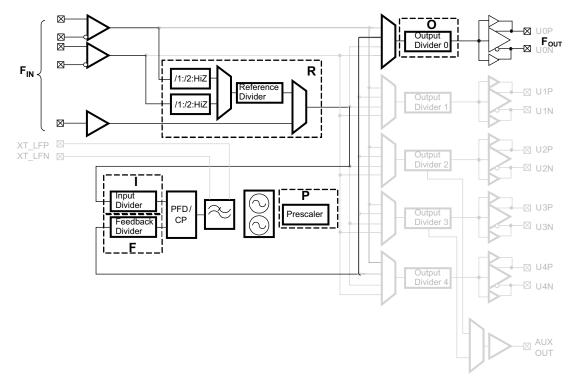

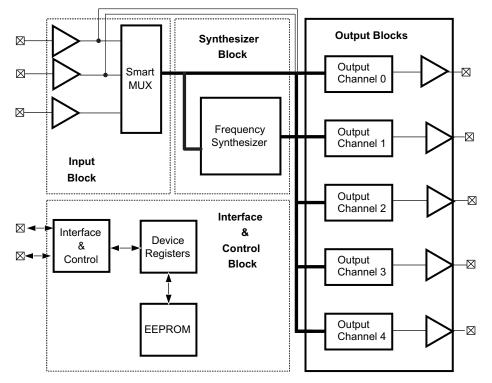

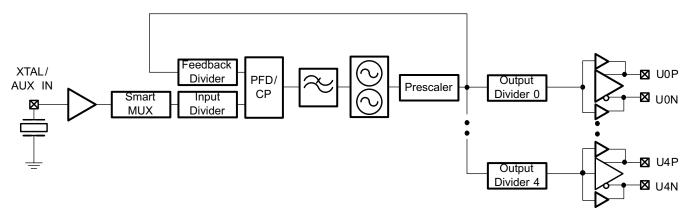

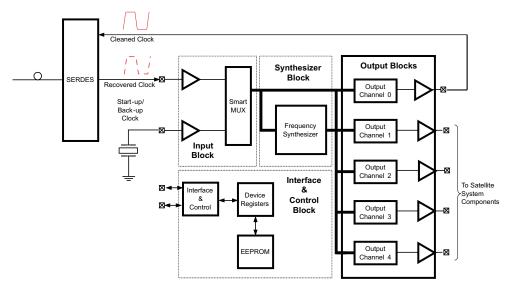

Figure 3. CDCE62005 Block Diagram

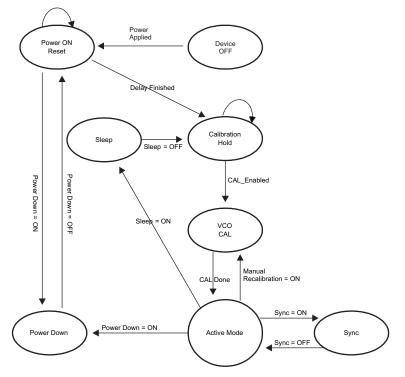

The CDCE62005 comprises of four primary blocks: the interface and control block, the input block, the output block, and the synthesizer block. In order to determine which settings are appropriate for any specific combination of input/output frequencies, a basic understanding of these blocks is required. The interface and control block determines the state of the CDCE62005 at power-up based on the contents of the on-chip EEPROM. In addition to the EEPROM, the SPI port is available to configure the CDCE62005 by writing directly to the device registers after power-up. The input block selects which of the three input ports is available for use by the synthesizer block and buffers all clock inputs. The output block provides five separate clock channels that are fully programmable and configurable to select and condition one of four internal clock sources. The synthesizer block multiplies and filters the input clock selected by the input block.

#### NOTE

This Section of the data sheet provides a high-level description of the features of the CDCE62005 for purpose of understanding its capabilities. For a complete description of device registers and I/O, please refer to the Device Configuration Section.

#### www.ti.com

#### **Interface and Control Block**

The CDCE62005 is a highly flexible and configurable architecture and as such contains a number of registers so that the user may specify device operation. The contents of nine 28-bit wide registers implemented in static RAM determine device configuration at all times. On power-up, the CDCE62005 copies the contents of the EEPROM into the RAM and the device begins operation based on the default configuration stored in the EEPROM. Systems that do not have a host system to communicate with the CDCE62005 use this method for device configuration. The CDCE62005 provides the ability to lock the EEPROM; enabling the designer to implement a fault tolerant design. After power-up, the host system may overwrite the contents of the RAM via the SPI (Serial Peripheral Interface) port. This enables the configuration and reconfiguration of the CDCE62005 during system operation. Finally, the device offers the ability to copy the contents of the RAM into EEPROM, if the EEPROM is unlocked.

Figure 4. CDCE62005 Interface and Control Block

www.ti.com

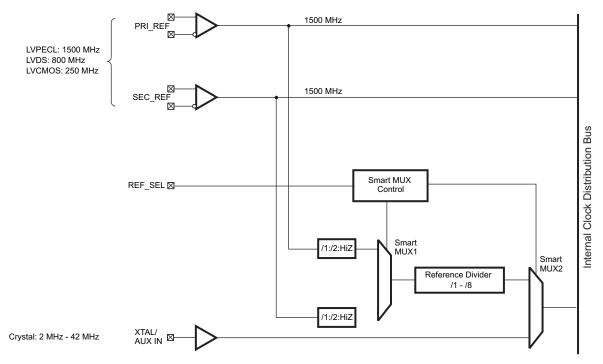

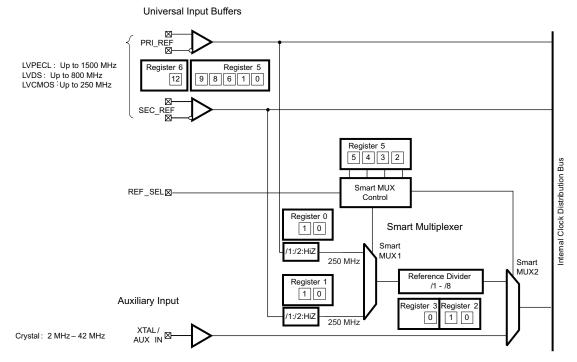

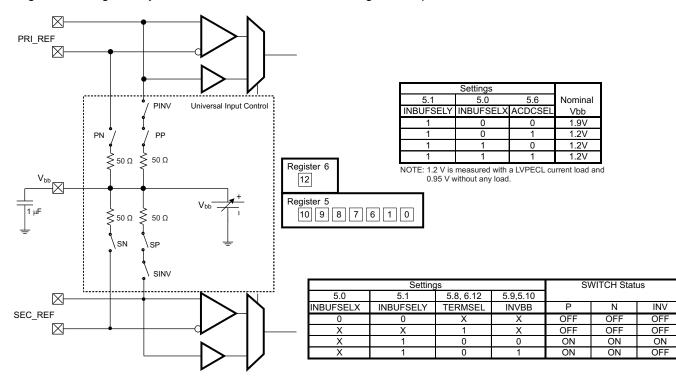

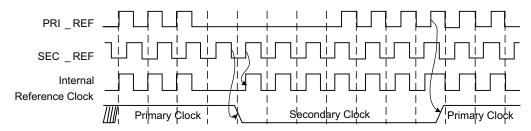

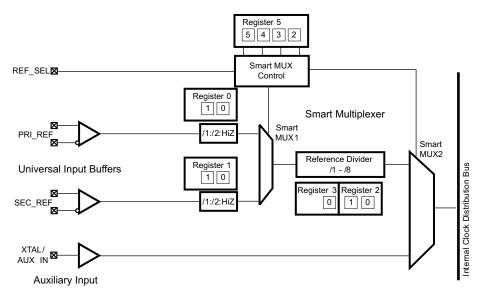

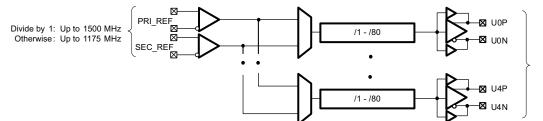

#### **Input Block**

The Input Block includes a pair of Universal Input Buffers and an Auxiliary Input. The Input Block buffers the incoming signals and facilitates signal routing to the Internal Clock Distribution bus and the Synthesizer Block via the smart multiplexer (called the Smart MUX). The Internal Clock Distribution Bus connects to all output blocks discussed in the next section. Therefore, a clock signal present on the Internal Clock Distribution bus can appear on any or all of the device outputs. The CDCE62005 routes the PRI\_REF and SEC\_REF inputs directly to the Internal Clock Distribution Bus. Additionally, it can divide these signals via the dividers present on the inputs and output of the first stage of the Smart MUX.

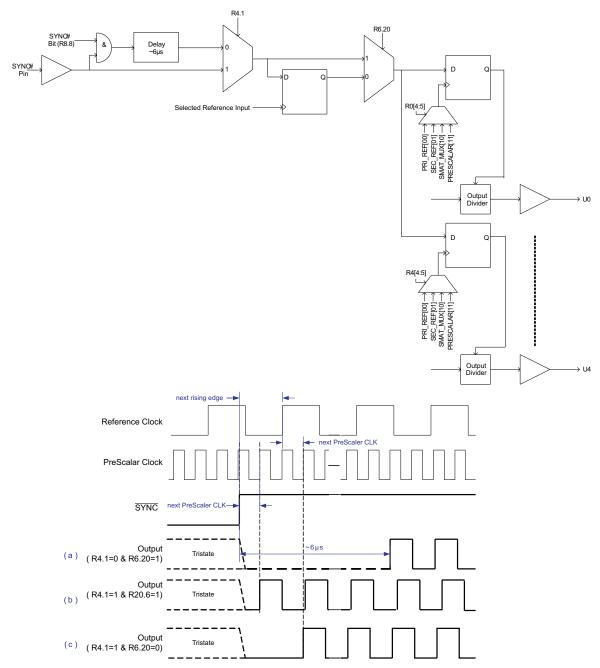

Figure 5. CDCE62005 Input Block

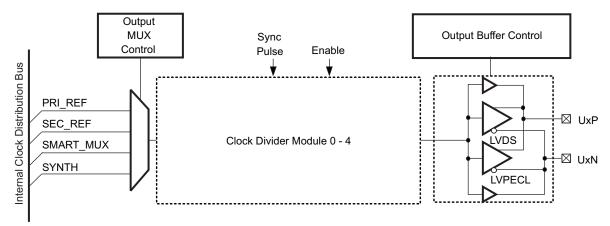

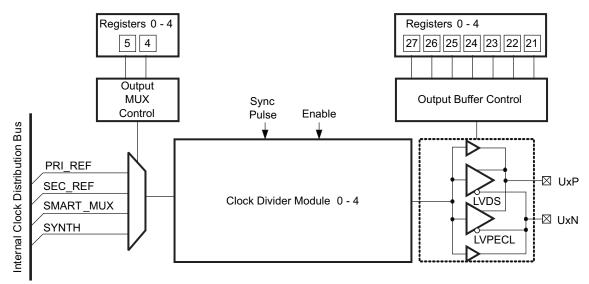

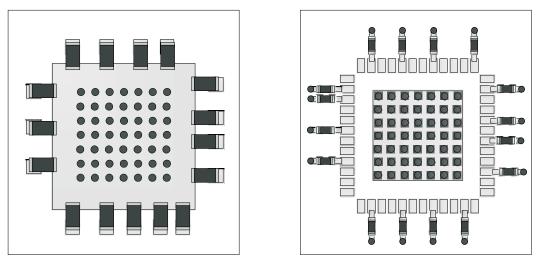

#### **Output Block**

Each of the five identical output blocks incorporates an output multiplexer, a clock divider module, and a universal output array as shown.

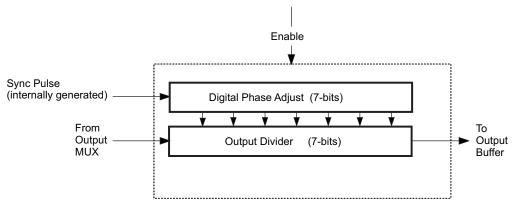

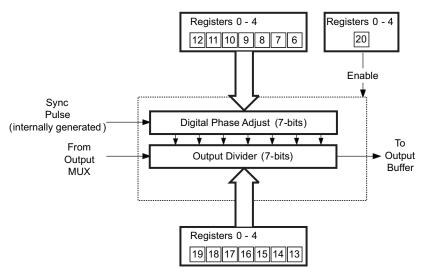

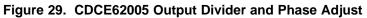

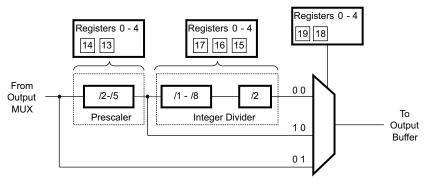

#### Clock Divider Module 0-4

The following shows a simplified version of a Clock Divider Module (CDM). If an individual clock output channel is not used, then the user should disable the CDM and Output Buffer for the unused channel to save device power. Each channel includes two 7-bit registers to control the divide ratio used and the clock phase for each output. The output divider supports divide ratios from divide by 1 (bypass the divider) to divide by 80; the divider does not support all integer values between 1 and 80. Refer to Table 24 for a complete list of divide ratios supported.

Figure 7. CDCE62005 Output Divider Module (1 of 5)

www.ti.com

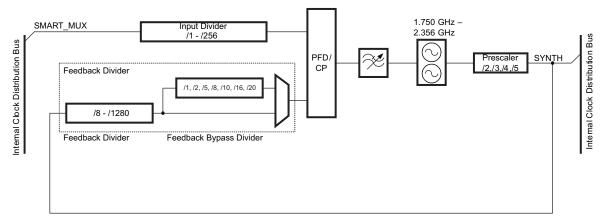

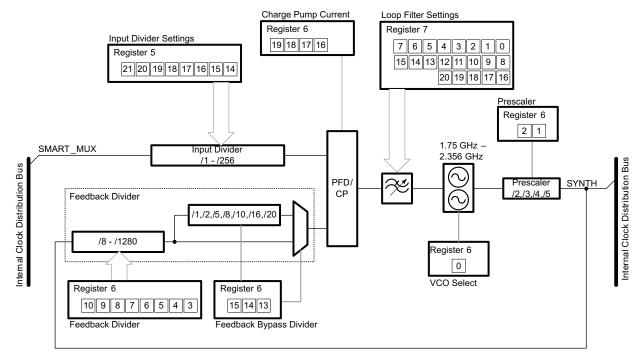

### Synthesizer Block

Figure 8 presents a high-level overview of the Synthesizer Block on the CDCE62005.

Figure 8. CDCE62005 Synthesizer Block

www.ti.com

### COMPUTING THE OUTPUT FREQUENCY

Figure 9 presents the block diagram of the CDCE62005 in synthesizer mode highlighting the clock path for a single output. It also identifies the following regions containing dividers comprising the complete clock path

- R: Includes the cumulative divider values of all dividers included from the Input Ports to the output of the Smart Multiplexer (see Input Block for more details)

- O: The output divider value (see Output Block for more details)

- I: The input divider value (see Synthesizer Block for more details)

- P: The Prescaler divider value (see Synthesizer Block of more details)

- F: The cumulative divider value of all dividers falling within the feedback divider (see Synthesizer Block for more details)

Figure 9. CDCE62005 Clock Path – Synthesizer Mode

With respect to Figure 9, any output frequency generated by the CDCE62005 relates to the input frequency connected to the Synthesizer Block by Equation 1.

$$F_{OUT} = F_{IN} \times \frac{F}{R \times I \times O}$$

(1)

Equation 1 holds true when subject to the following constraints:

1.750 Ghz < O x P x F<sub>OUT</sub>< 2.356 GHz

And the comparison frequency  $F_{COMP}$ ,

40 kHz  $\leq$  F<sub>COMP</sub> < 40 MHz

Where:

$F_{COMP} = \frac{F_{IN}}{R \times I}$

Note: This device cannot output the frequencies between 785 MHz to 875 MHz

(3)

(2)

www.ti.com

## **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                                                                                  | VALUE             | UNIT |

|------------------|----------------------------------------------------------------------------------|-------------------|------|

| V <sub>CC</sub>  | Supply voltage range <sup>(2)</sup>                                              | -0.5 to 4.6       | V    |

| VI               | Input voltage range <sup>(3)</sup>                                               | -0.5 to VCC + 0.5 | V    |

| Vo               | Output voltage range <sup>(3)</sup>                                              | -0.5 to VCC + 0.5 | V    |

|                  | Input Current ( $V_1 < 0$ , $V_1 > V_{CC}$ )                                     | ±20               | mA   |

|                  | Output current for LVPECL/LVCMOS Outputs (0 < V <sub>O</sub> < V <sub>CC</sub> ) | ±50               | mA   |

| TJ               | Maximum junction temperature                                                     | 125               | °C   |

| T <sub>stg</sub> | Storage temperature range                                                        | -65 to 150        | °C   |

(1) Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated *under recommended operating conditions* is not implied. Exposure to absolute–maximum–rated conditions for extended periods may affect device reliability.

(2) All supply voltages have to be supplied simultaneously.

(3) The input and output negative voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

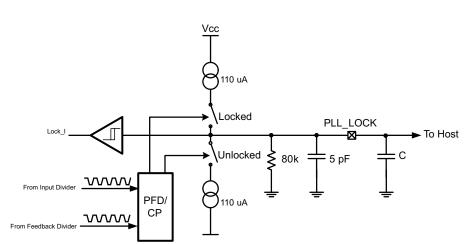

## THERMAL CHARACTERISTICS

Package Thermal Resistance for QFN (RGZ) Package (1) (2)

| AIRFLOW (Ifm) |                                         | θ <sub>JP</sub> (°C/W) <sup>(3)</sup> | θ <sub>JA</sub> (°C/W) |

|---------------|-----------------------------------------|---------------------------------------|------------------------|

| 0             | JEDEC Compliant Board (6X6 VIAs on PAD) | 2                                     | 28.9                   |

| 100           | JEDEC Compliant Board (6X6 VIAs on PAD) | 2                                     | 20.4                   |

| 0             | Recommended Layout (7X7 VIAs on PAD)    | 2                                     | 27.3                   |

| 100           | Recommended Layout (7X7 VIAs on PAD)    | 2                                     | 20.3                   |

(1) The package thermal impedance is calculated in accordance with JESD 51 and JEDEC2S2P (high-k board).

(2) Connected to GND with 36 thermal vias (0,3 mm diameter).

(3)  $\theta_{JP}$  (Junction – Pad) is used for the QFN Package, because the main heat flow is from the Junction to the GND-Pad of the QFN.

#### SCAS862D-NOVEMBER 2008-REVISED AUGUST 2011

## ELECTRICAL CHARACTERISTICS OPERATING CONDITIONS

recommended operating conditions for the CDCE62005 device for under the specified Industrial temperature range of  $-40^{\circ}$ C to  $85^{\circ}$ C

|                                                                                            | PARAMETER                                                          | TEST CONDITIONS                                                                                                    | MIN                   | TYP  | MAX                  | UNIT |

|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------|------|----------------------|------|

| POWER S                                                                                    | UPPLY                                                              |                                                                                                                    |                       |      |                      |      |

| V <sub>CC</sub>                                                                            | Supply voltage                                                     |                                                                                                                    | 3                     | 3.3  | 3.6                  | V    |

| V <sub>CC_PLL</sub> ,<br>V <sub>CC_IN</sub> ,<br>V <sub>CC_VCO</sub> ,<br>V <sub>CCA</sub> | Analog supply voltage                                              |                                                                                                                    | 3                     | 3.3  | 3.6                  |      |

| PLVPECL                                                                                    | REF at 30.72,MHz, Outputs are LVPECL                               | Output 1 = 491.52 MHz                                                                                              |                       | 1.9  |                      | W    |

| P <sub>LVDS</sub>                                                                          | REF at 30.72 MHz, Outputs are LVDS                                 | Output 2 = 245.76 MHz                                                                                              |                       | 1.65 |                      | W    |

| P <sub>LVCMOS</sub>                                                                        | REF at 30.72 MHz, Outputs are LVCMOS                               | Output 3 = 122.88 MHz<br>Output 4 = 61.44 MHz<br>Output 5 = 30.72 MHz<br>In case of LVCMOS<br>Output1 = 245.76 MHz |                       | 1.8  |                      | W    |

| P <sub>OFF</sub>                                                                           | REF at 30.72 MHz                                                   | Dividers are disabled. Outputs are disabled.                                                                       |                       | 0.75 |                      | W    |

| P <sub>PD</sub>                                                                            |                                                                    | Device is powered down                                                                                             |                       | 20   |                      | mW   |

| DIFFEREN                                                                                   | ITIAL INPUT MODE (PRI_REF, SEC_REF)                                |                                                                                                                    |                       |      |                      |      |

| V <sub>IN</sub>                                                                            | Differential input amplitude (V <sub>IN</sub> – V <sub>/IN</sub> ) |                                                                                                                    | 0.1                   |      | 1.3                  | V    |

| V <sub>IC</sub>                                                                            | Common-mode input voltage                                          |                                                                                                                    | 1.0                   |      | V <sub>CC</sub> -0.3 | V    |

| I <sub>IH</sub>                                                                            | Differential input current high (no internal termination)          | $V_{I} = V_{CC}, V_{CC} = 3.6 V$                                                                                   |                       |      | 20                   | μA   |

| IIL                                                                                        | Differential input current low (no internal termination)           | $V_{I} = 0 V, V_{CC} = 3.6 V$                                                                                      | -20                   |      | 20                   | μA   |

|                                                                                            | Input Capacitance on PRI_REF, SEC_REF                              |                                                                                                                    |                       | 3    |                      | pF   |

| CRYSTAL                                                                                    | INPUT SPECIFICATIONS                                               |                                                                                                                    |                       |      |                      |      |

|                                                                                            | On-chip load capacitance                                           |                                                                                                                    | 8                     |      | 10                   | pF   |

|                                                                                            | Equivalent series resistance (ESR)                                 |                                                                                                                    |                       |      | 50                   | Ω    |

| LVCMOS                                                                                     | INPUT MODE (SPI_CLK, SPI_MOSI, SPI_LE                              | , Power_Down, SYNC, REF_SEL, PRI_R                                                                                 | EF, SEC_REF           | )    |                      |      |

|                                                                                            | Low-level input voltage LVCMOS,                                    |                                                                                                                    | 0                     |      | $0.3 \times V_{CC}$  | V    |

|                                                                                            | High-level input voltage LVCMOS                                    |                                                                                                                    | $0.7 	ext{ x V}_{CC}$ |      | V <sub>CC</sub>      | V    |

| V <sub>IK</sub>                                                                            | LVCMOS input clamp voltage                                         | $V_{CC} = 3 \text{ V}, \text{ I}_{I} = -18 \text{ mA}$                                                             |                       |      | -1.2                 | V    |

| I <sub>IH</sub>                                                                            | LVCMOS input current                                               | $V_{I} = V_{CC}, V_{CC} = 3.6 \text{ V}$                                                                           |                       |      | 20                   | μA   |

| I <sub>IL</sub>                                                                            | LVCMOS input (Except PRI_REF and SEC_REF)                          | $V_{I} = 0 V, V_{CC} = 3.6 V$                                                                                      | -10                   |      | -40                  | μA   |

| IIL                                                                                        | LVCMOS input (PRI_REF and SEC_REF)                                 | $V_{I} = 0 V, V_{CC} = 3.6 V$                                                                                      | -10                   |      | 10                   | μA   |

| CI                                                                                         | Input capacitance                                                  | $V_{I} = 0 V \text{ or } V_{CC}$                                                                                   |                       | 3    |                      | pF   |

## ELECTRICAL CHARACTERISTICS OPERATING CONDITIONS (Continued)

recommended operating conditions for the CDCE62005 device for under the specified Industrial temperature range of  $-40^{\circ}$ C to  $85^{\circ}$ C

|                    | PARAMETER                                    | TEST                                 | CONDITIONS                | MIN                  | TYP <sup>(1)</sup> | MAX | UNIT   |

|--------------------|----------------------------------------------|--------------------------------------|---------------------------|----------------------|--------------------|-----|--------|

| SPI OUT            | FPUT (MISO) / PLL_LOCK OUTPUT                |                                      |                           |                      |                    |     |        |

| I <sub>OH</sub>    | High-level output current                    | V <sub>CC</sub> = 3.3 V,             | V <sub>O</sub> = 1.65 V   |                      | -30                |     | mA     |

| I <sub>OL</sub>    | Low-level output current                     | V <sub>CC</sub> = 3.3 V,             | V <sub>O</sub> = 1.65 V   |                      | 33                 |     | mA     |

| V <sub>OH</sub>    | High-level output voltage for LVCMOS outputs | V <sub>CC</sub> = 3 V,               | I <sub>OH</sub> = −100 μA | V <sub>CC</sub> -0.5 |                    |     | V      |

| V <sub>OL</sub>    | Low-level output voltage for LVCMOS outputs  | V <sub>CC</sub> = 3 V,               | I <sub>OL</sub> = 100 μA  |                      |                    | 0.3 | V      |

| Co                 | Output capacitance on MISO                   | VCC = 3.3 V; V                       | O = 0 V or VCC            |                      | 3                  |     | pF     |

| I <sub>OZH</sub>   |                                              | $V_{O} = V_{CC}$                     | $V_{O} = V_{CC}$          |                      | 5                  |     |        |

| I <sub>OZL</sub>   | 3-state output current                       | $V_0 = 0$ V                          |                           |                      | -5                 |     | μA     |

| EEPRO              | M                                            |                                      |                           |                      |                    |     |        |

| EEcy               | Programming cycle of EEPROM                  |                                      |                           | 100                  | 1000               |     | Cycles |

| EEret              | Data retention                               |                                      |                           | 10                   |                    |     | Years  |

| VBB                |                                              | 1                                    |                           |                      |                    |     |        |

| VBB                | Termination voltage for reference inputs.    | $I_{BB} = -0.2 \text{ mA},$ setting. | Depending on the          | 0.9                  |                    | 1.9 | V      |

| INPUT E            | BUFFERS INTERNAL TERMINATION RESISTORS       | (PRI_REF and                         | SEC_REF)                  |                      |                    |     |        |

|                    | Termination resistance                       | Single ended                         |                           |                      | 50                 |     | Ω      |

| PHASE              | DETECTOR                                     | -                                    |                           | ¥                    |                    |     |        |

| f <sub>CPmax</sub> | Charge pump frequency                        |                                      |                           | 0.04                 |                    | 40  | MHz    |

(1) All typical values are at V<sub>CC</sub> = 3.3 V, temperature =  $25^{\circ}C$

www.ti.com

STRUMENTS

**EXAS**

www.ti.com

# ELECTRICAL CHARACTERISTICS OPERATING CONDITIONS (Continued)

recommended operating conditions for the **CDCE62005** device for under the specified Industrial temperature range of -40°C to 85°C

|                                             | PARAMETER                                                | TEST                                        | CONDITIONS                                            | MIN                  | TYP <sup>(1)</sup> | MAX | UNIT |

|---------------------------------------------|----------------------------------------------------------|---------------------------------------------|-------------------------------------------------------|----------------------|--------------------|-----|------|

| LVCMOS                                      | SOUTPUT / AUXILIARY OUTPUT                               | i.                                          |                                                       |                      |                    |     |      |

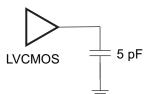

| f <sub>clk</sub>                            | Output frequency, see Figure Below                       | Load = 5 pF to GN                           | D                                                     | 0                    |                    | 250 | MHz  |

| V <sub>OH</sub>                             | High-level output voltage for LVCMOS<br>outputs          | $V_{CC}$ = min to max                       | I <sub>OH</sub> = −100 μA                             | V <sub>CC</sub> -0.5 |                    |     |      |

| V <sub>OL</sub>                             | Low-level output voltage for LVCMOS outputs              | $V_{CC}$ = min to max                       | I <sub>OL</sub> =100 μA                               |                      |                    | 0.3 | V    |

| I <sub>OH</sub>                             | High-level output current                                | $V_{CC} = 3.3 V$                            | V <sub>O</sub> = 1.65 V                               |                      | -30                |     | mA   |

| I <sub>OL</sub>                             | Low-level output current                                 | V <sub>CC</sub> = 3.3 V                     | V <sub>O</sub> = 1.65 V                               |                      | 33                 |     | mA   |

| t <sub>pho</sub>                            | Reference (PRI_REF or SEC_REF) to<br>Output Phase offset | Outputs are set to at 30.72 MHz             | Outputs are set to 122.88 MHz, Reference at 30.72 MHz |                      | 0.35               |     | ns   |

| t <sub>pd(LH)∕</sub><br>t <sub>pd(HL)</sub> | Propagation delay from PRI_REF or<br>SEC_REF to Outputs  | Crosspoint to V <sub>CC</sub> /2            | 2, Bypass Mode                                        |                      | 4                  |     | ns   |

| t <sub>sk(o)</sub>                          | Skew, output to output For Y0 to Y4                      | All Outputs set at 2<br>200 MHz             | 00 MHz, Reference =                                   |                      | 75                 |     | ps   |

| Co                                          | Output capacitance on Y0 to Y4                           | $V_{CC} = 3.3 \text{ V}; \text{ V}_{O} = 0$ | 0 V or V <sub>CC</sub>                                |                      | 5                  |     | pF   |

| I <sub>OZH</sub>                            |                                                          | $V_{O} = V_{CC}$                            |                                                       |                      | 5                  |     | μA   |

| I <sub>OZL</sub>                            | <ul> <li>3-State LVCMOS output current</li> </ul>        | $V_0 = 0 V$                                 |                                                       |                      | -5                 |     | μA   |

| I <sub>OPDH</sub>                           | Dever Deve extruit extremt                               | $V_{O} = V_{CC}$                            |                                                       |                      |                    | 25  | μA   |

| I <sub>OPDL</sub>                           | Power Down output current                                | $V_{O} = 0 V$                               |                                                       |                      |                    | 5   | μA   |

|                                             | Duty cycle LVCMOS                                        |                                             |                                                       | 45%                  |                    | 55% |      |

| t <sub>slew-rate</sub>                      | Output rise/fall slew rate                               |                                             |                                                       | 3.6                  | 5.2                |     | V/ns |

(1) All typical values are at  $V_{CC} = 3.3$  V, temperature =  $25^{\circ}C$

## ELECTRICAL CHARACTERISTICS OPERATING CONDITIONS (Continued) <sup>(1)</sup>

recommended operating conditions for the CDCE62005 device for under the specified Industrial temperature range of -40°C to 85°C

|                                   | PARAMETER                                               | TEST CONDITIONS                                                                                                      | MIN | TYP <sup>(2)</sup> | MAX | UNIT |

|-----------------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----|--------------------|-----|------|

| LVDS OUTP                         | UT                                                      |                                                                                                                      | 1   |                    |     |      |

| f <sub>clk</sub>                  | Output frequency                                        | Configuration Load                                                                                                   | 0   |                    | 800 | MHz  |

| V <sub>OD</sub>                   | Differential output voltage                             | R <sub>L</sub> = 100 Ω                                                                                               | 270 |                    | 550 | mV   |

| $\Delta V_{OD}$                   | LVDS VOD magnitude change                               |                                                                                                                      |     |                    | 50  | mV   |

| V <sub>OS</sub>                   | Offset Voltage                                          | -40°C to 85°C                                                                                                        |     | 1.24               |     | V    |

| $\Delta V_{OS}$                   | VOS magnitude change                                    |                                                                                                                      |     | 40                 |     | mV   |

|                                   | Short circuit Vout+ to ground                           | VOUT = 0                                                                                                             |     |                    | 27  | mA   |

|                                   | Short circuit Vout- to ground                           | VOUT = 0                                                                                                             |     |                    | 27  | mA   |

| t <sub>pho</sub>                  | Reference (PRI_REF or SEC_REF) to output phase offset   | Outputs are set to 491.52 MHz<br>Reference at 30.72 MHz                                                              |     | 1.65               |     | ns   |

| $t_{pd(LH)}/t_{pd(HL)}$           | Propagation delay from PRI_REF or<br>SEC_REF to outputs | Crosspoint to Crosspoint, Bypass Mode                                                                                |     | 3.1                |     | ns   |

| t <sub>sk(o)</sub> <sup>(3)</sup> | Skew, output to output For Y0 to Y4                     | All Outputs set at 200 MHz                                                                                           |     | 25                 |     | ps   |

| Co                                | Output capacitance on Y0 to Y4                          | $V_{CC} = 3.3 \text{ V}; V_{O} = 0 \text{ V or } V_{CC}$                                                             |     | 5                  |     | pF   |

| I <sub>OPDH</sub>                 | Power down output current                               | $V_{O} = V_{CC}$                                                                                                     |     |                    | 25  | μA   |

| I <sub>OPDL</sub>                 | Power down output current                               | $V_{O} = 0 V$                                                                                                        |     |                    | 5   | μA   |

|                                   | Duty cycle                                              |                                                                                                                      | 45% |                    | 55% |      |

| t <sub>r</sub> / t <sub>f</sub>   | Rise and fall time                                      | 20% to 80% of V <sub>OUT(PP)</sub>                                                                                   | 110 | 160                | 190 | ps   |

|                                   | LVCMOS-TO-LVDS                                          |                                                                                                                      |     |                    |     |      |

| t <sub>skP_c</sub>                | Output skew between LVCMOS and LVDS outputs             | $V_{\rm CC}/2$ to Crosspoint. Output are at the same output frequency and use the same output divider configuration. | 0.9 | 1.4                | 1.9 | ns   |

The phase of LVCMOS is lagging in reference to the phase of LVDS. (1)

(2) (3) All typical values are at V<sub>CC</sub> = 3.3 V, temperature =  $25^{\circ}$ C The t<sub>sk(o)</sub> specification is only valid for equal loading of all outputs.

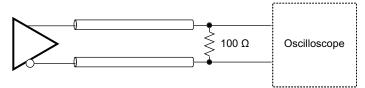

LVDS DC Termination Test

www.ti.com

#### SCAS862D-NOVEMBER 2008-REVISED AUGUST 2011

## **ELECTRICAL CHARACTERISTICS OPERATING CONDITIONS (Continued)**

recommended operating conditions for the **CDCE62005** device for under the specified Industrial temperature range of -40°C to 85°C

|                                              | PARAMETER                                            | TEST CONDITIONS                                                              | MIN                   | TYP <sup>(1)</sup> | MAX                   | UNIT |

|----------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------|-----------------------|--------------------|-----------------------|------|

| LVPECI                                       | _ OUTPUT                                             |                                                                              |                       |                    |                       |      |

| f <sub>clk</sub>                             | Output frequency, Configuration load                 |                                                                              | 0                     |                    | 1500                  | MHz  |

| V <sub>OH</sub>                              | LVPECL high-level output voltage load                |                                                                              | V <sub>CC</sub> -1.06 |                    | V <sub>CC</sub> -0.88 | V    |

| V <sub>OL</sub>                              | LVPECL low-level output voltage load                 |                                                                              | V <sub>CC</sub> -2.02 |                    | V <sub>CC</sub> -1.58 | V    |

| V <sub>OD</sub>                              | Differential output voltage                          |                                                                              | 610                   |                    | 970                   | mV   |

| t <sub>pho</sub>                             | Reference to Output Phase offset                     | Outputs are set to 491.52 MHz,<br>Reference at 30.72 MHz                     |                       | 1.47               |                       | ns   |

| t <sub>pd(LH)</sub> /<br>t <sub>pd(HL)</sub> | Propagation delay from PRI_REF or SEC_REF to outputs | Crosspoint to Crosspoint, Bypass<br>Mode                                     |                       | 3.4                |                       | ns   |

| t <sub>sk(o)</sub>                           | Skew, output to output For Y0 to Y4                  | All Outputs set at 200 MHz                                                   |                       | 25                 |                       | ps   |

| Co                                           | Output capacitance on Y0 to Y4                       | $V_{CC} = 3.3 \text{ V}; V_O = 0 \text{ V or } V_{CC}$                       |                       | 5                  |                       | pF   |

| I <sub>OPDH</sub>                            | Dower Down output ourrent                            | V <sub>O</sub> = V <sub>CC</sub>                                             |                       |                    | 25                    | μA   |

| I <sub>OPDL</sub>                            | Power Down output current                            | $V_0 = 0 V$                                                                  |                       |                    | 5                     | μA   |

|                                              | Duty Cycle                                           |                                                                              | 45%                   |                    | 55%                   |      |

| t <sub>r</sub> / t <sub>f</sub>              | Rise and fall time                                   | 20% to 80% of $V_{\text{OUT}(\text{PP})}$                                    | 55                    | 75                 | 135                   | ps   |

| LVDS-T                                       | O-LVPECL                                             |                                                                              |                       |                    |                       |      |

| t <sub>skP_C</sub>                           | Output skew between LVDS and LVPECL outputs          | Crosspoint to Crosspoint output dividers are configured identically.         | 0.9                   | 1.1                | 1.3                   | ns   |

| LVCMO                                        | S-TO-LVPECL                                          |                                                                              |                       |                    |                       |      |

| t <sub>skP_C</sub>                           | Output skew between LVCMOS and LVPECL outputs        | V <sub>CC</sub> /2 to Crosspoint output dividers are configured identically. | -150                  | 260                | 700                   | ps   |

| LVPECI                                       | HI-SWING OUTPUT                                      |                                                                              |                       |                    |                       |      |

| V <sub>OH</sub>                              | LVPECL high-level output voltage load                |                                                                              | V <sub>CC</sub> –1.11 |                    | V <sub>CC</sub> -0.87 | V    |

| V <sub>OL</sub>                              | LVPECL low-level output voltage load                 |                                                                              | V <sub>CC</sub> -2.06 |                    | V <sub>CC</sub> –1.73 | V    |

| V <sub>OD</sub>                              | Differential output voltage                          |                                                                              | 760                   |                    | 1160                  | mV   |

| t <sub>r</sub> / t <sub>f</sub>              | Rise and fall time                                   | 20% to 80% of V <sub>OUT(PP)</sub>                                           | 55                    | 75                 | 135                   | ps   |

(1) All typical values are at V<sub>CC</sub> = 3.3 V, temperature =  $25^{\circ}C$

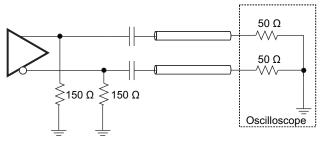

#### LVPECL AC Termination Test

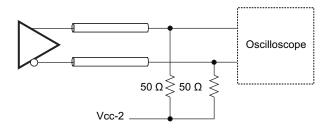

#### LVPECL DC Termination Test

TEXAS INSTRUMENTS

SCAS862D-NOVEMBER 2008-REVISED AUGUST 2011

CDCE62005

www.ti.com

#### TIMING REQUIREMENTS

over recommended ranges of supply voltage, load and operating free air temperature (unless otherwise noted)

|                                 | PARAMETER                                                                                                                                        | MIN | TYP | MAX  | UNIT |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| PRI_R                           | EF/SEC_REF REQUIREMENTS                                                                                                                          |     |     |      |      |

| f <sub>max</sub>                | Maximum Clock Frequency Applied to PRI_REF and SEC_REF in fan-out mode                                                                           |     |     | 1500 | MHz  |

|                                 | Maximum Clock Frequency Applied to Smart Multiplexer input Divider                                                                               |     |     | 500  | MHz  |

|                                 | Maximum Clock Frequency Applied to Reference Divider                                                                                             |     |     | 250  | MHz  |

|                                 | For Single ended Inputs (LVCMOS) on PRI_REF and SEC_REF                                                                                          |     |     | 250  | MHz  |

|                                 | Duty cycle of PRI_REF or SEC_REF at V <sub>CC</sub> / 2                                                                                          | 40% |     | 60%  |      |

|                                 | Input Clock Slew Rate (Differential and Single ended)                                                                                            | 1   |     |      | V/ns |

| Power                           | _Down, SYNC, REF_SEL REQUIREMENTS                                                                                                                |     |     |      |      |

| t <sub>r</sub> / t <sub>f</sub> | Rise and fall time of the $\overline{\text{Power}_{\text{Down}}}$ , $\overline{\text{SYNC}}$ , REF_SEL signal from 20% to 80% of V <sub>CC</sub> |     |     | 4    | ns   |

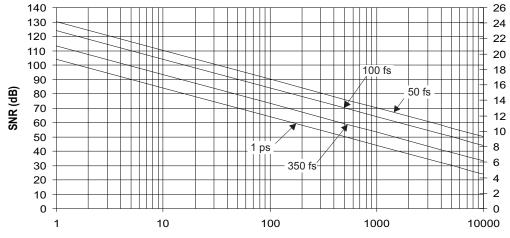

### PHASE NOISE ANALYSIS

#### Table 1. Device Output Phase Noise for 30.72 MHz External Reference

| •                         | Phase Noise Specifications under following configuration: VCO = 1966.08 MHz, REF = 30.72 MHz,<br>PFD Frequency = 30.72 MHz, Charge Pump Current = 1.5 mA Loop BW = 400 kHz at 3.3 V and 25°C |                   |                 |                   |        |  |  |  |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------|-------------------|--------|--|--|--|--|

| Phase Noise               | Reference 30.72 MHz                                                                                                                                                                          | LVPECL 491.52 MHz | LVDS 491.52 MHz | LVCMOS 122.88 MHz | UNIT   |  |  |  |  |

| 10 Hz                     | -108                                                                                                                                                                                         | 81                | 81              | -92               | dBc/Hz |  |  |  |  |

| 100 Hz                    | -130                                                                                                                                                                                         | -94               | -96             | -108              | dBc/Hz |  |  |  |  |

| 1 kHz                     | -134                                                                                                                                                                                         | -106              | -106            | -118              | dBc/Hz |  |  |  |  |

| 10 kHz                    | -152                                                                                                                                                                                         | -119              | -119            | -132              | dBc/Hz |  |  |  |  |

| 100 kHz                   | -156                                                                                                                                                                                         | -121              | -122            | -134              | dBc/Hz |  |  |  |  |

| 1 MHz                     | -157                                                                                                                                                                                         | -131              | -131            | -143              | dBc/Hz |  |  |  |  |

| 10 MHz                    | _                                                                                                                                                                                            | -145              | -144            | -150              | dBc/Hz |  |  |  |  |

| 20 MHz                    | _                                                                                                                                                                                            | -145              | -144            | -150              | dBc/Hz |  |  |  |  |

| Jitter(RMS) 10k~20<br>MHz | 193<br>(10 kHz – 1 MHz)                                                                                                                                                                      | 307               | 315             | 377               | fs     |  |  |  |  |

#### Table 2. Device Output Phase Noise for 25 MHz Crystal Reference

| •                         | ions under following configurate<br>MHz, Charge Pump Current = 4 |              | -              |        |

|---------------------------|------------------------------------------------------------------|--------------|----------------|--------|

| Phase Noise               | LVPECL 500 MHz                                                   | LVDS 250 MHz | LVCMOS 125 MHz | UNIT   |

| 10 Hz                     | -57                                                              | -62          | -68            | dBc/Hz |

| 100 Hz                    | -90                                                              | -95          | -102           | dBc/Hz |

| 1 kHz                     | -107                                                             | -113         | -119           | dBc/Hz |

| 10 kHz                    | -115                                                             | -122         | -128           | dBc/Hz |

| 100 kHz                   | -118                                                             | -124         | -130           | dBc/Hz |

| 1 MHz                     | -130                                                             | -137         | -143           | dBc/Hz |

| 10 MHz                    | -145                                                             | -147         | -150           | dBc/Hz |

| 20 MHz                    | -145                                                             | -147         | -150           | dBc/Hz |

| Jitter(RMS) 10k~20<br>MHz | 389                                                              | 405          | 437            | fs     |

www.ti.com

## OUTPUT TO OUTPUT ISOLATION

| Table 3. Output to Output Isolation | Table 3. | Output | to | Output | Isolation |

|-------------------------------------|----------|--------|----|--------|-----------|

|-------------------------------------|----------|--------|----|--------|-----------|

|                              |                               |                               | SPUR | Unit |

|------------------------------|-------------------------------|-------------------------------|------|------|

| The Output to Output Isolati | on was tested under following | settings (nominal conditions) |      |      |

| Output 2                     | Measured Channel              | In LVPECL Signaling 15.5 MHz  | -67  | db   |

| Output 2                     | Measured Channel              | In LVPECL Signaling 93 MHz    | -60  | db   |

| Output 2                     | Measured Channel              | In LVPECL Signaling 930 MHz   | -59  | db   |

| Output 0                     | Aggressor Channel             | LVPECL 22.14 MHz              |      |      |

| Output 1                     | Aggressor Channel             | LVPECL 22.14 MHz              |      |      |

| Output 3                     | Aggressor Channel             | LVPECL 22.14 MHz              |      |      |

| Output 4                     | Aggressor Channel             | LVPECL 22.14 MHz              |      |      |

#### www.ti.com

#### **DEVICE CONFIGURATION**

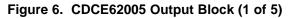

The Functional Description Section described four different functional blocks contained within the CDCE62005. Figure 14 depicts these blocks along with a high-level functional block diagram of the circuit elements comprising each block. The balance of this section focuses on a detailed discussion of each functional block from the perspective of how to configure them.

Figure 14. CDCE62005 Circuit Blocks

Throughout this section, references to Device Register memory locations follow the following convention:

Figure 15. Device Register Reference Convention

### INTERFACE AND CONTROL BLOCK

The Interface & Control Block includes a SPI interface, three control pins, a non-volatile memory array in which the device stores default configuration data, and an array of device registers implemented in Static RAM. This RAM, also called the device registers, configures all hardware within the CDCE62005.

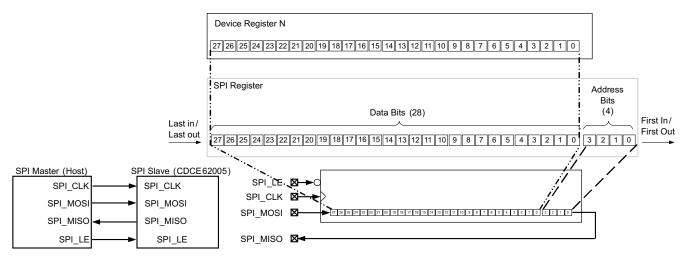

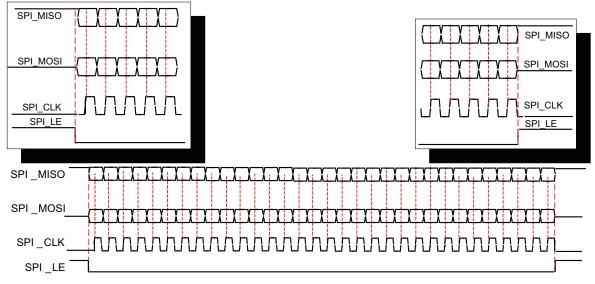

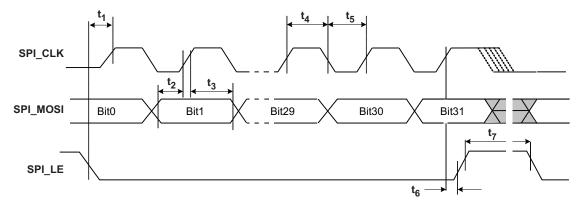

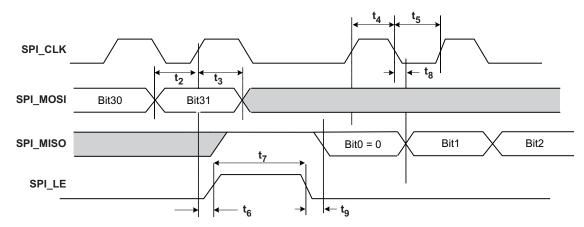

#### Serial Peripheral Interface (SPI)

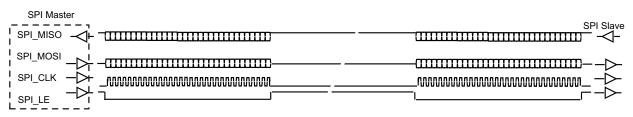

The serial interface of CDCE62005 is a simple bidirectional SPI interface for writing and reading to and from the device registers. It implements a low speed serial communications link in a master/slave topology in which the CDCE62005 is a slave. The SPI consists of four signals:

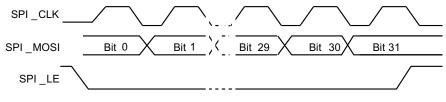

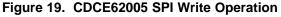

- **SPI\_CLK:** Serial Clock (Output from Master) the CDCE62005 clocks data in and out on the rising edge of SPI\_CLK. Data transitions therefore occur on the falling edge of the clock.

- SPI\_MOSI: Master Output Slave Input (Output from Master) .

- **SPI\_MISO:** Master Input Slave Output (Output from Slave)

- **SPI\_LE:** Latch Enable (Output from Master). The falling edge of SPI\_LE initiates a transfer. If SPI\_LE is high, no data transfer can take place.

The CDCE62005 implements data fields that are 28-bits wide. In addition, it contains 9 registers, each comprising a 28 bit data field. Therefore, accessing the CDCE62005 requires that the host program append a 4-bit address field to the front of the data field as follows:

Figure 16. CDCE62005 SPI Communications Format

#### CDCE62005 SPI Command Structure

The CDCE62005 supports four commands issued by the Master via the SPI:

- Write to RAM

- Read Command

- Copy RAM to EEPROM unlock

- Copy RAM to EEPROM lock