## DS25CP104A,DS25CP114

DS25CP104A / DS25CP114 3.125 Gbps 4x4 LVDS Crosspoint Switch with Transmit Pre-Emphasis and Receive Equalization

Literature Number: SNLS305B

## DS25CP104A / DS25CP114

# 3.125 Gbps 4x4 LVDS Crosspoint Switch with Transmit Pre-Emphasis and Receive Equalization

### **General Description**

The DS25CP104A and DS25CP114 are 3.125 Gbps 4x4 LVDS crosspoint switches optimized for high-speed signal routing and switching over lossy FR-4 printed circuit board backplanes and balanced cables. Fully differential signal paths ensure exceptional signal integrity and noise immunity. The non-blocking architecture allows connections of any input to any output or outputs. The switch configuration can be accomplished via external pins or the System Management Bus (SMBus) interface.

The DS25CP104A and DS25CP114 feature four levels (Off, Low, Medium, High) of transmit pre-emphasis (PE) and four levels (Off, Low, Medium, High) of receive equalization (EQ) settable via the SMBus interface. Off and Medium PE levels and Off and Low EQ levels are settable with the external pins. In addition, the SMBus circuitry enables the loss of signal (LOS) monitors that can inform a system of the presence of an open inputs condition (e.g. disconnected cable).

Wide input common mode range allows the switch to accept signals with LVDS, CML and LVPECL levels; the output levels are LVDS. A very small package footprint requires a minimal space on the board while the flow-through pinout allows easy board layout. On the DS25CP104A each differential input and output is internally terminated with a  $100\Omega$  resistor to lower return losses, reduce component count and further minimize board space. For added design flexibility the  $100\Omega$  input terminations on the DS25CP114 have been eliminated. This enables a designer to build custom crosspoint configurations and distribution circuits that require a limited multidrop signaling topology.

#### **Features**

- DC 3.125 Gbps low jitter, low skew, low power operation

- Pin and SMBus configurable, fully differential, non-blocking architecture

- Pin (two levels) and SMBus (four levels) selectable preemphasis and equalization eliminate ISI jitter

- Wide Input Common Mode Range enables easy interface to CML and LVPECL drivers

- LOS circuitry detects open inputs fault condition

- On-chip 100Ω input and output termination minimizes insertion and return losses, reduces component count and minimizes board space. The DS25CP114 eliminates the on-chip input termination for added design flexibility.

- 8 kV ESD on LVDS I/O pins protects adjoining components

- Small 6 mm x 6 mm LLP-40 space saving package

### **Applications**

- SD/HD/3G HD SDI Routers

- OC-48 / STM-16

- InfiniBand and FireWire

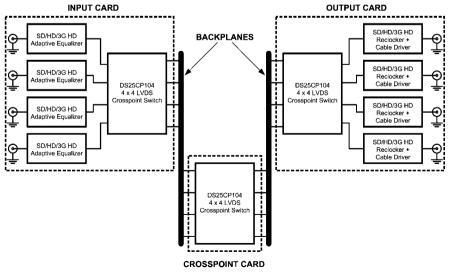

## **Typical Application**

30073603

## **Device Information**

| Device     | Function              | Termination Option                    | Available Signal<br>Conditioning |

|------------|-----------------------|---------------------------------------|----------------------------------|

| DS25CP104A | 4x4 Crosspoint Switch | Internal 100 $\Omega$ for LVDS inputs | 4 Levels: PE and EQ              |

| DS25CP114  | 4x4 Crosspoint Switch | None: Requires external termination   | 4 Levels : PE and EQ             |

## **Ordering Information**

| NSID           | Package             | Tape & Reel QTY | Package Number |

|----------------|---------------------|-----------------|----------------|

| DS25CP104ATSQ  | 40 Lead LLP Package | 250             | SQA40A         |

| DS25CP104ATSQX | 40 Lead LLP Package | 2500            | SQA40A         |

| DS25CP114TSQ   | 40 Lead LLP Package | 250             | SQA40A         |

| DS25CP114TSQX  | 40 Lead LLP Package | 2500            | SQA40A         |

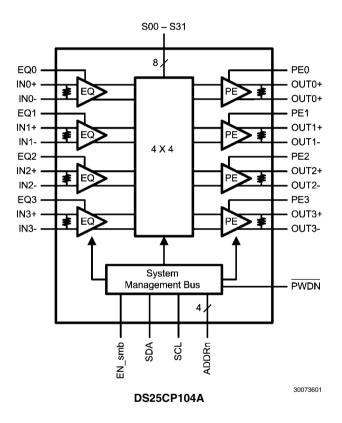

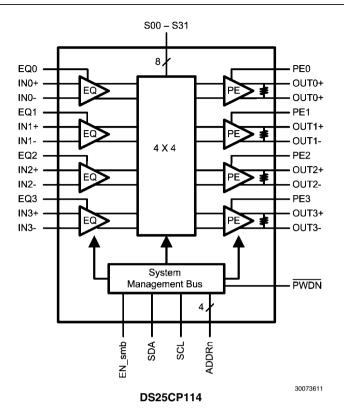

## **Block Diagrams**

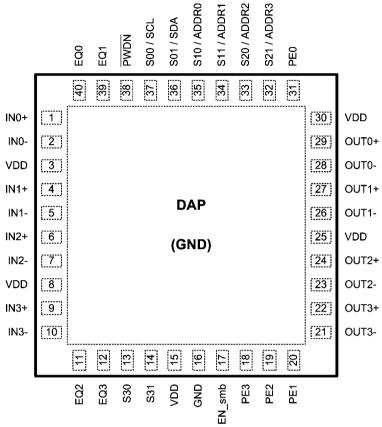

## **Connection Diagram**

DS25CP104A / DS25CP114 Pin Diagram

30073602

## **Pin Descriptions**

| Pin Name                                                        | Pin<br>Number                           | I/O, Type   | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------|-----------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IN0+, IN0-,<br>IN1+, IN1-,<br>IN2+, IN2-,<br>IN3+, IN3-         | 1, 2,<br>4, 5,<br>6, 7,<br>9, 10        | I, LVDS     | Inverting and non-inverting high speed LVDS input pins. These 4 input pairs have a 100 Ohm differential input termination on the CP104A device. The CP114 eliminates the input termination for added design flexibility.                                                                                                                                                                                                                                                                   |

| OUT0+, OUT0-,<br>OUT1+, OUT1-,<br>OUT2+, OUT2-,<br>OUT3+, OUT3- | 29, 28,<br>27, 26,<br>24, 23,<br>22, 21 | O, LVDS     | Inverting and non-inverting high speed LVDS output pins. Each output pair has an internal 100 Ohm termination to improve device return loss characteristics.                                                                                                                                                                                                                                                                                                                               |

| EQ0, EQ1,<br>EQ2, EQ3                                           | 40, 39,<br>11, 12                       | I, LVCMOS   | Receive equalization level select pins. These pins are functional regardless of the EN_smb pin state.                                                                                                                                                                                                                                                                                                                                                                                      |

| PE0, PE1,<br>PE2, PE3                                           | 31, 20,<br>19, 18                       | I, LVCMOS   | Transmit pre-emphasis level select pins. These pins are functional regardless of the EN_smb pin state.                                                                                                                                                                                                                                                                                                                                                                                     |

| EN_smb                                                          | 17                                      | I, LVCMOS   | System Management Bus (SMBus) enable pin. The pin has an internal pull down. When the pin is set to a [1], the device is in the SMBus mode. All SMBus registers are reset when this pin is toggled. There is a 20k pulldown device on this pin.                                                                                                                                                                                                                                            |

| S00/SCL                                                         | 37                                      | I, LVCMOS   | For EN_smb = [0], these pins select which LVDS input is routed                                                                                                                                                                                                                                                                                                                                                                                                                             |

| S01/SDA                                                         | 36                                      | I/O, LVCMOS | to the OUT0. In the SMBus mode, when the EN_smb = [1], these pins are SMBus clock input and data input pins respectively.                                                                                                                                                                                                                                                                                                                                                                  |

| S10/ADDR0,<br>S11/ADDR1                                         | 35,<br>34                               | I, LVCMOS   | For EN_smb = [0], these pins select which LVDS input is routed to the OUT1.  In the SMBus mode, when the EN_smb = [1], these pins are the User-Set SMBus Slave Address inputs.                                                                                                                                                                                                                                                                                                             |

| S20/ADDR2,<br>S21/ADDR3                                         | 33,<br>32                               | I, LVCMOS   | For EN_smb = [0], these pins select which LVDS input is routed to the OUT2.  In the SMBus mode, when the EN_smb = H, these pins are the User-Set SMBus Slave Address inputs.                                                                                                                                                                                                                                                                                                               |

| S30, S31                                                        | 13, 14                                  | I, LVCMOS   | For EN_smb = [0], these pins select which LVDS input is routed to the OUT3.  In the SMBus mode, when the EN_smb = [1], these pins are nonfunctional and should be tied to either logic H or L.                                                                                                                                                                                                                                                                                             |

| PWDN                                                            | 38                                      | I, LVCMOS   | For EN_smb = [0], this is the power down pin. When the PWDN is set to a [0], the device is in the power down mode. The SMBus circuitry can still be accessed provided the EN_smb pin is set to a [1].  In the SMBus mode, the device is powered up by either setting the PWDN pin to [1] OR by writing a [1] to the Control Register D[7] bit (SoftPWDN). The device will be powered down by setting the PWDN pin to [0] AND by writing a [0] to the Control Register D[7] bit (SoftPWDN). |

| VDD                                                             | 3, 8,<br>15,25, 30                      | Power       | Power supply pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| GND                                                             | 16, DAP                                 | Power       | Ground pin and a pad (DAP - die attach pad).                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Note: Center DAP connection must be made to GND for optimum electrical and thermal performance.

## **Absolute Maximum Ratings** (Note 4)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage                                | -0.3V to +4V                 |

|-----------------------------------------------|------------------------------|

| LVCMOS Input Voltage                          | $-0.3V$ to $(V_{CC} + 0.3V)$ |

| LVCMOS Output Voltage                         | $-0.3V$ to $(V_{CC} + 0.3V)$ |

| LVDS Input Voltage                            | -0.3V to +4V                 |

| Differential Input Voltage IVIDI (DS25CP104A) | 1.0V                         |

| LVDS Differential Input Voltage (DS25CP114)   | V <sub>CC</sub> + 0.6V       |

| LVDS Output Voltage                           | $-0.3V$ to $(V_{CC} + 0.3V)$ |

| LVDS Differential Output Voltage              | 0V to 1.0V                   |

| LVDS Output Short Circuit Current Duration    | 5 ms                         |

| Junction Temperature                          | +150°C                       |

| Storage Temperature Range                     | -65°C to +150°C              |

| Lead Temperature Range                        |                              |

| Soldering (4 sec.)                            | +260°C                       |

| Maximum Package Power Dissipati               | on at 25°C                   |

| SQA Package                                   | 4.65W                        |

| Derate SQA Package                            | 37.2 mW/°C above +25°C       |

| Package | Thermal | Resistance    |

|---------|---------|---------------|

| uonago  | HIGHHA  | 1 loolotarioc |

| $\Theta_{JA}$      | +26.9°C/W |

|--------------------|-----------|

| $\theta_{JC}$      | +3.8°C/W  |

| ESD Susceptibility |           |

| HBM (Note 1)       | ≥8 kV     |

MM (*Note 2*) ≥250V CDM (*Note 3*) ≥1250V

Note 1: Human Body Model, applicable std. JESD22-A114C

Note 2: Machine Model, applicable std. JESD22-A115-A

Note 3: Field Induced Charge Device Model, applicable std.

JESD22-C101-C

# Recommended Operating Conditions

|                                                                                | Min | Тур | Max | Units |

|--------------------------------------------------------------------------------|-----|-----|-----|-------|

| Supply Voltage (V <sub>CC</sub> )                                              | 3.0 | 3.3 | 3.6 | V     |

| Receiver Differential Input<br>Voltage (V <sub>ID</sub> )<br>(DS25CP104A only) | 0   |     | 1   | V     |

| Operating Free Air<br>Temperature (T <sub>A</sub> )                            | -40 | +25 | +85 | °C    |

| SMBus (SDA, SCL)                                                               |     |     | 3.6 | V     |

### **DC Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified. (Note 5, Note 6, Note 8)

| Symbol              | Parameter                           | Conditions                                                    |                           | Min  | Тур  | Max                    | Units |

|---------------------|-------------------------------------|---------------------------------------------------------------|---------------------------|------|------|------------------------|-------|

| LVCMOS              | DC SPECIFICATIONS                   |                                                               |                           |      |      |                        |       |

| V <sub>IH</sub>     | High Level Input Voltage            |                                                               |                           | 2.0  |      | $V_{CC}$               | V     |

| V <sub>IL</sub>     | Low Level Input Voltage             |                                                               |                           | GND  |      | 0.8                    | V     |

| I <sub>IH</sub>     | High Level Input Current            | V <sub>IN</sub> = 3.6V                                        |                           |      | 0    | ±10                    | μΑ    |

|                     |                                     | $V_{CC} = 3.6V$                                               | EN_smb pin                | 40   | 175  | 250                    | μΑ    |

| I <sub>IL</sub>     | Low Level Input Current             | $V_{IN} = GND$<br>$V_{CC} = 3.6V$                             |                           |      | 0    | ±10                    | μA    |

| V <sub>CL</sub>     | Input Clamp Voltage                 | $I_{CL} = -18 \text{ mA}, V$                                  | $V_{\rm CC} = 0 \text{V}$ |      | -0.9 | -1.5                   | V     |

| $\overline{V_{OL}}$ | Low Level Output Voltage            | I <sub>OL</sub> = 4 mA                                        | SDA pin                   |      |      | 0.4                    | V     |

| LVDS IN             | PUT DC SPECIFICATIONS               |                                                               |                           |      |      |                        |       |

| V <sub>ID</sub>     | Input Differential Voltage(Note 9)  |                                                               |                           | 0    |      | 1                      | V     |

| V <sub>TH</sub>     | Differential Input High Threshold   | $V_{CM} = +0.05V$                                             | or V <sub>CC</sub> -0.05V |      | 0    | +100                   | mV    |

| V <sub>TL</sub>     | Differential Input Low Threshold    |                                                               |                           | -100 | 0    |                        | mV    |

| V <sub>CMR</sub>    | Input Common Mode Voltage Range     | V <sub>ID</sub> = 100 mV                                      |                           | 0.05 |      | V <sub>CC</sub> - 0.05 | V     |

| I <sub>IN</sub>     | Input Current(Note 7)               | V <sub>IN</sub> = +3.6V or 0V<br>V <sub>CC</sub> = 3.6V or 0V |                           |      | ±1   | ±10                    | μA    |

| C <sub>IN</sub>     | Input Capacitance                   | Any LVDS Inpu                                                 | it Pin to GND             |      | 1.7  |                        | pF    |

| R <sub>IN</sub>     | Input Termination Resistor(Note 10) | Between IN+ a                                                 | nd IN-                    |      | 100  |                        | Ω     |

| Symbol           | Parameter                                                                 | Conditions                 | Min  | Тур | Max                                                                     | Units |

|------------------|---------------------------------------------------------------------------|----------------------------|------|-----|-------------------------------------------------------------------------|-------|

| LVDS O           | UTPUT DC SPECIFICATIONS                                                   | ·                          | •    | •   | •                                                                       | •     |

| V <sub>OD</sub>  | Differential Output Voltage                                               |                            | 250  | 350 | 450                                                                     | mV    |

| ΔV <sub>OD</sub> | Change in Magnitude of V <sub>OD</sub> for Complimentary<br>Output States | $R_L = 100\Omega$          | -35  |     | 35                                                                      | mV    |

| V <sub>os</sub>  | Offset Voltage                                                            |                            | 1.05 | 1.2 | 1.375                                                                   | ٧     |

| ΔV <sub>OS</sub> | Change in Magnitude of V <sub>OS</sub> for Complimentary<br>Output States | $R_L = 100\Omega$          | -35  |     | 35                                                                      | mV    |

|                  | Outrout Short Girevit Coment (Note 11)                                    | OUT to GND                 |      | -35 | -55                                                                     | mA    |

| los              | Output Short Circuit Current (Note 11)                                    | OUT to V <sub>CC</sub>     |      | 7   | 35<br>2 1.375<br>35<br>35<br>5 -55<br>7 55<br>2<br>90<br>0 50<br>45 175 | mA    |

| C <sub>OUT</sub> | Output Capacitance                                                        | Any LVDS Output Pin to GND |      | 1.2 |                                                                         | pF    |

| R <sub>OUT</sub> | Output Termination Resistor                                               | Between OUT+ and OUT-      |      | 100 |                                                                         | Ω     |

|                  | CURRENT                                                                   | •                          | •    |     | •                                                                       |       |

| I <sub>CC1</sub> | Supply Current                                                            | PWDN = 0                   |      | 40  | 50                                                                      | mA    |

| I <sub>CC2</sub> | Supply Current                                                            | PWDN = 1                   |      | 145 | 175                                                                     | mA    |

|                  |                                                                           | PE = Off, EQ = Off         |      |     |                                                                         |       |

|                  |                                                                           | Broadcast (1:4) Mode       |      |     |                                                                         |       |

| I <sub>CC3</sub> | Supply Current                                                            | PWDN = 1                   |      | 157 | 190                                                                     | mA    |

|                  |                                                                           | PE = Off, EQ = Off         |      |     |                                                                         |       |

|                  |                                                                           | Quad Buffer (4:4) Mode     |      |     |                                                                         |       |

Note 4: "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions at which the device is functional and the device should not be operated beyond such conditions.

**Note 5:** The Electrical Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.

**Note 6:** Current into device pins is defined as positive. Current out of device pins is defined as negative. All voltages are referenced to ground except  $V_{OD}$  and  $\Delta V_{OD}$ .

Note 7: I<sub>IN</sub> is applied to both pins of the LVDS input pair at the same time.

Note 8: Typical values represent most likely parametric norms for  $V_{CC} = +3.3V$  and  $T_A = +25^{\circ}C$ , and at the Recommended Operation Conditions at the time of product characterization and are not guaranteed.

Note 9: Input Differential Voltage (V<sub>ID</sub>) The DS25CP104A limits input amplitude to 1 volt. The DS25CP114 supports any V<sub>ID</sub> within the supply voltage to GND range.

Note 10: Input Termination Resistor (R<sub>IN</sub>) The DS25CP104A provides an integrated 100 ohm input termination for each high speed LVDS pair. The DS25CP114 eliminates this internal termination.

Note 11: Output short circuit current (I<sub>OS</sub>) is specified as magnitude only, minus sign indicates direction only.

## **AC Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified. (Note 12, Note 13)

| Symbol            | Parameter                                                                | Conditions                                   |            | Min | Тур  | Max  | Units             |

|-------------------|--------------------------------------------------------------------------|----------------------------------------------|------------|-----|------|------|-------------------|

| LVDS OUTPUT       | T AC SPECIFICATIONS (Note 14)                                            | •                                            |            |     |      |      |                   |

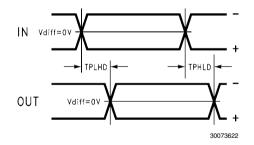

| t <sub>PLHD</sub> | Differential Propagation Delay Low to High                               | D = 4000                                     |            |     | 480  | 650  | ps                |

| t <sub>PHLD</sub> | Differential Propagation Delay High to Low                               | $R_L = 100\Omega$                            |            |     | 460  | 650  | ps                |

| t <sub>SKD1</sub> | Pulse Skew It <sub>PLHD</sub> - t <sub>PHLD</sub> I , ( <i>Note 15</i> ) |                                              |            |     | 20   | 100  | ps                |

| t <sub>SKD2</sub> | Channel to Channel Skew , (Note 16)                                      |                                              |            |     | 40   | 125  | ps                |

| t <sub>SKD3</sub> | Part to Part Skew , (Note 17)                                            |                                              |            |     | 50   | 200  | ps                |

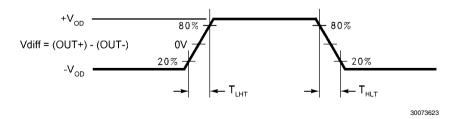

| t <sub>LHT</sub>  | Rise Time                                                                | D = 4000                                     |            |     | 80   | 150  | ps                |

| t <sub>HLT</sub>  | Fall Time                                                                | $R_L = 100\Omega$                            |            |     | 80   | 150  | ps                |

| t <sub>ON</sub>   | Power Up Time                                                            | Time from PWDN =LH to OUTn active            |            |     | 6    | 20   | μs                |

| t <sub>OFF</sub>  | Power Down Time                                                          | Time from PWDN =HL to OUTn inactive          |            |     | 8    | 25   | ns                |

| t <sub>SEL</sub>  | Select Time                                                              | Time from Sn =LH or HL to new signal at OUTn |            |     | 8    | 12   | ns                |

| JITTER PERFO      | DRMANCE WITH EQ = Off, PE = Off (Note                                    | 14)(Figure 5)                                |            |     | •    |      |                   |

| t <sub>RJ1</sub>  | Random Jitter (RMS Value)                                                | V <sub>ID</sub> = 350 mV                     | 1.25 GHz   |     | 0.5  | 1.1  | ps                |

| t <sub>RJ2</sub>  | No Test Channels (Note 18)                                               | V <sub>CM</sub> = 1.2V<br>Clock (RZ)         | 1.5625 GHz |     | 0.5  | 1.1  | ps                |

| t <sub>DJ1</sub>  | Deterministic Jitter (Peak to Peak)                                      | V <sub>ID</sub> = 350 mV                     | 2.5 Gbps   |     | 10   | 22   | ps                |

| t <sub>DJ2</sub>  | No Test Channels<br>(Note 19)                                            | V <sub>CM</sub> = 1.2V<br>K28.5 (NRZ)        | 3.125 Gbps |     | 10   | 27   | ps                |

| t <sub>TJ1</sub>  | Total Jitter (Peak to Peak)                                              | V <sub>ID</sub> = 350 mV                     | 2.5 Gbps   |     | 0.07 | 0.11 | UI <sub>P-P</sub> |

| t <sub>TJ2</sub>  | No Test Channels (Note 20)                                               | V <sub>CM</sub> = 1.2V<br>PRBS-23 (NRZ)      | 3.125 Gbps |     | 0.13 | 0.16 | UI <sub>P-P</sub> |

| Symbol            | Parameter                           | Cond                                    | Conditions |   | Тур  | Max  | Units             |

|-------------------|-------------------------------------|-----------------------------------------|------------|---|------|------|-------------------|

| JITTER PERFO      | DRMANCE WITH EQ = Off, PE = Low(No  | ote 14) <b>(Figure 6 Figur</b>          | re 9)      | • | •    | •    | •                 |

| t <sub>RJ1A</sub> | Random Jitter (RMS Value)           | V <sub>ID</sub> = 350 mV                | 1.25 GHz   |   | 0.5  | 1.1  | ps                |

| t <sub>RJ2A</sub> | Test Channels A (Note 18)           | V <sub>CM</sub> = 1.2V<br>Clock (RZ)    | 1.5625 GHz |   | 0.5  | 1.1  | ps                |

| t <sub>DJ1A</sub> | Deterministic Jitter (Peak to Peak) | V <sub>ID</sub> = 350 mV                | 2.5 Gbps   |   | 10   | 22   | ps                |

| t <sub>DJ2A</sub> | Test Channels A (Note 19)           | V <sub>CM</sub> = 1.2V<br>K28.5 (NRZ)   | 3.125 Gbps |   | 10   | 27   | ps                |

| JITTER PERFO      | DRMANCE WITH EQ = Off, PE = Mediun  | n (Note 14) (Figure 6 I                 | Figure 9)  |   |      |      |                   |

| t <sub>RJ1B</sub> | Random Jitter (RMS Value)           | V <sub>ID</sub> = 350 mV                | 1.25 GHz   |   | 0.5  | 1.1  | ps                |

| t <sub>RJ2B</sub> | Test Channels B (Note 18)           | V <sub>CM</sub> = 1.2V<br>Clock (RZ)    | 1.5625 GHz |   | 0.5  | 1.1  | ps                |

| t <sub>DJ1B</sub> | Deterministic Jitter (Peak to Peak) | V <sub>ID</sub> = 350 mV                | 2.5 Gbps   |   | 12   | 30   | ps                |

| t <sub>DJ2B</sub> | Test Channels B (Note 19)           | V <sub>CM</sub> = 1.2V<br>K28.5 (NRZ)   | 3.125 Gbps |   | 12   | 30   | ps                |

| t <sub>TJ1B</sub> | Total Jitter (Peak to Peak)         | V <sub>ID</sub> = 350 mV                | 2.5 Gbps   |   | 0.08 | 0.10 | UI <sub>P-P</sub> |

| t <sub>TJ2B</sub> | Test Channels B (Note 20)           | V <sub>CM</sub> = 1.2V<br>PRBS-23 (NRZ) | 3.125 Gbps |   | 0.10 | 0.15 | UI <sub>P-P</sub> |

| JITTER PERFO      | DRMANCE WITH EQ = Off, PE = High (  | Note 14) (Figures 6, 9)                 | •          | • | •    |      | •                 |

| t <sub>RJ1C</sub> | Random Jitter (RMS Value)           | V <sub>ID</sub> = 350 mV                | 1.25 GHz   |   | 0.5  | 1.1  | ps                |

| t <sub>RJ2C</sub> | Test Channels C (Note 18)           | V <sub>CM</sub> = 1.2V<br>Clock (RZ)    | 1.5625 GHz |   | 0.5  | 1.1  | ps                |

| t <sub>DJ1C</sub> | Deterministic Jitter (Peak to Peak) | V <sub>ID</sub> = 350 mV                | 2.5 Gbps   |   | 30   | 60   | ps                |

| t <sub>DJ2C</sub> | Test Channels C (Note 19)           | V <sub>CM</sub> = 1.2V<br>K28.5 (NRZ)   | 3.125 Gbps |   | 30   | 65   | ps                |

| Symbol            | Parameter                                              | Cond                                    | itions     | Min | Тур  | Max  | Units             |

|-------------------|--------------------------------------------------------|-----------------------------------------|------------|-----|------|------|-------------------|

| JITTER PERFO      | DRMANCE WITH PE = Off, EQ = Low (No                    | te 14) (Figure 7 Figu                   | re 9)      | · · |      |      |                   |

| t <sub>RJ1D</sub> | Random Jitter (RMS Value)                              | V <sub>ID</sub> = 350 mV                | 1.25 GHz   |     | 0.5  | 1.1  | ps                |

| t <sub>RJ2D</sub> | Test Channels D (Note 18)                              | V <sub>CM</sub> = 1.2V<br>Clock (RZ)    | 1.5625 GHz |     | 0.5  | 1.1  | ps                |

| t <sub>DJ1D</sub> | Deterministic Jitter (Peak to Peak)                    | V <sub>ID</sub> = 350 mV                | 2.5 Gbps   |     | 20   | 40   | ps                |

| t <sub>DJ2D</sub> | Test Channels D (Note 19)                              | V <sub>CM</sub> = 1.2V<br>K28.5 (NRZ)   | 3.125 Gbps |     | 20   | 40   | ps                |

| t <sub>TJ1D</sub> | Total Jitter (Peak to Peak)                            | V <sub>ID</sub> = 350 mV                | 2.5 Gbps   |     | 0.08 | 0.15 | UI <sub>P-P</sub> |

| t <sub>TJ2D</sub> | Test Channels D (Note 20)                              | V <sub>CM</sub> = 1.2V<br>PRBS-23 (NRZ) | 3.125 Gbps |     | 0.09 | 0.20 | UI <sub>P-P</sub> |

| JITTER PERFO      | DRMANCE WITH PE = Off, EQ = Medium                     | (Note 14) (Figures 7                    | , 9)       |     |      |      |                   |

| t <sub>RJ1E</sub> | Random Jitter (RMS Value)                              | V <sub>ID</sub> = 350 mV                | 1.25 GHz   |     | 0.5  | 1.1  | ps                |

| t <sub>RJ2E</sub> | Test Channels E<br>(Note 18)                           | V <sub>CM</sub> = 1.2V<br>Clock (RZ)    | 1.5625 GHz |     | 0.5  | 1.1  | ps                |

| t <sub>DJ1E</sub> | Residual Deterministic Jitter (Peak to                 | V <sub>ID</sub> = 350 mV                | 2.5 Gbps   |     | 35   | 60   | ps                |

| t <sub>DJ2E</sub> | Peak) Test Channels E (Note 19)                        | V <sub>CM</sub> = 1.2V<br>K28.5 (NRZ)   | 3.125 Gbps |     | 28   | 55   | ps                |

| JITTER PERFO      | DRMANCE WITH PE = Off, EQ = High (No                   | ote 14) (Figures 7, 9)                  | •          |     |      |      |                   |

| t <sub>RJ1F</sub> | Random Jitter (RMS Value)                              | V <sub>ID</sub> = 350 mV                | 1.25 GHz   |     | 1.3  | 1.8  | ps                |

| t <sub>RJ2F</sub> | Test Channels F (Note 18)                              | V <sub>CM</sub> = 1.2V<br>Clock (RZ)    | 1.5625 GHz |     | 1.4  | 2.4  | ps                |

| t <sub>DJ1F</sub> | Residual Deterministic Jitter (Peak to                 | V <sub>ID</sub> = 350 mV                | 2.5 Gbps   |     | 30   | 75   | ps                |

| t <sub>DJ2F</sub> | Peak) Test Channels F (Note 19)                        | V <sub>CM</sub> = 1.2V<br>K28.5 (NRZ)   | 3.125 Gbps |     | 35   | 90   | ps                |

| JITTER PERFO      | DRMANCE WITH PE = Medium, EQ = Lov                     | v (Note 14) (Figures                    | 7, 9)      | •   | •    |      | •                 |

| t <sub>RJ1G</sub> | Random Jitter (RMS Value)                              | V <sub>ID</sub> = 350 mV                | 1.25 GHz   |     | 0.5  | 1.1  | ps                |

| t <sub>RJ2G</sub> | Input Test Channels D Output Test Channels B (Note 18) | V <sub>CM</sub> = 1.2V<br>Clock (RZ)    | 1.5625 GHz |     | 0.5  | 1.1  | ps                |

| t <sub>DJ1G</sub> | Deterministic Jitter (Peak to Peak)                    | V <sub>ID</sub> = 350 mV                | 2.5 Gbps   |     | 25   |      | ps                |

| t <sub>DJ2G</sub> | Input Test Channels D Output Test Channels B (Note 19) | V <sub>CM</sub> = 1.2V<br>K28.5 (NRZ)   | 3.125 Gbps |     | 20   |      | ps                |

| Symbol               | Parameter                                                                                    | Min | Тур | Max | Units |     |

|----------------------|----------------------------------------------------------------------------------------------|-----|-----|-----|-------|-----|

| SMBus AC SP          | ECIFICATIONS                                                                                 |     |     | •   | •     | •   |

| f <sub>SMB</sub>     | SMBus Operating Frequency                                                                    |     | 10  |     | 100   | kHz |

| t <sub>BUF</sub>     | Bus free time between Stop and Start<br>Conditions                                           |     | 4.7 |     |       | μs  |

| t <sub>HD:SDA</sub>  | Hold time after (Repeated) Start Condition. After this period, the first clock is generated. |     | 4.0 |     |       | μs  |

| t <sub>SU:SDA</sub>  | Repeated Start Condition setup time.                                                         |     | 4.7 |     |       | μs  |

| t <sub>SU:SDO</sub>  | Stop Condition setup time                                                                    |     | 4.0 |     |       | μs  |

| t <sub>HD:DAT</sub>  | Data hold time                                                                               |     | 300 |     |       | ns  |

| t <sub>SU:DAT</sub>  | Data setup time                                                                              |     | 250 |     |       | ns  |

| t <sub>TIMEOUT</sub> | Detect clock low timeout                                                                     |     | 25  |     | 35    | ms  |

| t <sub>LOW</sub>     | Clock low period                                                                             |     | 4.7 |     |       | μs  |

| t <sub>HIGH</sub>    | Clock high period                                                                            |     | 4.0 |     | 50    | μs  |

| t <sub>POR</sub>     | Time in which a device must be operational after power-on reset                              |     |     |     | 500   | ms  |

Note 12: The Electrical Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.

Note 13: Typical values represent most likely parametric norms for  $V_{CC} = +3.3V$  and  $T_A = +25^{\circ}C$ , and at the Recommended Operation Conditions at the time of product characterization and are not guaranteed.

Note 14: Specification is guaranteed by characterization and is not tested in production.

Note 15: t<sub>SKD1</sub>, lt<sub>PLHD</sub> – t<sub>PHLD</sub>I, Pulse Skew, is the magnitude difference in differential propagation delay time between the positive going edge and the negative going edge of the same channel.

Note 16:  $t_{SKD2}$ . Channel to Channel Skew, is the difference in propagation delay  $(t_{PLHD} \text{ or } t_{PHLD})$  among all output channels in Broadcast mode (any one input to all outputs).

Note 17: t<sub>SKD3</sub>, Part to Part Skew, is defined as the difference between the same signal path of any two devices running at the same V<sub>CC</sub> and within 5°C of each other within the operating temperature range.

Note 18: Measured on a clock edge with a histogram and an acummulation of 1500 histogram hits. Input stimulus jitter is subtracted geometrically.

Note 19: Tested with a combination of the 1100000101 (K28.5+ character) and 0011111010 (K28.5- character) patterns. Input stimulus jitter is subtracted algebraically.

Note 20: Measured on an eye diagram with a histogram and an acummulation of 3500 histogram hits. Input stimulus jitter is subtracted.

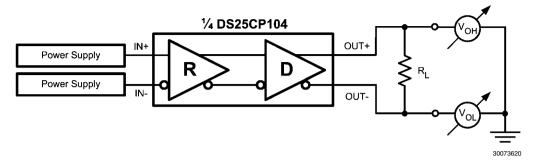

### **DC Test Circuits**

FIGURE 1. Differential Driver DC Test Circuit

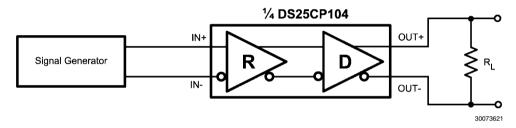

### **AC Test Circuits and Timing Diagrams**

FIGURE 2. Differential Driver AC Test Circuit

Note: DS25CP114 requires external  $100\Omega$  input termination.

FIGURE 3. Propagation Delay Timing Diagram

**FIGURE 4. LVDS Output Transition Times**

## **Pre-Emphasis and Equalization Test Circuits**

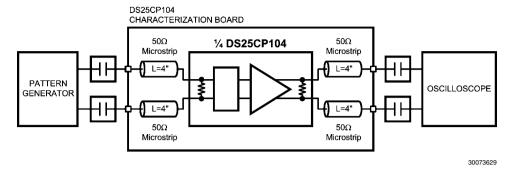

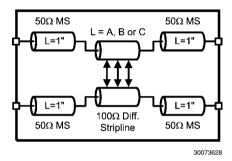

FIGURE 5. Jitter Performance Test Circuit

Note: DS25CP114 requires external 100  $\!\Omega$  input termination.

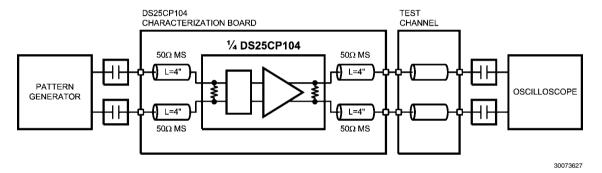

FIGURE 6. Pre-Emphasis Performance Test Circuit

Note: DS25CP114 requires external  $100\Omega$  input termination.

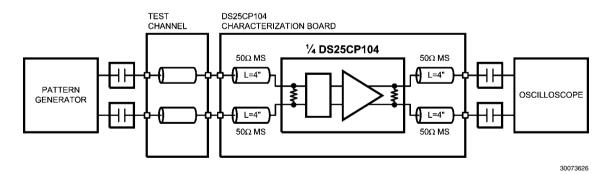

FIGURE 7. Equalization Performance Test Circuit

Note: DS25CP114 requires external  $100\Omega$  input termination.

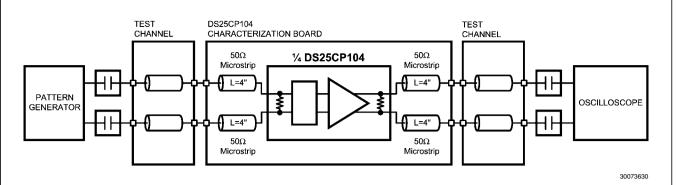

FIGURE 8. Pre-Emphasis and Equalization Performance Test Circuit

Note: DS25CP114 requires external  $100\Omega$  input termination.

FIGURE 9. Test Channel Block Diagram

#### **Test Channel Loss Characteristics**

The test channel was fabricated with Polyclad PCL-FR-370-Laminate/PCL-FRP-370 Prepreg materials (Dielectric constant of 3.7 and Loss Tangent of 0.02). The edge coupled differential striplines have the following geometries: Trace Width (W) = 5 mils, Gap (S) = 5 mils, Height (B) = 16 mils.

| Test Channel | Length   | Insertion Loss (dB) |         |          |          |          |          |

|--------------|----------|---------------------|---------|----------|----------|----------|----------|

|              | (inches) | 500 MHz             | 750 MHz | 1000 MHz | 1250 MHz | 1500 MHz | 1560 MHz |

| Α            | 10       | -1.2                | -1.7    | -2.0     | -2.4     | -2.7     | -2.8     |

| В            | 20       | -2.6                | -3.5    | -4.1     | -4.8     | -5.5     | -5.6     |

| С            | 30       | -4.3                | -5.7    | -7.0     | -8.2     | -9.4     | -9.7     |

| D            | 15       | -1.6                | -2.2    | -2.7     | -3.2     | -3.7     | -3.8     |

| E            | 30       | -3.4                | -4.5    | -5.6     | -6.6     | -7.7     | -7.9     |

| F            | 60       | -7.8                | -10.3   | -12.4    | -14.5    | -16.6    | -17.0    |

### **Functional Description**

The DS25CP104A and DS25CP114 are 3.125 Gbps 4x4 LVDS digital crosspoint switch optimized for high-speed signal routing and switching over lossy FR-4 printed circuit board backplanes and balanced cables. The DS25CP104A and DS25CP114 operate in two modes: Pin Mode (EN\_smb = 0) and SMBus Mode (EN\_smb = 1).

When in the Pin Mode, the switch is fully configurable with external pins. This is possible with two input select pins per output (e.g. S00 and S01 pins for OUT0). There is also one transmit pre-emphasis (PE) level select pin per output for switching the PE levels between Medium and Off settings and one receive equalization (EQ) level select pin per input for switching the EQ levels between Low and Off settings.

In the Pin Mode, feedback from the LOS (Loss Of Signal) monitor circuitry is not available (there is not an LOS output pin).

When in the SMBus Mode, the full switch configuration, four levels of transmit pre-emphasis (Off, Low, Medium and High), four levels of receive equalization (Off, Low, Medium and High) and SoftPWDN can be programmed via the SMBus interface. In addition, by using the SMBus interface, a user can obtain the feedback from the built-in LOS circuitry which detects an open inputs fault condition.

In the SMBus Mode, the S00 and S01 pins become SMBus clock (SCL) input and data (SDA) input pins respectively; the

S10, S11, S21 and S21 pins become the User-Set SMBus Slave Address input pins (ADDR0, 1, 2 and 3) while the S30 and S31 pins become non-functional (tieing these two pins to either H or L is recommended if the device will function only in the SMBus mode).

In the SMBus Mode, the PE and EQ select pins as well as the PWDN pin remain functional. How these pins function in each mode is explained in the following sections.

#### **OPERATION IN PIN MODE**

#### Power Up

In the Pin Mode, when the power is applied to the device power suppy pins, the DS25CP104A/DS25CP114 enters the Power Up mode when the  $\overline{PWDN}$  pin is set to logic H. When in the Power Down mode ( $\overline{PWDN}$  pin is set to logic L), all circuitry is shut down except the minimum required circuitry for the  $\overline{LOS}$  and SMBus Slave operation.

#### **Switch Configuration**

In the Pin Mode, the DS25CP104A/DS25CP114 operates as a fully pin-configurable crosspoint switch. The following truth tables illustrate how the swich can be configured with external pins.

#### **Switch Configuration Truth Tables**

TABLE 1. Input Select Pins Configuration for the Output OUT0

| S01 | S00 | INPUT SELECTED |

|-----|-----|----------------|

| 0   | 0   | IN0            |

| 0   | 1   | IN1            |

| 1   | 0   | IN2            |

| 1   | 1   | IN3            |

**TABLE 2. Input Select Pins Configuration for the Output OUT1**

| S11 | S10 | INPUT SELECTED |

|-----|-----|----------------|

| 0   | 0   | IN0            |

| 0   | 1   | IN1            |

| 1   | 0   | IN2            |

| 1   | 1   | IN3            |

**TABLE 3. Input Select Pins Configuration for the Output OUT2**

| S21 | S20 | INPUT SELECTED |

|-----|-----|----------------|

| 0   | 0   | IN0            |

| 0   | 1   | IN1            |

| 1   | 0   | IN2            |

| 1   | 1   | IN3            |

#### **TABLE 4. Input Select Pins Configuration for the Output OUT3**

| S31 | S30 | INPUT SELECTED |

|-----|-----|----------------|

| 0   | 0   | IN0            |

| 0   | 1   | IN1            |

| 1   | 0   | IN2            |

| 1   | 1   | IN3            |

#### **Setting Pre-Emphasis Levels**

The DS25CP104A/DS25CP114 has one PE level select pin per output for setting the transmit pre-emphasis to either

Medium or Off level. The following is the transmit pre-emphasis truth table.

**TABLE 5. Transmit Pre-Emphasis Truth Table**

| OUTPUT OUTn, n = {0, 1, 2, 3}        |                    |  |  |  |  |

|--------------------------------------|--------------------|--|--|--|--|

| Pre-Emphasis Control Pin (PEn) State | Pre-Emphasis Level |  |  |  |  |

| 0                                    | Off                |  |  |  |  |

| 1                                    | Medium             |  |  |  |  |

Transmit Pre-emphasis Level Selection for an Output OUTn

#### **Setting Equalization Levels**

The DS25CP104A/DS25CP114 has one EQ level select pin per input for setting the receive equalization to either Low or Off level. The following is the receive equalization truth table.

**TABLE 6. Receive Equalization Truth Table**

| INPUT INn, n = {0, 1, 2, 3}          |                    |  |  |  |  |

|--------------------------------------|--------------------|--|--|--|--|

| Equalization Control Pin (EQn) State | Equalization Level |  |  |  |  |

| 0                                    | Off                |  |  |  |  |

| 1                                    | Low                |  |  |  |  |

Receive Equalization Level Selection for an Input INn

#### **OPERATION IN SMBUS MODE**

The DS25CP104A/DS25CP114 operates as a slave on the System Management Bus (SMBus) when the EN\_smb pin is set to a high (1). Under these conditions, the SCL pin is a clock input while the SDA pin is a serial data input pin.

#### **Device Address**

Based on the SMBus 2.0 specification, the DS25CP104A/DS25CP114 has a 7-bit slave address. The three most sig-

nificant bits of the slave address are hard wired inside the DS25CP104A/DS25CP114 and are "101". The four least significant bits of the address are assigned to pins ADDR3-ADDR0 and are set by connecting these pins to GND for a low (0) or to VCC for a high (1). The complete slave address is shown in the following table:

#### **TABLE 7. Slave Address**

| 1   | 0 | 1 | ADDR3 | ADDR2 | ADDR1 | ADDR0 |

|-----|---|---|-------|-------|-------|-------|

| MSB |   |   |       |       |       | LSB   |

This slave address configuration allows up to sixteen DS25CP104A/DS25CP114 devices on a single SMBus bus.

#### **Transfer of Data via the SMBus**

During normal operation the data on SDA must be stable during the time when SCK is high.

There are three unique states for the SMBus:

**START:** A HIGH to LOW transition on SDA while SCK is high indicates a message START condition.

**STOP:** A LOW to HIGH transition on SDA while SCK is high indicates a message STOP condition.

**IDLE:** If SCK and SDA are both high for a time exceeding tBUF from the last detected STOP condition or if they are high for a total exceeding the maximum specification for tHIGH then the bus will transfer to the IDLE state.

#### **SMBus Transactions**

A transaction begins with the host placing the DS25CP104A SMBus into the START condition, then a byte (8 bits) is transferred, MSB first, followed by a ninth ACK bit. ACK bits are '0' to signify an ACK, or '1' to signify NACK, after this the host holds the SCL line low, and waits for the receiver to raise the SDA line as an ACKnowledge that the byte has been received.

#### Writing to a Register

To write a register, the following protocol is used (see SMBus 2.0 specification):

1) The Host drives a START condition, the 7-bit SMBus address, and a "0" indicating a WRITE.

- 2) The Device (Slave) drives an ACK bit ("0").

- 3) The Host drives the 8-bit Register Address.

- 4) The Device drives an ACK bit ("0").

- 5) The Host drives the 8-bit data byte.

- 6) The Device drives an ACK bit "0".

- 7) The Host drives a STOP condition.

The WRITE transaction is completed, the bus goes Idle and communication with other SMBus devices may now occur.

#### **Reading From a Register**

To read a register, the following protocol is used (see SMBus 2.0 specification):

- 1) The Host drives a START condition, the 7-bit SMBus address, and a "0" indicating a WRITE.

- 2) The Device (Slave) drives an ACK bit ("0").

- 3) The Host drives the 8-bit Register Address.

- 4) The Device drives an ACK bit ("0").

- 5) The Host drives a START condition.

- 6) The Host drives the 7-bit SMBus Address, and a "1" indicating a READ.

- 7) The Device drives an ACK bit "0".

- 8) The Device drives the 8-bit data value (register contents).

- 9) The Host drives a NACK bit "1" indicating end of READ transfer.

- 10) The Host drives a STOP condition.

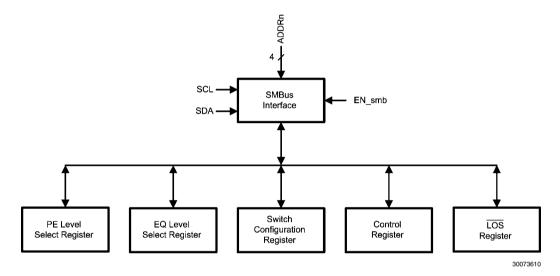

## **Register Descriptions**

There are five data registers in the DS25CP104A/DS25CP114 accessible via the SMBus interface.

**TABLE 8. SMBus Data Registers**

| Address<br>(hex) | Name                 | Access Description                              |                                                                      |  |

|------------------|----------------------|-------------------------------------------------|----------------------------------------------------------------------|--|

| 0                | Switch Configuration | R/W Switch Configuration Register               |                                                                      |  |

| 1                | PE Level Select      | R/W Transmit Pre-emphasis Level Select Register |                                                                      |  |

| 2                | EQ Level Select      | R/W Receive Equalization Level Select Register  |                                                                      |  |

| 3                | Control              | R/W                                             | R/W Powerdown, LOS Enable and Pin Control Register                   |  |

| 4                | LOS                  | RO                                              | Loss <b>O</b> f <b>S</b> ignal ( <del>LOS</del> ) Reporting Register |  |

FIGURE 10. Registers Block Diagram

#### **SWITCH CONFIGURATION REGISTER**

The Switch Configuration register is utilized to configure the switch. The following two tables show the Switch Configuration Register mapping and associated truth table.

| Bit    | Default | Bit Name       | Access | Description                                |

|--------|---------|----------------|--------|--------------------------------------------|

| D[1:0] | 00      | Input Select 0 | R/W    | Selects which input is routed to the OUT0. |

| D[3:2] | 00      | Input Select 1 | R/W    | Selects which input is routed to the OUT1. |

| D[5:4] | 00      | Input Select 2 | R/W    | Selects which input is routed to the OUT2. |

| D[7:6] | 00      | Input Select 3 | R/W    | Selects which input is routed to the OUT3. |

**TABLE 9. Switch Configuration Register Truth Table**

| D1 | D0 | Input Routed to the OUT0 |

|----|----|--------------------------|

| 0  | 0  | IN0                      |

| 0  | 1  | IN1                      |

| 1  | 0  | IN2                      |

| 1  | 1  | IN3                      |

The truth tables for the OUT1, OUT2, and OUT3 outputs are identical to this table.

The switch configuration logic has a SmartPWDN circuitry which automatically optimizes the device's power consumption based on the switch configuration (i.e. It places unused I/O blocks and other unused circuitry in the power down state).

#### PE LEVEL SELECT REGISTER

The PE Level Select register selects the pre-emphasis level for each of the outputs. The following two tables show the register mapping and associated truth table.

| Bit    | Default | Bit Name          | Access | Description                          |

|--------|---------|-------------------|--------|--------------------------------------|

| D[1:0] | 00      | PE Level Select 0 | R/W    | Sets pre-emphasis level on the OUT0. |

| D[3:2] | 00      | PE Level Select 1 | R/W    | Sets pre-emphasis level on the OUT1. |

| D[5:4] | 00      | PE Level Select 2 | R/W    | Sets pre-emphasis level on the OUT2. |

| D[7:6] | 00      | PE Level Select 3 | R/W    | Sets pre-emphasis level on the OUT3. |

#### **TABLE 10. PE Level Select Register Truth Table**

| D1 | D0 | Pre-Emphasis Level for the OUT0 |  |

|----|----|---------------------------------|--|

| 0  | 0  | Off                             |  |

| 0  | 1  | Low                             |  |

| 1  | 0  | Medium                          |  |

| 1  | 1  | High                            |  |

NOTE: The truth tables for the OUT1, OUT2, and OUT3 outputs are identical to this table.

#### **EQ LEVEL SELECT REGISTER**

The EQ Level Select register selects the equalization level for each of the inputs. The following two tables show the register mapping and associated truth table.

| Bit    | Bit Default Bit Name |                                                          | Access | Description                         |  |

|--------|----------------------|----------------------------------------------------------|--------|-------------------------------------|--|

| D[1:0] | 00                   | EQ Level Select 0 R/W Sets equalization level on the IN0 |        | Sets equalization level on the IN0. |  |

| D[3:2] | 00                   | EQ Level Select 1                                        | R/W    | Sets equalization level on the IN1. |  |

| D[5:4] | 00                   | EQ Level Select 2                                        | R/W    | Sets equalization level on the IN2. |  |

| D[7:6] | 00                   | EQ Level Select 3                                        | R/W    | Sets equalization level on the IN3. |  |

**TABLE 11. EQ Level Select Register Truth Table**

| D1 | D0 | Equalization Level for the IN0 |  |

|----|----|--------------------------------|--|

| 0  | 0  | Off                            |  |

| 0  | 1  | Low                            |  |

| 1  | 0  | Medium                         |  |

| 1  | 1  | High                           |  |

NOTE: The truth tables for the IN1, IN2, and IN3 outputs are identical to this table.

#### **CONTROL REGISTER**

The Control register enables SoftPWDN control, individual output power down (PWDNn) control, LOS Circuitry Enable control, PE Level Select Enable control and EQ Level Select Enable control via the SMBus. The following table shows the register mapping.

| Bit    | Default | Bit Name           | Access | Description                                                                                                                                                                                                                      |

|--------|---------|--------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[3:0] | 1111    | PWDNn              | R/W    | Writing a [0] to the bit D[n] will power down the output OUTn when either the PWDN pin OR the Control Register bit D[7] (SoftPWDN) is set to a high [1].                                                                         |

| D[4]   | 0       | Ignore_External_EQ | R/W    | Writing a [1] to the bit D[4] will ignore the state of the external EQ pins and will allow setting the EQ levels via the SMBus interface.                                                                                        |

| D[5]   | 0       | Ignore_External_PE | R/W    | Writing a [1] to the bit D[5] will ignore the state of the external PE pins and will allow setting the PE levels via the SMBus interface.                                                                                        |

| D[6]   | 0       | EN_LOS             | R/W    | Writing a [1] to the bit D[6] will enable the LOS circuitry and receivers on all four inputs. The SmartPWDN circuitry will not disable any of the inputs nor any supporting LOS circuitry depending on the switch configuration. |

| D[7]   | 0       | SoftPWDN           | R/W    | Writing a [0] to the bit D[7] will place the device into the power down mode. This pin is ORed together with the PWDN pin.                                                                                                       |

#### **TABLE 12. Power Modes Truth Table**

| PWDN        | SoftPWDN    | PWDNn       | Power Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|-------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0           | 0           | х           | Power Down Mode. In this mode, all circuitry is shut down except the minimum required circuitry for the LOS and SMBus Slave operation. The SMBus circuitry allows enabling the LOS circuitry and receivers on all inputs in this mode by setting the EN_LOS bit to a [1].                                                                                                                                                                                                                                                                                                                            |

| 0<br>1<br>1 | 1<br>0<br>1 | x<br>x<br>x | Power Up Mode. In this mode, the SmartPWDN circuitry will automatically power down any unused I/O and logic blocks and other supporting circuitry depending on the switch configuration.  An output will be enabled <b>only</b> when the SmartPWDN circuitry indicates that that particular output is needed for the particular switch configuration <b>and</b> the respective PWDNn bit has logic high [1].  An input will be enabled when the SmartPWDN circuitry indicates that that particular input is needed for the particular switch configuration <b>or</b> the EN_LOS bit is set to a [1]. |

#### **LOS REGISTER**

The LOS register reports an open inputs fault condition for each of the inputs. The following table shows the register mapping.

| Bit    | Default | Bit Name | Access | Description                                                                                                                      |

|--------|---------|----------|--------|----------------------------------------------------------------------------------------------------------------------------------|

| D[0]   | 0       | LOS0     | RO     | Reading a [0] from the bit D[0] indicates an open inputs fault condition on the INO. A [1] indicates presence of a valid signal. |

| D[1]   | 0       | LOS1     | RO     | Reading a [0] from the bit D[1] indicates an open inputs fault condition on the IN1. A [1] indicates presence of a valid signal. |

| D[2]   | 0       | LOS2     | RO     | Reading a [0] from the bit D[2] indicates an open inputs fault condition on the IN2. A [1] indicates presence of a valid signal. |

| D[3]   | 0       | LOS3     | RO     | Reading a [0] from the bit D[3] indicates an open inputs fault condition on the IN3. A [1] indicates presence of a valid signal. |

| D[7:4] | 0000    | Reserved | RO     | Reserved for future use. Returns undefined value when read.                                                                      |

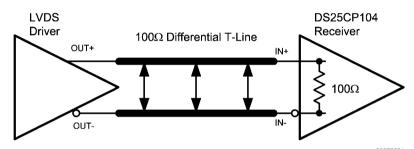

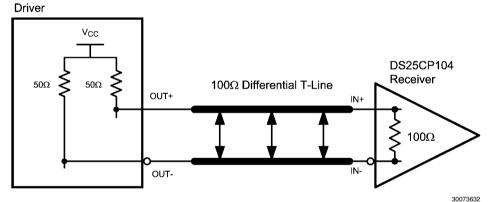

#### **INPUT INTERFACING**

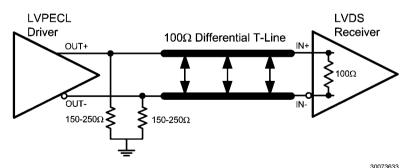

The DS25CP104A/DS25CP114 accepts differential signals and allows simple AC or DC coupling. With a wide common mode range, the DS25CP104A/DS25CP114 can be DC-coupled with all common differential drivers (i.e. LVPECL, LVDS, CML). The following three figures illustrate typical DC-coupled interface to common differential drivers.

The DS25CP104A inputs are internally terminated with a  $100\Omega$  resistor for optimal device performance, reduced component count, and minimum board space. External input terminations on the DS25CP114 need to be placed as close as possible to the device inputs to achieve equivalent AC performance. When all four inputs are utilized it may be necessary to alternate between the top and bottom layers to achieve the minimum device input to termination distance. It is rec-

ommended that SMT resistors sized 0402 or smaller be used and the mounting distance to the DS25CP114 pins kept under 200 mils.

When using the DS25CP114 in a limited multi-drop topology, any transmission line stubs should be kept very short to minimize any negative effects on signal quality. A single termination resistor or resistor network that matches the differential line impedance should be used. If DS25CP114 input pairs from two separate devices are to be connected to a single differential output, it is recommended that the DS25CP114 devices are mounted directly opposite of each other. One on top of the PCB and the other directly under the first on the bottom of the PCB, this keeps the distance between inputs equal to the PCB thickness.

Typical LVDS Driver DC-Coupled Interface to DS25CP104A Input

#### CML3.3V or CML2.5V

Typical CML Driver DC-Coupled Interface to DS25CP104A Input

Typical LVPECL Driver DC-Coupled Interface to DS25CP104A Input

Note: DS25CP114 requires external  $100\Omega$  input termination.

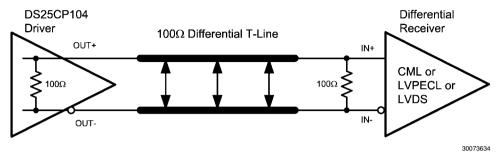

#### **OUTPUT INTERFACING**

The DS25CP104A/DS25CP114 outputs signals that are compliant to the LVDS standard. Its outputs can be DC-coupled to most common differential receivers. The following figure illustrates typical DC-coupled interface to common differential receivers and assumes that the receivers have high

impedance inputs. While most differential receivers have a common mode input range that can accomodate LVDS compliant signals, it is recommended to check respective receiver's data sheet prior to implementing the suggested interface implementation.

Typical Output DC-Coupled Interface to an LVDS, CML or LVPECL Receiver

### **Typical Performance Characteristics**

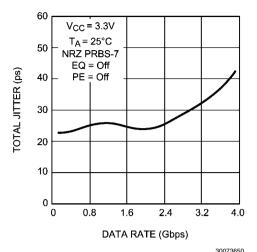

Total Jitter as a Function of Data Rate

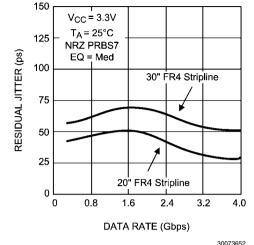

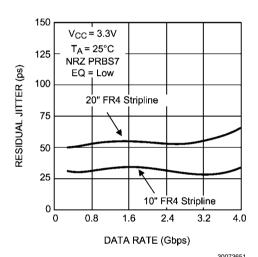

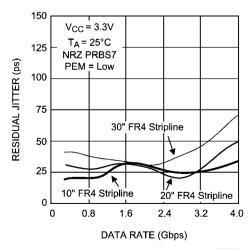

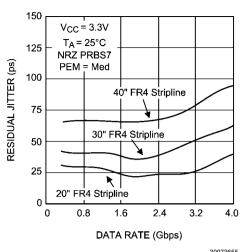

Residual Jitter as a Function of Data Rate, FR4 Stripline Length and EQ Level

Residual Jitter as a Function of Data Rate, FR4 Stripline Length and EQ Level

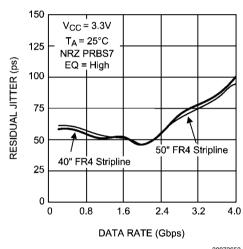

Residual Jitter as a Function of Data Rate, FR4 Stripline Length and EQ Level

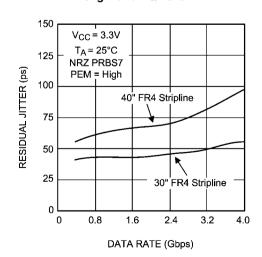

Residual Jitter as a Function of Data Rate, FR4 Stripline Length and PE Level

Residual Jitter as a Function of Data Rate, FR4 Stripline Length and PE Level

Residual Jitter as a Function of Data Rate, FR4 Stripline Length and PE Level

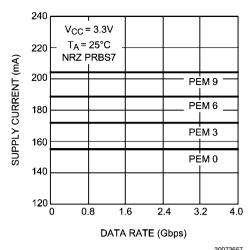

Supply Current as a Function of Data Rate and PE Level

### **Typical Performance**

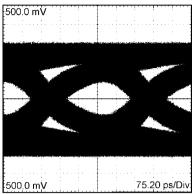

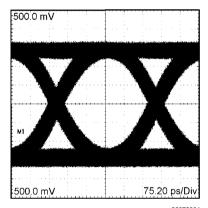

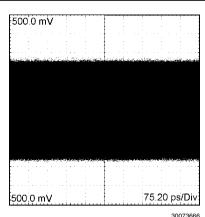

A 2.5 Gbps NRZ PRBS-23 without PE After 30" Differential FR-4 Stripline H: 75 ps / DIV, V: 100 mV / DIV

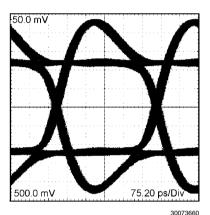

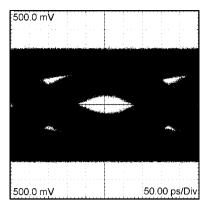

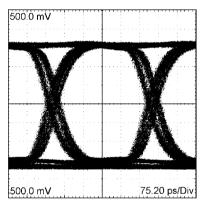

A 2.5 Gbps NRZ PRBS-23 with High PE After 2" Differential FR-4 Microstrip H: 75 ps / DIV, V: 100 mV / DIV

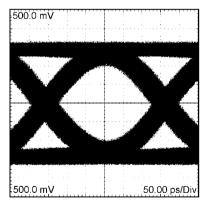

A 2.5 Gbps NRZ PRBS-23 with High PE After 30" Differential FR-4 Stripline H: 75 ps / DIV, V: 100 mV / DIV

A 3.125 Gbps NRZ PRBS-23 without PE After 30" Differential FR-4 Stripline H: 50 ps / DIV, V: 100 mV / DIV

A 3.125 Gbps NRZ PRBS-23 with High PE After 2" Differential FR-4 Microstrip H: 50 ps / DIV, V: 100 mV / DIV

A 3.125 Gbps NRZ PRBS-23 with High PE After 30" Differential FR-4 Stripline H: 50 ps / DIV, V: 100 mV / DIV

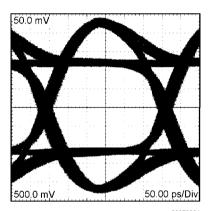

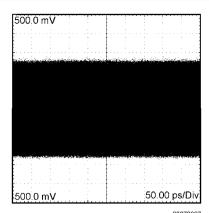

A 2.5 Gbps NRZ PRBS-23 without EQ After 60" Differential FR-4 Stripline H: 75 ps / DIV, V: 100 mV / DIV

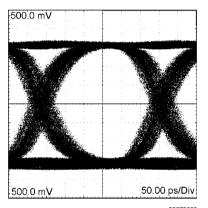

A 2.5 Gbps NRZ PRBS-23 with High EQ After 60" Differential FR-4 Stripline H: 75 ps / DIV, V: 100 mV / DIV

A 3.125 Gbps NRZ PRBS-23 without EQ After 60" Differential FR-4 Stripline H: 50 ps / DIV, V: 100 mV / DIV

A 3.125 Gbps NRZ PRBS-23 with High EQ After 60" Differential FR-4 Stripline H: 50 ps / DIV, V: 100 mV / DIV

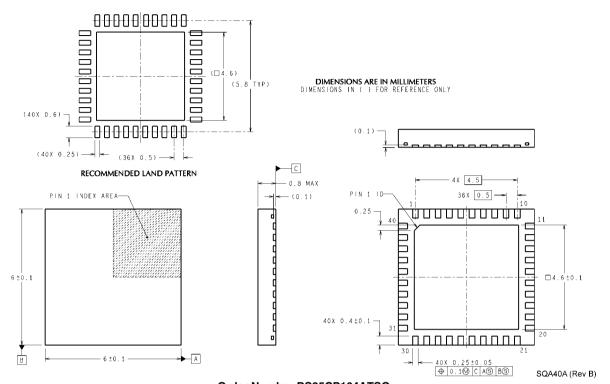

### Physical Dimensions inches (millimeters) unless otherwise noted

Order Number DS25CP104ATSQ

Order Number DS25CP114TSQ

NS Package Number SQA40A

(See AN-1187 for PCB Design and Assembly Recommendations)

### **Notes**

For more National Semiconductor product information and proven design tools, visit the following Web sites at: www.national.com

| Pr                             | oducts                       | Design Support                  |                                |  |

|--------------------------------|------------------------------|---------------------------------|--------------------------------|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools                  | www.national.com/webench       |  |

| Audio                          | www.national.com/audio       | App Notes                       | www.national.com/appnotes      |  |

| Clock and Timing               | www.national.com/timing      | Reference Designs               | www.national.com/refdesigns    |  |

| Data Converters                | www.national.com/adc         | Samples                         | www.national.com/samples       |  |

| Interface                      | www.national.com/interface   | Eval Boards                     | www.national.com/evalboards    |  |

| LVDS                           | www.national.com/lvds        | Packaging                       | www.national.com/packaging     |  |

| Power Management               | www.national.com/power       | Green Compliance                | www.national.com/quality/green |  |

| Switching Regulators           | www.national.com/switchers   | Distributors                    | www.national.com/contacts      |  |

| LDOs                           | www.national.com/ldo         | Quality and Reliability         | www.national.com/quality       |  |

| LED Lighting                   | www.national.com/led         | Feedback/Support                | www.national.com/feedback      |  |

| Voltage References             | www.national.com/vref        | Design Made Easy                | www.national.com/easy          |  |

| PowerWise® Solutions           | www.national.com/powerwise   | Applications & Markets          | www.national.com/solutions     |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                        | www.national.com/milaero       |  |

| Temperature Sensors            | www.national.com/tempsensors | SolarMagic™                     | www.national.com/solarmagic    |  |

| PLL/VCO                        | www.national.com/wireless    | PowerWise® Design<br>University | www.national.com/training      |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2011 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com

National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

#### Products Applications