### iinChip W3100A

Technical Datasheet v1.34

### Description

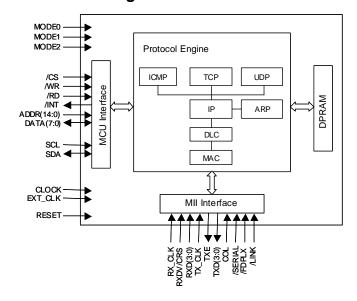

The iinChip W3100A is an LSI of hardware protocol stack that provides an easy, low-cost solution for high-speed Internet connectivity for digital devices by allowing simple installation of TCP/IP stack in the hardware.

The W3100A offers system designers a quick, easy way to add Ethernet networking functionality to any product. Implementing this LSI into a system can completely offload Internet connectivity and processing standard protocols from the system, thereby significantly reducing the software development cost.

The W3100A contains TCP/IP Protocol Stacks such as TCP, UDP, IP, ARP and ICMP protocols, as well as Ethernet protocols such as Data Link Control and MAC protocol.

The W3100A offers a socket API (Application Programming Interface) that is similar to the windows socket API. The chip provides a local bus interface and I<sup>2</sup>C for various MCUs and supports standard MII interface for under-layer Ethernet.

The W3100A can be applied to handheld devices including Internet phones, VoIP SOC chips, Internet MP3 players, handheld medical devices, LAN cards for Web servers, cellular phones and many other non-portable electronic devices such as large consumer electronic products.

#### ■ Features

- Hardware Internet protocols included:

TCP, IP Ver.4, UDP, ICMP, ARP

- Hardware Ethernet protocols included: DLC, MAC

- Supports 4 independent connections simultaneously

- Internal ICMP responds to PING commands

- Protocol processing speed: full-duplex 20 Mbps

- Intel MCU bus Interface

- I<sup>2</sup>C Interface

- Standard MII Interface for under-layer physical chip

- Socket API support for easy application programming

- Supports full-duplex mode

- Internal 16Kbytes Dual-port SRAM for data buffer

- 0.35 µm CMOS technology

- Wide operating voltage:

3.3V internal operation, 5V tolerant 3.3V IOs

- Small 64 Pin LQFP Package

#### ■ Block Diagram

### **Document History Information**

| Revision  | Date         | Description                                                                               |

|-----------|--------------|-------------------------------------------------------------------------------------------|

| Ver. 1.34 | Dec 14, 2005 | Modify RESET pin descriptions. (page 6)  Modify External Clock pin descriptions. (page 6) |

### **Table of Contents**

| Description                  |                                                | 1    |

|------------------------------|------------------------------------------------|------|

| Features                     |                                                | 1    |

| Block Diagram                | 1                                              | 1    |

| Pin Assignmer                | nt                                             | 4    |

| Signal Descrip               | tion                                           | 5    |

| Register Defin               | itions                                         | . 12 |

| 1. Control Reg               | isters                                         | . 12 |

| 2. System Reg                | isters                                         | . 17 |

| 3. Pointer Regi              | sters                                          | . 19 |

| 4. Channel Re                | gisters                                        | . 21 |

| Internal Memo                | ry and Registers                               | . 24 |

| Description of               | Functions                                      | . 26 |

| 1. Initialization            | of W3100A                                      | . 26 |

| 2. TCP Protoco               | lc                                             | . 26 |

| 3. UDP Protoco               | lo                                             | . 33 |

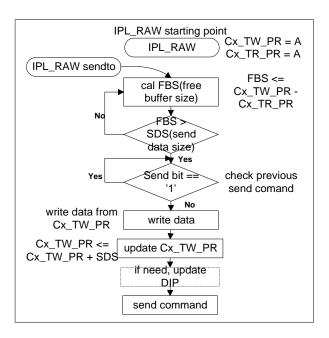

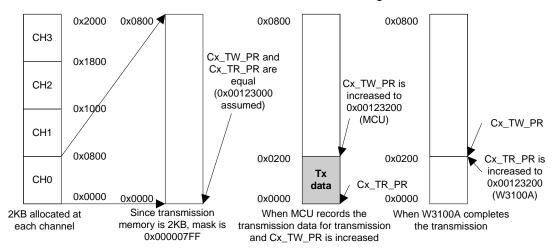

| 4. IP Layer RA               | W Mode                                         | . 37 |

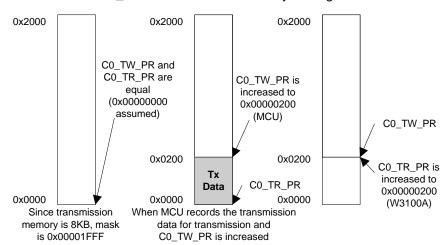

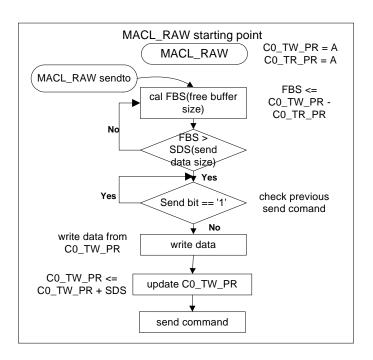

| 5. MAC Layer                 | RAW Mode                                       | . 38 |

| Application Info             | ormation                                       | . 42 |

| 1. Relationship              | between MCU Bus I/F Mode and Mode pin (M[2:0]) | . 42 |

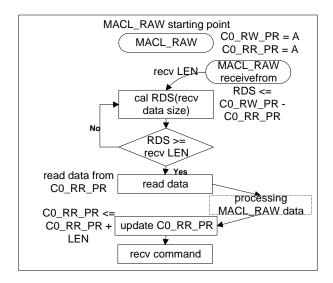

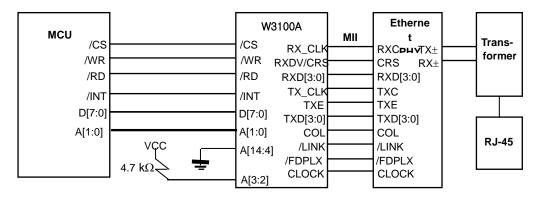

| 2. Direct Bus I/             | F Mode                                         | . 43 |

| 3. Indirect Bus              | I/F Mode                                       | . 43 |

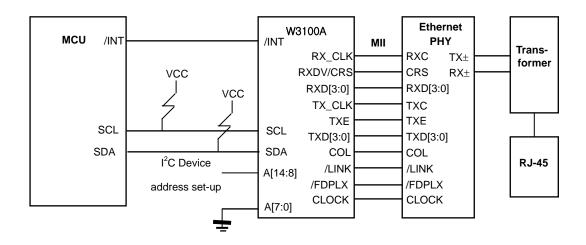

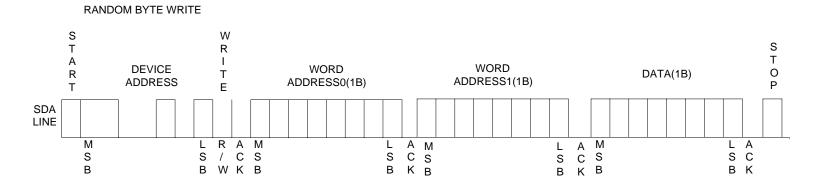

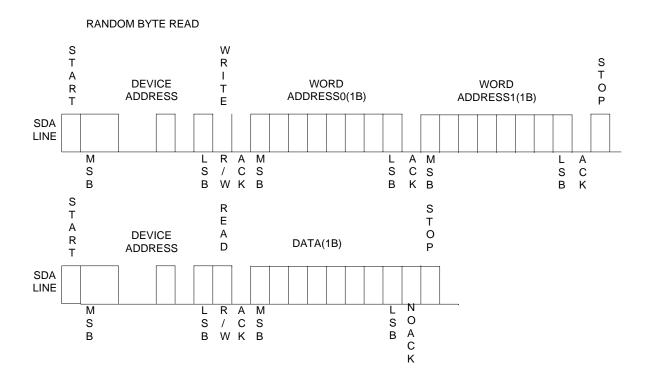

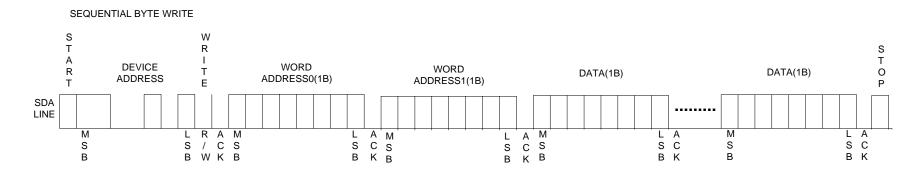

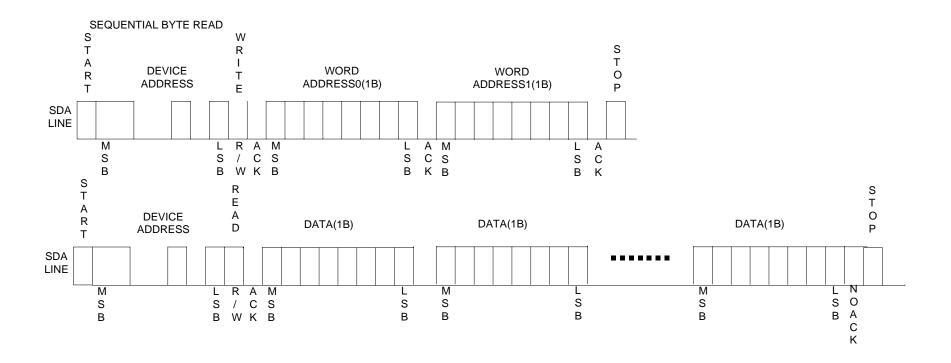

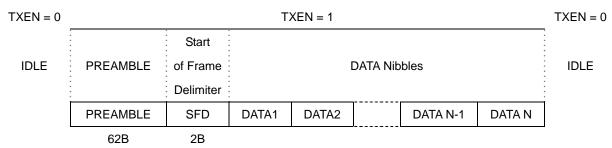

| 4. I <sup>2</sup> C I/F Mode | )                                              | . 45 |

| 5. Physical Lay              | ver Interface                                  | . 50 |

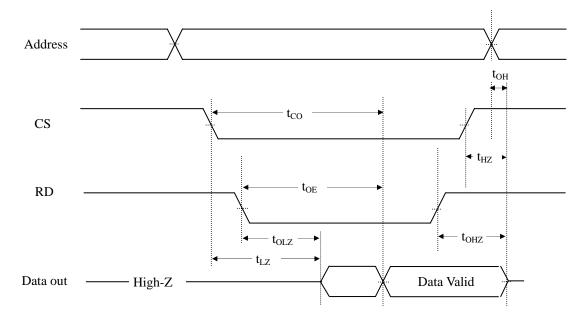

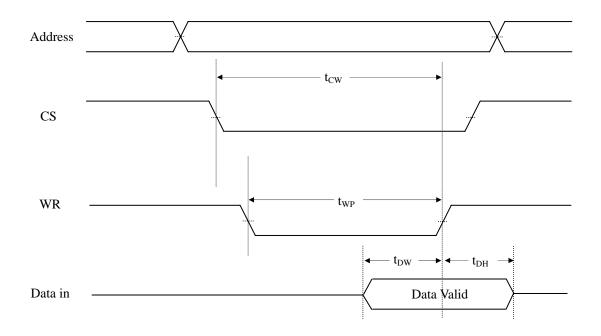

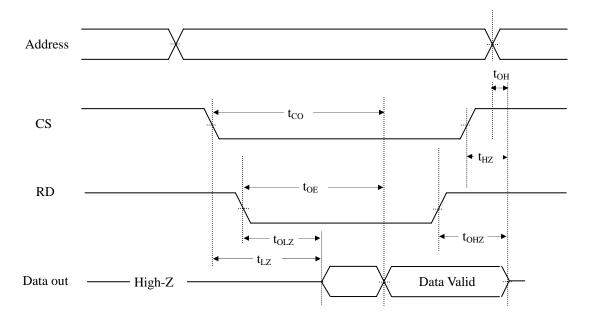

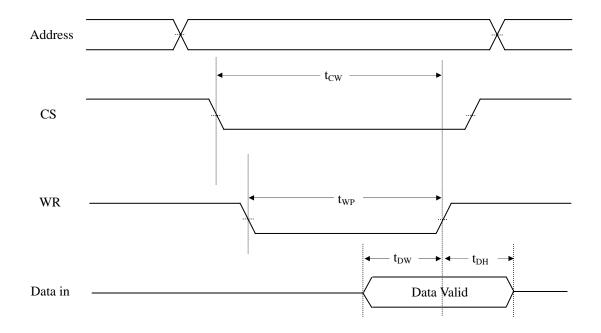

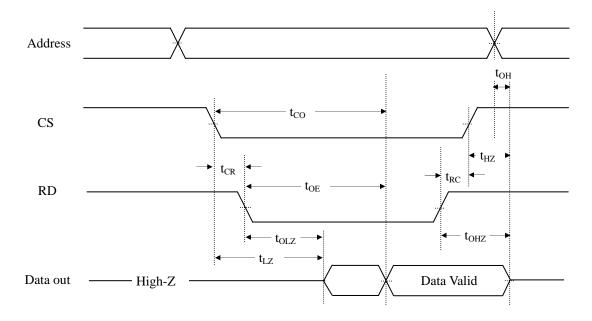

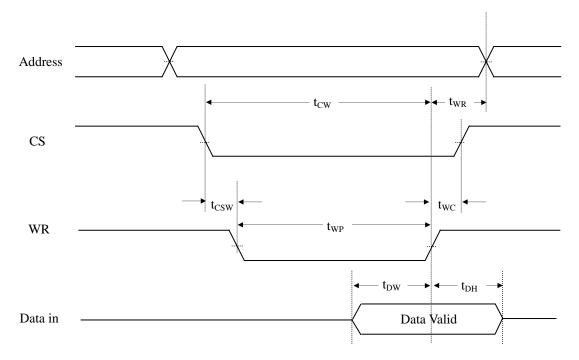

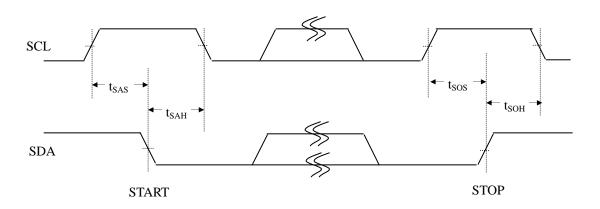

| Timing Diagrar               | ms                                             | . 52 |

| 1. Clocked mod               | de(CLOCK = 25MHz)                              | . 52 |

| 2. External clos             | cked mode(EXT_CLK = 50MHz)                     | . 54 |

| 3. Non-clocked               | I mode(CLOCK = 25MHz)                          | . 56 |

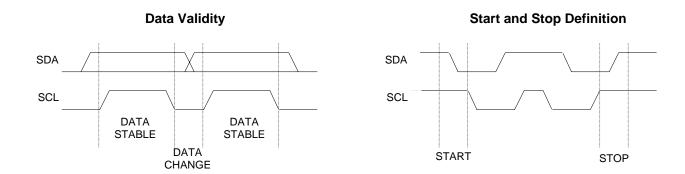

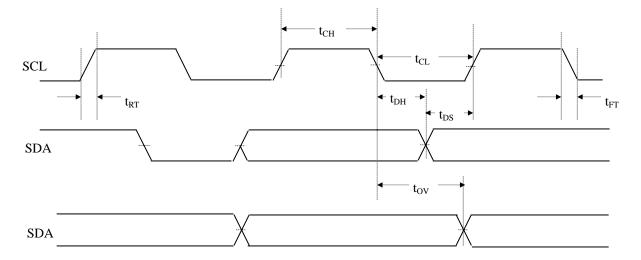

| 4. I <sup>2</sup> C mode(CI  | _OCK = 25MHz)                                  | . 59 |

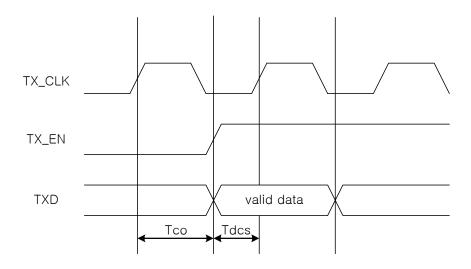

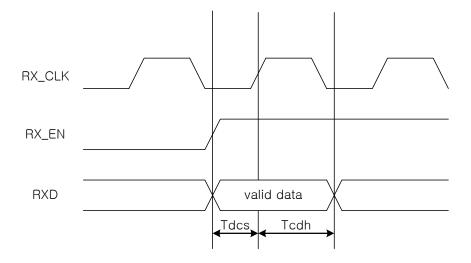

| 5. Media Indep               | endent Interface (MII)                         | . 61 |

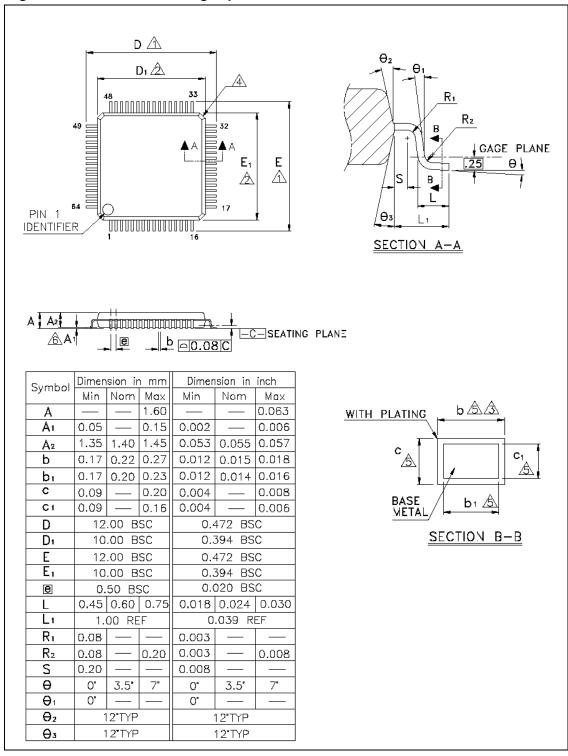

| Package Desc                 | ription                                        | . 63 |

| Appendix A.                  | Electrical Specifications                      | . 64 |

| Appendix B.                  | Programming Guide                              | . 66 |

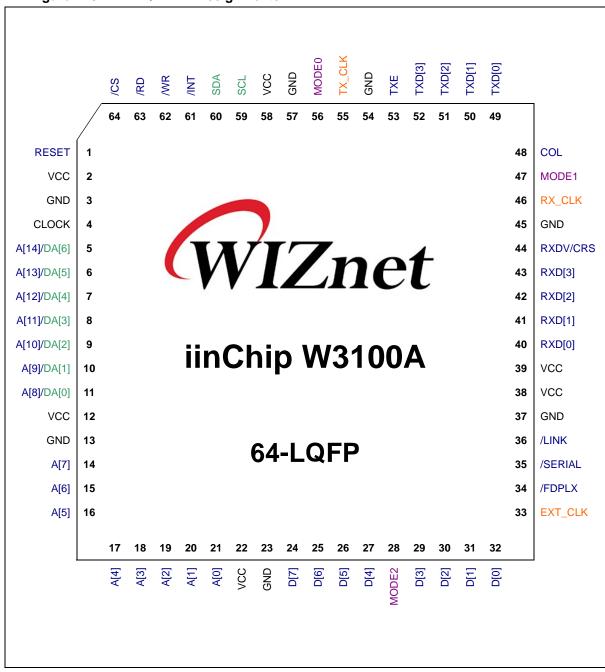

### ■ Pin Assignment

Figure 1: 64-Pin LQFP Pin Assignments

### ■ Signal Description

Table 1: W3100A MII Signal Description

| PIN# | Signal   | I/O | Description                                                            |

|------|----------|-----|------------------------------------------------------------------------|

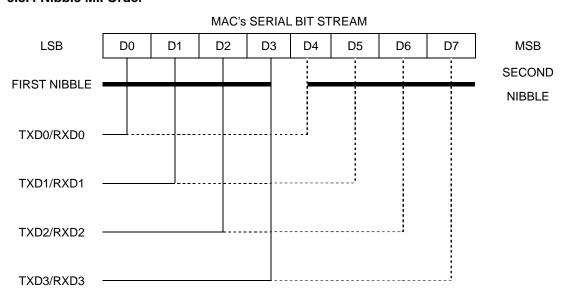

| 52   | TXD[3]   | 0   | TRANSMIT DATA: Nibble/Serial NRZ data output to the ENDEC              |

| 51   | TXD[2]   |     | that is valid on the rising edge of TX_CLK.                            |

| 50   | TXD[1]   |     | In serial mode, the TXD[0] pin is used as the serial data pin, and     |

| 49   | TXD[0]   |     | TXD[3:1] are ignored.                                                  |

| 53   | TXE      | 0   | TRANSMIT ENABLE: becomes active when the first nibble/serial           |

|      |          |     | data of the packet is valid on TXD[3:0] and goes low after the last    |

|      |          |     | nibble/serial data of the packet is clocked out of TXD[3:0]. This      |

|      |          |     | signal connects directly to the ENDEC (PHY device). This signal        |

|      |          |     | is active high.                                                        |

| 55   | TX_CLK   | I   | TRANSMIT CLOCK: TX_CLK is sourced by the PHY.                          |

|      |          |     | TX_CLK is 2.5 MHz in 10BASE-T Nibble mode, and 25 MHz in               |

|      |          |     | 100BASE-T Nibble mode.                                                 |

| 43   | RXD[3]   | ı   | RECEIVE DATA: Nibble wide receive data (synchronous to                 |

| 42   | RXD[2]   |     | RX_CLK) that must be driven on the falling edge of RX_CLK.             |

| 41   | RXD[1]   |     | In serial mode, the RXD[0] pin is used as the data input pin which is  |

| 40   | RXD[0]   |     | also clocked in on the falling edge of RX_CLK. and RXD[3:1] pins       |

|      |          |     | become don't cares.                                                    |

| 44   | RXDV/CRS | I   | Receive Data Valid: This pin's signal is asserted high when            |

|      |          |     | received data is present on the RXD[3:0] lines; the signal is          |

|      |          |     | deasserted at the end of the packet. The signal is valid on the rising |

|      |          |     | of the RXC.                                                            |

|      |          |     | CARRIER SENSE: signal provided by the ENDEC and indicates              |

|      |          |     | that carrier is present. This signal is active high.                   |

| 46   | RX_CLK   | I   | RECEIVE CLOCK: Re-synchronized clock from the ENDEC and                |

|      |          |     | indicates that carrier is present.                                     |

| 48   | COL      | I   | COLLISION DETECT: becomes active when a collision has been             |

|      |          |     | detected in Half Duplex modes.                                         |

|      |          |     | This signal is asynchronous, active high and ignored during full-      |

|      |          |     | duplex operation.                                                      |

Table 2: W3100A MCU Interface Signal Description

| PIN#  | Signal    | I/O | Description                                                                  |

|-------|-----------|-----|------------------------------------------------------------------------------|

| 5-11  | A[14-8] / | I   | ADDRESS PINS / DEVICE ADDRESS PINS                                           |

|       | DA[6-0]   |     | Used as Address[14 – 8] pin when set in MCU Bus Interface mode.              |

|       |           |     | Used as Device address[6 – 0] pin for I <sup>2</sup> C Interface when set in |

|       |           |     | I <sup>2</sup> C Interface mode.                                             |

| 14-21 | A[7-0]    | I   | ADDRESS PINS                                                                 |

| 24-27 | D[7-4]    | I/O | DATA PINS                                                                    |

| 29-32 | D[3-0]    |     |                                                                              |

| 61    | /INT      | 0   | INTERRUPT: Indicates that the W3100A requires MCU attention                  |

|    |     |     | after reception or transmission. The interrupt is cleared by writing to        |  |  |  |  |  |

|----|-----|-----|--------------------------------------------------------------------------------|--|--|--|--|--|

|    |     |     | the ISR (Interrupt Status Register). All interrupts are maskable by            |  |  |  |  |  |

|    |     |     | writing IMG (Interrupt Mask Register). This signal is active low.              |  |  |  |  |  |

| 64 | /CS | I   | CHIP SELECT: This signal is active low.                                        |  |  |  |  |  |

| 62 | /WR | I   | WRITE ENABLE: This signal is active low.                                       |  |  |  |  |  |

| 63 | /RD | I   | READ ENABLE: This signal is active low.                                        |  |  |  |  |  |

| 59 | SCL | I   | SCL: clock used by I <sup>2</sup> C when using I <sup>2</sup> C Interface mode |  |  |  |  |  |

|    |     |     | External Pull high (4.7 kΩ) is required.                                       |  |  |  |  |  |

| 60 | SDA | I/O | SDA: data used by I <sup>2</sup> C when using I <sup>2</sup> C Interface mode  |  |  |  |  |  |

|    |     |     | External Pull high (4.7 k $\Omega$ ) is required.                              |  |  |  |  |  |

Table 3: W3100A Miscellaneous Signal Description

| PIN# | Signal  | I/O | Description                                                              |

|------|---------|-----|--------------------------------------------------------------------------|

| 1    | RESET   | I   | RESET: Active High input that initializes or reinitializes the W3100A.   |

|      |         |     | Asserting this pin will force a reset process to occur which will result |

|      |         |     | in all internal registers reinitializing to their default states as      |

|      |         |     | specified for each bit in Internal Memory and Registers section, and     |

|      |         |     | all strapping options are reinitialized.                                 |

| 4    | CLOCK   | I   | CLOCK: primary clock required for internal operation of W3100A.          |

|      |         |     | In general, PHY driving clock is shared for saving cost.                 |

|      |         |     | (25MHz is recommended)                                                   |

|      |         |     | Note) Sharing crystal source clock with multiple devices may cause       |

|      |         |     | some troubles. In our reference design, we used Realtek's PHY and        |

|      |         |     | one crystal for both PHY and W3100A with verification.                   |

|      |         |     | But for other kind of PHY, please confirm safety prior to decision.      |

| 33   | EXT_CLK | - 1 | EXTERNAL CLOCK: supplementary clock used for MCU I/F of                  |

|      |         |     | W3100A.                                                                  |

|      |         |     | In external clocked mode, W3100A uses this clock to interface with       |

|      |         |     | MCU, and the access time of W3100A varies upon the frequency of          |

|      |         |     | the external clock. Refer to detailed timing diagram.                    |

|      |         |     | Frequency higher than 25MHz clock rate is granted.                       |

| 36   | /LINK   | I   | LINK: This is the signal generated by Ethernet PHY to indicate the       |

|      |         |     | PHY is connected to the Ethernet HUB device or other peer device.        |

|      |         |     | This is active low. W3100A can knows the status of physical line         |

|      |         |     | connection with this /LINK input. If /LINK is high, W3100A interprets    |

|      |         |     | the physical line is disconnected. It results in TCP timeout and         |

|      |         |     | connection close.                                                        |

|      |         |     | In special PHY case, LINK signal varies in time, which can be            |

|      |         |     | grounded.                                                                |

| 35   | /SERIAL | I   | 10BASE-T SERIAL/NIBBLE SELECT: With the selection of this                |

|      |         |     | active low input, transmit and receive data are exchanged serially at    |

|      |         |     | a 10 MHz clock rate on the least significant bits of the nibble-wide     |

|      |         |     | MII data buses, pins TXD[0] and RXD[0], respectively. This mode is       |

|      |         |     | intended for use with the W3100A connected to a PHY using a 10           |

|            |         |          | Mb/s serial interface.                                                  |                                                                         |           |                  |                                                |  |  |  |  |

|------------|---------|----------|-------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------|------------------|------------------------------------------------|--|--|--|--|

|            |         |          | There                                                                   | There is an internal pull-up resister for this pin. If this pin is left |           |                  |                                                |  |  |  |  |

|            |         |          | floated externally, then the device will be configured to normal        |                                                                         |           |                  |                                                |  |  |  |  |

|            |         |          | mode. This pin must be externally pulled low (typically x $k\Omega)$ in |                                                                         |           |                  |                                                |  |  |  |  |

|            |         |          | order                                                                   | to con                                                                  | figure th | ne W3100A        | for Serial MII operation.                      |  |  |  |  |

| 34         | /FDPLX  | I        | FULL                                                                    | _/HALF                                                                  | DUPL      | EX SELEC         | CT: This input pin selects Half/Full           |  |  |  |  |

|            |         |          | Duple                                                                   | ex oper                                                                 | ation.    |                  |                                                |  |  |  |  |

|            |         |          | This                                                                    | pin mu                                                                  | ist be e  | externally p     | ulled low (typically $x k\Omega$ ) in order to |  |  |  |  |

|            |         |          | confi                                                                   | gure th                                                                 | e W310    | 0A for Full I    | Duplex operation.                              |  |  |  |  |

|            |         |          | 0 = F                                                                   | ull Dup                                                                 | lex       |                  |                                                |  |  |  |  |

|            |         |          | 1 = H                                                                   | alf Dup                                                                 | olex      |                  |                                                |  |  |  |  |

| 28, 47, 56 | MODE[2- | I        | MOD                                                                     | E SEL                                                                   | ECT: Th   | his input pir    | selects MCU I/F type and operating             |  |  |  |  |

|            | 0]      |          | mode                                                                    | of W3                                                                   | 100A.     |                  |                                                |  |  |  |  |

|            | _       |          | Since                                                                   | each                                                                    | pin is p  | ositioned a      | as pull-down internally, clock mode -          |  |  |  |  |

|            |         |          |                                                                         |                                                                         |           |                  | when the connection is not made.               |  |  |  |  |

|            |         |          | M2                                                                      | M1                                                                      | MO        |                  | Description                                    |  |  |  |  |

|            |         |          | 0                                                                       | 0                                                                       | 0         | Clocked          | Mode where MCU Bus signal is                   |  |  |  |  |

|            |         |          |                                                                         |                                                                         |           | mode             | analyzed by W3100A by using the                |  |  |  |  |

|            |         |          |                                                                         |                                                                         |           |                  | clock when MCU Bus I/F is in                   |  |  |  |  |

|            |         |          |                                                                         |                                                                         |           |                  | use.                                           |  |  |  |  |

|            |         |          | 0                                                                       | 0                                                                       | 1         | External         | Mode where MCU Bus signal is                   |  |  |  |  |

|            |         |          |                                                                         |                                                                         |           | clocked          | analyzed by W3100A by using the                |  |  |  |  |

|            |         |          |                                                                         |                                                                         |           | mode             | external clock when MCU Bus I/F                |  |  |  |  |

|            |         |          |                                                                         |                                                                         |           |                  | is in use.                                     |  |  |  |  |

|            |         |          | 0                                                                       | 1                                                                       | 0         | Non-             | Mode where MCU bus signal is                   |  |  |  |  |

|            |         |          |                                                                         |                                                                         |           | clocked          | used directly by W3100A when                   |  |  |  |  |

|            |         |          |                                                                         |                                                                         |           | mode             | MCU Bus I/F is in use.                         |  |  |  |  |

|            |         |          | 0                                                                       | 1                                                                       | 1         | I <sup>2</sup> C | Mode using I <sup>2</sup> C for MCU I/F.       |  |  |  |  |

|            |         |          |                                                                         |                                                                         |           | mode             |                                                |  |  |  |  |

|            |         |          | 1                                                                       | Х                                                                       | Х         | Test             | Mode used for testing at the plant.            |  |  |  |  |

|            |         |          |                                                                         |                                                                         |           | mode             | Not to be used by regular users.               |  |  |  |  |

|            |         |          |                                                                         | Thous I not to be used by regular users.                                |           |                  |                                                |  |  |  |  |

|            |         |          | Clock                                                                   | Clocked mode, External clocked mode and Non-clocked mode are            |           |                  |                                                |  |  |  |  |

|            |         |          |                                                                         |                                                                         |           |                  | 3100A when MCU Bus I/F is in use.              |  |  |  |  |

|            |         |          |                                                                         |                                                                         |           |                  | and use it by analyzing the MCU bus            |  |  |  |  |

|            |         |          | timing                                                                  |                                                                         |           |                  | m for each mode for more detail.               |  |  |  |  |

| ļ          | ļ       | <u> </u> | ь.                                                                      | uming. Refer to uming diagram for each mode for more detail.            |           |                  |                                                |  |  |  |  |

Table 4: W3100A Power Supply Signal Description

| PIN#        | Signal | I/O | Description                                              |

|-------------|--------|-----|----------------------------------------------------------|

| 2, 12, 22,  | VCC    |     | POSITIVE 3.3V SUPPLY PINS                                |

| 38, 39, 58  |        |     |                                                          |

| 3, 13, 23,  | GND    |     | NEGATIVE (GROUND) SUPPLY PINS: a decoupling capacitor is |

| 37, 45, 54, |        |     | recommended to be connected between the Vcc and GND pins |

| 57          |        |     |                                                          |

Table5. W3100A Registers Map

| Address     | Register |                     | Bit Definitions |         |         |        |             |           |          |  |  |

|-------------|----------|---------------------|-----------------|---------|---------|--------|-------------|-----------|----------|--|--|

| 0x00        | C0_CR    | S/W Reset           | Recv            | Send    | Close   | Listen | Connect     | Sock_Init | Sys_Init |  |  |

| 0x01        | C1_CR    | Memory Test         | Recv            | Send    | Close   | Listen | Connect     | Sock_Init |          |  |  |

| 0x02        | C2_CR    |                     | Recv            | Send    | Close   | Listen | Connect     | Sock_Init |          |  |  |

| 0x03        | C3_CR    |                     | Recv            | Send    | Close   | Listen | Connect     | Sock_Init |          |  |  |

| 0x04        | C0_ISR   |                     | Recv_OK         | Send_OK | Timeout | Closed | Established | SInit_OK  | Init_OK  |  |  |

| 0x05        | C1_ISR   |                     | Recv_OK         | Send_OK | Timeout | Closed | Established | SInit_OK  |          |  |  |

| 0x06        | C2_ISR   |                     | Recv_OK         | Send_OK | Timeout | Closed | Established | SInit_OK  |          |  |  |

| 0x07        | C3_ISR   |                     | Recv_OK         | Send_OK | Timeout | Closed | Established | SInit_OK  |          |  |  |

| 0x08        | IR       | C3R                 | C2R             | C1R     | C0R     | C3     | C2          | C1        | C0       |  |  |

| 0x09        | IMR      | IM_C3R              | IM_C2R          | IM_C1R  | IM_C0R  | IM_C3  | IM_C2       | IM_C1     | IM_C0    |  |  |

| 0x0A - 0x0B | Reserved |                     |                 |         |         |        |             |           |          |  |  |

| 0x0C        | IDM_OR   | IND_EN              |                 |         |         |        |             | L/B       | AUTO_INC |  |  |

| 0x0D        | IDM_AR0  | Indirect bus I/F mo | de Address0 R   | egister |         |        |             |           |          |  |  |

| 0x0E        | IDM_AR1  | Indirect bus I/F mo | de Address1 R   | egister |         |        |             |           |          |  |  |

| 0x0F        | IDM_DR   | Indirect bus I/F mo | de Data Regist  | er      |         |        |             |           |          |  |  |

| 0x10 - 0x13 | C0_RW_PR | Channel 0 Rx Writ   | e Pointer Regis | ter     |         |        |             |           |          |  |  |

| 0x14 - 0x17 | C0_RR_PR | Channel 0 Rx Rea    | d Pointer Regis | ter     |         |        |             |           |          |  |  |

| 0x18 – 0x1B | C0_TA_PR | Channel 0 Tx ACK    | Pointer Registo | er      |         |        |             |           |          |  |  |

| 0x1C - 0x1F | C1_RW_PR | Channel 1 Rx Writ   | e Pointer Regis | ter     |         |        |             |           |          |  |  |

| 0x20 - 0x23 | C1_RR_PR | Channel 1 Rx Rea    | d Pointer Regis | ter     |         |        |             |           |          |  |  |

| 0x24 - 0x27 | C1_TA_PR | Channel 1 Tx ACK    | Pointer Registo | er      |         |        |             |           |          |  |  |

| 0x28 - 0x2B | C2_RW_PR | Channel 2 Rx Write Pointer Register |

|-------------|----------|-------------------------------------|

| 0x2C - 0x2F | C2_RR_PR | Channel 2 Rx Read Pointer Register  |

| 0x30 - 0x33 | C2_TA_PR | Channel 2 Tx ACK Pointer Register   |

| 0x34 - 0x37 | C3_RW_PR | Channel 3 Rx Write Pointer Register |

| 0x38 - 0x3B | C3_RR_PR | Channel 3 Rx Read Pointer Register  |

| 0x3C - 0x3F | C3_TA_PR | Channel 3 Tx ACK Pointer Register   |

| 0x40 - 0x43 | C0_TW_PR | Channel 0 Tx Write Pointer Register |

| 0x44 - 0x47 | C0_TR_PR | Channel 0 Tx Read Pointer Register  |

| 0x48 - 0x4B | Reserved |                                     |

| 0x4C - 0x4F | C1_TW_PR | Channel 1 Tx Write Pointer Register |

| 0x50 - 0x53 | C1_TR_PR | Channel 1 Tx Read Pointer Register  |

| 0x54 - 0x57 | Reserved |                                     |

| 0x58 – 0x5B | C2_TW_PR | Channel 2 Tx Write Pointer Register |

| 0x5C - 0x5F | C2_TR_PR | Channel 2 Tx Read Pointer Register  |

| 0x60 - 0x63 | Reserved |                                     |

| 0x64 - 0x67 | C3_TW_PR | Channel 3 Tx Write Pointer Register |

| 0x68 – 0x6B | C3_TR_PR | Channel 3 Tx Read Pointer Register  |

| 0x6C - 0x7F | Reserved |                                     |

| 0x80 - 0x83 | GAR      | Gateway Address Register            |

| 0x84 - 0x87 | SMR      | Subnet Mask Register                |

| 0x88 – 0x8D | SHAR     | Source Hardware Address Register    |

| 0x8E - 0x91 | SIPR     | Source IP Address Register          |

| 0x92 - 0x93 | IRTR     | Initial Retry Time-value Register   |

|             |          |                                     |

| 0x94        | RCR      |                                |                    |                | TC4   | TC3 | TC2      | TC1      | TC0      |  |

|-------------|----------|--------------------------------|--------------------|----------------|-------|-----|----------|----------|----------|--|

| 0x95        | RMSR     | Rx data Memory Size Register   |                    |                |       |     |          |          |          |  |

| 0x96        | TMSR     | Tx data Memory S               | ize Register       |                |       |     |          |          |          |  |

| 0x97 – 0x9F | Reserved |                                |                    |                |       |     |          |          |          |  |

| 0xA0        | C0_SSR   | Channel 0 Socket               | Status Register    |                |       |     |          |          |          |  |

| 0xA1        | C0_SOPR  | Broadcast/ERR                  | NDTimeout/B        | NDAck          | SWS/P |     | Protocol | Protocol | Protocol |  |

| 0xA2 - 0xA7 | Reserved |                                |                    |                |       |     |          |          |          |  |

| 0xA8 – 0xAB | C0_DIR   | Channel 0 Destina              | ation IP Address   | Register       |       |     |          |          |          |  |

| 0xAC – 0xAD | C0_DPR   | Channel 0 Destina              | ation Port Registe | er             |       |     |          |          |          |  |

| 0xAE – 0xAF | C0_SPR   | Channel 0 Source               | Port Register      |                |       |     |          |          |          |  |

| 0xB0        | C0_IPR   | Channel 0 IP Protocol Register |                    |                |       |     |          |          |          |  |

| 0xB1        | C0_TOSR  | Channel 0 TOS (ty              | pe of service) R   | egister        |       |     |          |          |          |  |

| 0xB2 - 0xB3 | C0_MSSR  | Channel 0 MSS (n               | naximum segme      | nt size) Regis | ster  |     |          |          |          |  |

| 0xB4 - 0xB7 | Reserved |                                |                    |                |       |     |          |          |          |  |

| 0xB8        | C1_SSR   | Channel 1 Socket               | Status Register    |                |       |     |          |          |          |  |

| 0xB9        | C1_SOPR  | Broadcast                      | NDTimeout          | NDAck          | SWS   |     | Protocol | Protocol | Protocol |  |

| 0xBA – 0xBF | Reserved |                                |                    |                |       |     |          |          |          |  |

| 0xC0 - 0xC3 | C1_DIR   | Channel 1 Destina              | ation IP Address   | Register       |       |     |          |          |          |  |

| 0xC4 - 0xC5 | C1_DPR   | Channel 1 Destina              | ation Port Registe | ər             |       |     |          |          |          |  |

| 0xC6 - 0xC7 | C1_SPR   | Channel 1 Source               | Port Register      |                |       |     |          |          |          |  |

| 0xC8        | C1_IPR   | Channel 1 IP Prote             | ocol Register      |                |       |     |          |          |          |  |

| 0xC9        | C1_TOSR  | Channel 1 TOS (ty              | pe of service) R   | egister        |       |     |          |          |          |  |

| 0xCA - 0xCB | C1_MSSR  | Channel 1 MSS (n               | naximum segme      | nt size) Regis | ster  |     |          |          |          |  |

| 0xCC - 0xCF | Reserved |                                          |                                               |                |      |  |          |          |          |  |

|-------------|----------|------------------------------------------|-----------------------------------------------|----------------|------|--|----------|----------|----------|--|

| 0xD0        | C2_SSR   | Channel 2 Socket                         | Channel 2 Socket Status Register              |                |      |  |          |          |          |  |

| 0xD1        | C2_SOPR  | Broadcast                                | NDTimeout                                     | NDAck          | SWS  |  | Protocol | Protocol | Protocol |  |

| 0xD2 - 0xD7 | Reserved |                                          |                                               |                |      |  |          |          |          |  |

| 0xD8 – 0xDB | C2_DIR   | Channel 2 Destina                        | ation IP Address                              | Register       |      |  |          |          |          |  |

| 0xDC –      | C2_DPR   | Channel 2 Destina                        | ation Port Regist                             | er             |      |  |          |          |          |  |

| 0xDD        |          |                                          |                                               |                |      |  |          |          |          |  |

| 0xDE – 0xDF | C2_SPR   | Channel 2 Source                         | Channel 2 Source Port Register                |                |      |  |          |          |          |  |

| 0xE0        | C2_IPR   | Channel 2 IP Protocol Register           |                                               |                |      |  |          |          |          |  |

| 0xE1        | C2_TOSR  | Channel 2 TOS (type of service) Register |                                               |                |      |  |          |          |          |  |

| 0xE2 - 0xE3 | C2_MSSR  | Channel 2 MSS (n                         | Channel 2 MSS (maximum segment size) Register |                |      |  |          |          |          |  |

| 0xE4 - 0xE7 | Reserved |                                          |                                               |                |      |  |          |          |          |  |

| 0xE8        | C3_SSR   | Channel 3 Socket                         | Status Register                               |                |      |  |          |          |          |  |

| 0xE9        | C3_SOPR  | Broadcast                                | NDTimeout                                     | NDAck          | SWS  |  | Protocol | Protocol | Protocol |  |

| 0xEA - 0xEF | Reserved |                                          |                                               |                |      |  |          |          |          |  |

| 0xF0 - 0xF3 | C3_DIR   | Channel 3 Destina                        | ation IP Address                              | Register       |      |  |          |          |          |  |

| 0xF4 - 0xF5 | C3_DPR   | Channel 3 Destina                        | ation Port Regist                             | er             |      |  |          |          |          |  |

| 0xF6 - 0xF7 | C3_SPR   | Channel 3 Source                         | Port Register                                 |                |      |  |          |          |          |  |

| 0xF8        | C3_IPR   | Channel 3 IP Prote                       | ocol Register                                 |                |      |  |          |          |          |  |

| 0xF9        | C3_TOSR  | Channel 3 TOS (ty                        | pe of service) R                              | egister        |      |  |          |          |          |  |

| 0xFA – 0xFB | C3_MSSR  | Channel 3 MSS (n                         | naximum segme                                 | nt size) Regis | ster |  |          |          |          |  |

| 0xFC - 0xFF | Reserved |                                          |                                               |                |      |  |          |          |          |  |

#### Register Definitions.

Register sets are categorized into (i) control registers related to command, status and interrupt, (ii) system registers for gateway address, subnet mask, source IP, source HA (Hardware Address) and timeout value, (iii) pointer registers for managing to send, receive data, and (iv) channel registers that control operation of each channel. R/W access to reserved register is not allowed, and also, writing on read-only register is not allowed.

#### 1. Control Registers

#### C0\_CR (Channel 0 Command Register) [R/W, 0x00]

This register commands Channel 0 socket to initialize, connect, close, transmit and receive data. Sys\_Init command is used to set the gateway, subnet mask, source IP and source H/W Address. The same command is used to close the socket in all channels.

Sock\_Init, Connect, Listen, Close, Send and Recv are used when initializing, establishing a connection, terminating a connection, sending and receiving data for Channel 0 socket. Each corresponding bit is automatically cleared after executing the command.

Sock\_Init command opens the corresponding Channel in TCP, UDP, RAW mode according to the protocol value as set at C0\_SOPR (Channel 0 Socket Option Protocol Register).

MCU can initialize the internal setting value of the chip by using S/W Reset.

Each bit in this register is automatically cleared after executing the command.

| 7         | 6    | 5    | 4     | 3      | 2       | 1         | 0        |

|-----------|------|------|-------|--------|---------|-----------|----------|

| S/W Reset | Recv | Send | Close | Listen | Connect | Sock_Init | Sys_Init |

| Bit | Symbol    | Description                                                             |

|-----|-----------|-------------------------------------------------------------------------|

| D0  | Sys_Init  | Command to set Gateway IP Address, Subnet Mask, Source H/W Address,     |

|     |           | Source IP Address                                                       |

| D1  | Sock_Init | Command to set corresponding protocol at C0_SOPR and open Channel 0     |

|     |           | socket                                                                  |

| D2  | Connect   | Command for Channel 0 socket to make a connection to the server         |

| D3  | Listen    | Command to stand by for connection when Channel 0 socket acts in server |

|     |           | mode                                                                    |

| D4  | Close     | Command to terminate connection and close Channel 0 socket              |

| D5  | Send      | Command to transmit Channel 0 socket data                               |

| D6  | Recv      | Command to receive Channel 0 socket data                                |

| D7  | S/W Reset | S/W Reset command                                                       |

#### C1\_CR (Channel 1 Command Register) [R/W, 0x01]

This register commands Channel 1 Socket to initialize, connect, close, transmit and receive data.

Sock\_Init, Connect, Listen, Close, Send and Recv are used when initializing, establishing a connection, terminating a connection, sending and receiving data for Channel 1 socket. Each corresponding bit is automatically cleared after executing the command.

Memory test command is used to verify transmission and reception memory where MCU reads and writes for the transmission and reception memory. Set memory test bit to '1' to become toggled as '0', '1' and W3100A acts in memory test mode when in '1'. Memory test bit needs to become set at '0' in order for W3100A to execute normal data transmission and reception.

| 7           | 6    | 5    | 4     | 3      | 2       | 1         | 0 |

|-------------|------|------|-------|--------|---------|-----------|---|

| Memory Test | Recv | Send | Close | Listen | Connect | Sock_Init |   |

| Bit | Symbol    | Description                                                             |

|-----|-----------|-------------------------------------------------------------------------|

| D0  |           | Reserved                                                                |

| D1  | Sock_Init | Sets corresponding protocol at C1_SOPR and opens Channel 1 socket       |

| D2  | Connect   | Command for Channel 1 socket to act in client mode to make a connection |

|     |           | to the server                                                           |

| D3  | Listen    | Command to stand by for connection when Channel 1 socket acts in server |

|     |           | mode                                                                    |

| D4  | Close     | Command to terminate connection and close Channel 1 socket              |

| D5  | Send      | Command to transmit Channel 1 socket data                               |

| D6  | Recv      | Command to receive Channel 1 socket data                                |

| D7  | Memory    | Command to set memory test mode                                         |

|     | Test      |                                                                         |

#### C2\_CR, C3\_CR (Channel 2, 3 Command Register) [R/W, 0x02, 0x03]

This register commands each Channel 2, 3 sockets to initialize, connect, close, transmit and receive data.

Sock\_Init, Connect, Listen, Close, Send and Recv are used when initializing, establishing a connection, terminating a connection, sending and receiving data for corresponding socket. Each corresponding bit is automatically cleared after executing the command.

| 7 | 6    | 5    | 4     | 3      | 2       | 1         | 0 |

|---|------|------|-------|--------|---------|-----------|---|

|   | Recv | Send | Close | Listen | Connect | Sock_Init |   |

| Bit | Symbol | Description |

|-----|--------|-------------|

|-----|--------|-------------|

| D0 |           | Reserved                                                                 |

|----|-----------|--------------------------------------------------------------------------|

| D1 | Sock_Init | Sets corresponding protocol at Cx_SOPR and opens corresponding channel   |

|    |           | socket                                                                   |

| D2 | Connect   | Command for corresponding channel socket to act in client mode to make a |

|    |           | connection to the server                                                 |

| D3 | Listen    | Command to stand by for connection when corresponding channel socket     |

|    |           | acts in server mode                                                      |

| D4 | Close     | Command to terminate connection and close corresponding channel socket   |

| D5 | Send      | Command to transmit corresponding channel socket data                    |

| D6 | Recv      | Command to receive corresponding channel socket data                     |

| D7 |           | Reserved                                                                 |

#### C0\_ISR (Channel 0 Interrupt Status Register) [R, 0x04]

This register notifies the outcome of Channel 0 socket command.

This register becomes cleared as 0x00 by read operation.

Init\_OK notifies the completion of Sys\_Init command.

Established notifies the completion of a connection executed by connection set-up command (Connect, Listen).

Timeout notifies an occurrence of a time out while executing connection set-up command (Connect, Listen) or Send command.

SInit\_OK, Closed, Send\_OK and Recv\_OK each notifies the completion of Sock\_Init, Close, Send and Recv commands, respectively.

| 7 | 6       | 5       | 4       | 3      | 2           | 1        | 0       |

|---|---------|---------|---------|--------|-------------|----------|---------|

|   | Recv_OK | Send_OK | Timeout | Closed | Established | SInit_OK | Init_OK |

| Bit | Symbol      | Description                                                               |

|-----|-------------|---------------------------------------------------------------------------|

| D0  | Init_OK     | Interrupt status bit for completion of Sys_Init command                   |

| D1  | SInit_OK    | Interrupt status bit for completion of Channel 0 socket Sock_Init command |

| D2  | Established | Interrupt status bit for completion of Channel 0 socket connection set-up |

| D3  | Closed      | Interrupt status bit for completion of Channel 0 socket connection ending |

| D4  | Timeout     | Interrupt status bit for occurrence of time out during Channel 0 socket   |

|     |             | connection set-up or data transmission                                    |

| D5  | Send_OK     | Interrupt status bit for completion of Channel 0 socket Send command      |

| D6  | Recv_OK     | Interrupt status bit for completion of Channel 0 socket Recv command      |

| D7  |             | Reserved                                                                  |

#### C1\_ISR, C2\_ISR, C3\_ISR (Channel 1, 2, 3 Interrupt Status Register) [R, 0x05, 0x06, 0x07]

This register notifies the outcome of the command of each Channel 1, 2 and 3.

This register becomes cleared as 0x00 by read operation.

Established notifies the completion of a connection executed by connection set-up command (Connect, Listen).

Timeout notifies an occurrence of a time out while executing connection set-up command (Connect, Listen) or Send command.

SInit\_OK, Closed, Send\_OK and Recv\_OK each notifies the completion of Sock\_Init, Close, Send and Recv commands, respectively.

| 7 | 6       | 5       | 4       | 3      | 2           | 1        | 0 |

|---|---------|---------|---------|--------|-------------|----------|---|

|   | Recv_OK | Send_OK | Timeout | Closed | Established | SInit_OK |   |

| Bit | Symbol      | Description                                                                  |  |  |  |  |  |  |

|-----|-------------|------------------------------------------------------------------------------|--|--|--|--|--|--|

| D0  |             | Reserved                                                                     |  |  |  |  |  |  |

| D1  | SInit_OK    | Interrupt status bit for completion of corresponding channel socket          |  |  |  |  |  |  |

|     |             | Sock_Init command                                                            |  |  |  |  |  |  |

| D2  | Established | Interrupt status bit for completion of corresponding channel socket          |  |  |  |  |  |  |

|     |             | connection set-up                                                            |  |  |  |  |  |  |

| D3  | Closed      | Interrupt status bit for completion of corresponding channel socket          |  |  |  |  |  |  |

|     |             | connection ending                                                            |  |  |  |  |  |  |

| D4  | Timeout     | Interrupt status bit for occurrence of time out during corresponding channel |  |  |  |  |  |  |

|     |             | socket connection set-up or data transmission                                |  |  |  |  |  |  |

| D5  | Send_OK     | Interrupt status bit for completion of corresponding channel socket Send     |  |  |  |  |  |  |

|     |             | command                                                                      |  |  |  |  |  |  |

| D6  | Recv_OK     | Interrupt status bit for completion of corresponding channel socket Recv     |  |  |  |  |  |  |

|     |             | command                                                                      |  |  |  |  |  |  |

| D7  |             | Reserved                                                                     |  |  |  |  |  |  |

#### IR (Interrupt Register) [R/W, 0x08]

This register is used to sort channel with occurring interrupt.

C0, C1, C2 and C3 bit notify each of 0, 1, 2 and 3 channels that an interrupt has occurred. MCU can identify which interrupt has occurred by examining the Channel Interrupt Status Register of the corresponding channel.

C0R, C1R, C2R and C3R Bit notify that data transmission has occurred for 0, 1, 2 and 3 Channel. This register can clear the interrupt signal by writing '1' at the corresponding bit.

| 7   | 6   | 5   | 4   | 3  | 2  | 1  | 0  |

|-----|-----|-----|-----|----|----|----|----|

| C3R | C2R | C1R | C0R | C3 | C2 | C1 | C0 |

| Bit | Symbol | Description                                 |

|-----|--------|---------------------------------------------|

| D0  | C0     | Occurrence of Channel 0 Socket Interrupt    |

| D1  | C1     | Occurrence of Channel 1 Socket Interrupt    |

| D2  | C2     | Occurrence of Channel 2 Socket Interrupt    |

| D3  | C3     | Occurrence of Channel 3 Socket Interrupt    |

| D4  | C0R    | Occurrence of Channel 0 Socket data receipt |

| D5  | C1R    | Occurrence of Channel 1 Socket data receipt |

| D6  | C2R    | Occurrence of Channel 2 Socket data receipt |

| D7  | C3R    | Occurrence of Channel 3 Socket data receipt |

#### IMR (Interrupt Mask Register) [R/W, 0x09]

This register is used to mask an interrupt from each bit of the corresponding interrupt register. Interrupt is enabled when the corresponding bit of the interrupt register is set by setting the corresponding bit at '1'.

| 7      | 6      | 5      | 4      | 3     | 2     | 1     | 0     |  |

|--------|--------|--------|--------|-------|-------|-------|-------|--|

| IM_C3R | IM_C2R | IM_C1R | IM_C0R | IM_C3 | IM_C2 | IM_C1 | IM_C0 |  |

| Bit | Symbol | Description                                     |

|-----|--------|-------------------------------------------------|

| D0  | IM_C0  | Channel 0 Socket Interrupt Enable.              |

| D1  | IM_C1  | Channel 1 Socket Interrupt Enable.              |

| D2  | IM_C2  | Channel 2 Socket Interrupt Enable.              |

| D3  | IM_C3  | Channel 3 Socket Interrupt Enable.              |

| D4  | IM_C0R | Channel 0 Socket data receipt Interrupt Enable. |

| D5  | IM_C1R | Channel 1 Socket data receipt Interrupt Enable. |

| D6  | IM_C2R | Channel 2 Socket data receipt Interrupt Enable. |

| D7  | IM_C3R | Channel 3 Socket data receipt Interrupt Enable. |

#### IDM\_OR (InDirect Mode Option Register) [R/W, 0x0C]

This register facilitates indirect bus I/F mode enable and option set-up.

IND\_EN (indirect mode enable) bit enables indirect bus I/F mode. H/W reset is required to convert from indirect bus I/F mode to another I/F.

L/B (Little-endian/Big-endian) bit enables the access to indirect address register as Little-endian

('1') or Big-endian ('0').

AUTO\_INC (auto-increment) bit automatically increases the address during an access to indirect data register.

| 7      | 6 | 5 | 4 | 3 | 2 | 1   | 0        |

|--------|---|---|---|---|---|-----|----------|

| IND_EN |   |   |   |   |   | L/B | AUTO_INC |

| Bit | Symbol   | Description                                         |

|-----|----------|-----------------------------------------------------|

| D7  | IND_EN   | Indirect bus I/F mode Enable.                       |

| D6  |          | Reserved                                            |

| D5  |          | Reserved                                            |

| D4  |          | Reserved                                            |

| D3  |          | Reserved                                            |

| D2  |          | Reserved                                            |

| D1  | L/B      | Little-endian/Big-endian ordering setting register. |

| D0  | AUTO_INC | Address auto-increment Enable                       |

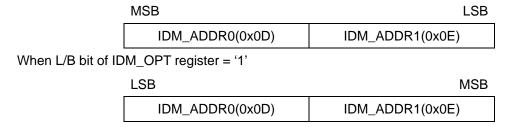

#### IDM\_AR0, IDM\_AR1 (InDirect Mode Address Register) [R/W, 0x0D - 0x0E]

This register is for address set-up when indirect bus I/F mode is in use, and the ordering changes according to the L/B bit set-up of IM\_OPT register.

When L/B bit of IDM\_OPT register = '0'

#### IDM\_DR (Indirect Mode Data Register) [R/W, 0x0F]

This register is for data when indirect bus I/F mode is in use.

#### 2. System Registers

#### GAR (Gateway Address Register) [R/W, 0x80 - 0x83]

This register sets up the default gateway address to be used in the system, which is required to be set IP address before executing Sys\_Init command.

#### SMR (Subnet Mask Register) [R/W, 0x84 - 0x87]

This register sets up the subnet mask to be used in the system, which is required to be set up

before executing Sys\_Init command.

#### SHAR (Source Hardware Address Register) [R/W, 0x88 - 0x8D]

This register sets up the HA to be used in the system, which is required to be set up before executing Sys\_Init command.

#### SIPR (Source IP Address Register) [R/W, 0x8E – 0x91]

This register sets up the IP to be used in the system, which is required to be set up before executing Sys\_Init command.

#### IRTR (Initial Retry Time-value Register) [R/W, 0x92 - 0x93]

This register sets up the timer value for initial re-transmission when using the TCP, and timer value 1 is equivalent to 100us.

| Value  | Timer (ms) |

|--------|------------|

| 0x03E8 | 100        |

| 0x07D0 | 200        |

| 0x0FA0 | 400        |

#### RCR (Retry Count Register) [R/W, 0x94]

This register assigns the number of retry when re-transmission occurs, and timeout interrupt occurs when re-transmission exceeds the number of retry.

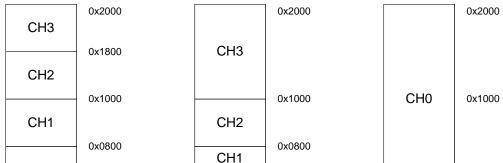

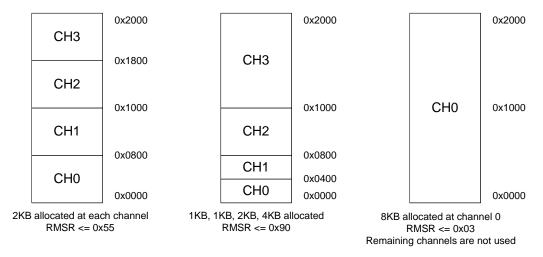

#### RMSR (Rx data Memory Size Register) [R/W, 0x95]

This register allocates 8KB of received memory for each channel.

| CI | <del>1</del> 3 | CI | <del>1</del> 2 | CI | <del>1</del> 1 | Cl | <del>1</del> 0 |

|----|----------------|----|----------------|----|----------------|----|----------------|

| S1 | S0             | S1 | S0             | S1 | S0             | S1 | S0             |

| S1 | S0 | Memory size |

|----|----|-------------|

| 0  | 0  | 1KB         |

| 0  | 1  | 2KB         |

| 1  | 0  | 4KB         |

| 1  | 1  | 8KB         |

2 bits of S1, S0 are allocated for each channel, and the memory for receiving is allocated according to the set-up value as shown in the table above.

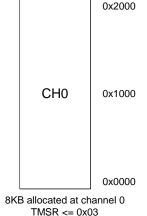

#### TMSR (Tx data Memory Size Register) [R/W, 0x96]

This register allocates 8KB of transmitted memory for each channel.

| CI | <del>1</del> 3 | Cl | <del>1</del> 2 | Cl | <del>1</del> 1 | Cl | H0 |  |

|----|----------------|----|----------------|----|----------------|----|----|--|

| S1 | S0             | S1 | S0             | S1 | S0             | S1 | S0 |  |

| S1 | S0 | Memory size |

|----|----|-------------|

| 0  | 0  | 1KB         |

| 0  | 1  | 2KB         |

| 1  | 0  | 4KB         |

| 1  | 1  | 8KB         |

2 bits of S1,S0 are allocated for each channel, and the memory for sending is allocated according to the set-up value as shown in the table above.

#### 3. Pointer Registers

In order to read pointer registers, the shadow register of the corresponding pointer needs to be read and time delay of Tx\_CLK \* 4 is required before reading the corresponding pointer register. (Access by W3100 MCU I/F is based on 1Byte unit, but the pointer register is comprised of 4Bytes. Therefore, shadow register is used in order for MCU to properly read 4Byte pointer.)

To write, no access to the shadow register or time delay is necessary.

| Shadow Registers | Address | Applicable Pointer Registers |

|------------------|---------|------------------------------|

| C0_SRW_PR        | 0x1E0   | C0_ RW_PR                    |

| C0_SRR_PR        | 0x1E1   | C0_ RR_PR                    |

| C0_STA_PR        | 0x1E2   | C0_TA_PR                     |

| C1_SRW_PR        | 0x1E3   | C1_ RW_PR                    |

| C1_SRR_PR        | 0x1E4   | C1_ RR_PR                    |

| C1_STA_PR        | 0x1E5   | C1_TA_PR                     |

| C2_SRW_PR        | 0x1E6   | C2_ RW_PR                    |

| C2_SRR_PR        | 0x1E7   | C2_ RR_PR                    |

| C2_STA_PR        | 0x1E8   | C2_TA_PR                     |

| C3_SRW_PR        | 0x1E9   | C3_ RW_PR                    |

| C3_SRR_PR        | 0x1EA   | C3_ RR_PR                    |

| C3_STA_PR        | 0x1EB   | C3_TA_PR                     |

| C0_STW_PR | 0x1F0 | C0_TW_PR |

|-----------|-------|----------|

| C0_STR_PR | 0x1F1 | C0_TR_PR |

| C1_STW_PR | 0x1F3 | C1_TW_PR |

| C1_STR_PR | 0x1F4 | C1_TR_PR |

| C2_STW_PR | 0x1F6 | C2_TW_PR |

| C2_STR_PR | 0x1F7 | C2_TR_PR |

| C3_STW_PR | 0x1F9 | C3_TW_PR |

| C3_STR_PR | 0x1FA | C3_TR_PR |

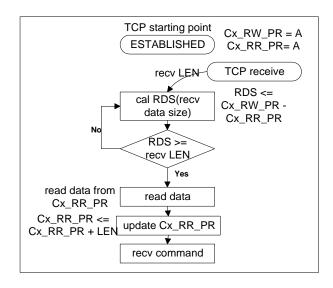

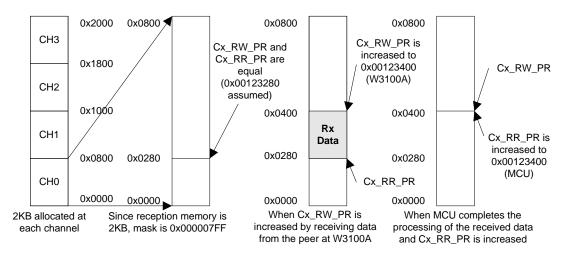

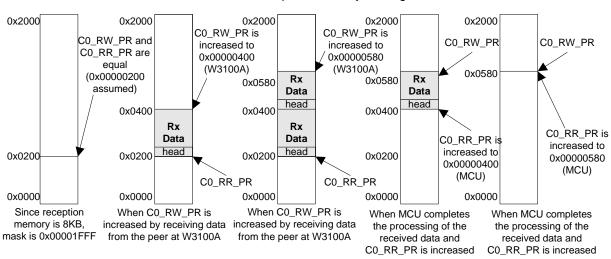

## RW\_PR (Rx Write Pointer Register) [R/W, C0 : 0x10 - 0x13, C1 : 0x1C - 0x1F, C2 : 0x28 - 0x2B, C3 : 0x34 - 0x37]

Included in each channel, this register displays the data end pointer when receiving data. The register is managed internally by W3100A and increases according to the size of the data received. MCU receives and processes the data from Rx Read Pointer to Rx Writer Pointer of the corresponding channel.

### RR\_PR (Rx Read Pointer Register) [R/W, C0 : 0x14 - 0x17, C1 : 0x20 - 0x23, C2 : 0x2C - 0x2F, C3 : 0x38 - 0x3B]

Included in each channel, this register displays the data start pointer when receiving data.

After processing the received data, MCU updates Rx Read Pointer as the pointer of the processed data and releases Recv Command.

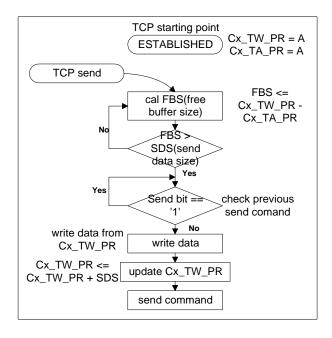

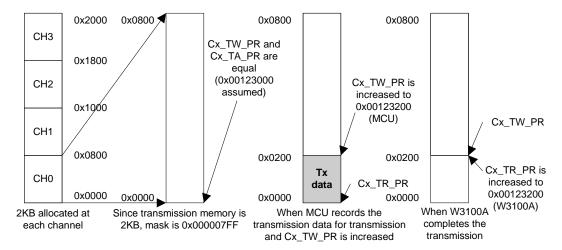

## TW\_PR (Tx Write Pointer Register) [R/W, C0 : 0x40 - 0x43, C1 : 0x4C - 0x4F, C2 : 0x58 - 0x5B, C3 : 0x64 - 0x67]

Included in each channel, this register displays the data end pointer of the data to be transmitted when transmitting data.

For transmission, MCU writes the data to be transmitted from Tx Write Pointer of the corresponding channel, and Tx Write Pointer needs to be updated with a new value after the data is copied.

Transmission is made after executing the Send command.

## TR\_PR (Tx Read Pointer Register) [R/W, C0 : 0x44 - 0x47, C1 : 0x50 - 0x53, C2 : 0x5C - 0x5F, C3 : 0x68 - 0x6B]

Included in each channel, this register displays the current working pointer of the data to be transmitted when transmitting data.

The register, used internally in W3100A, displays the pointer to start transmission when transmission is made by send command.

# TA\_PR (Tx Ack Pointer Register) [R/W, C0 : 0x18 - 0x1B, C1 : 0x24 - 0x27, C2 : 0x30 - 0x33, C3 : 0x3C - 0x3F]

Included in each channel, this register displays the start pointer of the data to be transmitted when transmitting data.

Driver uses this register and Tx Write Pointer to calculate free size of Tx Buffer.

In other words, the difference in value of Tx Write Pointer and Tx Ack Pointer is the buffer size being used.

### 4. Channel Registers

SSR (Socket State Register) [R, C0: 0xA0, C1: 0x B8, C2: 0x D0, C3: 0x E8]

Displays the socket state of the corresponding channel.

| Value | State            | Meaning                                           |

|-------|------------------|---------------------------------------------------|

| 0x00  | SOCK_CLOSED      | Socket is closed                                  |

| 0x01  | SOCK_ARP         | Standing by for reply after transmitting ARP      |

|       |                  | Request                                           |

| 0x02  | SOCK_LISTEN      | Standing by for connection set-up to the client   |

|       |                  | when acting in passive mode                       |

| 0x03  | SOCK_SYNSENT     | Standing by for SYN,ACK after transmitting        |

|       |                  | SYN for connection set-up when acting in          |

|       |                  | active mode                                       |

| 0x04  | SOCK_SYNSENT_ACK | Connection set-up is complete after               |

|       |                  | SYN,ACK is received and ACK is transmitted        |

| 005   | COOK CYNDEOV     | in active mode                                    |

| 0x05  | SOCK_SYNRECV     | SYN,ACK is being transmitted after receiving      |

|       |                  | SYN from the client in listen state, passive mode |

| 0x06  | SOCK ESTABLISHED | Connection set-up is complete in active,          |

| 0000  | SOCK_ESTABLISHED | passive mode                                      |

| 0x07  | SOCK_CLOSE_WAIT  | Connection being terminated                       |

| 0X08  | SOCK_LAST_ACK    | Connection being terminated                       |

| 0X09  | SOCK FIN WAIT1   | Connection being terminated                       |

| 0X0A  | SOCK FIN WAIT2   | Connection being terminated                       |

| 0X0B  | SOCK_CLOSING     | Connection being terminated                       |

| 0X0C  | SOCK_TIME_WAIT   | Connection being terminated                       |

| 0X0D  | SOCK_RESET       | Connection is being terminated after receiving    |

|       |                  | reset packet from the peer                        |

| 0X0E  | SOCK_INIT        | Socket initializing                               |

| 0X0F  | SOCK_UDP         | Applicable channel is initialized in UDP mode     |

| 0X10  | SOCK_RAW         | Applicable channel is initialized in IP layer     |

|       |                  | RAW mode                                          |

| 0X11  | SOCK_UDP_ARP     | Standing by for reply after transmitting ARP      |

|       |                  | request packet to the destination for UDP         |

|       |                  | transmission                                      |

| 0X12  | SOCK_UDP_DATA    | Data transmission in progress in UDP or           |

| ->//- |                  | RAW mode                                          |

| 0X13  | SOCK_RAW_INIT    | W3100A initialized in MAC layer RAW mode          |

# SOPR (Socket Option and Protocol Register) [R/W, C0 : 0xA1, C1 : 0x B9, C2 : 0x D1, C3 : 0x E9]

This register sets up socket option or protocol of the corresponding channel.

| 7          | 6          | 5     | 4    | 3 | 2        | 1        | 0        |

|------------|------------|-------|------|---|----------|----------|----------|

| Broadcast/ | NDTimeout/ | NDAck | SWS/ |   | Protocol | Protocol | Protocol |

| ERR        | В          |       | Р    |   |          |          |          |

| Bit | Symbol        | Description                                                         |                                                             |  |  |

|-----|---------------|---------------------------------------------------------------------|-------------------------------------------------------------|--|--|

| D0  | Protocol      | Sets up corresponding channel in TCP, UDP, IP Layer RAW mode or     |                                                             |  |  |

| D1  |               | MAC Layer RAW mode                                                  |                                                             |  |  |

| D2  |               | Value Meaning                                                       |                                                             |  |  |

|     |               | 000                                                                 | Closed                                                      |  |  |

|     |               | 001                                                                 | SOCK_STREAM(TCP)                                            |  |  |

|     |               | 010                                                                 | SOCK_DGRAM(UDP)                                             |  |  |

|     |               | 011                                                                 | SOCK_IPL_RAW(IP Layer RAW Mode)                             |  |  |

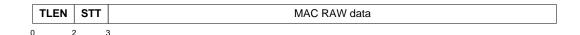

|     |               | 100                                                                 | SOCK_MACL_RAW(MAC Layer RAW Mode)                           |  |  |

| D3  |               | Reserved                                                            |                                                             |  |  |

| D4  | SWS/P         | Silly Window Syndrome                                               |                                                             |  |  |

|     |               | '0': prevents Silly Window Syndrome when using TCP                  |                                                             |  |  |

|     |               | '1': does not prevent Silly Window Syndrome when using TCP          |                                                             |  |  |

|     |               | When using MAC Layer RAW mode, promiscuous packet (packet with      |                                                             |  |  |

|     |               | specific M                                                          | IAC address) can be received by when C0_SOPR sets the bit   |  |  |

|     |               | as '1'                                                              |                                                             |  |  |

| D5  | NDAck         | No Delaye                                                           | ed ACK                                                      |  |  |

|     |               | '0': use:                                                           | s delayed ACK                                               |  |  |

|     |               | '1': does not use delayed ACK – ACK is transmitted immediately upon |                                                             |  |  |

|     |               | receiving                                                           | the data packet                                             |  |  |

| D6  | NDTimeout/B   | No Dynamic Timeout                                                  |                                                             |  |  |

|     |               | '0': use                                                            | es dynamic timeout during operation to set up timeout value |  |  |

|     |               | regardless                                                          | s of the set-up value                                       |  |  |

|     |               | '1': activ                                                          | vates by using the timeout value as set up in Timeout Value |  |  |

|     |               | When usi                                                            | ng MAC Layer RAW mode, broadcast packet can be received     |  |  |

|     |               | by when (                                                           | C0_SOPR sets the bit as '1'                                 |  |  |

| D7  | Broadcast/ERR | Broadcas                                                            | t packet is received and transmitted in IP Layer RAW mode   |  |  |

|     |               | When using MAC Layer RAW mode, error packet can be received by      |                                                             |  |  |

|     |               | when C0_                                                            | SOPR sets the bit as '1'                                    |  |  |

### DIR (Destination IP Address Register) [R/W, C0 : 0xA8 – 0xAB, C1 : 0xC0 – 0xC3, C2 : 0xD8 – 0xDB, C3 : 0xF0 – 0xF3]

This register sets the Destination IP Address of each channel to be used in setting the TCP connection. In active mode, IP address needs to be set before executing the Connect command. In passive mode, W3100A sets up the connection and then updates as peer IP internally.

## DPR (Destination Port Register) [R/W, C0 : 0xAC - 0xAD, C1 : 0xC4 - 0xC5, C2 : 0xDC - 0xDD, C3 : 0xF4 - 0xF5]

This register sets the Destination Port number of each channel to be used in setting the TCP connection. In active mode, port number needs to be set before executing the Connect command. In passive mode, W3100A sets up the connection and then updates as peer port number internally.

## SPR (Source Port Register) [R/W, C0 : 0xAE - 0xAF, C1 : 0xC6 - 0xC7, C2 : 0xDE - 0xDF, C3 : 0xF6 - 0xF7]

This register sets the Source Port number for each channel when using TCP or UDP mode, and the set-up needs to be made before executing the Sock\_Init Command.

#### IPR (IP Protocol Register) [R/W, C0: 0xB0, C1: 0xC8, C2: 0xE0, C3: 0xF8]

This IP Protocol Register is used to be set up at the Protocol Field of IP Header when executing the IP Layer RAW Mode, and the set-up needs to be made before executing the Sock\_Init Command.

#### TOSR (TOS Register) [R/W, C0: 0xB1, C1: 0xC9, C2: 0xE1, C3: 0xF9]

This register is used to be set up at the TOS (Type Of Service) Field of IP Header, and the set-up needs to be made before executing the Sock\_Init Command.

## MSSR (MSS Register) [R/W, C0 : B2 - 0xB3, C1 : 0xCA - 0xCB, C2 : 0xE2 - 0xE3, C3 : 0xFA - 0xFB]

This register is used for MSS (Maximum Segment Size) of TCP, and the register displays MSS set by the other party when TCP is activated in Passive Mode.

### ■ Internal Memory and Registers

#### **W3100A Top level Memory Map**

| 0x0000 | Control registers |

|--------|-------------------|

| 0x0200 | Control registers |

| 0×4000 | Not used          |

| 0x4000 |                   |

|        |                   |

|        |                   |

|        | Tx data buffer    |

|        |                   |

|        |                   |

|        |                   |

| 0x6000 |                   |

|        |                   |

|        |                   |

|        | Rx data buffer    |

|        |                   |

|        |                   |

|        |                   |

| 0x8000 |                   |

W3100A internal register and memory are comprised of 512 byte Control Registers and 16KB data buffer as displayed in the diagram above.

- 0x0000 ~ 0x00FF: Space for Control Registers

- 0x0100 ~ 0x01FF: Space for Shadow Registers

- 0x0200 ~ 0x3FFF: Not used (This space can be used by other devices)

- 0x4000 ~ 0x5FFF: Tx Data Buffer

- 0x6000 ~ 0x7FFF: Rx Data Buffer

Tx data buffer is the memory used for MCU transmission, and MCU can execute 'write' but cannot execute 'read'. Rx data buffer is the memory used for MCU reception, and MCU can execute

'read' but cannot execute 'write'. In order to verify the active status of Tx data buffer and Rx data buffer, MCU can execute both write and read by setting the memory test mode (setting up of C1\_CR memory test bit). In memory test mode, however, W3100A cannot execute proper transmission and reception of data. Memory test mode must be terminated for normal operation of W3100A.

#### Description of Functions

#### 1. Initialization of W3100A

In order to use W3100A, the basic registers that are required to run W3100A need to be set up. The basic registers include GAR (Gateway Address Register), SMR (Subnet Mask Register), SHAR (Source Hardware Address Register), and SIPR (Source IP Address Register).

GAR, SMR and SIPR are the network information on which W3100A is operated, and the registers need to be set according to the operating environment. SHAR is the Hardware address to be used at the MAC layer of W3100A, and the address already provided to the manufacturer is used. After appropriately setting up above registers, W3100A can activate in the network by executing the sys\_init command. Activation can be verified by using Ping (ICMP Echo request).

#### 2. TCP Protocol

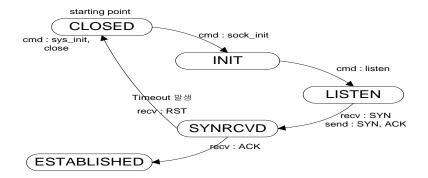

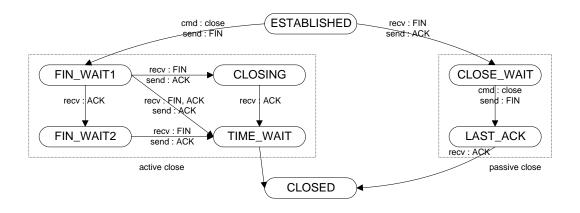

TCP is a connection-oriented protocol. By using three-way handshaking method in executing the connection set-up and termination process, reliable data transmission and reception are assured.

#### **TCP Initialization Process**

In order to use W3100A TCP, the protocol field of the corresponding channel's Cx\_SOPR (Socket Option/Protocol Register of Channel x) needs to be set up as SOCK\_STREAM(0x01). After the channel is activated by sock\_init command, Cx\_TW\_PR (Tx Write Pointer Register of Channel x), Cx\_TR\_PR (Tx Read Pointer Register of Channel x), and Cx\_TA\_PR (Tx Ack Pointer Register of Channel x) need to be initialized with same value.

#### **TCP Connection Set-up Process**

In W3100A, the TCP connection process as directed by Connect or Listen command is processed internally. Sending SYN Packet as directed by Connect command is called active open, and standing by for SYN Packet from peer as directed by Listen command is called passive open.

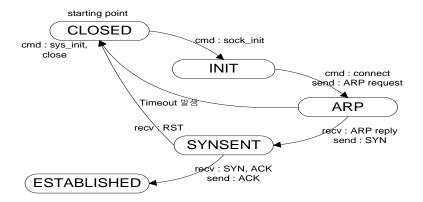

#### Active open.

TCP Client mode that knows the IP address and port number of the destination, and the connection set-up is made ahead.

Above diagram illustrates the connection set-up process using active open. Each status can be verified through the socket status register of the corresponding channel.

- a. CLOSED state: channel is initialized by executing sys\_init or close command

- b. INIT state: sets the port number (source port register) to be used in the channel and activates the channel by executing the sock\_init command

- c. ARP state: In order to set up connection, MCU sets the Destination IP, Destination Port register and executes the connect command. Based on this command, W3100A changes to this state and transmits ARP request packet. When ARP reply packet is received from the peer under this state, it changes to SYNSENT state and transmits SYN packet. In case no reply is received from the peer, re-transmission is made. When no reply is received within the designated timeout duration, timeout occurs and it changes to CLOSED state.

- d. SYNSENT state: In this state, W3100A transmits SYN packet and stands by to receive SYN,ACK packet from the peer. In case appropriate SYN,ACK packet is received, W3100A transmits ACK packet and completes the connection set-up to become changed to ESTABLISHED state. In case no appropriate SYN,ACK packet is received from the peer, re-transmission of SYN Packet is made. When no reply is received within the designated timeout duration, timeout occurs and it changes to CLOSED state. Also, if the peer has no application standing by in passive mode, the peer receives RST packet and changes to CLOSED state.

#### Passive open.

In TCP Server mode, stands by for connection set-up from the peer under the Listen command, and the connection set-up is accepted when requested.

- a. CLOSED state: channel is initialized by executing sys\_init or close command

- b. INIT state: sets the port number (source port register) to be used in the channel and activates the channel by executing the sock\_init command

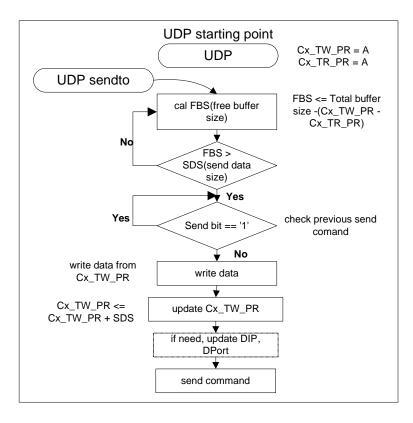

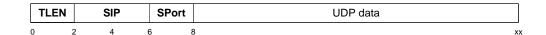

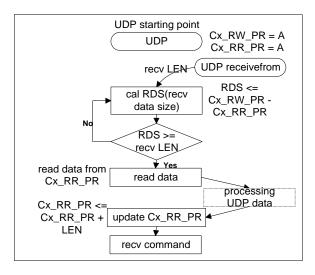

- c. LISTEN state: stands by for connection set-up from the peer. When SYN packet for the corresponding port is received from the peer, SYN,ACK packet is transmitted and changes to SYNRCVD state.