# **Ring Generator Controller IC**

#### **Features**

- ▶ 3.3V operation, logic inputs 3.3V & 5.0V compatible

- ▶ Digital control of ring frequency, amplitude, and offset

- ► Control via 8-bit bus or via individual inputs

- ▶ 8 built-in ring frequencies: 12, 16²/₃, 20, 25, 33¹/₃, 40, 50, 60Hz

- External ring frequency input

- ▶ Low distortion sine wave synthesizer

- ► AC-only, AC+DC, or DC-only ringer output

- Adjustable over-current protection

- Internal precision voltage references

- Power-on reset and undervoltage lockout for hotswap capability

- Sync output with adjustable lead time for synchronizing ringing relays

- ► Fault output for problem detection

- Open or closed loop operation

- ► Efficient 4-quadrant operation

- Zero-cross turn-on with zero-cross turn-off option

#### **Applications**

- ▶ PBX

- DLC

- Key Systems

- Remote Terminal

- Wireless Loop Systems

#### **General Description**

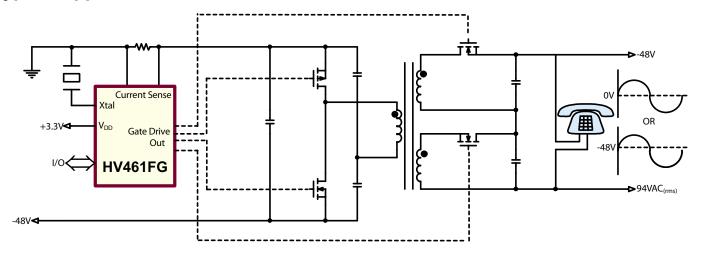

The HV461FG is a highly integrated ring generator controller IC, designed to work with a patented four-quadrant inverter topology, with synchronous rectifiers on the secondary side to achieve higher efficiencies. The inverter delivers the desired ring voltage from a standard -48V Telecom power supply.

The HV461 consists of a sine wave synthesizer that can provide eight different ring frequencies for universal applications. Any other frequency in the 12 to 63Hz range can be obtained by applying an external logic signal to the IC. A transparent latch permits control of the ringer output individually or through the 8-bit bus. The output amplitude and DC offset can be digitally controlled providing high flexibility to the designers. The patented inverter topology using the HV461 controller IC is capable of achieving higher efficiencies, typically over 80%, and drive up to a 40 REN load.

The controller allows ring generators to provide a floating 94VAC (rms) waveform that can be referenced to either the -48V or any other offset level by using the programmable offset pins of the IC. Output offset may be achieved by directly generating the offset within the power stage, or by floating the output stage on a DC source, or both.

The HV461 also has an internal boost converter that can be used to provide the gate drive voltages for the two MOSFETS on the primary side and the two secondary rectifiers on the secondary side.

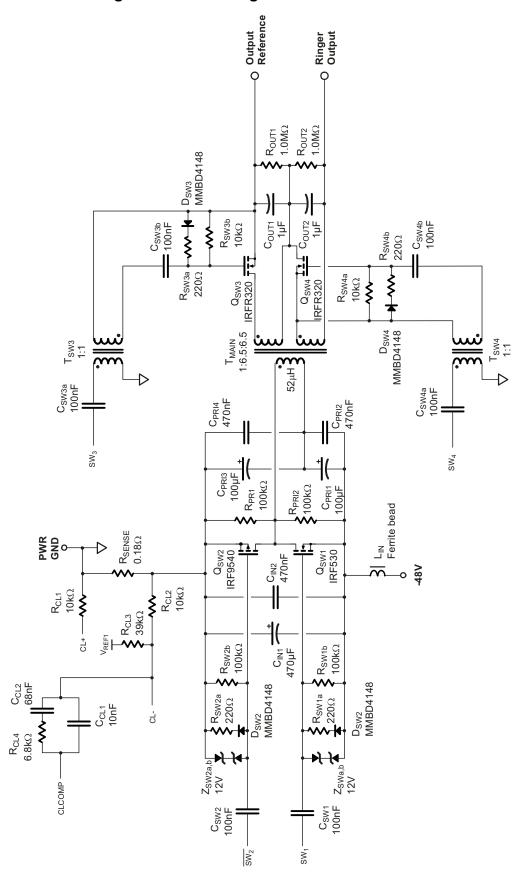

#### **Typical Application Circuit**

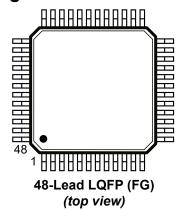

#### **Ordering Information**

|        | Package Option                                                         |

|--------|------------------------------------------------------------------------|

| Device | 48-Lead LQFP<br>7.00x7.00mm body<br>1.6mm height (max)<br>0.50mm pitch |

| HV461  | HV461FG-G                                                              |

-G indicates package is RoHS compliant ('Green')

#### **Absolute Maximum Ratings**

| Parameter             | Value           |

|-----------------------|-----------------|

| V <sub>DD</sub>       | +4.0V           |

| Digital inputs        | -0.5V to +7.0V  |

| Analog inputs         | -0.5V to +7.0V  |

| Storage temperature   | -65°C to +150°C |

| Operating temperature | -40°C to +85°C  |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect device reliability. All voltages are referenced to device ground.

#### **Pin Configuration**

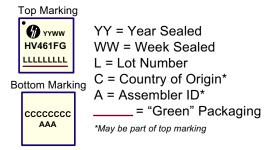

#### **Product Marking**

48-Lead LQFP (FG)

# **Electrical Specifications** (unless otherwise specified: $V_{DD} = 3.3V$ , $T_{A} = -40$ °C to +85°C) **External Supply**

| Sym             | Parameter                                             | Min | Тур | Max | Units | Conditions                                                                                                             |

|-----------------|-------------------------------------------------------|-----|-----|-----|-------|------------------------------------------------------------------------------------------------------------------------|

| $V_{_{DD}}$     | Supply voltage                                        | 3.0 | 3.3 | 3.6 | V     |                                                                                                                        |

| I <sub>DD</sub> | Supply current (AV <sub>DD</sub> + DV <sub>DD</sub> ) | -   | 7   | 30  | mA    | f <sub>PWM</sub> = 100kHz<br>f <sub>osc</sub> = 19.6608MHz SW outputs NC<br>Open loop config, External V <sub>GD</sub> |

#### **Gate Drive Supply**

| Sym               | Parameter                 | Min                   | Тур     | Max       |          | Conditions                                                                                |

|-------------------|---------------------------|-----------------------|---------|-----------|----------|-------------------------------------------------------------------------------------------|

| $V_{GD}$          | Boost circuit voltage     | 9.0                   | 9.6     | 10.2      | V        |                                                                                           |

| l <sub>GD</sub>   | Gate drive supply current | -                     | -       | 5.0<br>10 | mA<br>mA | $V_{DD}$ = 2.97 - 3.63V, SW outputs unloaded $V_{DD}$ = 2.50 - 2.93V, SW outputs unloaded |

| $V_{DR(lo)}$      | Drive voltage, low        | -                     | -       | 0.2       | V        | I <sub>OUT</sub> = -10μA                                                                  |

| $V_{DR(hi)}$      | Drive voltage, hi         | V <sub>DD</sub> - 0.4 | -       | -         | V        | I <sub>ουτ</sub> = 10μA                                                                   |

| t <sub>RISE</sub> | Rise time                 | -                     | -       | 100       | ns       | C <sub>L</sub> = 200pF                                                                    |

| t <sub>FALL</sub> | Fall time                 | -                     | -       | 100       | ns       | C <sub>L</sub> = 200pF                                                                    |

| f <sub>GD</sub>   | Converter frequency       | 5                     | same as | PWM       |          |                                                                                           |

| D <sub>GD</sub>   | Duty cycle                | 45                    | 50      | 55        | %        |                                                                                           |

#### **Voltage Reference**

| Sym                | Parameter               | Min   | Тур   | Max   | Units | Conditions                          |

|--------------------|-------------------------|-------|-------|-------|-------|-------------------------------------|

| V <sub>REF1</sub>  | Reference voltage 1     | 1.213 | 1.250 | 1.288 | V     | T <sub>a</sub> = 25°C               |

| TC <sub>REF1</sub> | Temperature coefficient | -     | 200   | -     | μV/°C |                                     |

| $\Delta V_{ref1}$  | Output regulation       | -6.25 | -     | +6.25 | mV    | I <sub>out</sub> = ±100μA           |

| V <sub>REF2</sub>  | Reference voltage 2     | 2.425 | 2.500 | 2.575 | V     | T <sub>A</sub> = 25°C               |

| TC <sub>REF2</sub> | Temperature coefficient | -     | 500   | -     | μV/°C |                                     |

| $\Delta V_{ref2}$  | Output regulation       | -12.5 | -     | 0     | mV    | I <sub>out</sub> = 0 - 100μA source |

#### **Logic Inputs**

| Sym                 | Parameter          | Min                 | Тур | Max                 | Units | Conditions             |

|---------------------|--------------------|---------------------|-----|---------------------|-------|------------------------|

| V <sub>IN(Io)</sub> | Input voltage low  | -                   | -   | 0.3·V <sub>DD</sub> | V     |                        |

| V <sub>IN(hi)</sub> | Input voltage high | 0.7·V <sub>DD</sub> | -   | -                   | V     |                        |

| I <sub>IN(lo)</sub> | Input current low  | -                   | -   | -1                  | μA    | V <sub>IN</sub> = 0V   |

| I <sub>IN(hi)</sub> | Input current high | -                   | -   | 1                   | μA    | V <sub>IN</sub> = 5.0V |

| C <sub>IN</sub>     | Input capacitance  | -                   | -   | 10                  | pF    |                        |

| t <sub>s</sub>      | Set-up time        | -                   | -   | 100                 | ns    |                        |

| t <sub>H</sub>      | Hold time          | -                   | -   | 100                 | ns    |                        |

#### Reset

| Sym                      | Parameter             | Min   | Тур   | Max   | Units | Conditions |

|--------------------------|-----------------------|-------|-------|-------|-------|------------|

| V <sub>RESET(ON)</sub>   | RESET on voltage      | 1.200 | 1.325 | 1.450 | V     |            |

| V <sub>RESET(OFF)</sub>  | RESET off voltage     | 1.000 | 1.125 | 1.250 | V     |            |

| V <sub>RESET (HYS)</sub> | RESET hysteresis      | 0.150 | 0.200 | 0.250 | V     |            |

| I <sub>P-UP</sub>        | RESET pull-up current | 7.0   | 10.0  | 13.0  | μA    |            |

### **Undervoltage Lockout**

| Sym                  | Parameter                   | Min     | Тур                     | Max        | Units | Conditions |

|----------------------|-----------------------------|---------|-------------------------|------------|-------|------------|

| $V_{DD(ON)}$         | V <sub>DD</sub> on voltage  | 2.75    | 2.85                    | 2.95       | V     |            |

| $V_{DD(OFF)}$        | V <sub>DD</sub> off voltage | 2.50    | -                       | -          | V     |            |

| V <sub>DD(HYS)</sub> | V <sub>DD</sub> hysteresis  | -       | 0.10                    | -          | V     |            |

| $V_{GD(ON)}$         | V <sub>GD</sub> on voltage  | same as | V <sub>GD</sub> regulat | tion point | V     |            |

| $V_{GD(OFF)}$        | V <sub>GD</sub> off voltage | 7.0     | -                       | -          | V     |            |

| $V_{\rm GD(HYS)}$    | V <sub>GD</sub> hysteresis  | 0.20    | -                       | -          | V     |            |

#### **Fault Output**

| Sym                      | Parameter           | Min | Тур | Max | Units | Conditions                |

|--------------------------|---------------------|-----|-----|-----|-------|---------------------------|

| $V_{OUT(lo)}$            | Output voltage low  | -   | -   | 0.2 | V     | I <sub>OUT</sub> = 1mA    |

| K <sub>FAULT(on)</sub>   | FAULT on threshold  | 6   | 8   | 10  | %*    | C <sub>FAULT</sub> = 10µF |

| K <sub>FAULT(off)</sub>  | FAULT off threshold | 1   | 2   | 3   | %*    | C <sub>FAULT</sub> = 10µF |

| t <sub>FAULT(hold)</sub> | FAULT hold time     | 50  | -   | -   | mS    | C <sub>FAULT</sub> = 10µF |

<sup>\*</sup> Percent of time PWM overrange or overcurrent is active.

#### **Amplifiers**

| Sym                   | Parameter                    | Min                  | Тур                  | Max  | Units | Conditions                                |

|-----------------------|------------------------------|----------------------|----------------------|------|-------|-------------------------------------------|

| V <sub>IN</sub>       | Input range                  | 0.25                 | -                    | 2.50 | V     |                                           |

| I <sub>IN</sub>       | Input bias current           | -500                 | -                    | 500  | nA    | $V_{IN} = 0.5 V \text{ to } V_{DD} - 0.5$ |

| V <sub>OFFSET</sub>   | Input offset voltage         | -15                  | -                    | 15   | mV    |                                           |

| $V_{\text{OUT(min)}}$ | Min output                   | -                    | 0.1                  | 0.2  | V     | I <sub>OUT</sub> = ±100uA                 |

| V <sub>OUT(max)</sub> | Max output                   | V <sub>DD</sub> -0.2 | V <sub>DD</sub> -0.1 | -    |       | I <sub>OUT</sub> = ±100uA                 |

| A <sub>VOL</sub>      | Open loop gain               | 60                   | 80                   | -    | dB    |                                           |

| CMRR                  | Common mode rejection ratio  | -40                  | -60                  | -    | dB    |                                           |

| GBW                   | Gain-bandwidth product       | 1.0                  | -                    | -    | MHz   |                                           |

| SL                    | Slew rate                    | 0.1                  | -                    | -    | V/µs  |                                           |

| PSRR                  | Power supply rejection ratio | -30                  | -                    | -    | dB    | f<10kHz                                   |

# **Sinewave Synthesizer**

| Sym              | Parameter           | Min          | Тур                            | Max          | Units            | Conditions                                       |

|------------------|---------------------|--------------|--------------------------------|--------------|------------------|--------------------------------------------------|

| V <sub>DC</sub>  | DC level            | 1.213        | 1.250                          | 1.288        | V                |                                                  |

| ^                | Amplitudo           | 1.900        | 2.000                          | 2.100        | V <sub>P-P</sub> | AMP ≠ 00                                         |

| Α                | Amplitude           |              |                                | 0            | $V_{P-P}$        | AMP = 00                                         |

| f <sub>0</sub>   | Frequency           | -            | 16 <sup>2</sup> / <sub>3</sub> | -            | Hz               | FREQ = 000, f <sub>OSC</sub> = 19.6608MHz        |

| f <sub>1</sub>   | Frequency           | -            | 20                             | -            | Hz               | FREQ = 001, f <sub>osc</sub> = 19.6608MHz        |

| f <sub>2</sub>   | Frequency           | -            | 25                             | -            | Hz               | FREQ = 010, f <sub>OSC</sub> = 19.6608MHz        |

| f <sub>3</sub>   | Frequency           | -            | 30                             | -            | Hz               | FREQ = 011, f <sub>osc</sub> = 19.6608MHz        |

| f <sub>4</sub>   | Frequency           | -            | 33 <sup>1</sup> / <sub>3</sub> | -            | Hz               | FREQ = 100, f <sub>osc</sub> = 19.6608MHz        |

| $f_5$            | Frequency           | -            | 40                             | -            | Hz               | FREQ = 101, f <sub>osc</sub> = 19.6608MHz        |

| f <sub>6</sub>   | Frequency           | -            | 50                             | -            | Hz               | FREQ = 110, f <sub>osc</sub> = 19.6608MHz        |

| f <sub>7</sub>   | Frequency           | -            | 60                             | -            | Hz               | FREQ = 111, f <sub>osc</sub> = 19.6608MHz        |

| $\Delta f$       | Frequency accuracy  | -            | -                              | 0.1          | %                | f <sub>osc</sub> = 19.6608MHz                    |

| THD              | Harmonic distortion | -            | -                              | 3            | %                | $C_{SINE} = 33nF$<br>$f_{ring} = 16 2/3 to 60Hz$ |

| R <sub>out</sub> | Output resistance   | 14.4<br>72.0 | 16.0<br>80.0                   | 17.6<br>88.0 | kΩ<br>kΩ         | AMP ≠ 00<br>AMP = 00                             |

#### **External Ring Frequency**

| Sym                   | Parameter                  | Min                 | Тур | Max                   | Units | Conditions                                                       |

|-----------------------|----------------------------|---------------------|-----|-----------------------|-------|------------------------------------------------------------------|

| f <sub>CAP(lo)</sub>  | Capture frequency low*     | -                   | 12  | -                     | Hz    | loop filter = $(33\mu\text{F}+10\text{k}\Omega)  4.7\mu\text{F}$ |

| f <sub>CAP(hi)</sub>  | Capture frequency high*    | -                   | 63  | -                     | Hz    | loop filter = $(33\mu\text{F}+10\text{k}\Omega)  4.7\mu\text{F}$ |

| V <sub>IN(Io)</sub>   | Input low                  | -                   | -   | 0.3 - V <sub>DD</sub> | V     |                                                                  |

| V <sub>IN(hi)</sub>   | Input high                 | 0.7·V <sub>DD</sub> | -   | -                     | V     |                                                                  |

| $\Delta 	heta_{RING}$ | Phase jitter, sine ref out | -5                  | -   | +5                    | deg   | loop filter = $(33\mu\text{F}+10\text{k}\Omega)  4.7\mu\text{F}$ |

<sup>\*</sup> Lock range is the same as capture range

#### **Sine Reference Attenuator**

| Sym              | Parameter   | Min   | Тур   | Max                   | Units | Conditions                   |

|------------------|-------------|-------|-------|-----------------------|-------|------------------------------|

| V <sub>DC</sub>  | DC level    | 1.213 | 1.250 | 1.288                 | V     | V <sub>IN(DC)</sub> = 1.250V |

| A <sub>OFF</sub> | Attenuation | -     | -     | 0.010                 | V/V   | AMP = 00                     |

| A <sub>LO</sub>  | Attenuation | 0.490 | 0.500 | 0.510                 | V/V   | AMP = 01                     |

| A <sub>MED</sub> | Attenuation | 0.735 | 0.750 | 0.765                 | V/V   | AMP = 10                     |

| A <sub>HI</sub>  | Attenuation | 0.980 | 1.000 | 1.020                 | V/V   | AMP = 11                     |

| V <sub>IN</sub>  | Input range | 0.2   | -     | V <sub>DD</sub> - 0.2 | V     |                              |

#### **DC REF Multiplexer**

| Sym              | Parameter           | Min  | Тур | Max             | Units | Conditions                                |

|------------------|---------------------|------|-----|-----------------|-------|-------------------------------------------|

| V <sub>IN</sub>  | Input range         | 0.0  | -   | V <sub>DD</sub> | V     |                                           |

| I <sub>IN</sub>  | Input bias current  | -500 | -   | +500            | nA    |                                           |

| I <sub>OFF</sub> | Off leakage current | -    | -   | 1.0             | μA    | $V_{IN} = 0.5 \text{ to } V_{DD} - 0.5 V$ |

#### **Enable and SYNC**

| Sym                     | Parameter                | Min                   | Тур | Max     | Units               | Conditions                                                     |

|-------------------------|--------------------------|-----------------------|-----|---------|---------------------|----------------------------------------------------------------|

| V <sub>OUT(Io)</sub>    | SYNC output voltage low  | -                     | -   | 0.2     | V                   | I <sub>OUT</sub> = 1.0mA sink                                  |

| $V_{OUT(hi)}$           | SYNC output voltage high | V <sub>DD</sub> - 0.2 | -   | -       | V                   | I <sub>OUT</sub> = 1.0mA source                                |

| t <sub>on</sub>         | ENABLE delay, on         | -                     | -   | 5       | μs                  |                                                                |

| t <sub>off</sub>        | ENABLE delay, off        | 0                     | -   | 60<br>1 | μs<br>ring<br>cycle | SYNCMODE = 0<br>SYNCMODE = 1                                   |

| T <sub>SYNC(ON)</sub>   | SYNC on lead time        | 4.5                   | 5.0 | 5.5     | ms                  | $C_{SINE} = 0$<br>$R_{SYNC} = 154k\Omega$<br>$C_{SYNC} = 47nF$ |

| T <sub>SYNC(OFF)</sub>  | SYNC off delay           | -250                  | 0   | +250    | μs                  | C <sub>SINE</sub> = 10nF                                       |

| t <sub>SYNC(rise)</sub> | SYNC rise time           | -                     | -   | 300     | ns                  | C <sub>L</sub> = 50pF                                          |

| t <sub>SYNC(fall)</sub> | SYNC fall time           | -                     | -   | 300     | ns                  | C <sub>L</sub> = 50pF                                          |

| Sym                          | Parameter                      | Min                  | Тур                  | Max                  | Units       | Conditions                                                                                                                                       |

|------------------------------|--------------------------------|----------------------|----------------------|----------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| PWM Fred                     | quency                         |                      |                      |                      |             |                                                                                                                                                  |

| f <sub>PWM</sub>             | PWM frequency                  | 21.25<br>127.5       | 25.00<br>150.0       | 28.75<br>172.5       | kHz<br>kHz  | $R_{PWM}$ = 500kΩ $R_{PWM}$ = 83kΩ                                                                                                               |

| t <sub>PWMSYNC(OUT)</sub>    | PWM sync output pulse width    | 30                   | 50                   | 70                   | ns          |                                                                                                                                                  |

| t <sub>PWMSYNC(IN)</sub>     | PWM sync input pulse width     | 25                   | -                    | -                    | ns          |                                                                                                                                                  |

| f <sub>PWMSYNC(IN)</sub>     | PWM sync input frequency range | 25                   | -                    | 150                  | kHz         |                                                                                                                                                  |

| $V_{\text{PWMSYNC(lo)}}$     | PWM sync output low voltage    | -                    | -                    | 0.2                  | V           | I <sub>OUT</sub> = 1.0mA sink                                                                                                                    |

| PWMSYNC                      | PWM sync pull-up current       | -                    | 100                  | -                    | μA          |                                                                                                                                                  |

| Switch Dr                    | iver Outputs                   |                      |                      |                      |             |                                                                                                                                                  |

| $V_{OUT(lo)}$                | Output voltage, low            | -                    | -                    | 0.2                  | V           | I <sub>OUT</sub> = 20mA sink                                                                                                                     |

| $V_{\text{OUT(hi)}}$         | Output voltage, high           | V <sub>GD</sub> -0.2 | -                    | -                    | V           | I <sub>OUT</sub> = 20mA source                                                                                                                   |

| t <sub>RISE</sub>            | Rise time                      | -                    | -                    | 50                   | ns          | C <sub>L</sub> = 4nF                                                                                                                             |

| $t_{\scriptscriptstyleFALL}$ | Fall time                      | -                    | -                    | 50                   | ns          | C <sub>L</sub> = 4nF                                                                                                                             |

| Timing                       |                                |                      |                      |                      |             |                                                                                                                                                  |

| D                            | Duty cycle                     | 23<br>48<br>73       | 25<br>50<br>75       | 27<br>52<br>77       | %<br>%<br>% | PWM <sub>IN</sub> = 0.625V<br>PWM <sub>IN</sub> = 1.250V<br>PWM <sub>IN</sub> = 1.875V<br>V <sub>DCL</sub> = 0V                                  |

| D <sub>limit</sub>           | Duty cycle limit               | 12<br>72<br>22<br>62 | 20<br>80<br>30<br>70 | 28<br>88<br>38<br>78 | %<br>%<br>% | $V_{DCL} = 0.50V, PWM_{IN} = 0V$<br>$V_{DCL} = 0.50V, PWM_{IN} = 2.5V$<br>$V_{DCL} = 0.75V, PWM_{IN} = 0V$<br>$V_{DCL} = 0.75V, PWM_{IN} = 2.5V$ |

| I <sub>DCL</sub>             | V <sub>DCL</sub> input current | -                    | -                    | 1.0                  | μA          | V <sub>DCL</sub> = 0 - 1.0V                                                                                                                      |

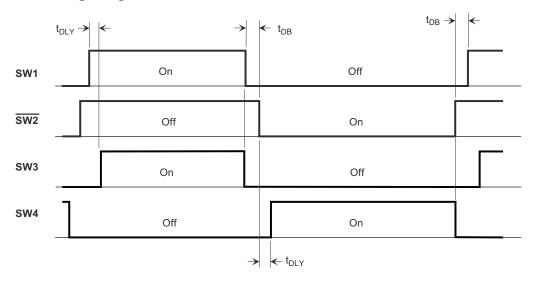

| t <sub>DB</sub>              | Primary switch deadband        | 0<br>0.95            | 100<br>1.00          | 150<br>1.05          | ns<br>µs    | $C_{DB} = 0pF$<br>$R_{DB} = 14k\Omega, C_{DB} = 100pF$                                                                                           |

|                              |                                |                      |                      |                      |             |                                                                                                                                                  |

0

0.95

Secondary switch delay

$\boldsymbol{t}_{\text{DLY}}$

100

1.00

150

1.05

ns

μs

$$\begin{split} &C_{\tiny DLY} \text{= 0pF} \\ &R_{\tiny DLY} \text{= 14k}\Omega, \ C_{\tiny DLY} \text{= 100pF} \end{split}$$

#### **Switch Outputs**

| ENABLE | AMP | OFF | SW1       | SW2       | SW3       | SW4       |

|--------|-----|-----|-----------|-----------|-----------|-----------|

| 0      | 00  | XX  | Off       | Off       | Off       | Off       |

| 0      | ≠00 | XX  | Off       | Off       | Switching | Switching |

| 1      | XX  | XX  | Switching | Switching | Switching | Switching |

$X = don't \ care, \neq 00 = 01,10, \ or \ 11$

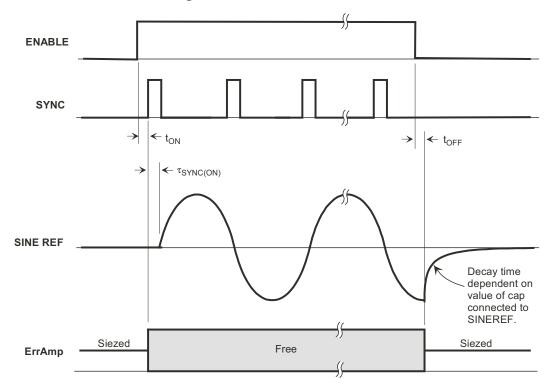

**Figure 1: Switch Timing Diagram**

Figure 2: ENABLE and SYNC Timing - SYNCMODE = 0

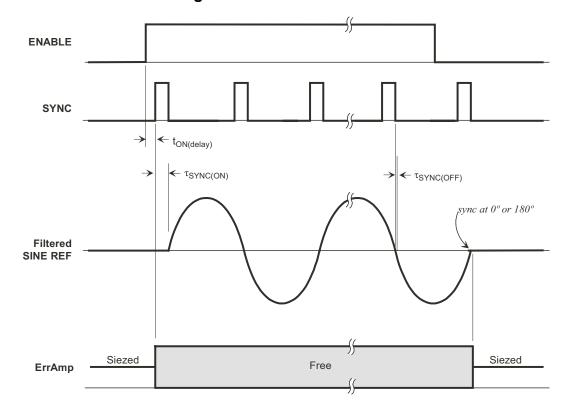

Figure 3: ENABLE and SYNC Timing - SYNCMODE = 1

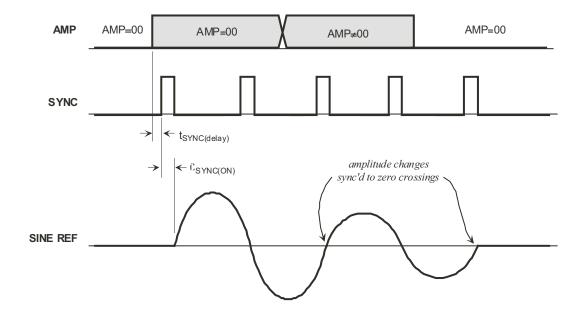

**Figure 4: AMP Timing**

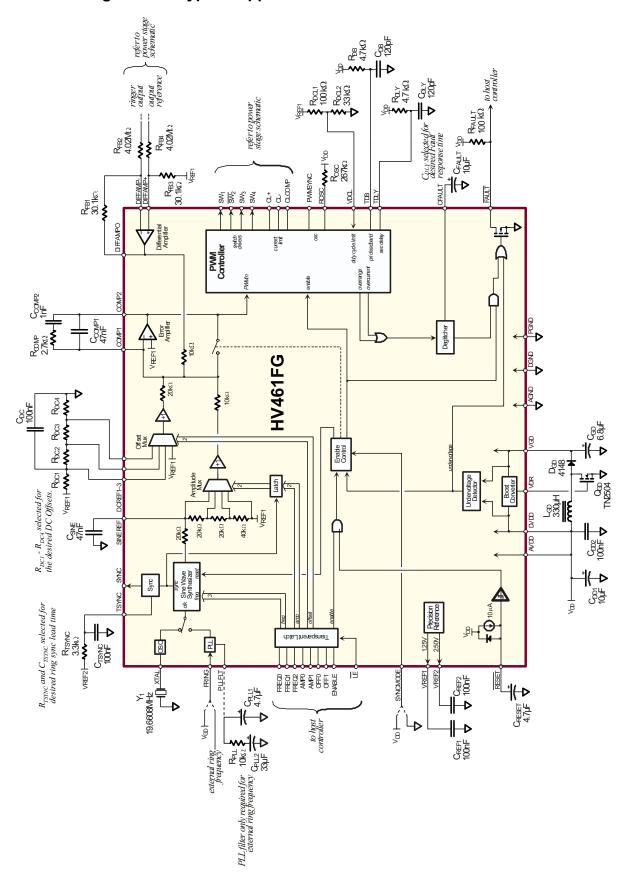

## **Typical Application**

Figures 5 and 6 on pages 9 and 10 show the schematic of a typical 15 REN ring generator application. The basic design

equations for elements connected to different pins are given in the Pin Descriptions Table beginning on page 11.

Figure 5: Block Diagram and Typical Applicatin Circuit

Figure 6: Typical Power Stage for 15 REN Ring Generator

# Pin Description (refer to pin configuration on page 2)

| Pin | Name    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | DCREF3  | See DCREF1 and DCREF2 (pins 47 & 48).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2   | VREF1   | Outputs a 1.25V nominal reference voltage. Bypass with a 100nF capacitor to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3   | VREF2   | Outputs a 2.50V nominal reference voltage. Bypass with a 100nF capacitor to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4   | AVDD    | Supply for the analog section. 3.0 to 3.6V Must be from the same source as DVDD. Bypass with a 100nF capacitor to ground as close as possible to the IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5   | TSYNC   | An RC network connected to this pin determines the SYNC pulse lead time (see SYNC pin 14). $t_{LEAD} = 0.48RC$ If SYNC is not utilized, TSYNC must still have a connected RC network.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6   | XTAL    | A crystal from this pin to ground provides the frequency reference for the internal sine wave synthesizer. A 19.6608MHz baud rate crystal provides the 8 most common ring frequencies. The crystal is operated in the series mode. A loading capacitor is not necessary. See also FREQ0–2 (pins 21–23) and FRING (pin 7).                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7   | FRING   | Ring frequency is normally selected from the 8 built-in frequencies using control inputs FREQ0–2. Other arbitrary frequencies in the range of 12 to 63Hz may be obtained by applying an external signal to FRING. This external signal sets the ring frequency at a 1:1 ratio. The ring signal remains a sine wave, with amplitude and offset still controlled via AMPx and OFFx. The ring signal, while frequency locked to the FRING signal, is not phase–synchronized to it. This allows the ring signal to immediately start at 0° when enabled via ENABLE or AMP ≠ 00. When unused, this input must be connected to VGD.                                                                                                         |

| 8   | PLLFLT  | Phase locked loop filter. An RC network connected to this pin stabilizes the PLL that locks on to the optional external ring frequency signal. (See FRING, pin 7) The RC network determines the lock time of the PLL. Due to the low frequencies involved, it may take a couple seconds to lock to the external signal. See the typical application schematic for typical values. When unused, this pin should be left unconnected.                                                                                                                                                                                                                                                                                                   |

| 9   | ROSC    | A resistor from this pin to VDD sets the PWM frequency. $f_{PWM} \approx 12.5 GHz\Omega / R_{OSC}$ (valid for 20-150kHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10  | RESET   | A capacitor from this pin to ground provides a power—on reset interval. It has an internal $10\mu A$ pull—up to charge the external reset capacitor. Alternatively, an external logic—level or open—drain signal may be applied to implement the reset function. During the reset interval when $V_{RESET}$ <1.325V, the ringer output is disabled regardless of the state of the ENABLE input, allowing time for the host controller to assume control. Use a low leakage tantalum or ceramic capacitor. $t_{RESET}$ = 1.325V · $C_{RESET}$ / $10\mu A$                                                                                                                                                                              |

| 11  | PWMSYNC | This pin functions as both an input and an output. It is open—drain with an internal 100µA pullup. As an output, it provides a short, low-going pulse at the internal PWM frequency. As an input, it synchronizes internal PWM frequency to the externally applied signal, provided the external signal is at a higher frequency. The low-going applied sync pulse should be between 25ns and less than the PWM period in duration. The external source should be open drain. If the PWMSYNC pins of multiple HV461s are tied together, their PWM frequencies will be phase-locked to the HV461 with the highest free-running frequency. A maximum of 10 HV461s may be tied together. If unused, this pin should be left unconnected. |

| 12  | CFAULT  | A capacitor from this pin to ground sets the integration time of the FAULT detection circuitry. A larger capacitor provides less suseptability to transient problems, while a smaller capacitor provides quicker response. Values in the range of $1\mu F$ to $100\mu F$ are appropriate. If the FAULT output is not used, this pin should be grounded. See also FAULT (pin 15).                                                                                                                                                                                                                                                                                                                                                      |

# **Pin Description (cont.)**

| Pin | Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| 13  | SYNCMODE | With SYNCMODE low, ringer output ceases the instant ENABLE goes low. When high, ringer output ceases at the next ring signal phase crossing (0°/180°) after ENABLE goes low.                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| 14  | SYNC     | Outputs a pulse indicating sine reference 0° and 180° phase crossing (not to be confused with zero–voltage crossing). The rising edge precedes phase crossing by a user–adjustable time period (see TSYNC pin 44). Falling edge coincides with sine reference phase crossing. SYNC is digitally derived, therefore phase shifts caused by the external filter capacitor at SINEREF will not be reflected at the SYNC output.                                                                                                                                |  |  |  |  |  |  |  |  |  |

| 15  | FAULT    | Indicates abnormal operating conditions of output overcurrent, supply undervoltage (VDD & VGD), or PWM overrange (duty cycle limit – see VDCL, pin 3). Together, these 3 conditions catch most any problem. When an overcurrent or overrange condition exists for more than 8% of the time, this output becomes active. It is cleared when the problem occurs less than 2% of the time. Undervoltage conditions immediately activate the FAULT output. It is active low and open drain to allow wire-ORing. See CFAULT (pin 15) for additional information. |  |  |  |  |  |  |  |  |  |

| 16  | ENABLE   | Ringer output enable. Active high. When enabled, the ring signal always starts immediately at 0 degrees. If AMP≠00, SW1 and SW2 are held off when ENABLE=0 but SW3 and SW4 continue switching. If AMP=00, SW3 and SW4 are held off as well. When disabled, the error amplifier is set at unity gain to prevent saturation, reducing turn-on glitches when re-enabled. See SYNCMODE (pin 13) for additional information.                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| 17  | OFF0     | Sets ring DC offset. Offset changes are effected at the next phase crossing $(0^{\circ}/180^{\circ})$ of the ring signal. Except for 00, offsets are set by the voltages at DCREF1–3. (OFF0 is LSB) Offset = $\frac{1}{2}$ x                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| 18  | OFF1     | Gain x $(V_{DCREFx} - V_{REF1})$<br>00 = 0V $01 = DCREF1$ $10 = DCREF2$ $11 = DCREF3$                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

| 19  | AMP0     | Sets ring amplitude. Amplitude changes are effected at the next phase crossing (0°/180°) of the ring signal. Amplitudes, as a percentage of full scale, are: (AMP0 is LSB)                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |

| 20  | AMP1     | Full scale amplitude = 0.707V <sub>RMS</sub> x Gain  00 = 0%  01 = 50%  10 = 75%  11 = 100%                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |  |

| 21  | FREQ0    | Sets ring frequency. Frequency changes are effected at the next phase crossing (0°/180°) of the ring signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| 22  | FREQ1    | Frequencies when using a 19.6608MHz crystal are: (FREQ0 is LSB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

| 23  | FREQ2    | 000 = 16.7Hz 001 = 20Hz 010 = 25Hz 011 = 30Hz<br>100 = 33.3Hz 101 = 40Hz 110 = 50Hz 111 = 60Hz                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

| 24  | ĪĒ.      | Latch enable. The latch gates control inputs FREQ0–2, AMP0–1, OFF0–1, and ENABLE. When LE is high, latch outputs follow inputs. On a low–going transition, outputs are latched.                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

| 25  | TDLY     | An RC network on this pin sets the primary to secondary switch delay. This prevents the secondary–side switches (SW3&4) from turning on prematurely. $t_{DLY}$ = 0.48RC                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

| 26  | TDB      | An RC network on this pin sets the deadband (break–before–make time) on the primary–side switches (SW1&2). Deadband prevents both switches from conducting simultaneously. $t_{DB} = 0.48RC$                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| 27  | DGND     | Digital ground. Connect to AGND and PGND close to the IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| 28  | SW4      | Secondary–side switch driver output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

| 29  | SW3      | Secondary–side switch driver output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

| 30  | SW2      | Primary–side N-channel switch driver output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |  |

| Pin | Name     | Description                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 31  | SW1      | Primary-side P-channel switch driver out                                                                                                                                                                                                                                                                   | Primary–side P-channel switch driver output.                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| 32  | PGND     | Power ground. Connect to AGND and DO                                                                                                                                                                                                                                                                       | GND close to the IC.                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| 33  | VGD      | Supply for the SW1–4 drivers. An external boost converter controlled by VDR provides 9.6V for driving the power stage MOSFETs. An undervoltage condition on this supply pin disables ringer butput and activates the FAULT output.                                                                         |                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 34  | VDR      | PWM frequency (see ROSC, pin 9). Outp                                                                                                                                                                                                                                                                      | Gate drive for the external boost converter circuit. Outputs a fixed 50% duty cycle at the ringer PWM frequency (see ROSC, pin 9). Output voltage regulation is via burp-mode operation. This butput is boostrapped to VGD, thus during startup VDR amplitude is VDD and after startup is VGD. (See VGD, pin 33) |  |  |  |  |  |  |  |

| 35  | DVDD     | Supply for the digital section. 3.0V to 3.6V input. Undervoltage disables ringer output. Must be from the same source as AVDD. Bypass with a 100nF capacitor to ground as close as possible to the IC. An undervoltage condition on this supply pin disables ringer output and activates the FAULT output. |                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 36  | CL+      | Current limit amplifier non-inverting input.                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 37  | CL-      | Current limit amplifier inverting input.                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 38  | CLCOMP   | Current limit compensation. An RC network connected between this pin and CL- establishes current limit reaction time and stability.                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 39  | DIFFAMP+ | Differential amplifier non-inverting input.                                                                                                                                                                                                                                                                | The differential amplifier sets gain, establishing output                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| 40  | DIFFAMP- | Differential amplifier inverting input.                                                                                                                                                                                                                                                                    | amplitude and DC offset in conjunction with AMPx and OFFx.  Gain = $R_{ER2}/R_{ER1}$ ( $R_{ER3}$ = $R_{ER1}$ and $R_{ER4}$ = $R_{ER2}$ ,                                                                                                                                                                         |  |  |  |  |  |  |  |

| 41  | DIFFAMPO | Differential amplifier output.                                                                                                                                                                                                                                                                             | see schematic)                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| 42  | COMP2    | Error amplifier compensation. An RC net stability.                                                                                                                                                                                                                                                         | work connected between these pins establishes loop                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| 43  | COMP1    | COMP1 is the error amp inverting input.                                                                                                                                                                                                                                                                    | COMP2 is the error amp output.                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| 44  | SINEREF  |                                                                                                                                                                                                                                                                                                            | nominal. Output impedance is approximately $16k\Omega$ . An pround should be employed to remove high frequency at a frequency of $2^{15} \cdot f_{RING}$                                                                                                                                                         |  |  |  |  |  |  |  |

| 45  | AGND     | Analog ground. Connect to AGND and D                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 46  | VDCL     | Voltage applied to this pin sets the min/max d of the ringer output will occur and the FAULT                                                                                                                                                                                                               | uty cycle limits. If the PWM controller hits these limits, clipping output will be activated. $D_{MIN} = 0.4 V_{DCL}$ $D_{MAX} = 1 - 0.4 V_{DCL}$                                                                                                                                                                |  |  |  |  |  |  |  |

| 47  | DCREF1   | In conjunction with the OFFx control inputs, v                                                                                                                                                                                                                                                             | oltages applied to these inputs set the output DC offset. Output                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| 48  | DCREF2   |                                                                                                                                                                                                                                                                                                            | ied by gain. See also OFF0 & OFF1 (pins 17 & 18)                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

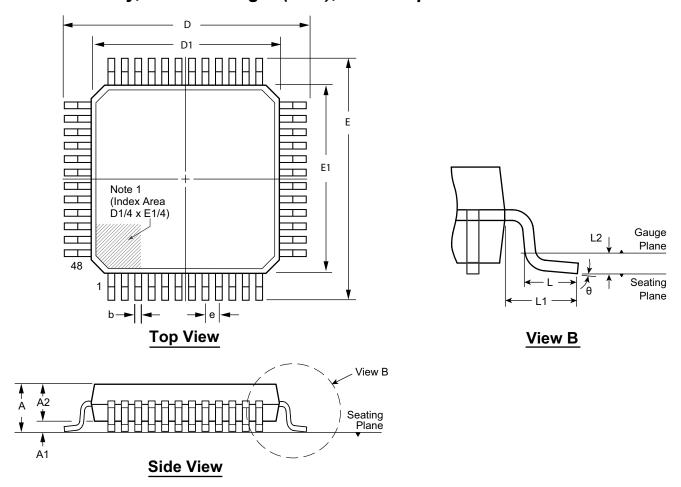

# 48-Lead LQFP Package Outline (FG)

#### 7.00x7.00mm body, 1.60mm height (max), 0.50mm pitch

#### Note:

A Pin 1 identifier must be located in the index area indicated. The Pin 1 Identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

| Symbo          | ol  | Α     | A1   | A2   | b    | D     | D1    | E     | E1    | е           | L    | L1          | L2          | θ          |

|----------------|-----|-------|------|------|------|-------|-------|-------|-------|-------------|------|-------------|-------------|------------|

| Dimension (mm) | MIN | 1.40* | 0.05 | 1.35 | 0.17 | 8.80* | 6.80* | 8.80* | 6.80* | 0.50<br>BSC | 0.45 | 1.00<br>REF | 0.25<br>BSC | <b>0</b> ° |

|                | NOM | -     | -    | 1.40 | 0.22 | 9.00  | 7.00  | 9.00  | 7.00  |             |      |             |             | 3.5°       |

| ()             | MAX | 1.60  | 0.15 | 1.45 | 0.27 | 9.20* | 7.20* | 9.20* | 7.20* |             | 0.75 |             |             | <b>7</b> ° |

JEDEC Registration MS-026, Variation BBC, Issue D, Jan. 2001.

\* This dimension is not specified in the original JEDEC drawing. The value listed is for reference only.

Drawings are not to scale.

Supertex Doc. #: DSPD-48LQFPFG Version, B090808.

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="http://www.supertex.com/packaging.html">http://www.supertex.com/packaging.html</a>.)

Supertex inc. does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an adequate "product liability indemnification insurance agreement." Supertex inc. does not assume responsibility for use of devices described, and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications refer to the Supertex inc. website: http://www.supertex.com.

©2008 Supertex inc. All rights reserved. Unauthorized use or reproduction is prohibited