#### Introduction

The Supertex HV301DB2 demo board contains all necessay circuitry to demonstrate the features of the HV301 hotswap controller. Intended primarily as a negative hotswap controller, the HV301 controls the negative supply path.

Included on board is a 100 $\mu$ F capacitor to provide a capacitive load for testing. Additional capacitance (up to 2000 $\mu$ F) may be connected to the V<sub>OUT</sub> terminals, or the 100 $\mu$ F may be removed altogether

The board may be modified to meet custom requirements. Instructions are provided on the next page for modifications.

### Specifications

| Input Voltage        | 10V to 90V          |

|----------------------|---------------------|

| Inrush Limit         | 1A ±20%             |

| Circuit Breaker Trip | 2A ±20%             |

| Retry Interval       | 12sec min           |

| On Resistance        | 165m $\Omega$ max   |

| Undervoltage Trip    | 35.0V on, 32.2V off |

| Overvoltage Trip     | 64.5V on, 70.0V off |

| Power Good Signal    | Active High         |

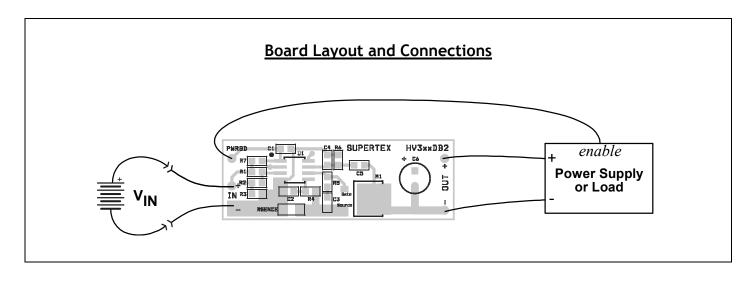

#### $V_{IN}$

Connect the supply voltage to these terminals. Supply voltage may range from 10 volts to 90 volts.

A high source impedance may cause oscillations when the input voltage is near the undervoltage trip point. A high source impedance results in a large voltage drop when loaded, causing undervoltage lockout to kick in, disconnecting the load. With the load removed, input voltage rises, causing undervoltage to release and reconnecting the load. The cycle repeats, resulting in oscillations. <u>Source impedance must be less than the following to avoid oscillations:</u>

$$R_{SOURCE} < \frac{3\mathrm{V}}{I_{LOAD}}$$

# Vout

Connect the power supply or other load to these terminals.  $V_{\text{OUT+}}$  is permanently connected to  $V_{\text{IN+}}$ , it is  $V_{\text{OUT-}}$  that is switched.

Application of a DC load during start-up extends the time inrush limiting is active. If this time exceeds 100ms, the

HV301 shuts off, retrying 12s later. For this reason, DC load at start-up should be less than 900mA. Note that DC start-up load limitation decreases with added load capacitance.

Adding external load capacitance increases inrush limit time. Since inrush time is internally limited to 100ms, a maximum of  $2000\mu$ F may be added

#### PWRGD

Connect to the power supply's ENABLE input. Depending on the power supply, it may be necessary to level-translate this signal via opto-isolator or discrete circuit. Refer to the HV301/311 data sheet for a description of PWRGD and related application circuits.

PWRGD is an open-drain output. During start-up and whenever  $V_{IN}$  is lower than the undervoltage trip point or greater than the overvoltage trip point, PWRGD is high impedance. Once  $V_{IN}$  is within the proper range and  $V_{OUT}$  has stabilized, PWRGD is pulled down to  $V_{IN-}$ .

#### **Inrush Limit**

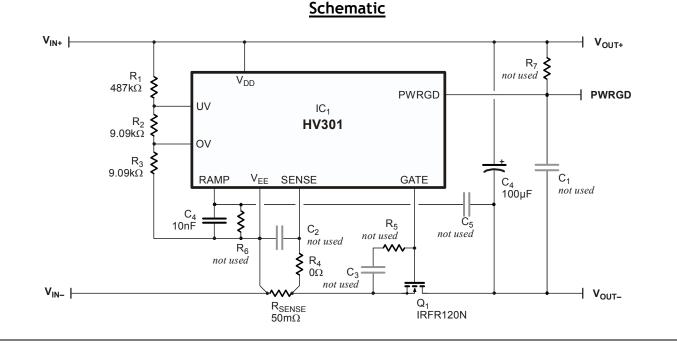

As supplied, the inrush current limit is set at 1 amp. To set inrush limit to another value, change current sense resistor  $R_{\mbox{\scriptsize SENSE}}$  according to the formula:

$$R_{SENSE} = \frac{50 \text{mV}}{I_{INRUSH}}$$

The circuit breaker trip point ( $I_{CB}$ ) is 2 times the inrush limit. For other ratios, refer to the 'Programming Inrush &  $I_{CB}$ ' section of the HV301/311 data sheet.

The power rating of  $R_{\text{SENSE}}$  should be selected based on maximum current during normal operation, which could be just under the circuit breaker trip point.

$$P_{SENSE} = I_{CB}^{2} R_{SENSE}$$

# Timing

Timing capacitor C<sub>4</sub> determines start-up delay, rise time, and circuit breaker retry interval. Changing C<sub>4</sub> will alter these timings. Refer to the HV301/311 datasheet for the equations that relate these timings to the value of C<sub>4</sub>. For use in the equations, the nominal gate threshold voltage (V<sub>GS</sub>) of the supplied IRFR120N is 3V and transconductance is about 10 siemens.

### **Circuit Breaker Transient Immunity**

The HV301 has built-in transient immunity of  $2-5\mu$ s. To increase transient immunity, an RC low-pass filter (R<sub>4</sub>C<sub>2</sub>) may be placed on the SENSE input. (The demo board is supplied with no filtering.)

Be aware that filtering the sense input will cause the inrush current limit to overshoot at turn-on – the greater the filtering, the greater the overshoot.

#### Undervoltage/Overvoltage Lockout

Resistors  $R_1$ ,  $R_2$ , and  $R_3$  set the undervoltage and overvoltage trip points. New trip points may be programmed by changing the values of these resistors. Refer to the HV301/311 data sheet for more information.

#### **Additional Components**

The RC network  $(R_5C_3)$  across the gate-source of the external FET provides control loop compensation which prevents inrush current peaking.

A resistor at  $R_7$  can be used to provide a passive pull-up for the PWRGD signal.

A 10nF capacitor at  $C_1$  may be needed for stability to limit dV/dt if PWRGD experiences large voltage swings.

A 2.4M  $\Omega$  resistor in the R6 location can be used to defeat the circuit breaker auto-retry function.