# bq77908EVM Evaluation Module

The bq77908EVM-001 evaluation module (EVM) is a complete evaluation system for the bq77908, a fourto eight-cell Li-ion battery protection integrated circuit. The EVM consists of a bq77908 circuit module and a resistor cell simulator module, which can be used for simple evaluation of the bq77908 functions. The circuit module includes one bq77908 integrated circuit (IC), sense resistor, power FETs and all other onboard components necessary to protect the cells from overcharge, overdischarge, short circuit, and overcurrent discharge in a 8-series cell Li-ion or Li-polymer battery pack. The circuit module connects directly across the cells in a battery. With a compatible interface board and Windows<sup>™</sup>-based PC software, the user can view the bq77908 registers and program the IC configuration and protection limits.

Contents

| 1 | Featur | 'es                                         | 3  |

|---|--------|---------------------------------------------|----|

|   | 1.1    | Kit Contents                                | 3  |

|   | 1.2    | Required Equipment                          | 3  |

| 2 | bq779  | 08 Circuit Module and Interfaces            | 3  |

|   | 2.1    | Circuit Module Connections                  | 3  |

|   | 2.2    | Signal Descriptions                         | 4  |

| 3 | bq779  | 08EVM Hardware Connection and Operation     | 5  |

|   | 3.1    | Initial Considerations                      | 5  |

|   | 3.2    | Connecting the Cell Simulator               | 6  |

|   | 3.3    | Simulated Battery Connection                | 6  |

|   | 3.4    | Pack Connections                            | 6  |

|   | 3.5    | Basic Operation                             | 8  |

|   | 3.6    | Cell Connections                            | 8  |

| 4 | Softwa | are Installation                            | 9  |

|   | 4.1    | System Requirements                         |    |

|   | 4.2    | Interface Adapter                           |    |

|   | 4.3    | Install bq77910GUI Evaluation Software      |    |

| 5 | Softwa | are Operation                               |    |

|   | 5.1    | Menu commands                               |    |

|   | 5.2    | Working With Register Values                |    |

|   | 5.3    | Status Section                              |    |

|   | 5.4    | Basic Operation With Software               |    |

|   | 5.5    | Operation With Other Interfaces or Hosts    |    |

| 6 |        | d Documents From Texas Instruments          |    |

| 7 | bq779  | 08EVM Circuit Description and Configuration |    |

|   | 7.1    | Battery Voltage Clamp                       |    |

|   | 7.2    | Device Power                                |    |

|   | 7.3    | Cell Monitor Inputs and Configuration       |    |

|   | 7.4    | Ground Connection                           |    |

|   | 7.5    | Current Sense Connections                   |    |

|   | 7.6    | Filter Capacitors                           | 20 |

|   | 7.7    | FET Circuits                                |    |

|   | 7.8    | Detection Sensing                           |    |

|   | 7.9    | Output Protection Components                |    |

|   | 7.10   | Reserved Pins                               | 22 |

|   |        |                                             |    |

Windows, Microsoft are trademarks of Microsoft Corporation. Total Phase, Aardvark are trademarks of Total Phase, Inc.

|   | 7.11 | Flag Outputs                            | 22 |

|---|------|-----------------------------------------|----|

|   |      | Thermal Sensor                          |    |

|   |      | ZEDE                                    |    |

|   |      | Programming Interface                   |    |

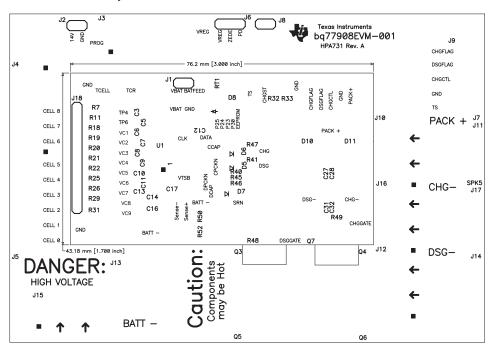

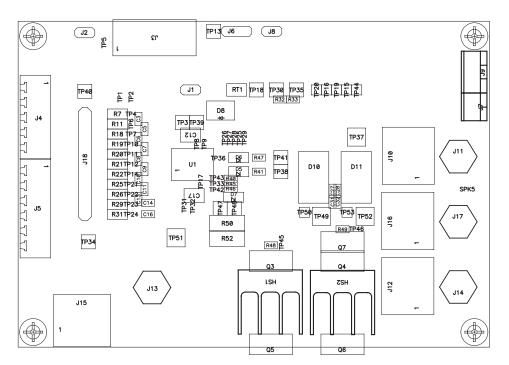

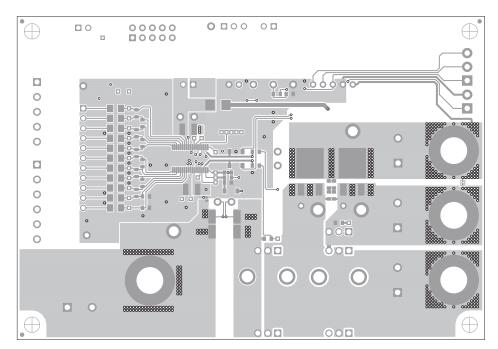

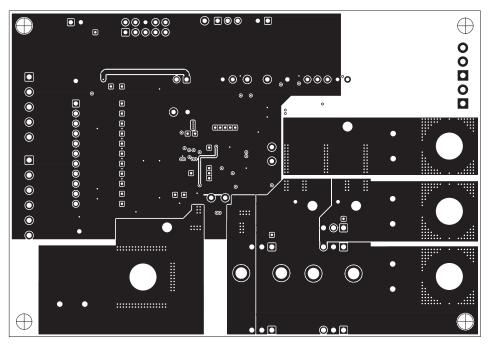

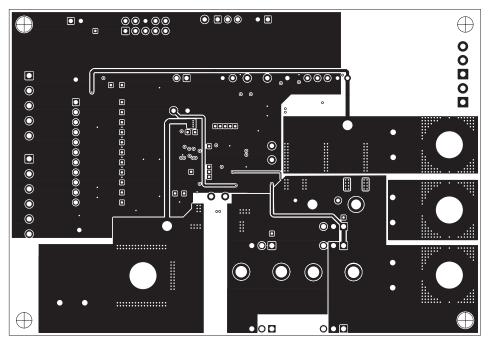

| 8 |      | 08 Circuit Module Physical Construction |    |

|   |      | Main Board                              |    |

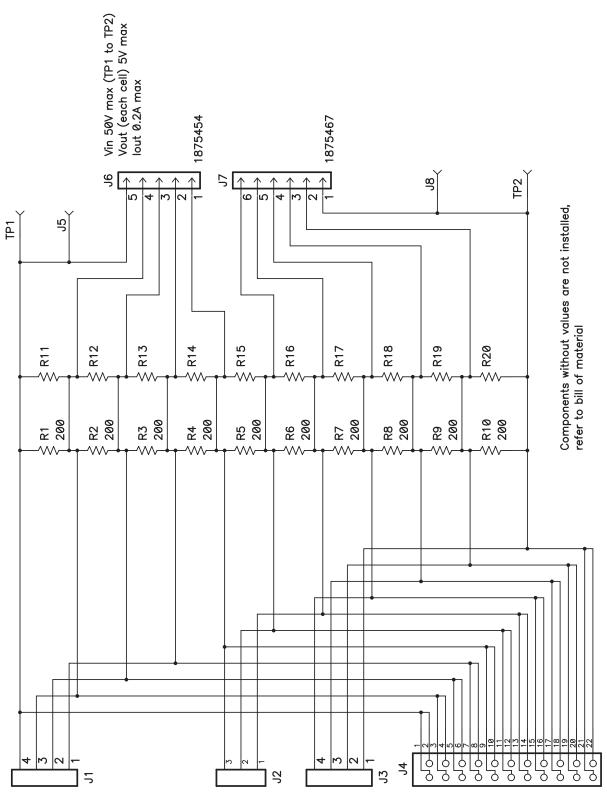

|   |      | Resistor Cell Simulator                 |    |

|   | -    |                                         | -  |

# List of Figures

| 1  | Basic EVM Setup                                  | 8  |

|----|--------------------------------------------------|----|

| 2  | Successfully Updated TI USB Interface Adapter    | 10 |

| 3  | EVM Connection for Communication and Programming | 11 |

| 4  | GUI With Communication Established               | 12 |

| 5  | Communication Selection Window                   | 13 |

| 6  | Commands Without Communication Established       | 13 |

| 7  | Register Section                                 | 14 |

| 8  | Status Section                                   | 16 |

| 9  | Polling Status With Undervoltage Condition       | 17 |

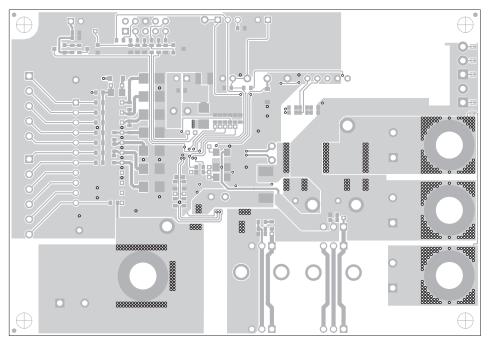

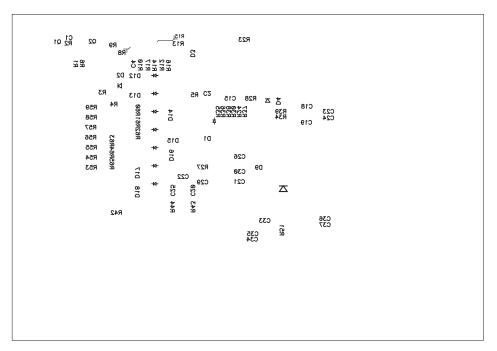

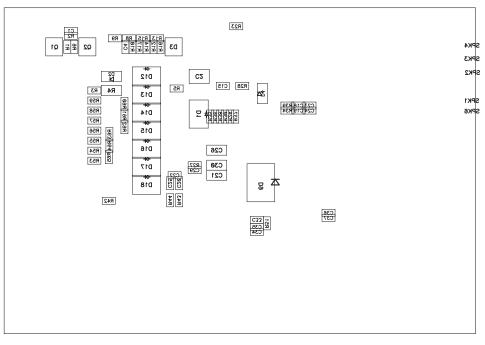

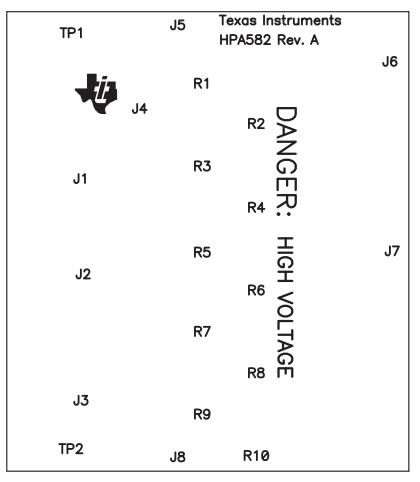

| 10 | Top Silk Screen                                  | 23 |

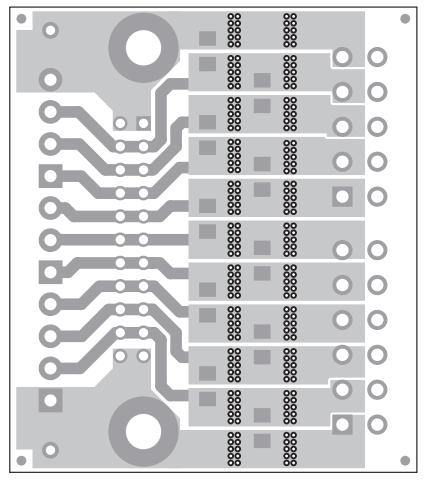

| 11 | Top Assembly                                     | 24 |

| 12 | Top Layer                                        | 24 |

| 13 | Layer 2                                          | 25 |

| 14 | Layer 3                                          | 25 |

| 15 | Bottom Layer                                     | 26 |

| 16 | Bottom Silk Screen                               | 26 |

| 17 | Bottom Assembly                                  | 27 |

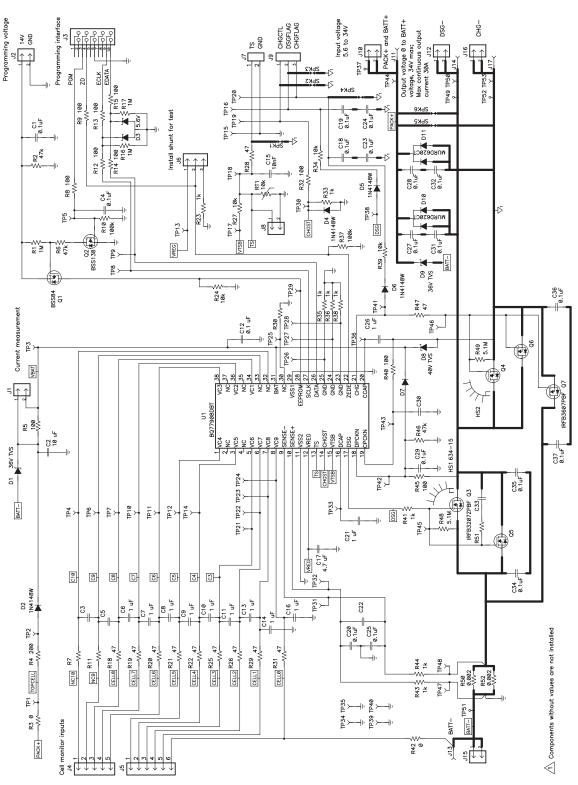

| 18 | Schematic Diagram, Sheet 1 of 2                  | 30 |

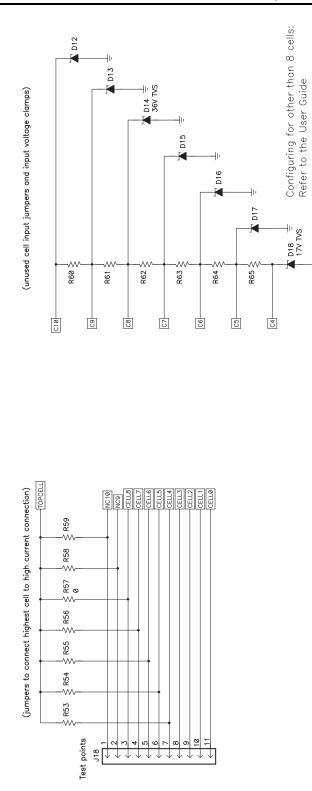

| 19 | Schematic Diagram, Sheet 2 of 2                  | 31 |

| 20 | Resistor Simulator Top Silk Screen               | 32 |

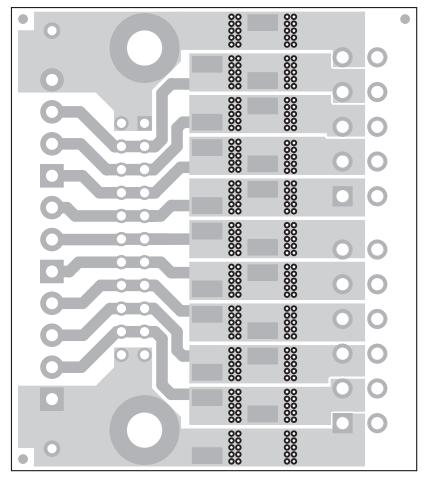

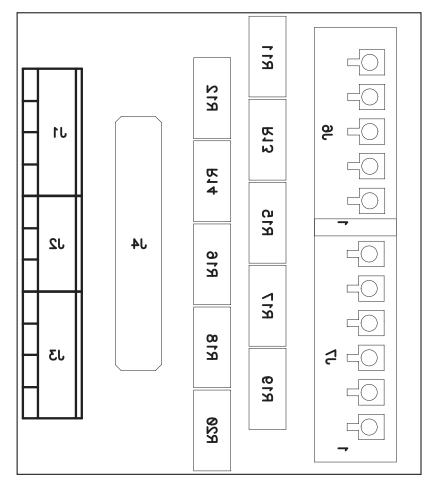

| 21 | Resistor Simulator Top Layer                     | 33 |

| 22 | Resistor Simulator Bottom Layer                  | 34 |

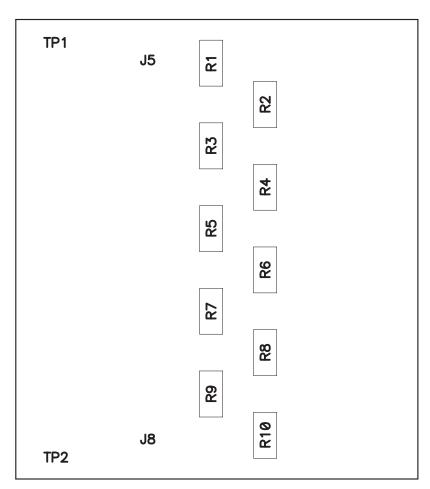

| 23 | Resistor Simulator Top Assembly                  | 35 |

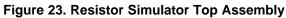

| 24 | Resistor Simulator Bottom assembly               | 36 |

| 25 | Resistor Simulator Schematic Diagram             | 38 |

#### List of Tables

| Ordering Information                     | 3                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cell Connections                         | 4                                                                                                                                                                                                                                                                                                                    |

| PACK Connections                         | 4                                                                                                                                                                                                                                                                                                                    |

| Programming Interface Connections        | 5                                                                                                                                                                                                                                                                                                                    |

| Test Header Signals                      | 5                                                                                                                                                                                                                                                                                                                    |

| Control and Status Connections           | 5                                                                                                                                                                                                                                                                                                                    |

| Adapter Cable Pinout                     | 10                                                                                                                                                                                                                                                                                                                   |

| Status Section Indicator Colors          | 16                                                                                                                                                                                                                                                                                                                   |

| Cell Count Component Configuration       | 19                                                                                                                                                                                                                                                                                                                   |

| bq77908 Circuit Module Bill of Materials | 27                                                                                                                                                                                                                                                                                                                   |

| Performance Specification Summary        | 32                                                                                                                                                                                                                                                                                                                   |

| Resistor Simulator Bill of Materials     | 36                                                                                                                                                                                                                                                                                                                   |

|                                          | Cell Connections<br>PACK Connections<br>Programming Interface Connections<br>Test Header Signals<br>Control and Status Connections<br>Adapter Cable Pinout<br>Status Section Indicator Colors<br>Cell Count Component Configuration<br>bq77908 Circuit Module Bill of Materials<br>Performance Specification Summary |

TEXAS INSTRUMENTS

#### www.ti.com

#### 1 Features

- Complete evaluation system for the bq77908 4-to-8 series cell Li-ion or Li-polymer battery protector

- Populated circuit module for 8-cell, parallel FET configuration for quick setup

- Pads for components for configuration of additional cell counts and series FETs

- · Power connections available on terminal blocks or banana jacks

- · Control and status signals available on terminal blocks

- Resistor cell simulator for quick setup with only a power supply

- · Personal computer software available for configuration

#### 1.1 Kit Contents

- bq77908 circuit module

- · Resistor cell simulator

- Set of support documentation

#### Table 1. Ordering Information

| EVM Part Number | Chemistry | Configuration | Capacity |

|-----------------|-----------|---------------|----------|

| bq77908EVM-001  | Li-ion    | 8 cells       | Any      |

**NOTE:** Although capacity Table 1 is show as Any, practical limits of the physical construction of the module typically limit the operation of the EVM to a 1P or 2P battery construction. See Section 8 for board details.

### 1.2 Required Equipment

The following equipment is required to operate the bq77908EVM in a simple demonstration.

- DC power supply, 0-V to 34-V at 0.5 A

- DC voltmeter or oscilloscope,

- DC power supply, ~3 V at .1 A or an approximately 15-kΩ, 1/4-W resistor

- Test leads to connect equipment

The following equipment is required to operate the bq77908EVM with a more extensive demonstration.

- TI USB-TO-GPIO interface adapter

- Computer with USB port and compatible Windows 32-bit operating system

- Electronic load

- Additional power supplies

- TI bq77910GUI Evaluation Software see Section 4.

### 2 bq77908 Circuit Module and Interfaces

The bq77908 circuit module contains the bq77908 IC and related circuitry to demonstrate the features of the IC. A FET with heatsink is provided for the high-current discharge path. A lower current FET is provided for the charge path. A thermistor provides temperature sensing for the device. Other components provide support for the IC and connections to the board.

# 2.1 Circuit Module Connections

Connections are provided for the following interfaces:

- Direct cell connections

- PACK connections

- Programming interface

3

Features

#### 2.2 Signal Descriptions

Signals available on the EVM are described in this section. For details on the location and connector types, see Section 8. High current signals can be connected at either the terminal block or banana jack. Refer to the physical construction section for identification.

Cell connections are described in Table 2. The default board assembly supports only 5 cells, so the upper cell connections are not used. CELL0 and CELL5 are connected to the high current paths on the board through  $0-\Omega$  resistors. This allows operation of the resistive cell simulator without external connections. If the onboard resistors are removed, connections must be made off the board. See Section 8 for resistor identification. Cell connection sequence is described in Section 3.6.

| Reference<br>Designator | Pin Number | Signal | Description                                                                             |  |

|-------------------------|------------|--------|-----------------------------------------------------------------------------------------|--|

| J13, J15                | All        | BATT-  | Negative electrode of first (bottom) cell, high-current connection                      |  |

| J5                      | 6          | CELL0  | Negative electrode of first (bottom) cell, optional separate monitor connection to cell |  |

|                         | 5          | CELL1  | Positive electrode of first (bottom) cell                                               |  |

|                         | 4          | CELL2  | Positive electrode of second cell                                                       |  |

|                         | 3          | CELL3  | Positive electrode of third cell                                                        |  |

|                         | 2          | CELL4  | Positive electrode of fourth cell                                                       |  |

|                         | 1          | CELL5  | Positive electrode of fifth cell,                                                       |  |

| J4                      | 5          | CELL6  | Positive electrode of sixth cell                                                        |  |

|                         | 4          | CELL7  | Positive electrode of seventh cell                                                      |  |

|                         | 3          | CELL8  | Positive electrode of eighth cell, optional separate monitor connection to cell         |  |

|                         | 2          | NC9    | Unused connection                                                                       |  |

|                         | 1          | NC10   | Unused connection                                                                       |  |

| J10, J11                | All        | PACK+  | Most positive cell output, high-current connection, shared with PACK+                   |  |

Load connections are described in Table 3.

#### **Table 3. PACK Connections**

| Reference<br>Designator | Pin Number | Signal | Description                                                                          |

|-------------------------|------------|--------|--------------------------------------------------------------------------------------|

| J10, J11                | All        | PACK+  | Positive output of evaluation board, shared with the battery high-current connection |

| J12, J14                | All        | DSG-   | Negative output of evaluation board for discharge                                    |

| J16, J17                | All        | CHG-   | Negative input to evaluation board for charge                                        |

Programming signals are described in Table 4. J3 signals are 3.3-V logic level.

| Reference<br>Designator | Pin Number    | Signal | Description                                    |

|-------------------------|---------------|--------|------------------------------------------------|

| J3                      | 1, 2, 5, 7, 8 |        | Not used                                       |

|                         | 3             | PGM    | Control signal for EEPROM programming voltage. |

|                         | 4             | ZD     | Control signal for device ZEDE                 |

|                         | 6             | GND    | Signal reference for the IC                    |

|                         | 9             | ECLK   | Serial interface clock connection              |

|                         | 10            | EDATA  | Serial interface data connection               |

| J2                      | 1             | 14V    | Regulated 14-V input for IC programming        |

|                         | 2             | GND    | Signal reference for the IC                    |

### **Table 4. Programming Interface Connections**

Test header or pattern signals are described in Table 5.

| Reference<br>Designato<br>r | Usage                                                                                                        | Pin Number | Signal          | Description                                                  |

|-----------------------------|--------------------------------------------------------------------------------------------------------------|------------|-----------------|--------------------------------------------------------------|

| J1                          | Default: shunt<br>installed for normal<br>operation. Remove<br>shunt for U1 supply<br>current<br>measurement | 1          | Battery<br>feed | Power feed to $100-\Omega$ shunt resistor                    |

|                             |                                                                                                              | 2          | BAT             | Output of 100- $\Omega$ shunt resistor to IC BAT pin         |

| J6                          | Default: no shunt.<br>Install shunt to hold<br>ZEDE high                                                     | 1          | VREG            | IC regulator output                                          |

|                             |                                                                                                              | 2          | ZEDE            | IC zero delay test point and input pin, also connected to J3 |

|                             |                                                                                                              | 3          | PD              | Pulldown resistor for strong pulldown of ZEDE if required    |

| J8                          | Not populated.                                                                                               | 1          | TS              | IC temperature sense pin                                     |

|                             | Alternate test point<br>or remote<br>thermistor<br>connection                                                | 2          | GND             | Signal reference for the IC                                  |

#### **Table 5. Test Header Signals**

Control and status signals are provided on terminal blocks. These signals are described in Table 6.

| Reference<br>Designator | Pin Number | Signal  | Description                                                                           |

|-------------------------|------------|---------|---------------------------------------------------------------------------------------|

| J7                      | 1          | TS      | IC TS signal through a resistor                                                       |

|                         | 2          | GND     | Signal reference for the IC                                                           |

| J9                      | 1          | CHGCTL  | Control signal for charger detection, connects through a resistor to the IC CHGST pin |

|                         | 2          | DSGFLAG | Diode and resistor isolated DSG signal                                                |

|                         | 3          | CHGFLAG | Diode and resistor isolated CHG signal                                                |

# 3 bq77908EVM Hardware Connection and Operation

This section describes the connection of the circuit module and EVM and simple operation in its default configuration.

# 3.1 Initial Considerations

Boards are tested after assembly with a basic functional test. This test may not check every connection on the board. Boards must be checked for function in the user's environment before relying on the safety features of the board. Operation of the board with test equipment before connecting cells is recommended and described in this document.

#### bq77908EVM Hardware Connection and Operation

The default configuration of the board is 8 cells with parallel FETs. Modifying the EVM for different cell counts or FET configuration requires solder connections. It is recommended that the users familiarize themselves with operation of the board in the default configuration before modifying the board, and check the operation of the board with test equipment after any modification. Configuration of the board is described in Section 7.

Be sure to observe the cautions and warnings in this document.

A variety of connections are provided on the EVM. The manufacturer's rating for the terminal blocks for Pack and Battery connections is 32 A nominal. Parallel connections are provided for high-current operation. The banana jacks are rated at 15 A. Safety agency ratings may be lower than the manufacturer ratings; limit currents to appropriate values for your evaluation. Cell monitor terminal blocks and the control signal terminal blocks are rated at lower currents and must not be used for high-current paths.

A communication interface is not required for basic operation; it must be connected to the computer and EVM circuit module only after proper installation of software. The software along with an appropriate communication interface allows setting the programmable safety limits of the device and checking the status after fault detection. Installation of the software and its use are described in Section 4 and Section 5, respectively.

### 3.2 Connecting the Cell Simulator

The cell simulator consists of headers to mate the board and ten  $200-\Omega$  resistors to divide the battery voltage between the inputs. Only 8 of these resistors are used for the bq77908 EVM. Power is provided through the Cell0 and Cell8 connections on the terminal block headers. Various test points are provided on the board. See Section 8 for additional details.

- Be certain no power is applied to the board.

- Unplug the screw terminal blocks from J4 and J5 of the EVM, and save these for later use.

- Plug the cell simulator board onto J4 and J5. Support may be required on the bottom of the EVM while the connectors are pressed together firmly.

#### CAUTION

Do not connect or remove the cell simulator board while power is applied to the EVM. The resistor pulldown or pullup from intermittent connections overstresses the device inputs.

### 3.3 Simulated Battery Connection

Connect a power supply between BATT- (negative) and PACK+ (positive). This power supply connects to the resistor cell simulator through default connections on the bq77908 circuit module.

### 3.4 Pack Connections

A load or charger is connected to the pack terminals using the terminal blocks provided. It is recommended that the load or charger be connected with the current switched off to prevent arcing or transients during connection of the wires to the terminal blocks. Charger detection is required for the bq77908 with a signal at the CHGST pin. Charger detection can be provided by connecting a resistor from the CHGCTL terminal of the board to the PACK supply, or with a logic level voltage supply for evaluation. An external resistor is required due to the low resistance pulldown on the board. The selected resistor must keep the CHGST voltage above the VCHG\_DET1 data sheet threshold over the entire evaluation voltage range while limiting the power in the 1-k $\Omega$  pulldown resistor to 1/16 W or less. A 15-k $\Omega$ , 1/4-W resistor is typically suitable for the default configuration; a smaller value may be required for low voltage or if the configuration is changed.

bq77908EVM Hardware Connection and Operation

# WARNING

The CHGCTL must not be tied to the power supply without the external resistor because the 1-k $\Omega$  resistor on the board becomes very hot and may damage the board.

Although designed for 30-A operation, the board may not dissipate enough power to operate without exceeding all component ratings. The user must monitor the temperature of the board and components during evaluation and provide cooling air and/or heatsinks as required for operation. The thermal sensor on the board may not respond to protect the FETs from damaging temperatures due to its location and possible thermal gradients on the board.

### CAUTION

The bq77908 circuit module may be damaged by overtemperature. To avoid damage, monitor the temperature during evaluation, and provide cooling as needed for your system environment.

# WARNING

The bq77908 circuit module may become hot during operation due to dissipation of heat. Avoid contact with the board. Follow all applicable safety procedures applicable to your laboratory.

# CAUTION

Some power supplies can be damaged by application of external voltages. If using more than one power supply, check your equipment requirements, and use blocking diodes or other isolation techniques as needed to prevent damage to your equipment.

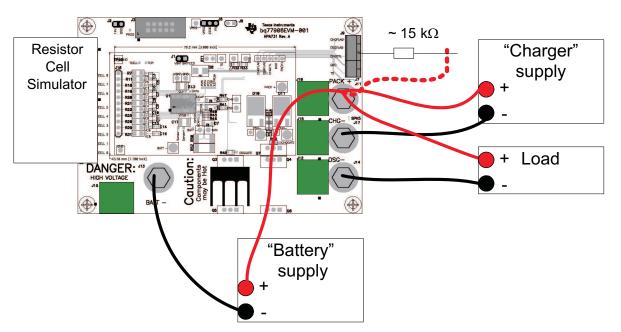

The connection of the EVM looks similar to Figure 1.

bq77908EVM Hardware Connection and Operation

Figure 1. Basic EVM Setup

# 3.5 Basic Operation

The following steps are suggested for basic operation of a default EVM with the cell simulator and the default configuration in EEPROM.

- 1. Confirm that the cell simulator board is installed on the EVM.

- 2. Connect a power supply between the BATT- (negative) and PACK+ (positive) terminals.

- 3. Connect a 15-k $\Omega$ , 1/4-W resistor to the CHGCTL terminal of the board.

- 4. Set the bench supply to approximately 29 V.

- 5. Connect a disabled load between the DSG- (negative) and PACK+ (positive) terminals.

- 6. Wake up the part by momentarily connecting the  $15 \cdot k\Omega$  resistor to the bench supply positive.

- 7. Monitor the CHG and DSG test points using a meter or oscilloscope as desired.

- 8. Enable the load with a nominal 0.2-A or other current within the capability of the supply.

- 9. Increase the bench supply voltage to approximately 34 V, and observe that the CHG output goes low.

- 10. Reduce the voltage to approximately 29 V, and observe that the CHG output returns high.

- 11. Decrease the voltage to approximately 20 V, and observe that the DSG output goes low and the load current drops. The device shuts down after 9 seconds at low voltage.

- 12. Remove the load, and connect the CHGCTL resistor to the supply to simulate a charger.

- 13. Increase the supply voltage to approximately 29 V, and observe that the DSG test point goes high, and if the load is re-connected, that current flows again.

# 3.6 Cell Connections

For initial evaluation, it is suggested power supplies be used for cell simulation to observe the behavior of the device. An isolated power supply with a resistor connected across its terminals may be connected to test points on the resistor simulator to vary the voltage above or below the voltage of the other cells, or a similar configuration may be used. The smaller the resistor value, the more current is required from the battery simulator power supply and the smaller the influence on the voltages if cell balancing is operated.

Whether power supplies or cells are used, inductance in the high-current path must be minimized. Inductance in this path can cause inductive transients at the board when the load current is stopped or the bq77908 opens the discharge FET with current flow. Use heavy-gauge wires for the high-current connections; minimize inductances by keeping leads close together.

When connecting cells to the EVM, the user must use care not to exceed the absolute maximum ratings of the device. The bq77908 is designed with open-cell (wire) detection; however, fixturing must not pull unconnected signals up or down. Signal reference (VSS) for the part is from the BATT- terminal of the EVM, and this lowest potential must be connected first. Cells must be connected in sequence from lowest to highest voltage as described in the data sheet. When terminating the cells to the removable terminal blocks prior to connection to the EVM, the following steps are recommended:

- 1. Be sure the charger and any load is disconnected (CHGCTL is open).

- 2. Connect the cell stack negative high-current terminal to the EVM BATT- terminal.

- 3. Connect the lower cell group to the J5 connector.

- 4. Connect the upper cell group to the J4 connector.

- 5. Connect the cell stack positive high-current terminal to the EVM PACK+ terminal.

- 6. When removing cells, remove any charger and CHGCTL connection, then disconnect in the reverse order.

#### 4 Software Installation

This section describes how to install the software for the bq77908EVM-001.

The bq77908 uses the same evaluation software as the bq77910.

#### 4.1 System Requirements

The bq77908 evaluation software requires a 32-bit version of Windows<sup>™</sup> XP, Windows Vista, or Windows 7. The computer must also have Microsoft<sup>™</sup> .NET framework version 2.0 or higher installed. Examples in this document are from Windows XP.

#### 4.2 Interface Adapter

The bq77908 evaluation software supports either the TI USB-TO-GPIO adapter (TI USB Interface Adapter) or the Total Phase<sup>™</sup> Aardvark<sup>™</sup> to provide communication with the EVM board from the computer. The Total Phase Aardvark must be selected if desired. The EVM connector supports the TI USB Interface Adapter; a special cable must be constructed if you wish to use the Aardvark.

#### 4.2.1 TI USB Interface Adapter

The TI USB Interface Adapter is the default option for the bq77908 evaluation software. Its pinout is compatible with the bq77908EVM board J3 connector.

The TI USB Interface Adapter <a href="http://focus.ti.com/docs/toolsw/folders/print/usb-to-gpio.html">http://focus.ti.com/docs/toolsw/folders/print/usb-to-gpio.html</a> is actually a separate EVM from Texas Instruments, and its default firmware is not compatible with the bq77908. If the firmware has already been updated to version 2.0.19 to work with other BMS-HCE products, additional update is not required. If required, update the firmware using the following steps.

- 1. Obtain the USB-to-GPIO EVM Firmware Loader from http://focus.ti.com/docs/toolsw/folders/print/usb2gpio-loader-sw.html, or search from power.ti.com

- 2. Download, extract, and run the installer

- 3. Installation requires the Microsoft .NET connection software. If a suitable version is not found on the system by the installer, the user is prompted to obtain and install .NET.

- 4. Connect the TI USB Interface Adapter to the computer with the USB cable. The green LED illuminates.

- 5. Run the program, typically from Start  $\rightarrow$  Run  $\rightarrow$  Texas Instruments  $\rightarrow$  USB-TO-GPIO Firmware Loader.

- 6. Detailed instructions are provided in the Readme.txt file.

#### CAUTION

Do not disconnect the USB cable to the Interface Adapter during firmware update. Loss of power may leave the adapter with corrupt firmware and be unable to further update the firmware.

Software Installation

www.ti.com

- 7. If you want to be able to return to the original configuration, back up the installed firmware before update.

- 8. Load and update to the 2.0.19 version using the instructions provided.

- 9. If an error occurs, do not unplug the adapter. Re-try loading, load a different firmware, or re-start the software and repeat until a load is successful.

- 10. After successful update, the window appears as is shown in Figure 2

- 11. After update, exit the program.

| Texas Instruments - USB-TO-GPIO Firmware Loader                                                                                     | × |

|-------------------------------------------------------------------------------------------------------------------------------------|---|

| File Tools About                                                                                                                    |   |

| 🗰 Find Device 💾 Backup 🔃 Load Image 🔒 Update                                                                                        |   |

| Connected Adapter<br>Adapter Version: 2.0.19 Adapter ID: FFFF Set<br>Group Owner: BMS<br>Loaded Firmware Image: usb_bms_v2.0.19.bin |   |

Figure 2. Successfully Updated TI USB Interface Adapter

#### 4.2.2 Aardvark Adapter

Although the Total Phase Aardvark adapter can physically mate to the EVM J3 connector, the pinout is incompatible. A special interface cable must be constructed to use the Aardvark. Refer to the schematics and Table 7 below for information.

#### CAUTION

Do not connect the Aardvark to the EVM without a properly constructed cable. Damage may result to the EVM and/or Aardvark.

| IC Pin Name<br>or Description                          | USB-TO-GPIO (Mates to J3) |        | Aardvark |           |  |

|--------------------------------------------------------|---------------------------|--------|----------|-----------|--|

|                                                        | Pin                       | Signal | Pin      | Signal    |  |

| VSS – signal reference                                 | 6                         | GND    | 2        | GND       |  |

| SCLK                                                   | 9                         | SCL    | 1        | SCL       |  |

| SDATA                                                  | 10                        | SDA    | 3        | SDA       |  |

| ZEDE -<br>communication<br>enable                      | 4                         | GPIO4  | 5        | MISO/GPIO |  |

| Programming<br>voltage control<br>signal for<br>EEPROM | 3                         | GPIO5  | 7        | SCLK/GPIO |  |

Table 7. Adapter Cable Pinout

# 4.3 Install bq77910GUI Evaluation Software

The bq77908 uses the same evaluation software as the bq77910. Find the latest software version in the bq77910GUI Evaluation Software tool folder on

http://focus.ti.com/docs/toolsw/folders/print/bq77910gui-sw.html, or search from power.ti.com. Check periodically for software updates. Use the following steps to install the bq77908 Evaluation Software:

- 1. Copy the archive file to a directory of your choice; extract and run the bq77910 Setup.msi installer.

- 2. Follow the instructions, and make selections as required on the setup windows, selecting next as required.

- 3. On the last window, select "close" to complete the bq77910 software installation.

### 5 Software Operation

This section describes connection of the communication interface to the EVM and operation of the software.

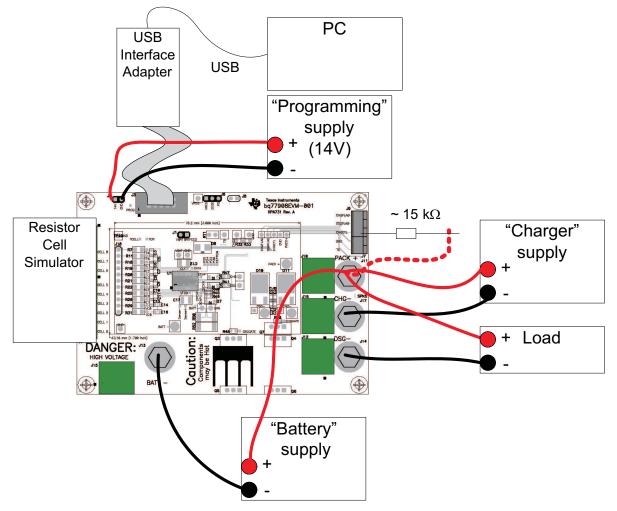

Although the software will run without connection to a powered device, it is recommended to have the device on when starting the software. Figure 3 shows connections for operation with the GUI software.

Figure 3. EVM Connection for Communication and Programming

To connect the computer to the GUI and start the software, use the following steps:

- 1. Connect the TI USB interface adapter to the computer.

- 2. Connect the 10-pin connector from the interface adapter to the EVM J3

TEXAS INSTRUMENTS

www.ti.com

Software Operation

#### CAUTION

The communication interface is not isolated on the EVM. Be sure no ground potential exists between the computer and the EVM. Also be aware that the computer is referenced to the battery-potential of the EVM.

- 3. Remove any shunt installed on J6 so that the interface can control ZEDE.

- 4. Connect the battery power supply to the EVM, and adjust to approximately 29 Vdc.

- 5. Wake the bq77908 by connecting CHGCTL high.

- 6. Start the software, typically using Start  $\rightarrow$  All Programs  $\rightarrow$  Texas Instruments  $\rightarrow$  bq77908 Evaluation.

When started, the software looks for the communication interface and the device. When communication is established with the device, the main window appears as shown in Figure 4. The software copies the EEPROM to the volatile registers.

| 🞆 Texas Instr | ments - bq77908 : bq77910 Evaluation v2.2.0.0                                                                                                  |                                                                                                                                                  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| File Comman   | ds Setup Help                                                                                                                                  |                                                                                                                                                  |

| • bq77908     | <ul> <li>bq77910</li> <li>Polling</li> <li>Enable</li> <li>Seconds</li> <li>Fault Status</li> <li>Parity</li> <li>Short Circuit Dsg</li> </ul> | Open Cell     Over Temp     Under Voltage     Over Current Dsg     Short Circuit Chg     Over Voltage     Shorted Thermistor     Open Thermistor |

|               | Volatile Registers                                                                                                                             | EEPROM View                                                                                                                                      |

|               |                                                                                                                                                |                                                                                                                                                  |

| SYS_CFG       | CNF2 CNF1 CNF0 CHGTMPDI THPEN OT_REC SHTDIS SOR 40                                                                                             | SYS_CFG CNF2 CNF1 CNF0 CHGTMPDI TMPEN 0T_REC SHTDIS SOR 4C                                                                                       |

| OV_CFG1       | 0VT 4.225 💙 35                                                                                                                                 | OV_CFG1 RSVD RSVD OVTS OVT4 OVT3 OVT2 OVT1 OVT0 39                                                                                               |

| OV_CFG2       | OV_T\$_CTRL OVH 100 VD 1.00 V                                                                                                                  | OV_CFG2 0VTSCTRL 0VH2 0VH1 0VH0 R5VD 0VD2 0VD1 0VD0 42                                                                                           |

| UV_CFG1       | UV_HYST_INH UVT 2.6 🗸 C                                                                                                                        | UV_CFG1 UVHYSTIIN RSVD RSVD RSVD UVT3 UVT2 UVT1 UVT0 C                                                                                           |

| UV_CFG2       | VUV_REC VUV_REC_DLY UVH 0.4 VVD 1.0 VC                                                                                                         | UV_CFG2 UV_REC URD UVH1 UVH0 RSVD UVD2 UVD1 UVD0 C1                                                                                              |

| OCD_DELAY     | 0CDD 500 💌 10                                                                                                                                  | OCD_DELAY RSVD RSVD 0CDD4 0CD03 0C002 0CDD1 0CD00 10                                                                                             |

| SCD_DELAY     | ISNS_RNG SCDD_RNG SCDD 960 💌 F                                                                                                                 | SCD_DELAY RSVD RSVD ISNS_RNG SCD0_RNG SCD03 SCD02 SCD01 SCD00 F                                                                                  |

| O_S_TRIP      | SCDT 60 🔽 OCDT 45 🔽 24                                                                                                                         | O_S_TRIP SCOT3 SCDT2 SCDT1 SCDT0 0CDT3 0CDT2 0CDT1 0CDT0 24                                                                                      |

| SCC_CFG       | SCCD 960 👽 SCCT -30 💌 F4                                                                                                                       | SCC_CFG SCC03 SCC02 SCC01 SCC00 SCCT3 SCCT2 SCCT1 SCCT0 F4                                                                                       |

| CELL_BAL      | CB_EN 3 V CBT 8 V CBV 3.6 V F3                                                                                                                 | CELL_BAL CB_ENI CB_ENO CBTI CBTO CBV3 CBV2 CBV1 CBV0 F3                                                                                          |

|               | Legend<br>Logic<br>Logic                                                                                                                       | 0 Logic 0                                                                                                                                        |

Figure 4. GUI With Communication Established

Other than the menu selections, the software window has three sections. In the bottom border is a status section. The middle section is a register section. The top section has a selection for the device used and a status area useful for checking the device status when a fault is detected. Details are described in following sections.

### 5.1 Menu commands

### 5.1.1 Help Menu

The Help  $\rightarrow$  About menu selection displays version information about the program.

#### 5.1.2 Setup Menu

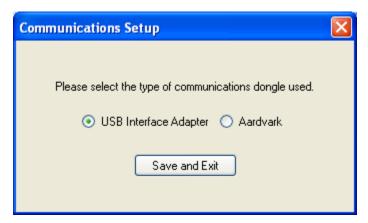

The Setup  $\rightarrow$  Communication selection allows selection of either the USB Interface Adapter or the Aardvark. Default is the TI USB Interface Adapter, and this window is not needed. Selecting the Save and Exit button checks for the adapter. If the selected adapter is not present, a communications error window appears. Selecting OK in the window returns to the Communication Selection window. To exit without having the selected adapter connected, use the close window tool (red X button). Selection of an adapter other than the two shown is not supported.

**Figure 5. Communication Selection Window**

#### 5.1.3 Commands Menu

Most commands are only available after communication is established with the device. Figure 6 shows the command window when communication is not yet established.

| 🗯 Texas Instruments - bq77908 : bq77910 E |     |                                  |            |         |        |  |  |

|-------------------------------------------|-----|----------------------------------|------------|---------|--------|--|--|

| File                                      | Con | nmands                           | Setup      | Help    |        |  |  |

| ~Dev                                      |     | Find Ta                          | rget       |         |        |  |  |

| юь                                        |     | Read V                           | olatile Re | gisters | Ctrl+R |  |  |

|                                           |     | Read EEPROM Registers Ctrl+E     |            |         |        |  |  |

|                                           |     | Read All Registers Ctrl+A        |            |         |        |  |  |

|                                           |     | Copy EEPROM to Volatile Ctrl+C   |            |         |        |  |  |

|                                           |     | Verify Volatile Registers Ctrl+V |            |         |        |  |  |

| SY                                        |     | Program                          | n EEPROI   | 4       | Ctrl+P |  |  |

Figure 6. Commands Without Communication Established

The communication status in the bottom border of the window shows the adapter in use and the device communication status. If the software is started and the adapter is not found, a Communication Error message box is displayed. Selecting OK on the box displays the main window. If the device is not recognized, a Device Not Found box is displayed. Selecting OK to this box also displays the main window. The communication fault is displayed in the status area of the window. Communication can be re-tried by selecting the menu command Commands  $\rightarrow$  Find Target. Once communication is established with the part, the Find Target command is no longer available.

The other commands relate to the register section. The register section is shown in Figure 7. Two sets of registers are displayed: the right section can display the EEPROM settings, and the left side can display

#### Software Operation

www.ti.com

the volatile registers waiting to be programmed in the EEPROM. When the software is first started, all values are shown as zero. When the software is started and connects to the device, it will copy the EEPROM values to the volatile registers. The software does not know if power has been removed from the part and will continue to display the values, even though the device may have different values. Registers should be read before use.

|            | Volatile Registers                                | EEPROM View                                                 |              |

|------------|---------------------------------------------------|-------------------------------------------------------------|--------------|

| SYS_CFG    | CNF2 CNF1 CNF0 CHGTMPDI TMPEN OT_REC SHTDIS SOR C | SYS_CFG CNF2 CNF1 CNF0 CHGTMPDI TMPEN 0T_REC SHTDIS 50      | R C          |

| OV_CFG1    | 0VT 4.225 💙 39                                    | OV_CFG1 RSVD RSVD OVTS OVT4 OVT3 OVT2 OVT1 OVT              | <b>10</b> 39 |

| OV_CFG2    | OV_TS_CTRL OVH 100 VD 1.00 VD 42                  | OV_CFG2 OVTSCTRL 0VH2 OVH1 0VH0 RSVD 0VD2 0VD1 0VD          | 42           |

| UV_CFG1    | UV_HYST_INH UVT 2.6 🗸 C                           | UV_CFG1 UVHYSTIDN RSVD RSVD RSVD UVT3 UVT2 UVT1 UVT         | ro C         |

| UV_CFG2    | VUV_REC VUV_REC_DLY UVH 0.4 VUVD 1.0 VC           | UV_CFG2 UV_REC URD UVH1 UVHO RSVD UVD2 UVD1 UVD             | 0 C1         |

| OCD_DELAY  | 0CDD 500 💙 10                                     | OCD_DELAY RSVD RSVD RSVD 0CDD4 0CDD3 0CDD2 0CDD1 0CD        | 10           |

| SCD_DELAY  | SCDD_RNG SCDD 960                                 | SCD_DELAY RSVD RSVD ISNS_RNG SCDD_RNG SCDD3 SCDD2 SCDD1 SCD | 00 F         |

| O_S_TRIP   | SCDT 40 🗸 OCDT 25 🗸 0                             | O_S_TRIP SCDT3 SCDT2 SCDT1 SCDT0 0CDT3 0CDT2 0CDT1 0CD      | σ            |

| SCC_CFG    | SCCD 960 💙 SCCT -10 💙 FO                          | SCC_CFG SCCD3 SCCD2 SCCD1 SCCD0 SCCT3 SCCT2 SCCT1 SCC       | TO FO        |

| CELL_BAL C | CB_EN 3 CBT 8 CBV 3.6 F3                          | CELL_BAL C8_EN1 C8_EN0 C8T1 C8T0 C8V3 C8V2 C8V1 C8V         | /0 F3        |

|            |                                                   |                                                             |              |

#### Figure 7. Register Section

The Read Volatile Registers command reads the values from the registers in the part and displays them in the GUI window. When a part is first powered, these are typically zero. When connecting to a powered part, they likely contain residual values.

The Read EEPROM Registers command reads the EEPROM values from the device and displays them in the EEPROM registers section of the window for viewing. This is a viewing operation, and data manipulation is not allowed in the displayed EEPROM data.

The Read All Registers command reads both the volatile and EEPROM registers from the device and displays the values.

The Copy EEPROM to Volatile command copies the EEPROM register values to the corresponding volatile registers and displays both in the GUI. This is a good starting point for making incremental changes to the device settings.

The Verify Volatile Registers command checks whether the volatile registers match the contents of the device. This can be useful as a check before programming the EEPROM.

The Program EEPROM command writes the volatile register values

#### 5.1.4 File Menu

The Load Registers from File command reads a properly formatted file and fills the volatile register section with the values. This is useful for loading a device with a saved configuration. A windows navigation tool allows selection of the file. Whereas files can be edited, it is recommended to load files saved by the software, and if any editing is performed on the file, check all values before programming the device.

The Save Registers to File command creates a file. A windows navigation tool allows selection of the location and file name. Files have the .cfg extension.

The Exit command exits the program.

#### 5.2 Working With Register Values

When the software initially connects to a device it will copy that device's EEPROM to its volatile registers and display those results. Since the device does not know if power has been lost to the device, the register display may be stale. If the device has been changed or power cycled to the part, the registers should always be read before making changes. If a file is loaded with values matching the displayed values, the software will not know the data is different from the part. Reading the registers or copying EEPROM values to the volatile registers is recommended before any change.

EEPROM values are displayed but are not directly editable in either the device or the GUI. Changes are made to a volatile register set by changing the volatile register value which is written to the volatile register in the device and later written to the device EEPROM by the programming process. Changes in the volatile registers do not affect operation of the device until written into the EEPROM.

The software does not know the difference between the bq77908 and bq77910. The user must select the device connected with the selection buttons in the top section of the window. Selecting the bq77908 will add some limit checking for the SYS\_CFG CNF field to avoid programming an invalid configuration into the device. Attempting to program an invalid configuration with the bq77908 selected will display an error box and will not program the part. The device selection also changes the device name in saved configuration files.

Values in the Volatile Registers section can be typically be changed in three ways:

- Loading a register file

- Changing a check box or drop-down selection

- Entering a data value in the box corresponding to the register name

The SYS\_CFG register bits are displayed as selection boxes; these are green for a value 0 and orange for a value 1.

The following steps describe changing a device EEPROM setting on the EVM using the GUI with a connected adapter:

- 1. Power the EVM (device) with the battery supply, and wake it up with charger detection.

- 2. Maintain a logic high on the CHGCTL pin of the EVM (CHGST device pin).

- 3. Copy the EEPROM values to the volatile registers with the Copy EEPROM to Volatile command.

- 4. Edit the values in the Volatile Registers section as desired.

- 5. Provide a 14 V ±0.5 V at approximately 0.1-A programming voltage at the EVM J2 connector.

- 6. Select the Program EEPROM command.

- 7. After a short delay, a programming complete status window appears. Select OK in this window.

- 8. Disconnect the programming voltage from the EVM J2 connector.

Programming the EEPROM from a file uses a similar sequence. This can be useful in evaluation when replacing a device or duplicating a design on a small number of boards. The following steps describe programming a device EEPROM on the EVM from a saved configuration file using the GUI with a connected adapter:

- 1. Power the EVM (device), and wake it up with charger detection.

- 2. Maintain a logic high on the CHGCTL pin of the EVM (CHGST device pin).

- 3. Copy the EEPROM values to the volatile registers with the Copy EEPROM to Volatile command if the software is not restarted for each device.

- 4. Select the File  $\rightarrow$  Load Register File command, navigate to, and open the desired file.

- 5. Provide a 14 V ±0.5 V at approximately 0.1-A programming voltage at the EVM J2 connector.

- 6. Select the Program EEPROM command.

- 7. After a short delay, a programming complete status window appears. Select OK in this window.

- 8. Disconnect the programming voltage from the EVM J2 connector.

After programming, it may be necessary to clear fault status because programming requires communication with the device and that requires setting ZEDE high. ZEDE high may make the part respond to noise. SCC is typically the lowest value threshold in the device and is common after programming or other communication with the part, depending on the device settings and operating environment.

#### CAUTION

Although the software may be useful for producing a small number of boards, it is not intended as a production programming tool. Accidental manipulation of the registers when the file is loaded and when the programming command is sent is not prohibited.

During programming, the software checks that the device volatile registers match the values shown. If they do not match, an error message is displayed. Continuing with programming when the values do not match will unexpectedly alter the configuration of the device. If the error is displayed, it is recommended to read the volatile registers to examine the contents, correct any communication error, and re-start the software or device as needed for proper programming.

#### 5.3 Status Section

The status section of the GUI is shown in Figure 8. This section allows the user to display internal status registers of the devices fault condition. This data is not part of normal operation of the device and is not shown in the data sheet. Accessing the data is disruptive to the device; however, it can be beneficial in evaluation.

| _Polling           | Fault Status-                                         |                             |                                                     |                                  |                                  |

|--------------------|-------------------------------------------------------|-----------------------------|-----------------------------------------------------|----------------------------------|----------------------------------|

| Enable 1 👽 Seconds | <ul> <li>Parity</li> <li>Short Circuit Dsg</li> </ul> | Open Cell Short Circuit Chg | <ul> <li>Over Temp</li> <li>Over Voltage</li> </ul> | Under Voltage Shorted Thermistor | Over Current Dsg Open Thermistor |

#### Figure 8. Status Section

The status is read by selecting the Polling Enable button on the left side of the status section. This periodically sets ZEDE high to the device, reads the status registers, and returns ZEDE low. The polling period can be selected with the drop-down box next to the button. The button function and label change to Disable. The button label indicates the action of the next button actuation.

A consequence of polling is that a pending fault delay is terminated by the status read. Polling is typically independent of any system change, and a fault may be recorded as soon as the poll occurs. This may lead to unexpected results in evaluation. The following text describes a couple examples which can occur:

- The user has selected a 2-second undervoltage delay and wants to observe the timing on a scope. The user leaves polling active and decreases the device voltage. The poll occurs just after the voltage drops, and the zero delay causes the fault to be registered. The FETs turn off and the user thinks the delay setting is not working. This situation occurred because the poll set ZEDE high and terminated the undervoltage delay.

- The user is polling status to watch faults. CHGST is tied high to prevent the part from shutting down due to undervoltage. The user begins switching currents and is surprised when a SCC fault occurs. Observing the sense resistor voltage, the user does not see a charge current. This situation occurred because the poll set zero delay and eliminated noise filtering on the current. The SCCT is typically a low and thus most sensitive to any noise; having CHGST high prevents recovery from the fault.

The values display in several colors. See Table 8.

#### **Table 8. Status Section Indicator Colors**

| Color                  | Meaning                                                                                   |

|------------------------|-------------------------------------------------------------------------------------------|

| Gray                   | Status is not read                                                                        |

| Bright green           | Device is polling and status is normal with connected device, or adapter is not connected |

| Bright red             | Device is polling and status is fault                                                     |

| Dark green or dark red | Device is not polling and value is residual from last poll                                |

Software Operation

Figure 9 shows a typical status display polling with undervoltage.

### Figure 9. Polling Status With Undervoltage Condition

Another use of the status section is to determine the reason the part has turned off the FETs. For example, if during test the EVM has turned off the FETs but the VREG is still on, the interface might be connected and the status polled to see what fault the device identifies.

### 5.4 Basic Operation With Software

The following steps are suggested for exercising more of the device features using the EVM in its default 8-cell configuration and EEPROM settings. The board is connected as shown in Figure 3. Remember that timing as described in Section 5.3 will be incorrect.

- 1. Install the software.

- 2. Connect the USB Interface Adapter to the computer with the USB cable.

- 3. Remove the screw terminal blocks from J4 and J5, and save for later use. Connect the cell simulator board to the bq77908 main board J4 and J5. Support the under side of the EVM board as the connectors are pressed together.

### CAUTION

Do not connect or remove the resistive cell simulator from the board with power applied. The resistor pulldown or pullup from intermittent connections overstresses the device inputs.

- 4. Connect the 10-pin ribbon cable from the USB Interface Adapter to the EVM J3.

- 5. Connect an isolated power supply negative to BATT- and positive to PACK+. Adjust the voltage to approximately 29 V.

- 6. Connect an approximate 15-kΩ resistor from the power supply positive to the CHGCTL terminal. This wakes up the part; leave the resistor connected.

- 7. Start the software.

- 8. Connect a disabled load to the pack terminals.

- 9. Select the Polling Enable button in the software window.

- 10. Observe that the status values are bright green.

- 11. Set a current on the load within the capability of the supply and board.

- 12. Decrease the power supply voltage to approximately 20 V. Observe that using the load current stops, and the UV status indicator turns red.

- 13. Increase the supply voltage to approximately 29 V. Observe that the UV indicator turns green.

- 14. Load current may not resume until the load is disabled or disconnected.

- 15. Increase the supply voltage to approximately 34 V. Observe that the OV status indicator turns red.

- 16. Decrease the power supply voltage to approximately 29 V. Observe that the OV indicator turns green.

- 17. Disable polling.

- 18. Disable the load

- 19. Set the supply to 0 V, and turn off equipment.

# 5.5 Operation With Other Interfaces or Hosts

The bq77910 GUI software does not support other interfaces.

#### Related Documents From Texas Instruments

www.ti.com

Communication with the bq77908 from other hosts must be straightforward. See to the data sheet for timing and interface details. On the EVM, zero delay mode can be set to allow communication using a 0.1-inch shunt (not provided) at J6 pins 1 to 2, or a signal at ZD on J3. To program, the onboard programming voltage switch can be used by controlling the PGM signal on J3. Signals must be 3.3-V CMOS levels.

### 6 Related Documents From Texas Instruments

To obtain a copy of any of the following TI document, call the Texas Instruments Literature Response Center at (800) 477-8924 or the Product Information Center (PIC) at (972) 644-5580. When ordering, identify this document by its title and literature number. Updated documents can also be obtained through the TI Web site at www.ti.com

#### Document

bq77908 data sheet

Literature Number SLUSAI5

# 7 bq77908EVM Circuit Description and Configuration

This section describes the circuit on the bq77908 circuit module and how to configure it for changes the user may want to make to the board for specific evaluations. In many cases, an EVM schematic is used as a starting point for a circuit design. This can result in unnecessary extra components on the product design that take up space and add cost. Refer to the schematic in Section 8 while reading the following descriptions. Note that the schematic has two pages: the first shows the main functions, and the second page shows primarily cell count configuration and protection components.

### 7.1 Battery Voltage Clamp

The TVS diode D9 provides a clamp for transients on the pack. A common transient is due to system inductances and sudden load shutoff. The breakdown voltage of D9 must be set near or below the 5-V per cell absolute maximum of the device. As a transient pushes the voltage up the I-V curve, a substantial device here reduces the demands on other clamping components in the system, which may be needed to protect the device. Alternatives to D9 may be to control the system inductance and current switching rate, use capacitance to absorb transients, or other transient protectors such as MOVs where appropriate.

### 7.2 Device Power

The device is powered through the BAT pin. C12 is a bypass capacitor near the IC; the footprint is large in order to make it easy to mount larger capacitors, in the event that this is desired in evaluation. R5 and J1 provide a way to measure current to the device during evaluation and are not needed in an application. D2 provides power from the battery to the IC and prevents the IC power from being pulled down when the battery voltage dips suddenly due to a heavy load on the battery. C2 provides an operating reservoir for device current during battery voltage droop. D1 limits the voltage to the BAT pin preventing overvoltage from rectification of transients by D2.

Power is provided through R4. The 200- $\Omega$  resistor provides for a voltage drop when an overvoltage charger pulls down BAT through D8. For lower cell counts, this resistor may be a smaller value. R3 is a 0- $\Omega$  connection to the high-current battery positive connection BATT+ which is shared with the PACK+. This jumper is provided in case the user wants to power the part from the current monitor line instead.

# 7.3 Cell Monitor Inputs and Configuration

The cell monitor inputs are provided through an RC filter network. The series resistors  $R_{VCX}$  connect the cells to the device to allow voltage measurement and limit the balancing current. Balancing current is approximately the cell voltage divided by twice the resistor. The EVM is circuit-designed to use the internal balancing path at near the maximum current. The 47- $\Omega$  R<sub>VCX</sub> value on the EVM is nominally within 10% of the 50- $\Omega$  minimum recommended in the data sheet and prevents exceeding the absolute maximum balancing current up to 4.3 V per cell. The input capacitance is typically connected between cell inputs, except the capacitances at VC8 and VC9 are connected to ground to avoid pushing the inputs below ground during transients. The capacitance must not be increased beyond the 1 µF shown because the

capacitors are discharged into the device during balancing. The filter effect both reduces cell transients to the device inputs and slows voltage recovery after balancing. The resulting time constant is complicated due to the multiple components but relatively short due to the small resistors used for high balancing current. Due to the cell input voltage measurement after balancing, the time constant ( $R_{VCX}$ ) must not be made too large.

Note that two limits are implied by the absolute maximum cell-to-cell differential rating of the part. One is the applied differential voltage, or 5 V on any cell regardless of the other inputs. Note also that this is an applied voltage, not the voltage induced by the part during balancing, which may be higher. The second voltage limit is the voltage to ground the cumulative voltage from summing the individual limits. Because the input filter time constant is small, clamping the inputs to safe values may be required. While a Zener or TVS diode per cell may be a suitable way to protect the device in some applications, the EVM provides patterns D14 to D18 to clamp the inputs for cells 8 to 4 to ground. The top cell input is clamped (VC1 with D14 on the EVM), and cell 4's input, VC7, is clamped with D18 on the EVM because this input showed more sensitivity than others in testing. For nominal transients, these clamps along with the capacitors between cells hold the inputs to safe values; however, different or additional clamping may be required in evaluation or the target application.

The EVM has resistor jumper positions and is populated to connect to the cells with N+1 wires where N is the number of cells. R42 connects the high-current BATT- connection to the lowest cell monitor point. Similarly, R57 connects cell 8 input to the high-current path through R3. Additional resistor patterns R53 to R58 allow the same connections when the board is configured for other series cell counts. The board may be configured to monitor the cell voltages directly at the cells (N+3 wires) by removing R42 and R59 or the equivalent.

When configuring the part for fewer than 8 cells, the unused inputs must not be left floating and must be connected to avoid exceeding absolute maximums. The EVM provides patterns to allow flexible connections. The unused pin group may be connected together on the EVM by shorting the capacitors between them or shorting the appropriate resistor jumper positions R62 to R64. The unused pin group then needs to be connected to a safe level, either to the top cell through one of the unused cell  $R_{VCX}$  patterns or to the highest used VCx pin using the appropriate R63 to R65. When configuring for fewer than 8 cells and using the cell simulator, be sure to remove components to avoid parallel paths. Due to the flexibility allowed by the EVM for configuration, it is recommended evaluators study the schematic before modifying the board to achieve their desired configuration. Table 9 shows possible configurations for different cell counts assuming use of the cell simulator, retaining the N+1 wiring plan, and adjusting the transient protection. The board operates at a lower cell count without the transient protection adjustment, but users must be sure they provide adequate protection for the IC in the evaluation and system design to prevent damage. The table describes a change from the 8-cell default to one of the other configurations. The users must check configurations if multiple changes are made. D14 is shown removed in the table for less than 8 cells to avoid any possible leakage current or unexpected clamp during evaluation.

| Cell Count/<br>Reference<br>Designator | 8 Cells (Default) | 7 Cells   | 6 Cells   | 5 Cells   | 4 Cells   |

|----------------------------------------|-------------------|-----------|-----------|-----------|-----------|

| C6                                     | Installed         | Remove    | Installed | Installed | Installed |

| C7                                     | Installed         | Installed | Remove    | Installed | Installed |

| C8                                     | Installed         | Installed | Installed | Remove    | Installed |

| C9                                     | Installed         | Installed | Installed | Installed | Remove    |

| D1                                     | Installed         | < 35 V    | < 30 V    | < 25 V    | < 20 V    |

| D9                                     | Installed         | < 35 V    | < 30 V    | < 25 V    | < 20 V    |

| D14                                    | Installed         | Remove    | Remove    | Remove    | Remove    |

| D15                                    | -                 | < 35 V    | -         | -         | -         |

| D16                                    | -                 | -         | < 30 V    | -         | -         |

| D17                                    | -                 | -         | -         | < 25 V    | -         |

| D18                                    | Installed         | Installed | Installed | Installed | Installed |

| R18                                    | Installed         | Remove    | Remove    | Remove    | Remove    |

| R19                                    | Installed         | Installed | Remove    | Remove    | Remove    |

| Table 9. C | ell Count | Component C | Configuration |

|------------|-----------|-------------|---------------|

|------------|-----------|-------------|---------------|

| Cell Count/<br>Reference<br>Designator | 8 Cells (Default) | 7 Cells   | 6 Cells   | 5 Cells   | 4 Cells |

|----------------------------------------|-------------------|-----------|-----------|-----------|---------|

| R20                                    | Installed         | Installed | Installed | Remove    | Remove  |

| R21                                    | Installed         | Installed | Installed | Installed | Remove  |

| R53                                    | -                 | -         | -         | -         | 0 Ω     |

| R54                                    | -                 | -         | -         | 0 Ω       | -       |

| R55                                    | -                 | -         | 0 Ω       | -         | -       |

| R56                                    | -                 | 0 Ω       | -         | -         | -       |

| R57                                    | Installed         | Remove    | Remove    | Remove    | Remove  |

| R62                                    | -                 | 100 Ω     | 0 Ω       | 0 Ω       | 0 Ω     |

| R63                                    | -                 | -         | 100 Ω     | 0 Ω       | 0 Ω     |

| R64                                    | -                 | -         | -         | 100 Ω     | 0 Ω     |

| R65                                    | -                 | -         | -         | -         | 100 Ω   |

| Table 9. Cell Count Component Configuration (continued) |

|---------------------------------------------------------|

|---------------------------------------------------------|

The cell count programmed in the EEPROM must match the physical connection for proper operation. If the device is programmed for more than the connected cells, the unused cells are still checked by the device and show undervoltage or open-cell faults. If the device is programmed for fewer than the connected cells, the upper cells are ignored and faults on these cells are not checked. Also be aware that the voltage applied to the part can exceed the absolute maximum or show undervoltage when used with the resistor simulator.

# WARNING

When the device is configured for fewer than the connected cells, the device does not monitor the upper cells and does not protect against faults on those unmonitored cells.

### 7.4 Ground Connection

The IC VSS (ground) reference on the bq77908EVM-001 circuit module is connected to the BATT– at the sense resistor. Note the range of the inputs when considering moving the ground location in an application design. The ground connection must be made at one location on the high-current path to avoid differential voltages on the board ground due to high currents.

### 7.5 Current Sense Connections

R50 and R52 in parallel make the current sense resistor. Two resistors allow for lower heat dissipation per component at a given current and allow flexibility in evaluation. R43 and R44 isolate the sense input pins from the current path transients; C20 and C25 provide filtering. Be aware that C20 and C25 add a time delay to the system current response depending on where sense resistor voltage falls in relation to the threshold voltage. A mismatch in C20 and C25 can convert a common-mode signal to a differential signal at the device pins; the C22 pattern is available if a differential filter is desired.

### 7.6 Filter Capacitors

The regulator filter capacitor C17 value of 4.7  $\mu$ F exceeds the minimum data sheet value of 1  $\mu$ F. The 1- $\mu$ F DCAP and CCAP filter capacitors C21 and C26 are the data sheet recommended typical values

#### bq77908EVM Circuit Description and Configuration

### 7.7 FET Circuits

The circuit board has five TO-220 power FET patterns to allow flexibility in evaluation. By default, the board is populated for parallel FET operation. The Q3 discharge FET is mounted to a heatsink expecting high-discharge currents. Users must monitor temperature in their evaluation environment and provide additional cooling if required. Q7 is the parallel charge FET. Anticipating a low-charge current of up to a couple amperes, Q7 does not have a heatsink. Users must measure the device temperature in their evaluation environment and provide heatsinking and cooling, if required.

The Q4 pattern allows an FET to be installed instead of Q7 to provide series FET configuration. In this case, the pack negative is the CHG- terminal. HS2 pattern is provided for Q4. If configured for series FETs, it is recommended to insulate DSG- to avoid erroneous connections. Patterns Q5 ane Q6 are in parallel with Q3 and Q4 to provide for optional patterns, to allow parallel FET connection, to provide for a large heatsink to be mounted to the FETs off the board edge if desired, or to provide connection points for additional circuitry. When using series FETs the CPCKN can rise above VSS when the FETs are shut off or the device is shut down. This can result in an increased supply current. Look for TI application reports related to the device for alternate series FET configurations on the Texas Instruments Web site..

C34 and C35 provide an ESD path and high-frequency bypass during switching of the discharge FET. Two capacitors in series are used so that if one is shorted, the other still blocks dc signals. C36 and C37 provide a similar function for the charge FET or across both FETs in series configuration.