### **New Product**

# PSM Buck Converter with Dynamic Adjustable Output and Bypass Capability

#### **FEATURES**

- 2.7-V to 6-V Input Voltage Range

- Dynamic Adjustable 1.5-V to 3.6-V Output.

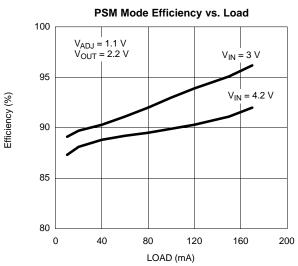

- Power Conversion Efficiency of 95% at 170-mA Load

- Selectable Pulse Skipping Modulation (PSM) or Bypass Mode (BP) Operation

- Bypass for up to 800-mA Load

- Integrated MOSFET with Low External Part Count

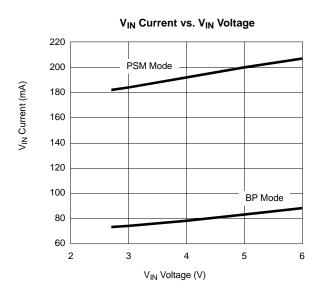

- Low Quiescent Current–110 μA/250 μA (BP/PSM)

- Shutdown Current <1 μA</li>

- Integrated UVLO and POR

- Integrated Soft-Start

- Over Temperature Protection

- MSOP-10 Package

#### **APPLICATIONS**

- Cellular Phones, Cordless Phones

- Computer Point of Use, Notebook

- PDAs

- Battery Powered Devices

#### **DESCRIPTION**

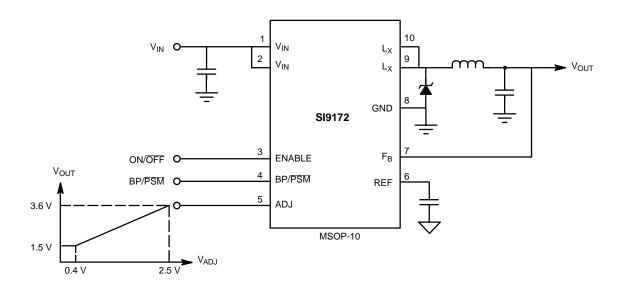

The Si9172 is a dual-mode power adjustable output converter. When it is set to PSM mode, the Si9172 operates as a pulse-skipping-modulation controlled step-down (buck) converter with a dynamically adjustable output of 1.5 V to 3.6 V. It has an integrated MOSFET, capable of supplying a minimum 170-mA load current with a 1.5- $\mu$ H inductor. The output voltage is adjusted by the analog dc signal at the ADJ pin. The typical conversion efficiency is above 90%. A logic high at the BP/PSM pin puts the Si9172 in bypass mode. The main PMOS buck switch is forced to turn on at 100% duty cycle, overriding the FB signal. The voltage differential between input and

output is the resistive voltage drop on the internal PMOS and the inductor. The Si9172 guarantees to deliver 800-mA load in bypass mode with a typical 95% efficiency.

The Si9172 is available in MSOP-10 package. In order to satisfy the stringent ambient temperature requirements, the Si9172 is rated to handle the industrial temperature range of  $-25^{\circ}$ C to  $85^{\circ}$ C.

#### TYPICAL APPLICATION CIRCUIT

# **Vishay Siliconix**

# **New Product**

## ABSOLUTE MAXIMUM RATINGS $(T_A = 25^{\circ}C)$

| V <sub>IN</sub>           | Power Dissipation (Package) <sup>a</sup> 10-Pin MSOP (Q Suffix) <sup>b</sup>                                                         |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| ADJ                       | Thermal Impedance ( $\Theta_{JA}$ )                                                                                                  |

| Continuous Output Current | Notes <ul> <li>a. Device mounted with all leads soldered or welded to PC board.</li> <li>b. Derate 6.6 mW/ °C above 25°C.</li> </ul> |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **RECOMMENDED OPERATING RANGE**

| V <sub>IN</sub>                       | Inductor                |

|---------------------------------------|-------------------------|

| BP/PSM, ENABLE 0 V to V <sub>IN</sub> | PSM Load                |

| REF Capacitor                         | Bypass Load 0 to 800 mA |

| Output Capacitor10 μF                 |                         |

| SPECIFICATIONS                      |                      |                                                                                      |                  |       |                  |      |

|-------------------------------------|----------------------|--------------------------------------------------------------------------------------|------------------|-------|------------------|------|

| Parameter                           | Symbol               | Test Conditions Unless Specified  -25°C to 85°C  2.7 $\lor \le \lor_{IN} \le 6 \lor$ | Limits           |       |                  |      |

|                                     |                      |                                                                                      | Min <sup>a</sup> | Typb  | Max <sup>a</sup> | Unit |

| Output                              |                      |                                                                                      |                  |       |                  |      |

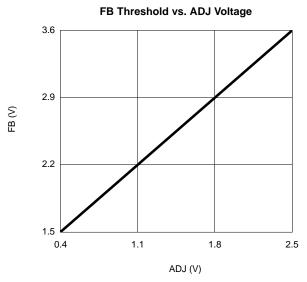

| FB Threshold                        | V                    | ADJ = 0.4 V                                                                          | 1.440            | 1.5   | 1.560            | V    |

| FB Threshold                        | $V_{FB}$             | $ADJ = 2.5 \text{ V}, V_{IN} \ge V_{FB}$                                             | 3.492            | 3.6   | 3.708            | 1 °  |

| Reference                           |                      |                                                                                      |                  |       |                  |      |

| Outsid Vallage                      |                      | I <sub>REF</sub> = 0                                                                 | 1.175            | 1.215 | 1.255            |      |

| Output Voltage                      | $V_{REF}$            | $I_{REF} = 0, T_A = 25^{\circ}C$                                                     | 1.195            | 1.215 | 1.235            | V    |

| Power Supply Rejection <sup>c</sup> | PSRR                 |                                                                                      |                  | 60    |                  | dB   |

| UVLO                                |                      |                                                                                      |                  | -     |                  |      |

| Under Voltage Lockout (turn-on)     | $V_{UVLD}$           |                                                                                      | 2.3              | 2.4   | 2.5              | .,   |

| Hysteresis                          | UVLD <sub>HYST</sub> |                                                                                      |                  | 0.1   |                  | V    |

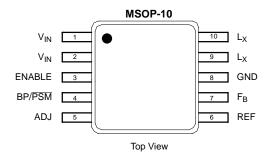

| Start-Up                            |                      |                                                                                      | •                | •     | •                |      |

| Start-Up Delay Time                 | t <sub>DELAY</sub>   |                                                                                      |                  | 3     |                  | ms   |

| Soft Start Time <sup>c</sup>        | t <sub>ss</sub>      |                                                                                      |                  | 100   |                  | μS   |

| ENABLE, BP/PSM                      |                      |                                                                                      |                  | •     | •                |      |

| Logic High                          | $V_{IH}$             |                                                                                      | 1.5              |       |                  |      |

| Logic Low                           | $V_{IL}$             |                                                                                      |                  |       | 0.4              | V    |

| Output Capability/MOSFE             | Т                    |                                                                                      | -                | -     | -                |      |

| Maximum Bypass Output Current       |                      |                                                                                      | 800              |       |                  |      |

| Maximum PSM Output Current          | l <sub>OUT</sub>     | L = 1.5 μH                                                                           | 170              |       |                  | - mA |

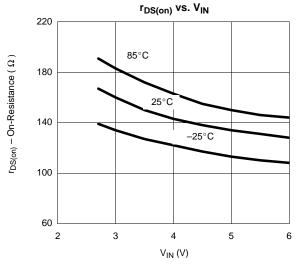

| MOSFET On-resistance                | r <sub>DS(on)</sub>  | $V_{IN} \ge 3.3 \text{ V}$                                                           |                  | 150   | 300              | mΩ   |

| Supply Current                      |                      |                                                                                      | -                | •     | -                |      |

| BP Mode                             |                      | V <sub>IN</sub> = 3.3 V                                                              |                  | 75    | 110              | μΑ   |

| PSM Mode <sup>d</sup>               | I <sub>IN</sub>      |                                                                                      |                  | 190   | 250              |      |

| Shutdown Mode                       | 1                    | $V_{IN} = 3.3 \text{ V}, \text{ENABLE} = 0 \text{ V}$                                |                  |       | 1                |      |

| Thermal Shutdown                    |                      |                                                                                      | -                | •     | -                |      |

| Threshold                           | T <sub>S/D</sub>     | Up-Rising                                                                            |                  | 165   |                  |      |

| Hysteresis                          | T <sub>HYST</sub>    | V <sub>IN</sub> = 3.3 V                                                              |                  | 25    |                  | °C   |

# Notes

- The algebraic convention whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet. Typical values are for DESIGN AID ONLY, not guaranteed or subject to production testing.

Guaranteed by design and characterization, not subject to production testing.

For operation involving L<sub>X</sub> frequency faster than 1-Hz the supply current may be higher.

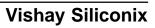

# **PIN CONFIGURATION**

| ORDERING INFORMATION |                   |               |  |

|----------------------|-------------------|---------------|--|

| Part Number          | Temperature Range | Package       |  |

| Si9172BH-TI          | –25°C to 85°C     | Tape and Reel |  |

| Eval Kit | Temperature Range | Board Type    |  |

|----------|-------------------|---------------|--|

| Si9172DB | –25°C to 85°C     | Surface Mount |  |

| PIN DES | PIN DESCRIPTION |                                                                                                        |  |

|---------|-----------------|--------------------------------------------------------------------------------------------------------|--|

| Pin No. | Name            | Function                                                                                               |  |

| 1, 2    | V <sub>IN</sub> | Input voltage source for buck converter, MOSFET driver, and IC control circuits.                       |  |

| 3       | ENABLE          | Logic high enables the converter. Logic low shuts down the IC and decreases current consumed to <1 μA. |  |

| 4       | BP/PSM          | Logic high = Bypass mode, logic low = PSM mode.                                                        |  |

| 5       | ADJ             | Analog voltage input to control output voltage                                                         |  |

| 6       | REF             | 1.215-V reference. Decouple with 0.1-μF capacitor.                                                     |  |

| 7       | F <sub>B</sub>  | Direct output voltage sense feedback                                                                   |  |

| 8       | GND             | IC ground                                                                                              |  |

| 9, 10   | L <sub>X</sub>  | Inductor connection node                                                                               |  |

**New Product**

# **TIMING WAVEFORMS**

FIGURE 1.

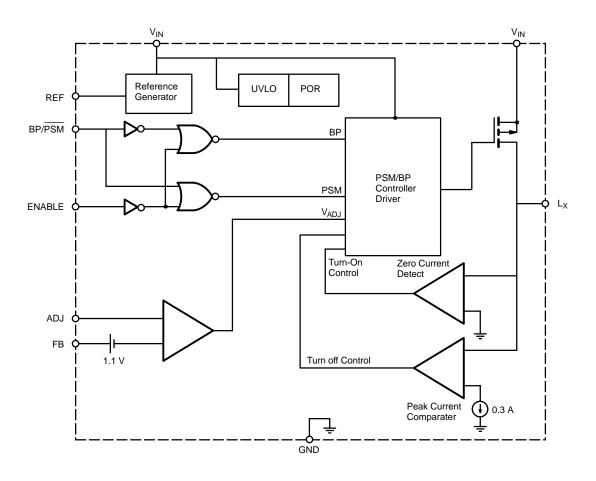

# **FUNCTIONAL BLOCK DIAGRAM**

#### **New Product**

#### **DETAIL OPERATIONAL DESCRIPTION**

#### Start-Up

The built-in UVLO circuit in the Si9172 prevents the internal MOSFET from turning on if the voltage on the V<sub>IN</sub> pin is less than 2.4 V. With typical UVLO hysteresis of 0.1 V, the controller is continuously powered ON until the V<sub>IN</sub> voltage drops below 2.3 V. This hysteresis prevents the converter from oscillating during the start-up phase and unintentionally locking up the system. Once the  $V_{\mbox{\scriptsize IN}}$  voltage exceeds the UVLO threshold, and with no other shutdown condition detected, an internal power-on-reset timer is activated. The circuitry, except the output driver, is turned on. After the POR time-out of about 3 ms, the soft-start begins. If pin 4 is in BP mode, the high side PMOS will turn on gradually in about 100 µs to avoid any inrush current. If pin 4 is in PSM mode, the converter will soft-start in PSM operation, forcing the output voltage to rise smoothly with minimum overshoot. The rise time is approximatly 100-us. In order to start-up properly in PSM mode, the load current has to be 170 mA or less.

#### **Pulse Skipping Mode**

The gate charge losses produced from the Miller capacitance of the MOSFET are the dominant power dissipation parameter during light load. Therefore, reduced gate switching frequency improves overall converter efficiency. This is exactly why the Si9172 is designed to operate in pulse-skipping mode rather than PWM mode. If the BP/PSM pin is connected to logic low level, the converter runs in pulse skipping modulation mode. In this mode, the internal MOSFET operates with a constant on-time. The on-time is reduced if necessary by the peak current detector circuitry. There is an enforced minimum off-time acting as the feedback comparator blanking time. If the output voltage drops below the desired level, the main switch is first turned on and then off. If the applied on-time did not deliver enough energy to keep the output at the desired voltage level, the controller will force another on and off sequence, until the desired voltage is accomplished. If the applied on-time forces the output to exceed the desired level, the converter stays off. The excess energy is delivered to the output slowly, forcing the converter to skip pulses as needed to maintain regulation. The on-time and off-time are set internally based on the inductor value (1.5 µH Typical) and maximum load current. With a 1.5-μH inductor, the Si9172 guarantees to deliver minimum of 170-mA load current. This current capability decreases as the inductance increases. In pulse-skipping mode, the switching frequency, f<sub>sw</sub>, varies with load current. When the load increases,  $\mathbf{f}_{\text{sw}}$  increases as well. The typical conversion efficiency in PSM mode is 90%. Efficiency is higher at high output voltage and decreases with the output voltage.

#### **Adjustable Output**

In PSM mode, the output voltage regulation point can be adjusted by an external analog voltage signal at the ADJ pin. When this voltage varies from 0.4 V to 2.5 V, the output voltage also increases linearly from 1.5 V to 3.6 V. When the programmed output voltage is higher than the input voltage

can support, the converter will be in drop out mode and the output voltage will be the input voltage minus the resistive drop of the MOSFET and inductor.

#### **BYPASS Mode**

The Si9172 can also operate in Bypass mode to handle heavy load current. In this mode the IC ignores the feedback signal at the FB pin, forcing the internal PMOS to turn on at 100% duty cycle. The input-output voltage differential is merely the resistive voltage drop on the MOSFET and the inductor. The Si9172 can bypass at least 800mA at 95% typical efficiency. Whenever the converter enters BP mode, regardless switching from PSM or starting up, the PMOS turns on gradually within 100  $\mu s$ .

#### Shutdown

The Si9172 is designed to conserve as much battery life as possible by decreasing current consumption of the IC during normal operation as well as the shutdown mode. With logic low level on the ENABLE pin, the current consumption of the IC is decreased to less than 1  $\mu$ A by shutting off most of the circuits. A logic high enables the controller and starts up as described in the "Start-Up" section above.

#### Reference

The reference voltage of the Si9172 is set to 1.215 V. It is internally connected to the non-inverting inputs of the error amplifier. A 0.1- $\mu$ F decoupling capacitor is required at the V<sub>REF</sub> pin.

#### **Power Switches**

The main MOSFET switch is integrated in the Si9172 for optimum performance and minimum overall converter size. The internal MOSFET is designed to minimize the gate charge loss as well as the conduction loss. The typical on-resistance of the PMOS is 150 m $\Omega$  with a minimum V<sub>IN</sub> pin voltage of 3.3 V.

An external Schottky diode is mandatory for PSM mode operation. It freewheels the inductor current after the main switch is turned off, which is typical in basic non-synchronous buck converter operation. It must be rated at 800 mA or higher, with low forward drop to minimize power loss. The diode has to be connected at PGND with the cathode connected to the  $L_{\rm X}$  pin.

#### **Over Temperature Protection**

The Si9172 includes an over temperature protection circuit to prevent thermal runaway in the MOSFET switch. If the temperature reaches  $165^{\circ}$ C, an internal soft-start capacitor is discharged, shutting down the output stage. The converter remains in the disabled mode until the temperature in the IC decreases below  $140^{\circ}$ C.

# **New Product**

# TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)

Vishay

# **Disclaimer**

All product specifications and data are subject to change without notice.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.

Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

Product names and markings noted herein may be trademarks of their respective owners.

Revision: 18-Jul-08

Document Number: 91000 www.vishay.com