# TMS470M Series Technical Reference Manual (TRM)

Literature Number: SPNU495A November 2010

www.ti.com

|              |         | Specification                                         |    |

|--------------|---------|-------------------------------------------------------|----|

| 1.1          |         | iew                                                   |    |

| 1.2          | Block   | Diagrams                                              |    |

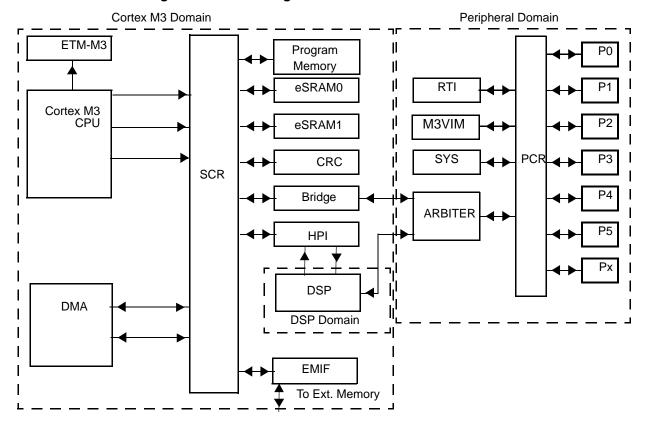

|              | 1.2.1   | TMS470M Series with ARM Cortex M3 CPU                 | 19 |

| 1.3          | Memoi   | ry Mapping                                            | 20 |

|              | 1.3.1   | Internal Program Memory                               | 20 |

|              | 1.3.2   | Endian System                                         | 26 |

| 1.4          | Systen  | m Module (SYS)                                        |    |

| 1.5          | •       | Definition                                            |    |

|              | 1.5.1   | Terminology                                           | 28 |

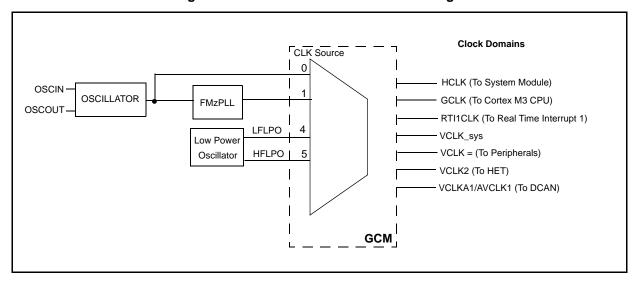

|              | 1.5.2   | Clock Domains                                         |    |

|              | 1.5.3   | Clock Domains and Low Power Mode                      |    |

|              | 1.5.4   | Primary/Secondary Clock Source Control                |    |

|              | 1.5.5   | Oscillator Fail Detection                             |    |

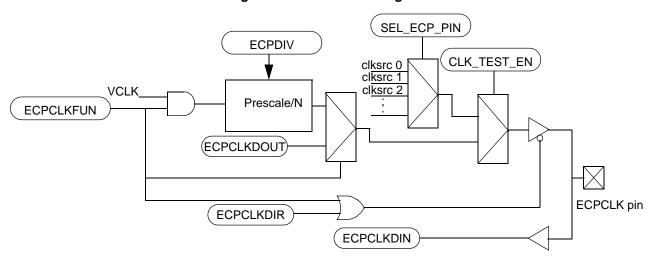

|              | 1.5.6   | ECP                                                   |    |

| 1.6          |         | \$                                                    |    |

| 1.7          |         | ry Ordering Model and Memory Protection               |    |

| 1.7          | 1.7.1   | Memory Attributes                                     |    |

|              | 1.7.1   | •                                                     |    |

|              |         | Memory Types                                          |    |

|              | 1.7.3   | Memory Ordering Model Variations                      |    |

| 1.8          | •       | m Abort Concept and Illegal Transactions              |    |

|              | 1.8.1   | Abort Types                                           |    |

|              | 1.8.2   | Accesses to Illegal Addresses                         |    |

|              | 1.8.3   | Illegal Accesses                                      |    |

|              | 1.8.4   | Illegal Transaction Detection and Response            |    |

| 1.9          | •       | m Interrupts                                          |    |

|              | 1.9.1   | System Software Interrupt (SSI)                       |    |

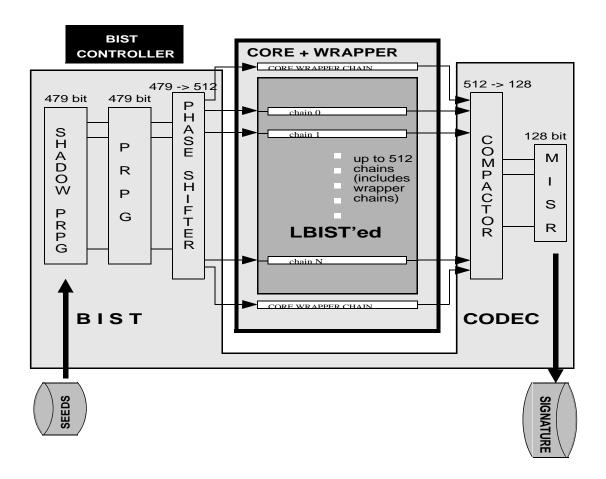

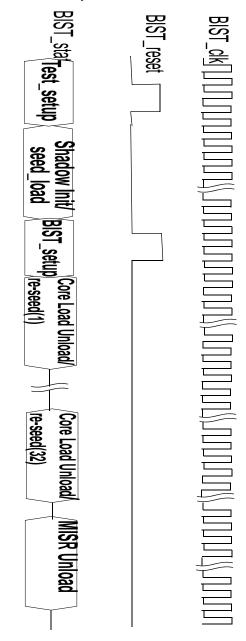

| 1.10         |         | ry Self Test                                          |    |

|              |         | MBIST                                                 |    |

|              | 1.10.2  | Memory BIST Implementation                            | 40 |

| 1.11         | Memoi   | ry Module Hardware Initialization                     | 41 |

|              | 1.11.1  | Memory Module Hardware Initialization Features        | 41 |

| l ow         | Power I | Mode Operation                                        | 43 |

| 2.1          |         | iew                                                   |    |

| 2.2          |         | ard Power Management Functionality                    |    |

|              | 2.2.1   | Overview                                              |    |

|              |         | Active Clock Modes                                    |    |

|              | 2.2.3   | Inactive Clock Modes                                  |    |

|              | 2.2.3   | External Wake Up Signals (Optional)                   |    |

|              | 2.2.4   | · · · · · · · · · · · · · · · · · · ·                 |    |

|              |         | Wakeup Registers                                      |    |

|              | 2.2.6   | ARM CPU Idle Mechanisms                               | 48 |

| Inter        | connec  | t                                                     | 51 |

| 3.1          | Interco | onnect Overview                                       | 52 |

| 3.2          | Switch  | ned Central Resource (SCR) or Bus Matrix Module (BMM) | 52 |

| 3.3          |         | ř                                                     |    |

|              | 3.3.1   | Arbitration Scheme                                    |    |

| 3.4          |         | eral Central Resource (PCR)                           |    |

| <b>-</b> 1-7 | 3.4.1   | PCR Operation                                         |    |

|              | 3.4.2   | Clock Management Interface                            |    |

|              | 3.4.3   | Low Power Mode Interface                              |    |

|              | J       |                                                       | -  |

| Con | trol Req | ijsters                                                           | 57  |

|-----|----------|-------------------------------------------------------------------|-----|

| 1.1 |          | m Peripherals Memory Mapping                                      |     |

| 1.2 |          | m Control Registers (SYS)                                         |     |

|     | 4.2.1    | SYS Pin Control Register 1 (SYSPC1)                               |     |

|     | 4.2.2    | SYS Pin Control Register 2 (SYSPC2)                               |     |

|     | 4.2.3    | SYS Pin Control Register 3 (SYSPC3)                               |     |

|     | 4.2.4    | SYS Pin Control Register 4 (SYSPC4)                               |     |

|     | 4.2.5    | SYS Pin Control Register 5 (SYSPC5)                               |     |

|     | 4.2.6    | SYS Pin Control Register 6 (SYSPC6)                               |     |

|     | 4.2.7    | SYS Pin Control Register 7 (SYSPC7)                               |     |

|     | 4.2.8    | SYS Pin Control Register 8 (SYSPC8)                               |     |

|     | 4.2.9    | SYS Pin Control Register 9 (SYSPC9)                               |     |

|     | 4.2.10   | SSW PLL BIST Control Register 1 (SSWPLL1)                         |     |

|     | 4.2.11   | SSW PLL BIST Control Register 2 (SSWPLL2)                         |     |

|     | 4.2.12   |                                                                   |     |

|     | 4.2.13   | Clock Source Disable Register (CSDIS)                             |     |

|     | 4.2.14   |                                                                   |     |

|     | 4.2.15   | Clock Source Disable Clear Register (CSDISCLR)                    |     |

|     |          | Clock Domain Disable Register (CDDIS)                             |     |

|     | 4.2.17   |                                                                   |     |

|     | 4.2.18   | Clock Domain Disable Clear Register (CDDISCLR)                    |     |

|     | 4.2.19   | GCLK, HCLK, VCLK, and VCLK2 Source Register (GHVSRC)              |     |

|     | 4.2.20   | Peripheral Asynchronous Clock Source Register (VCLKASRC)          |     |

|     | 4.2.21   | RTI Clock Source Register (RCLKSRC)                               |     |

|     | 4.2.22   | g ,                                                               |     |

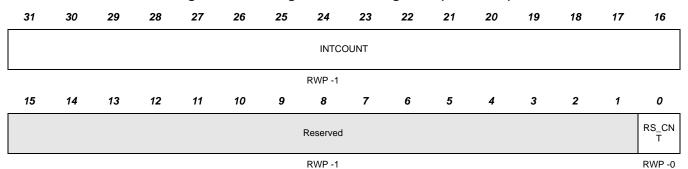

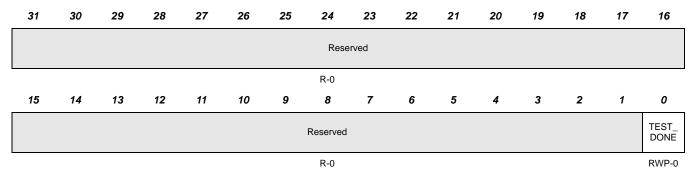

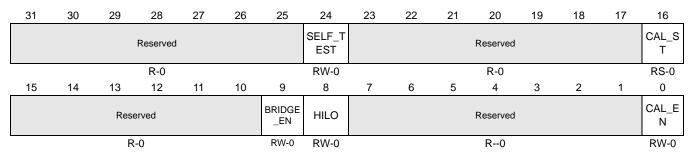

|     | 4.2.23   | Memory Self-Test Global Control Register (MSTGCR)                 |     |

|     | 4.2.24   | Memory Hardware Initialization Global Control Register (MINITGCR) |     |

|     | 4.2.25   | MBIST Controller/ Memory Initialization Enable Register (MSINENA) |     |

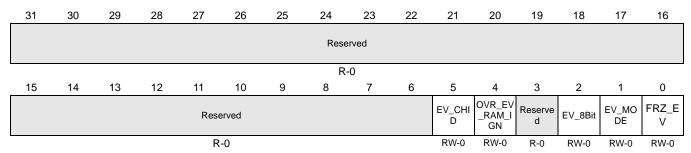

|     | 4.2.26   | Memory Self-Test Fail Status Register (MSTFAIL)                   |     |

|     | 4.2.27   | MSTC Global Status Register (MSTCGSTAT)                           |     |

|     | 4.2.28   | Memory Hardware Initialization Status Register (MINISTAT)         |     |

|     | 4.2.29   | PLL Control Register 1 (PLLCTL1)                                  |     |

|     | 4.2.30   | PLL Control Register 2 (PLLCTL2)                                  |     |

|     | 4.2.31   | Die Identification Register Lower Word (DIEIDL)                   |     |

|     | 4.2.32   | Die Identification Register Upper Word (DIEIDH).                  |     |

|     | 4.2.33   | Voltage Regulator Control Register (VRCTL)                        |     |

|     |          | LPO/Clock Monitor Control Register (LPOMONCTL)                    |     |

|     | 4.2.35   | Clock Test Register (CLKTEST).                                    |     |

|     | 4.2.36   | General Purpose Register 1(GPREG1)                                |     |

|     | 4.2.37   | BOOT ROM Select Register (BTRMSEL)                                |     |

|     | 4.2.38   | Imprecise Fault Status Register (IMPFASTS)                        |     |

|     | 4.2.39   | Imprecise Fault Address Register (IMPFTADD)                       |     |

|     | 4.2.40   | System Software Interrupt Request 1 Register (SSIR1)              |     |

|     | 4.2.41   | System Software Interrupt Request 2 Register (SSIR2)              |     |

|     | 4.2.42   | System Software Interrupt Request 2 Register (SSIR3)              |     |

|     | 4.2.43   | System Software Interrupt Request 4 Register (SSIR4)              |     |

|     | 4.2.44   | RAM Control Register (RAMGCR)                                     |     |

|     | 4.2.45   | Bus Matrix Module Control Register1 (BMMCR1).                     | 124 |

|     | 4.2.46   | Bus Matrix Module Control Register (BMMCR2)                       |     |

|     | 4.2.47   | MMU Global Control Register (MMUGCR)                              |     |

|     | 4.2.47   | Clock Control Register (CLKCNTL)                                  |     |

|     | 4.2.49   | ECP Control Register (ECPCNTL)                                    |     |

|     | 4.2.49   | DSP Master Global Control Register (DSPGCR)                       |     |

|     | 4.2.50   | DOF Master Global Cultiful Register (DOFGCR)                      | 130 |

|            | 4.2.51  |                                                               |     |

|------------|---------|---------------------------------------------------------------|-----|

|            |         | System Exception Control Register (SYSECR)                    |     |

|            |         | System Exception Status Register (SYSESR)                     |     |

|            | 4.2.54  | Global Status Register (GLBSTAT)                              |     |

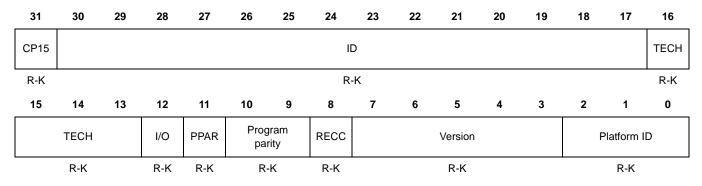

|            | 4.2.55  | Device Identification Register (DEVID)                        |     |

|            | 4.2.56  | Software Interrupt Vector Register (SSIVEC)                   |     |

|            | 4.2.57  | System Software Interrupt Flag Register (SSIF)                | 139 |

| 4.3        | Periph  | neral Central Resource (PCR) Control Registers                |     |

|            | 4.3.1   | Peripheral Memory Protection Set Register 0 (PMPROTSET0)      | 148 |

|            | 4.3.2   | Peripheral Memory Protection Set Register1 (PMPROTSET1)       | 149 |

|            | 4.3.3   | Peripheral Memory Protection Clear Register 0 (PMPROTCLR0)    | 150 |

|            | 4.3.4   | Peripheral Memory Protection Clear Register1 (PMPROTCLR1)     | 151 |

|            | 4.3.5   | Peripheral Protection Set Register 0 (PPROTSET0)              |     |

|            | 4.3.6   | Peripheral Protection Set Register 1 (PPROTSET1)              | 154 |

|            | 4.3.7   | Peripheral Protection Set Register 2 (PPROTSET2)              |     |

|            | 4.3.8   | Peripheral Protection Set Register 3 (PPROTSET3)              |     |

|            | 4.3.9   | Peripheral Protection Clear Register 0 (PPROTCLR0)            |     |

|            | 4.3.10  | Peripheral Protection Clear Register 1 (PPROTCLR1)            |     |

|            | 4.3.11  | Peripheral Protection Clear Register 2 (PPROTCLR2)            |     |

|            | 4.3.12  | Peripheral Protection Clear Register 3 (PPROTCLR3)            |     |

|            | 4.3.13  | Peripheral Memory Power-Down Set Register 0 (PCSPWRDWNSET0)   |     |

|            | 4.3.14  | Peripheral Memory Power-Down Set Register1 (PCSPWRDWNSET1)    |     |

|            | 4.3.15  | Peripheral Memory Power-Down Clear Register 0 (PCSPWRDWNCLR0) |     |

|            | 4.3.16  | Peripheral Memory Power-Down Clear Register (PCSPWRDWNCLR1)   |     |

|            | 4.3.17  | Peripheral Power-Down Set Register 0 (PSPWRDWNSET0)           |     |

|            | 4.3.18  | Peripheral Power-Down Set Register 1 (PSPWRDWNSET1)           |     |

|            | 4.3.19  | Peripheral Power-Down Set Register 2 (PSPWRDWNSET2)           |     |

|            | 4.3.19  | Peripheral Power-Down Set Register 3 (PSPWRDWNSET3)           |     |

|            | 4.3.21  | Peripheral Power-Down Clear Register 0 (PSPWRDWNCLR0)         |     |

|            | 4.3.21  | Peripheral Power-Down Clear Register 1 (PSPWRDWNCLR1)         |     |

|            | 4.3.23  | Peripheral Power-Down Clear Register 2 (PSPWRDWNCLR2)         |     |

|            |         | Peripheral Power-Down Clear Register 3 (PSPWRDWNCLR3)         |     |

| 4.4        |         |                                                               |     |

| 4.4        | 4.4.1   | up Control Registers                                          |     |

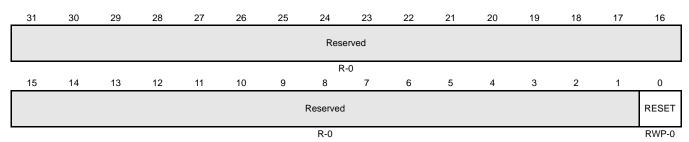

|            |         | Wakeup Reset Control Register (RSTCR)                         |     |

|            | 4.4.2   | External Wakeup Enable Register (EXTWAKENR)                   |     |

|            | 4.4.3   | External Wakeup Level Register (EXTWAKLVR)                    |     |

|            | 4.4.4   | External Wakeup Status Register (EXTWAKESR)                   |     |

|            | 4.4.5   | Hibernate Exit and Status Register (HIBXSTATR)                |     |

| 4.5        |         | m Control Registers Secondary Frame(SYS2)                     |     |

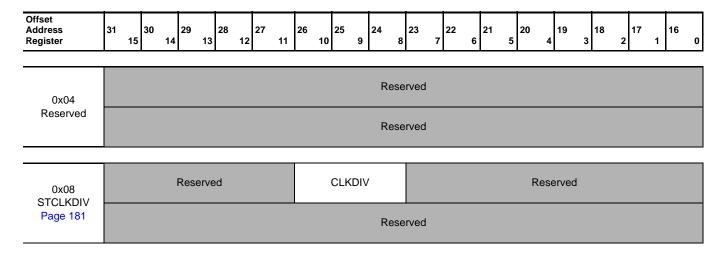

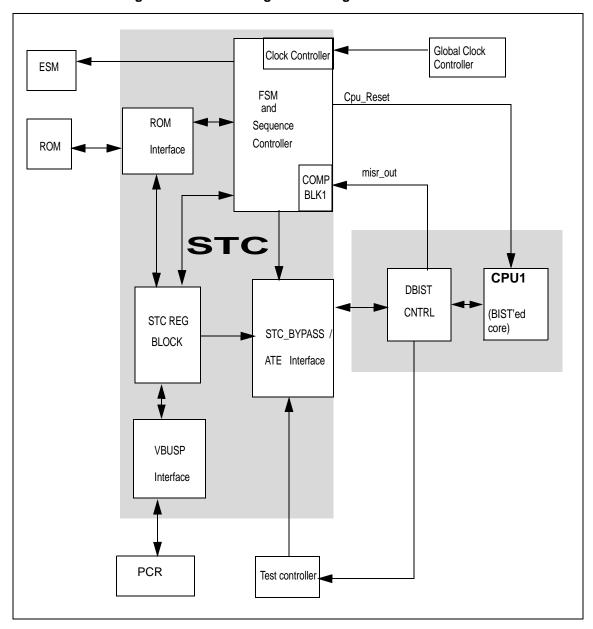

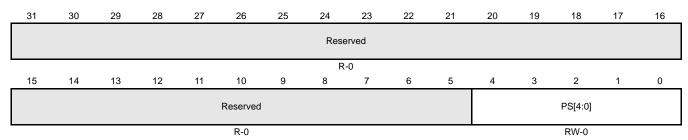

|            | 4.5.1   | CPU Logic BIST Clock Divider (STCLKDIV)                       | 181 |

| Emb        | oddod 9 | SRAM (eSRAM)                                                  | 102 |

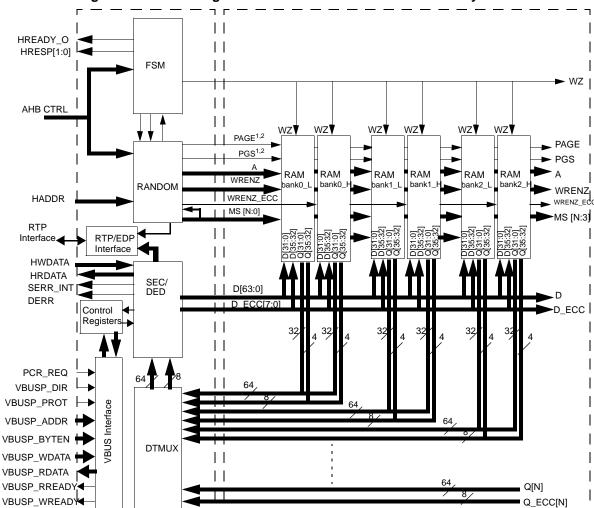

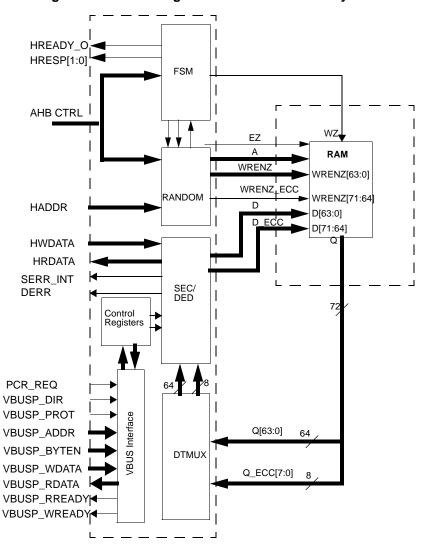

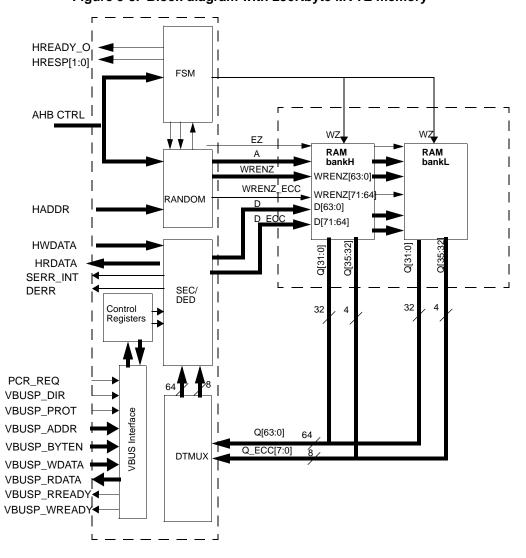

| 5.1        |         | al Description                                                |     |

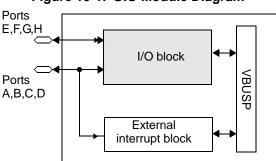

| 5.1<br>5.2 |         | diagramdiagram                                                |     |

| 5.2<br>5.3 |         |                                                               |     |

|            |         | e operation                                                   |     |

| 5.4        |         | cess Operation                                                |     |

| 5.5        |         | <b>,</b>                                                      | 190 |

|            | 5.5.1   | Read-Modify-Write Operation                                   |     |

|            | 5.5.2   |                                                               | 191 |

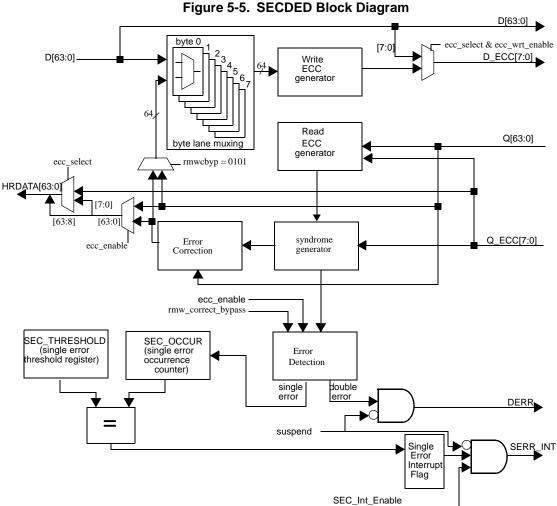

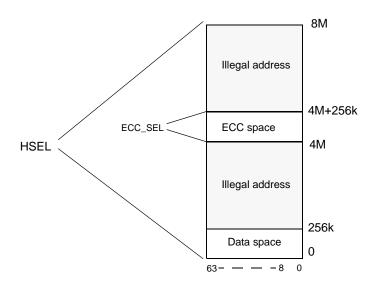

|            | 5.5.3   | ECC Memory Mapping                                            |     |

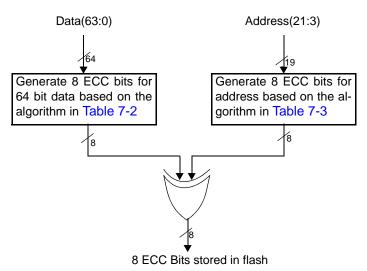

|            | 5.5.4   | ECC Generation                                                |     |

|            | 5.5.5   | Double Error Detection                                        |     |

|            | 5.5.6   | Single Error Correction                                       | 194 |

|     | 5.5.7   | False Double Error Detection                                                       |     |

|-----|---------|------------------------------------------------------------------------------------|-----|

|     | 5.5.8   | Interrupt and Error Generation                                                     |     |

|     | 5.5.9   | Emulation                                                                          | 195 |

| 5.6 | Hardw   | are RAM Initialization                                                             | 196 |

| 5.7 | Contro  | ol Registers                                                                       | 197 |

|     | 5.7.1   | RAM Control Register (RAMCTRL)                                                     |     |

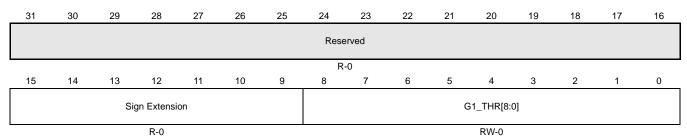

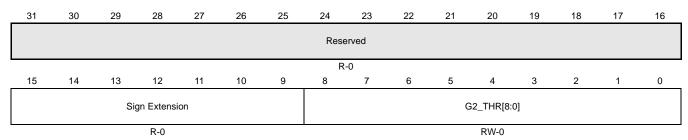

|     | 5.7.2   | Threshold Register (RAMTHRESHOLD)                                                  |     |

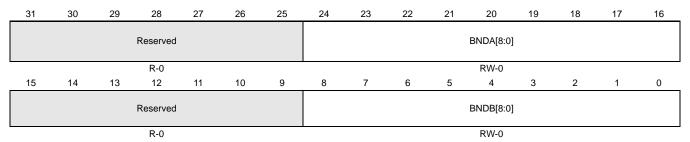

|     | 5.7.3   | Occurrence Register (RAMOCCUR)                                                     |     |

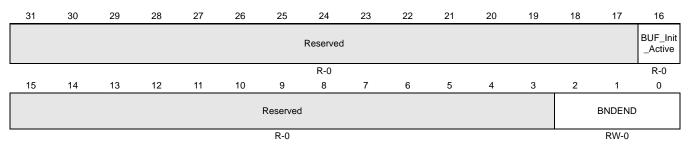

|     | 5.7.4   | Interrupt Control Register (RAMINTCTRL)                                            |     |

|     | _       |                                                                                    |     |

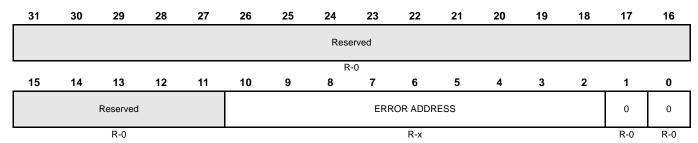

|     | 5.7.5   | Memory Fault Detect Status Register (RAMERRSTATUS)                                 |     |

|     | 5.7.6   | Single Error Address Register (RAMSERRADD)                                         |     |

|     | 5.7.7   | RAM Error Position Register (RAMERRPOSITION)                                       |     |

|     | 5.7.8   | Double Error Address Register (RAMDERRADD)                                         | 206 |

|     | 5.7.9   | RAM Control Register (RAMCTRL2)                                                    | 207 |

|     |         |                                                                                    |     |

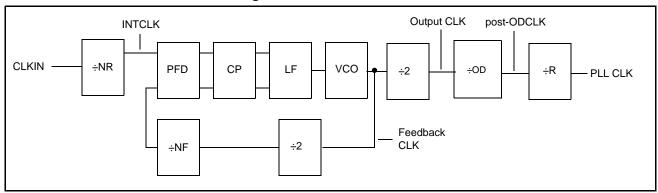

| Pha | se-Lock | ed Loop (PLL) Clock Module                                                         | 209 |

| 6.1 | Device  | Clock Overview                                                                     | 210 |

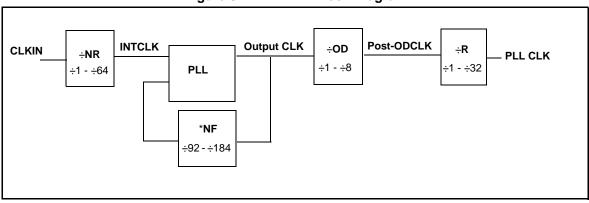

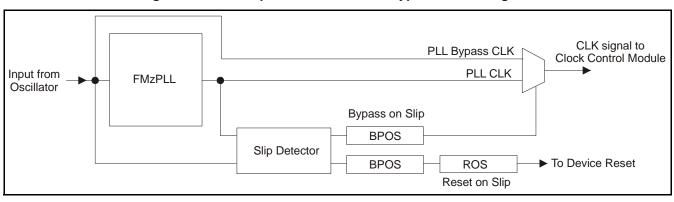

| 6.2 | FMzPL   | L Introduction/Feature Overview                                                    | 212 |

|     | 6.2.1   | Features                                                                           |     |

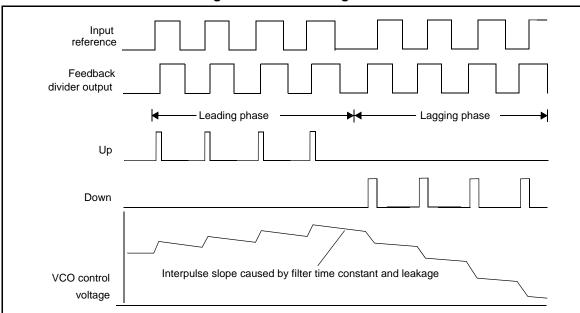

| 6.3 |         | L Operation                                                                        |     |

| 0.0 | 6.3.1   | Phase-Locked Loop (PLL) Description                                                |     |

| 6.4 | 0.0     | , .                                                                                |     |

| 0.4 |         | L Control Registers                                                                |     |

|     | 6.4.1   | Control registers                                                                  |     |

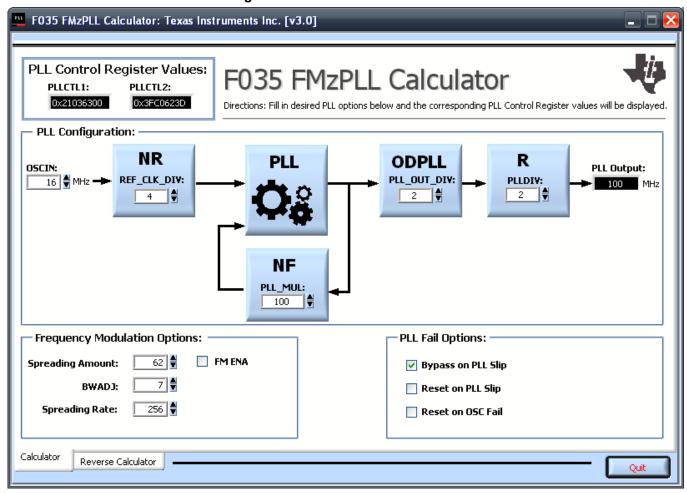

| 6.5 |         | L Calculator (F035 FMzPLL Calculator)                                              |     |

| 6.6 | FMzPL   | L Configuration Example                                                            | 225 |

|     |         |                                                                                    |     |

|     |         | Module                                                                             |     |

| 7.1 | Overvi  | iew                                                                                | _   |

|     | 7.1.1   | Features                                                                           | 228 |

|     | 7.1.2   | Definition of Terms                                                                | 228 |

|     | 7.1.3   | F035 Flash Tools                                                                   | 229 |

| 7.2 | Defaul  | t flash configuration                                                              |     |

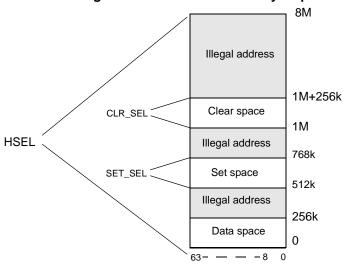

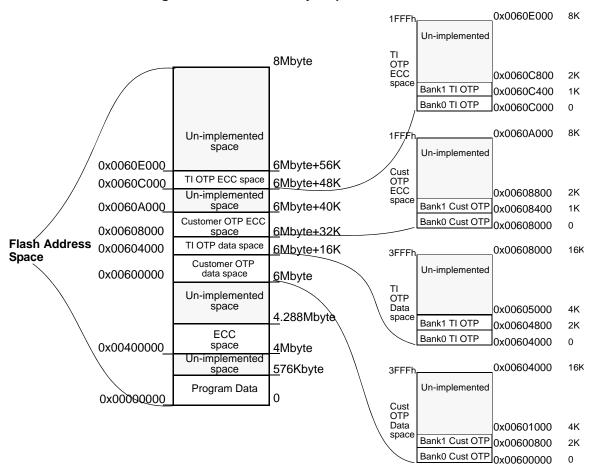

| 7.3 |         | ry Map                                                                             |     |

|     | 7.3.1   | Illegal Address Generation                                                         |     |

| 7.4 |         | tion                                                                               |     |

| 7.4 | 7.4.1   |                                                                                    |     |

|     |         | Flash Read Modes                                                                   |     |

|     | 7.4.2   | Erase/Program Flash                                                                |     |

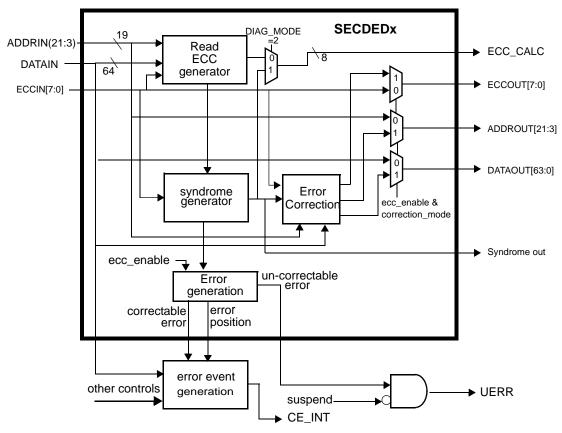

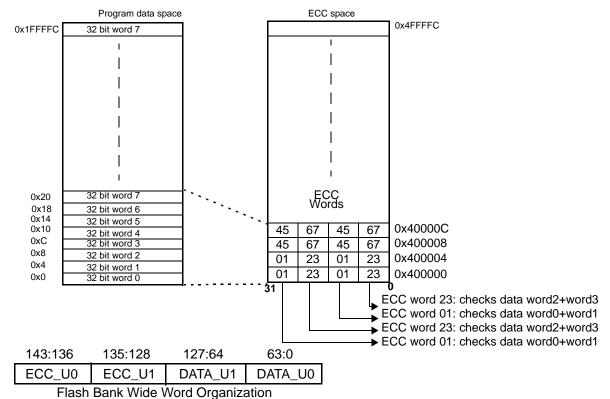

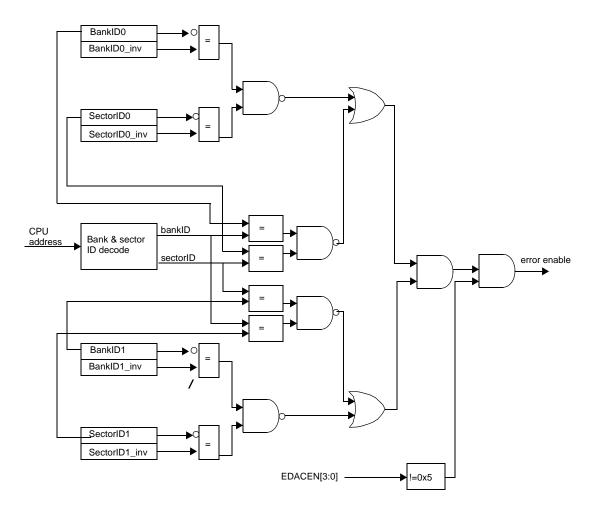

|     | 7.4.3   | ECC Protection                                                                     |     |

|     | 7.4.4   | Data Security                                                                      |     |

|     | 7.4.5   | Automatic Power-down of Flash Banks                                                | 244 |

| 7.5 | Contro  | ol Registers                                                                       | 245 |

|     | 7.5.1   | Flash Option Control Register (FRDCNTL)                                            | 249 |

|     | 7.5.2   | Flash Special Read Control Register (FSPRD)                                        |     |

|     | 7.5.3   | Flash Error Detection and Correction Control Register 1 (FEDACCTRL1 - 0xFFF87008)  |     |

|     | 7.5.4   | Flash Error Correction and Correction Control Register 2 (FEDACCTRL2 - 0xFFF8700C) |     |

|     | 7.5.5   | Flash Error Correction Counter Register (FCOR_ERR_CNT - 0xFFF87010)                |     |

|     |         |                                                                                    |     |

|     | 7.5.6   | Flash Correctable Error Address (FCOR_ERR_ADD - 0xFFF87014)                        |     |

|     | 7.5.7   | Correctable Error Position Register (FCOR_ERR_POS)                                 |     |

|     | 7.5.8   | Flash Error Status Register (FEDACSTATUS - 0xFFF8701C)                             |     |

|     | 7.5.9   | Flash Un-correctable Error Address (FUNC_ERR_ADD - 0xFFF87020)                     | 261 |

|     | 7.5.10  | Flash Error Detection Sector Disable (FEDACSDIS - 0xFFF87024)                      | 262 |

|     | 7.5.11  | Flash Bank Protection Register (FBPROT - 0xFFF87030)                               |     |

|     | 7.5.12  | Flash Bank Sector Enable Register (FBSE- 0xFFF87034)                               |     |

|     |         | Flash Bank Access Control Register (FBAC - 0x3C)                                   |     |

|     | 1.0.13  | 1 1831 Dank 700633 CUITIUI Negistei (1 DAC - 0830)                                 | ∠00 |

|                 | 7 5 14   | Flash Bank Fallback Power Register (FBFALLBACK - 0xFFF87040)   | 266 |

|-----------------|----------|----------------------------------------------------------------|-----|

|                 |          | Flash Bank/Pump Ready Register (FBPRDY - 0xFFF87044)           |     |

|                 |          | Flash Pump Access Control Register 1 (FPAC1 - 0xFFF87048)      |     |

|                 |          | Flash Pump Access Control Register 2 (FPAC2 - 0xFFF8704C)      |     |

|                 | 7.5.18   | Flash Module Access Control Register (FMAC - 0xFFF87050)       |     |

|                 | 7.5.19   | Flash Emulation ECC Register (FEMU_ECC - 0xFFF87060 )          |     |

|                 |          | Flash Error Detection Sector Disable (FEDACSDIS2 - 0xFFF870C0) |     |

|                 | 0.20     | (1 25/1005) October 2000 5/005/01 (1 25/1005/02                |     |

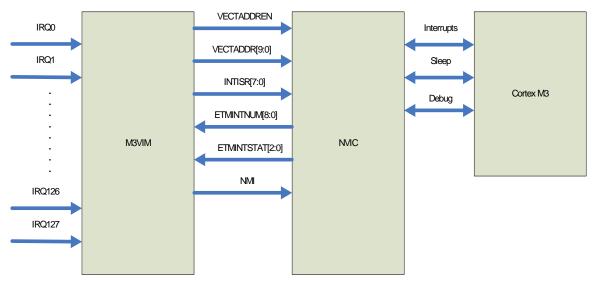

| Cort            | ex-M3 V  | /ectored Interrupt Manager (M3VIM) Module                      | 275 |

| 8.1             | Overvi   | iew                                                            | 276 |

|                 | 8.1.1    | Interrupt Handling at the CPU                                  | 276 |

|                 | 8.1.2    | Nesting Behavior                                               | 276 |

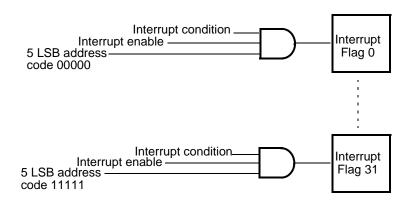

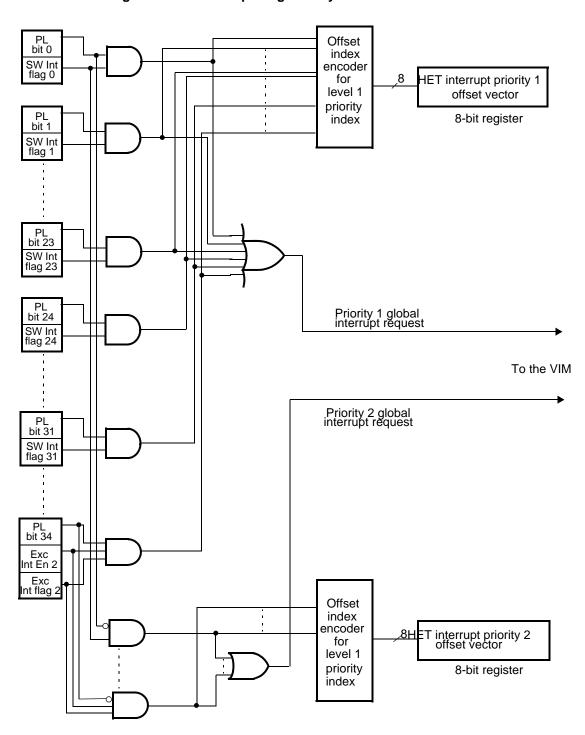

|                 | 8.1.3    | Interrupt Generation at the Peripheral                         | 277 |

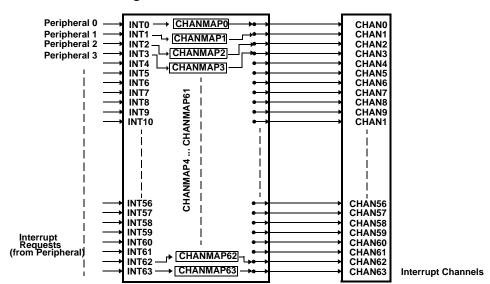

| 8.2             |          | ıpt management                                                 | 278 |

|                 | 8.2.1    | M3VIM Interrupt request management                             |     |

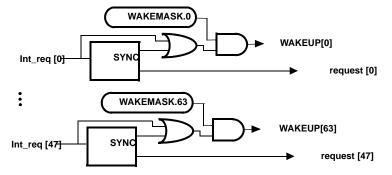

|                 | 8.2.2    | M3VIM Wake-up Interrupt                                        |     |

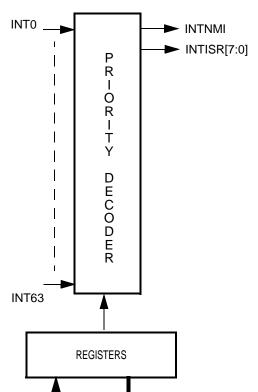

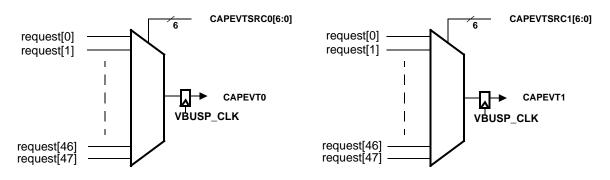

|                 | 8.2.3    | M3VIM Input Channel Management                                 |     |

|                 | 8.2.4    | M3VIM Prioritization                                           |     |

| 8.3             |          | 1 Operation                                                    |     |

|                 | 8.3.1    | Vector Table                                                   |     |

|                 | 8.3.2    | M3VIM response to interrupt request                            |     |

|                 | 8.3.3    | .Emulation                                                     |     |

| 8.4             | •        | re event sources                                               |     |

| 8.5             | _        | ammer's Model Notes                                            |     |

|                 | 8.5.1    | Required Software Initialization                               |     |

|                 | 8.5.2    | NVIC vs. M3VIM controls                                        |     |

|                 | 8.5.3    | Autovectoring versus INTNMI Interrupts                         |     |

|                 | 8.5.4    | Interrupt Clearing                                             |     |

|                 | 8.5.5    | Reset                                                          |     |

| 8.6             | _        | ters                                                           |     |

|                 | 8.6.1    | M3VIM Channel Offset Registers                                 |     |

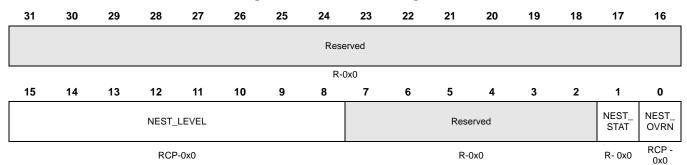

|                 | 8.6.2    | NESTCTRL Register                                              |     |

|                 | 8.6.3    | NESTSTAT Register                                              |     |

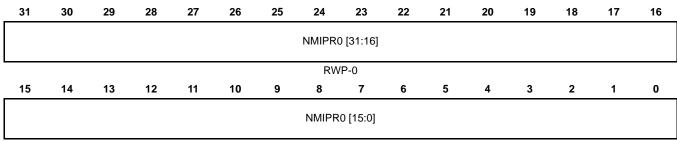

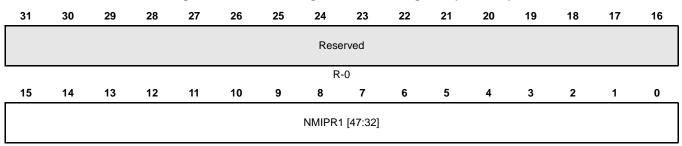

|                 | 8.6.4    | INTNMI/INTISR Program Control Registers (NMIPRx)               |     |

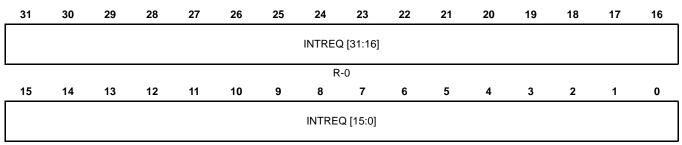

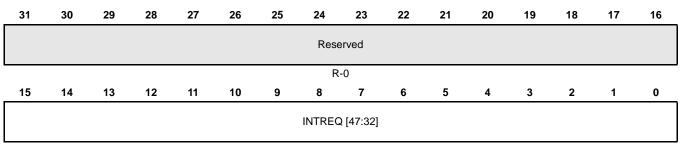

|                 | 8.6.5    | Pending Interrupt Read Location Registers (INTREQx)            |     |

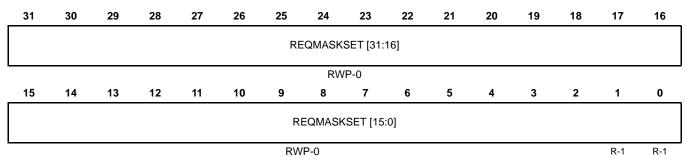

|                 | 8.6.6    | Interrupt Mask Set Registers (REQMASKSETx)                     |     |

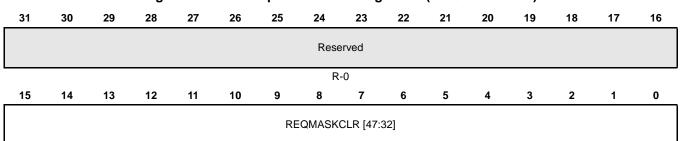

|                 | 8.6.7    | Interrupt Mask Clear Registers (REQMASKCLRx)                   |     |

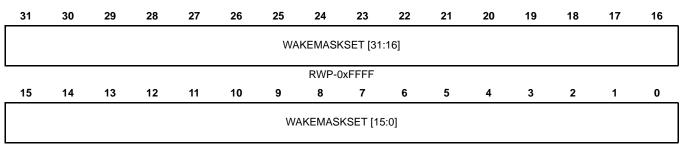

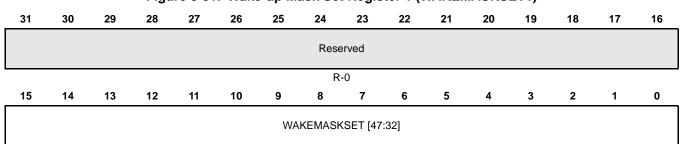

|                 | 8.6.8    | Wake-up Mask Set Registers (WAKEMASKSETx)                      |     |

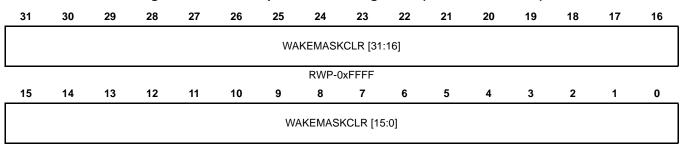

|                 | 8.6.9    | Wake-up Mask Clear Registers (WAKEMASKCLRx)                    |     |

|                 | 8.6.10   | Capture Event Register (CAPEVT)                                |     |

|                 | 8.6.11   | M3VIM Interrupt Control Register x (CHANCTRL x)                | 318 |

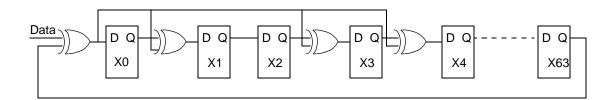

| Cvc             | lic Radu | ındancy Check Controller (CRC) Module                          | 323 |

| 9.1             |          | iew                                                            |     |

| 9.2             |          | 70M Series CRC Features                                        |     |

| 9.3             |          | e Operation                                                    |     |

| 3.3             | 9.3.1    | General Operation                                              |     |

|                 | 9.3.2    | Modes                                                          |     |

|                 | 9.3.3    | Register Definitions                                           |     |

|                 | 9.3.4    | Power-Down Mode                                                |     |

|                 | 9.3.5    | Emulation                                                      |     |

| 9.4             |          | Control Registers                                              |     |

| J. <del>T</del> | 9.4.1    | CRC Global Control Register 0 (CRC_CTRL0)                      |     |

|                 | 9.4.2    | CRC Global Control Register (CRC_CTRL1)                        |     |

|                 | U.T.Z    |                                                                | JJ2 |

|      | 9.4.3   | CRC Global Control Register 2 (CRC_CTRL2)                  | 333 |

|------|---------|------------------------------------------------------------|-----|

|      | 9.4.4   | PSA Signature Low Register 1 (PSA_SIGREGL1)                | 335 |

|      | 9.4.5   | PSA Signature High Register 1 (PSA_SIGREGH1)               |     |

|      | 9.4.6   | PSA Sector Signature Low Register 1 (PSA_SECSIGREGL1)      | 337 |

|      | 9.4.7   | PSA Sector Signature High Register 1 (PSA_SECSIGREGH1)     | 338 |

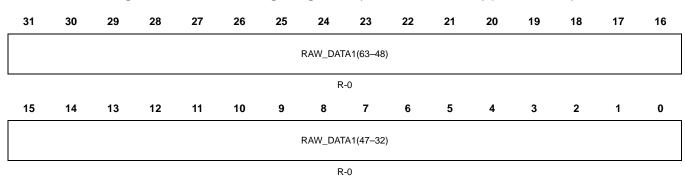

|      | 9.4.8   | Raw Data Low Register 1 (RAW_DATAREGL1)                    | 339 |

|      | 9.4.9   | Raw Data High Register 1 (RAW_DATAREGH1)                   | 340 |

|      |         |                                                            |     |

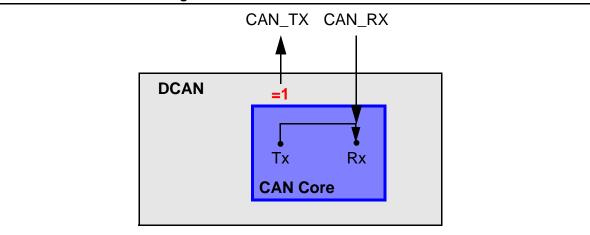

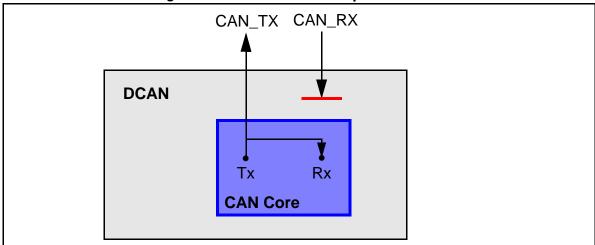

|      |         | Area Network (DCAN)                                        |     |

| 10.1 |         | iew                                                        |     |

|      |         | Features                                                   |     |

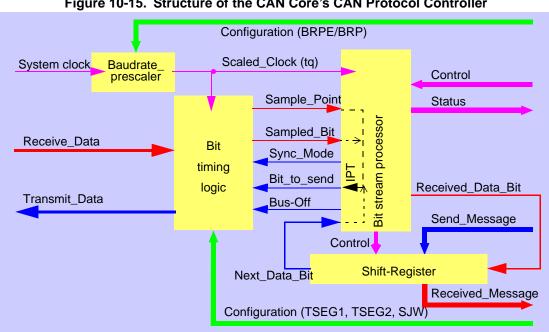

|      |         | Functional Description                                     |     |

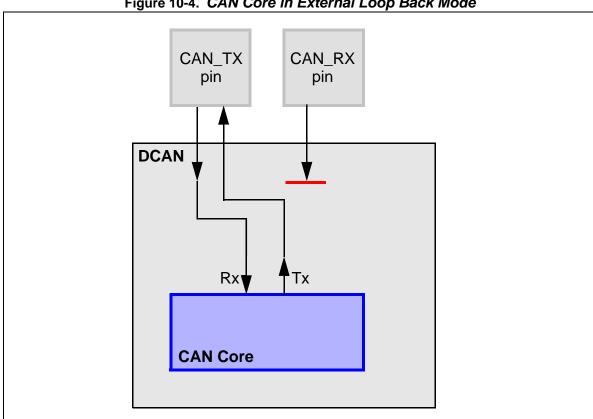

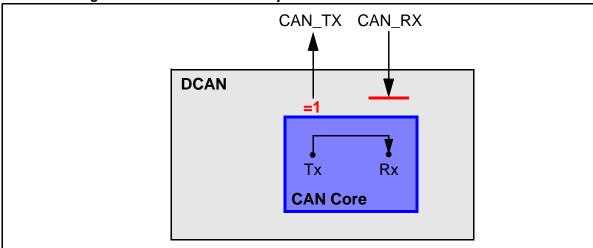

|      |         | Block Diagram                                              |     |

| 10.2 | •       | ting Modes                                                 |     |

|      |         | Software Initialization                                    |     |

|      |         | CAN Message Transfer (Normal Operation)                    |     |

|      |         | Test Modes                                                 |     |

|      |         | Clock Source                                               |     |

|      |         | upport                                                     |     |

|      |         | nitialization                                              |     |

| 10.6 |         | ıpt functionality                                          |     |

|      |         | Message Object interrupts                                  |     |

|      |         | Status Change Interrupts                                   |     |

|      |         | Error Interrupts                                           |     |

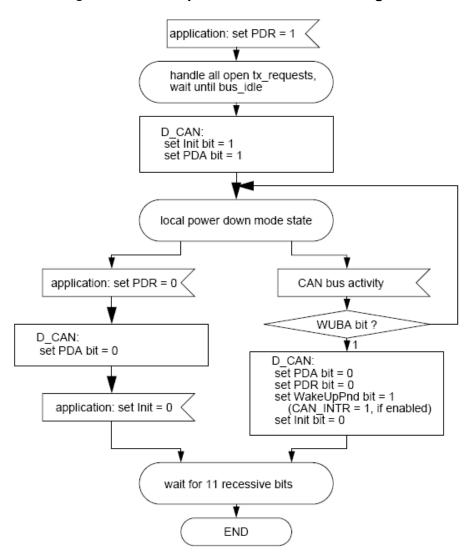

| 10.7 |         | I power down mode                                          |     |

|      |         | Entering global power down mode                            |     |

|      |         | Wakeup from global power down mode                         |     |

| 10.8 |         | power down mode                                            |     |

|      |         | Entering local power down mode                             |     |

|      |         | Wakeup from local power down                               |     |

| 10.9 | •       | Check Mechanism                                            |     |

|      |         | Behavior on parity error                                   |     |

|      |         | Parity testing.                                            |     |

|      | -       | g/Suspend Mode                                             |     |

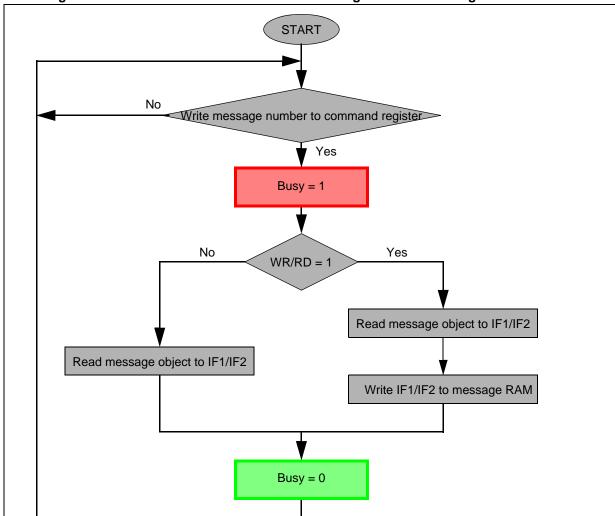

|      |         | le Initialization                                          |     |

| 10.1 |         | guration of Message Objects                                |     |

|      |         | Configuration of a Transmit Object for Data Frames         |     |

|      |         | 2 Configuration of a Transmit Object for Remote Frames     |     |

|      |         | 3 Configuration of a Single Receive Object for Data Frames |     |

|      |         | Configuration of a Single Receive Object for Remote Frames |     |

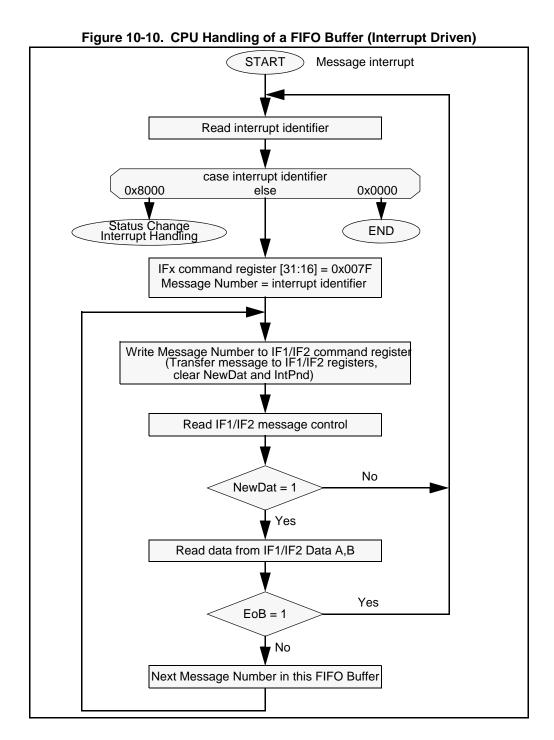

|      |         | Configuration of a FIFO Buffer                             |     |

| 10.1 |         | age Handling                                               |     |

|      |         | Message Handler Overview                                   |     |

|      |         | Receive/Transmit Priority                                  |     |

|      |         | 5                                                          | 365 |

|      |         | ,                                                          |     |

|      |         | ,                                                          |     |

|      |         | Acceptance Filtering of Received Messages                  |     |

|      |         | Reception of Data Frames                                   |     |

|      |         | Reception of Remote Frames                                 |     |

|      |         | Reading Received Messages                                  |     |

|      |         | ORequesting New Data for a Receive Object                  |     |

|      | 10.13.1 | 1Storing Received Messages in FIFO Buffers                 | 367 |

|       | 10.13.12Reading from a FIFO Buffer                                                        |     |

|-------|-------------------------------------------------------------------------------------------|-----|

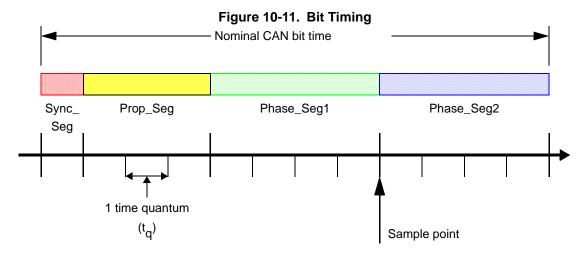

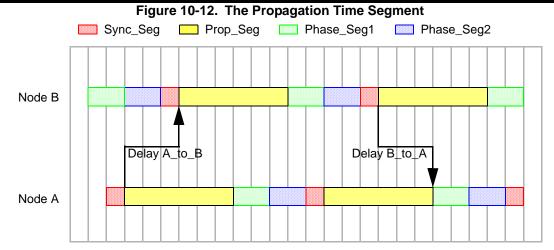

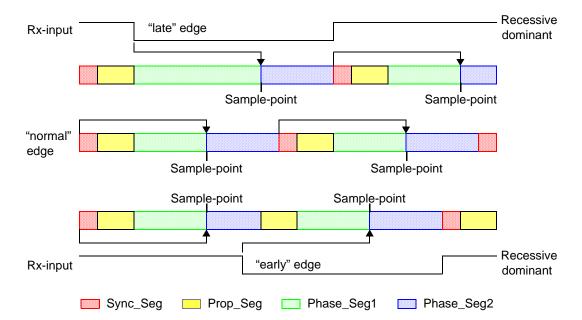

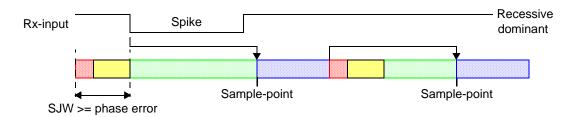

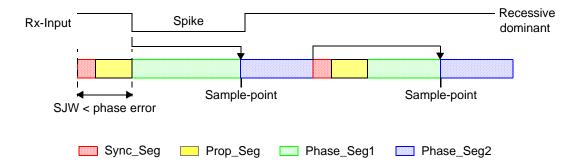

| 10.14 | 4 CAN Bit Timing                                                                          |     |

|       | 10.14.1 Bit Time and Bit Rate                                                             |     |

|       | 10.14.2 Configuration of the DCAN Bit Timing                                              |     |

| 10.15 | 5 Message Interface Register Sets                                                         |     |

|       | 10.15.1 Message Interface Register Sets 1 and 2                                           |     |

|       | 10.15.2 IF3 Register Set                                                                  |     |

| 10.16 | 6 Message RAM                                                                             |     |

|       | 10.16.1 Structure of Message Objects                                                      |     |

|       | 10.16.2 Addressing Message Objects in RAM                                                 |     |

|       | 10.16.3 Message RAM representation in Debug/Suspend Mode                                  |     |

|       | 10.16.4 Message RAM representation in Direct Access Mode                                  |     |

| 10.17 | 7 DCAN Control Registers                                                                  |     |

|       | 10.17.1 CAN Control Register (DCAN CTL)                                                   |     |

|       | 10.17.2 Error and Status Register (DCAN ES)                                               |     |

|       | 10.17.3 Error Counter Register (DCAN ERRC).                                               |     |

|       | 10.17.4 Bit Timing Register (DCAN BTR)                                                    |     |

|       | 10.17.5 Interrupt Register (DCAN INT)                                                     |     |

|       | 10.17.6 Test Register (DCAN TEST)                                                         |     |

|       | 10.17.7 Parity Error Code Register (DCAN PERR)                                            |     |

|       | 10.17.8 DCAN Core Release Register (DCAN REL)                                             |     |

|       | 10.17.9 Auto-Bus-On Time Register (DCAN ABOTR)                                            |     |

|       | 10.17.10Transmission Request X Register (DCAN TXRQ X)                                     |     |

|       | 10.17.11Transmission Request Registers (DCAN TXRQ12 to DCAN TXRQ78)                       |     |

|       | 10.17.12New Data X Register (DCAN NWDAT X)                                                |     |

|       | 10.17.13New Data Registers (DCAN NWDAT12 to DCAN NWDAT78)                                 |     |

|       | 10.17.14Interrupt Pending X Register (DCAN INTPND X)                                      |     |

|       | 10.17.15Interrupt Pending Registers (DCAN INTPND12 to DCAN INTPND78)                      |     |

|       | 10.17.16Message Valid X Register (DCAN MSGVAL X)                                          |     |

|       | 10.17.17Message Valid Registers (DCAN MSGVAL12 to DCAN MSGVAL78)                          |     |

|       | 10.17.18Interrupt Multiplexer Registers (DCAN INTMUX12 to DCAN INTMUX78)                  |     |

|       | 10.17.19IF1/IF2 Command Registers (DCAN IF1CMD, DCAN IF2CMD)                              |     |

|       | 10.17.20IF1/IF2 Mask Registers (DCAN IF1MSK, DCAN IF2MSK)                                 |     |

|       | 10.17.21IF1/IF2 Arbitration Registers (DCAN IF1ARB, DCAN IF2ARB)                          |     |

|       | 10.17.22IF1/IF2 Message Control Registers (DCAN IF1MCTL, DCAN IF2MCTL)                    |     |

|       | 10.17.23IF1/IF2 Data A and Data B Registers (DCAN IF1DATA/DATB, DCAN IF2DATA/DATB)        |     |

|       | 10.17.24IF3 Observation Register (DCAN IF3OBS)                                            |     |

|       | 10.17.25IF3 Mask Register (DCAN IF3MSK)                                                   |     |

|       | 10.17.26IF3 Arbitration Register (DCAN IF3ARB)                                            |     |

|       | 10.17.27IF3 Message Control Register (DCAN IF3MCTL)                                       |     |

|       | 10.17.28IF3 Data A and Data B Registers (DCAN IF3DATA/DATB)                               |     |

|       | 10.17.29IF3 Update Enable Registers (DCAN IF3UPD12 to IF3UPD78)                           |     |

|       | 10.17.30CAN TX IO Control Register (DCAN TIOC)                                            |     |

|       | 10.17.31CAN RX IO Control Register (DCAN RIOC)                                            | 446 |

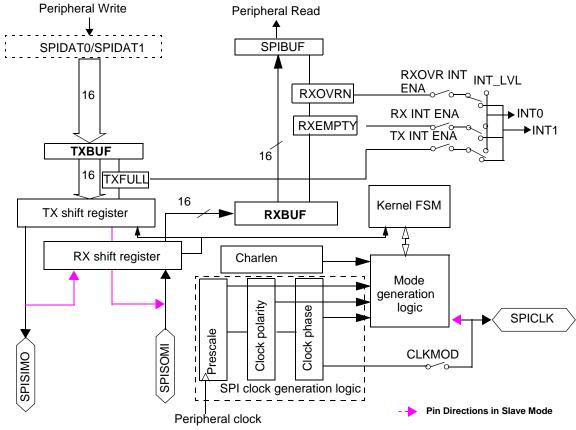

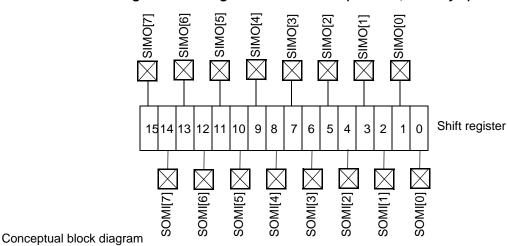

| Multi | i-Buffered Serial Peripheral Interface Module (MibSPI) with Parallel Pin Option (MibSPIP) | 440 |

|       | Overview                                                                                  |     |

|       | 11.1.1 Word Format Options                                                                |     |

|       | 11.1.2 Multi-buffering (Mib) support                                                      |     |

|       | 11.1.3 Transmission Lock (Multi-Buffer Mode Master Only)                                  |     |

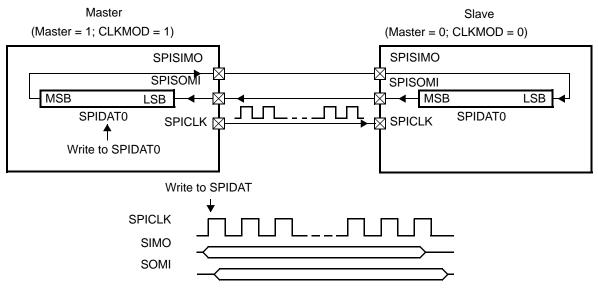

| 11 2  | Operating Modes                                                                           |     |

| 2     | 11.2.1 Pin Configurations                                                                 |     |

|       | 11.2.2 Data Handling                                                                      |     |

|       |                                                                                           |     |

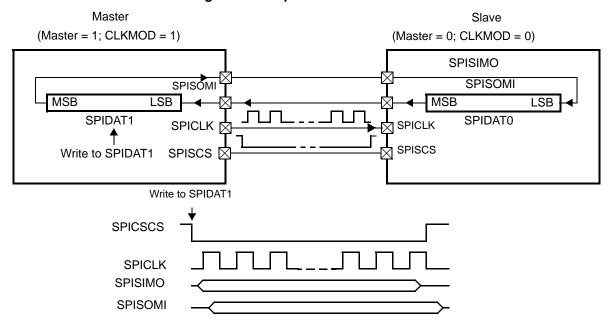

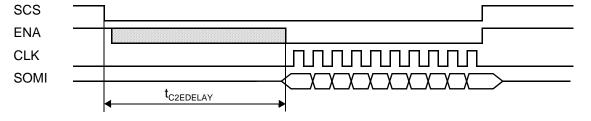

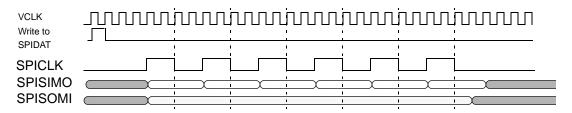

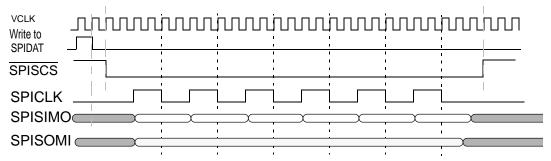

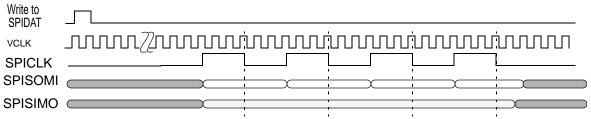

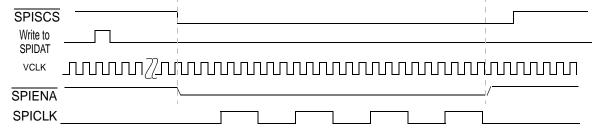

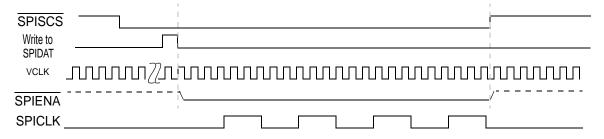

|      | 11.2.3 Operation with SPISCS                                                     |     |

|------|----------------------------------------------------------------------------------|-----|

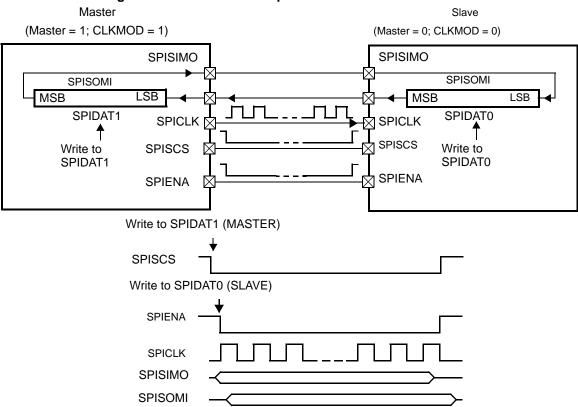

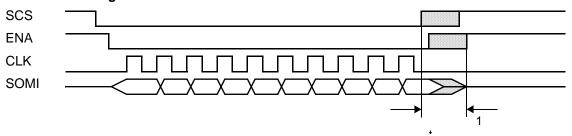

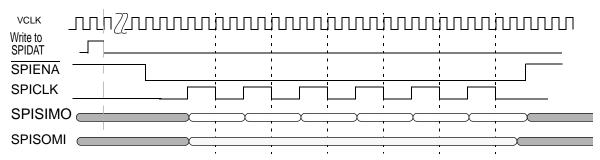

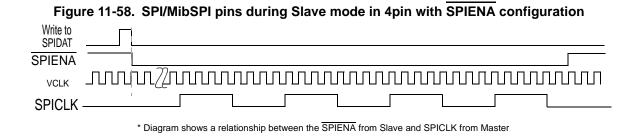

|      | 11.2.4 Operation with SPIENA                                                     |     |

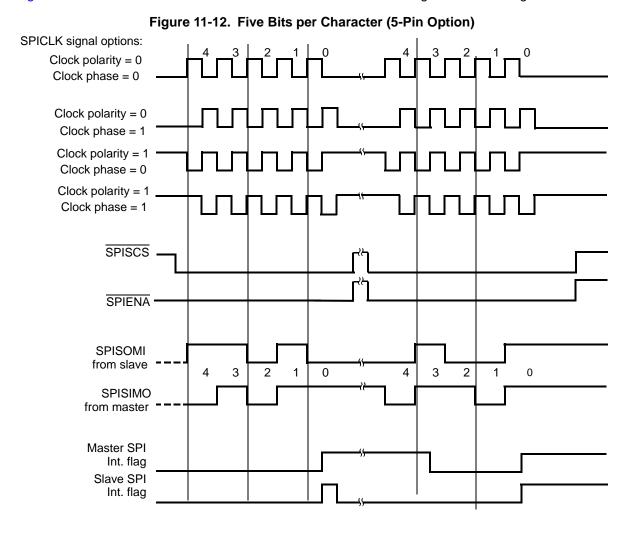

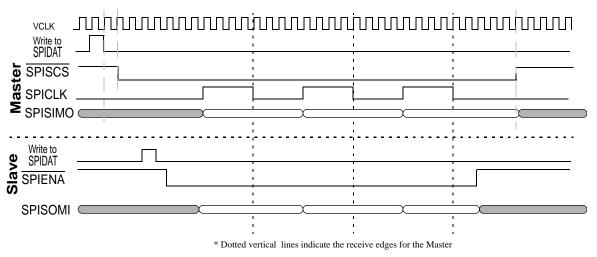

|      | 11.2.5 Five-Pin Operation (Hardware Handshaking)                                 |     |

|      | 11.2.6 Data Formats                                                              |     |

|      | 11.2.7 Clocking Modes                                                            |     |

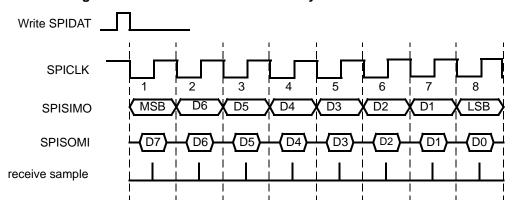

|      | 11.2.8 Data Transfer Example                                                     |     |

|      | 11.2.9 Decoded and Encoded Chip Select (Master Only)                             |     |

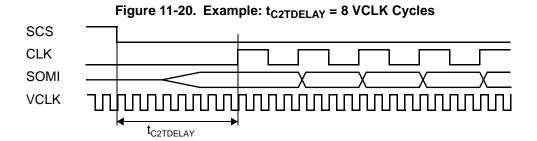

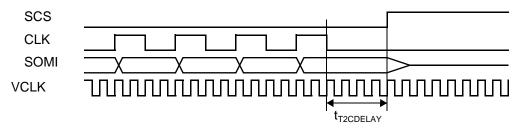

|      | 11.2.10 Variable Chip Select Setup and Hold Timing (Master Only)                 |     |

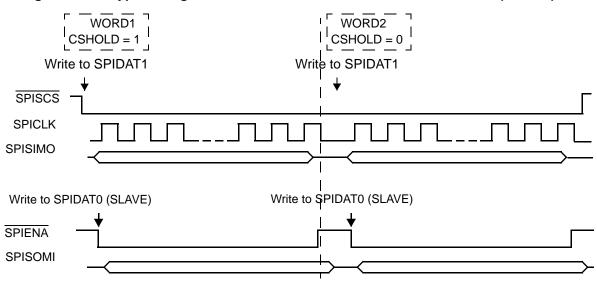

|      | 11.2.11 Hold Chip-Select Active                                                  |     |

|      | 11.2.12 Detection of Slave Desynchronization (Master Only)                       |     |

|      | 11.2.13 ENA Signal Time-Out (Master Only)                                        |     |

|      | 11.2.14 Data-Length Error                                                        |     |

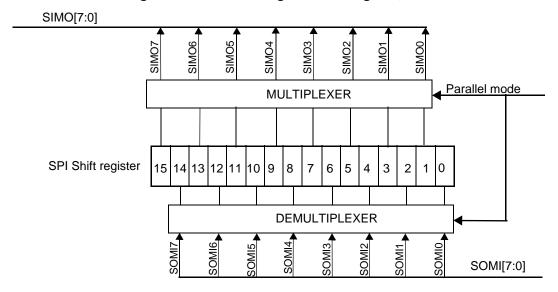

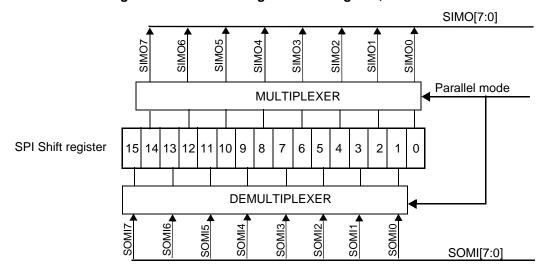

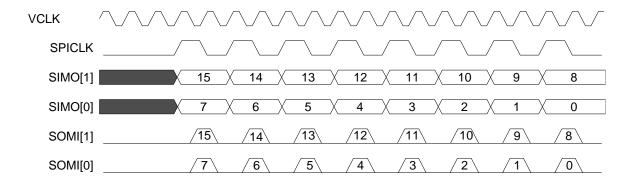

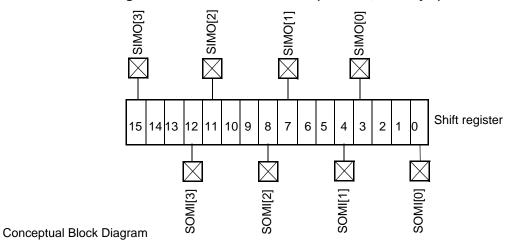

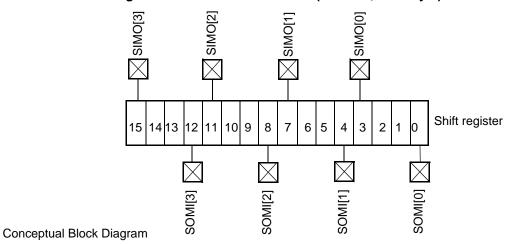

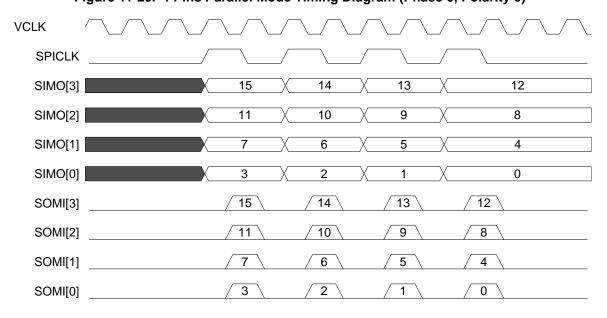

|      | 11.2.15 Parallel Mode (Multiple SIMO/SOMI Support, not available on all devices) |     |

|      | 11.2.16 Continuous Self-Test (Master/Slave)                                      |     |

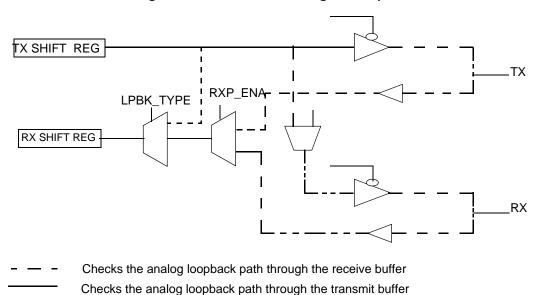

| 11.3 | Test Features                                                                    |     |

|      | 11.3.1 Internal Loop-Back Test Mode (Master Only)                                |     |

|      | 11.3.2 Input/Output Loopback Test Mode                                           |     |

|      | General-Purpose I/O                                                              |     |

| 11.5 | Low-Power Mode                                                                   | 474 |

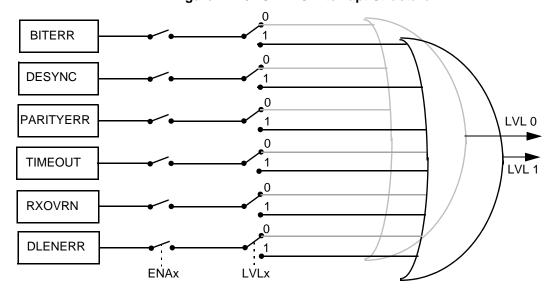

| 11.6 | Interrupts                                                                       | 475 |

|      | 11.6.1 Interrupts in Multi-Buffer Mode                                           | 475 |

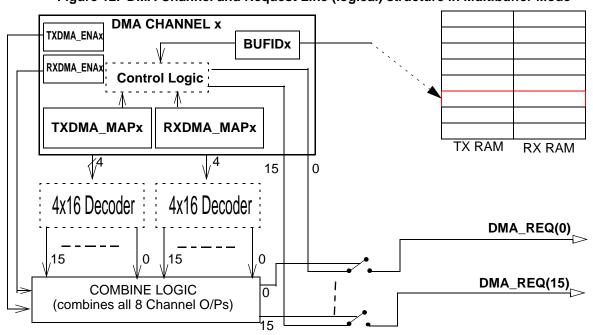

| 11.7 | DMA Interface                                                                    | 478 |

|      | 11.7.1 DMA in Multi-Buffer Mode                                                  | 478 |

| 11.8 | Module Configuration                                                             | 479 |

|      | 11.8.1 Compatibility(SPI) Mode Configuration                                     | 479 |

|      | 11.8.2 MibSPI Mode Configuration                                                 | 479 |

| 11.9 | Control Registers                                                                | 481 |

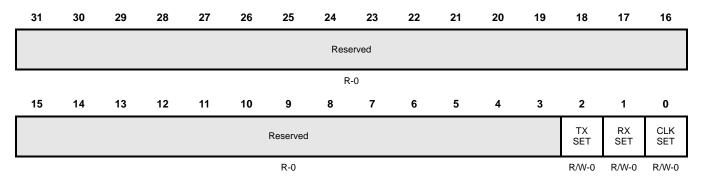

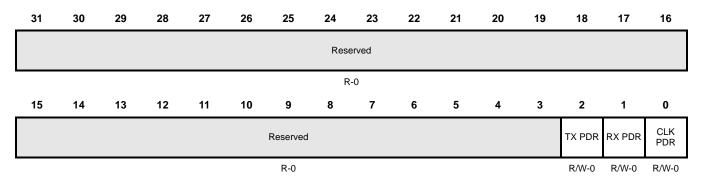

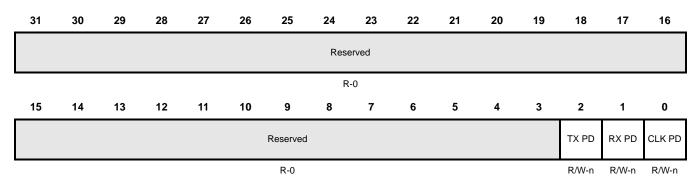

|      | 11.9.1 SPI Global Control Register 0 (SPIGCR0)                                   | 487 |

|      | 11.9.2 SPI Global Control Register 1 (SPIGCR1)                                   | 488 |

|      | 11.9.3 SPI Interrupt Register (SPIINT0)                                          |     |

|      | 11.9.4 SPI Interrupt Level Register (SPILVL)                                     |     |

|      | 11.9.5 SPI Flag Register (SPIFLG)                                                |     |

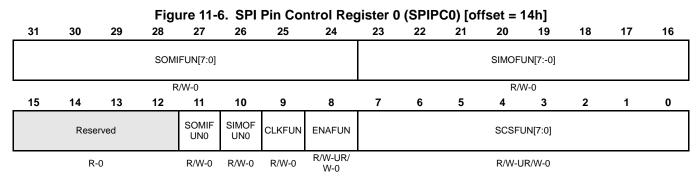

|      | 11.9.6 SPI Pin Control Register 0 (SPIPC0)                                       |     |

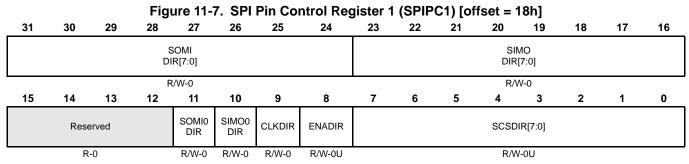

|      | 11.9.7 SPI Pin Control Register 1 (SPIPC1)                                       |     |

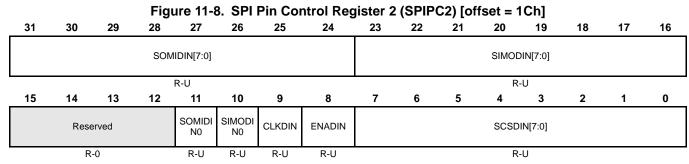

|      | 11.9.8 SPI Pin Control Register 2 (SPIPC2)                                       |     |

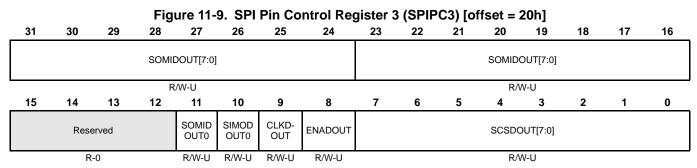

|      | 11.9.9 SPI Pin Control Register 3 (SPIPC3)                                       |     |

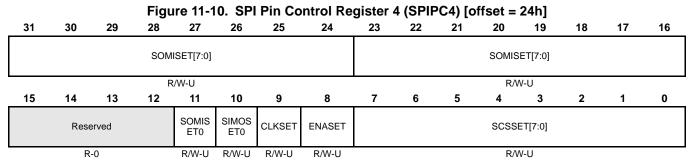

|      | 11.9.10 SPI Pin Control Register 4 (SPIPC4)                                      |     |

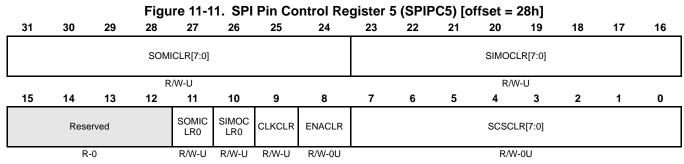

|      | 11.9.11 SPI Pin Control Register 5 (SPIPC5)                                      |     |

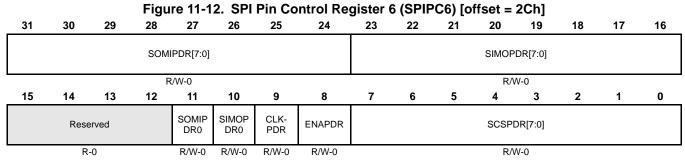

|      | 11.9.12 SPI Pin Control Register 6 (SPIPC6)                                      |     |

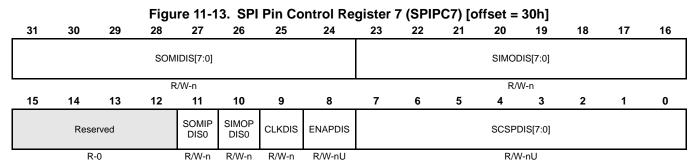

|      | 11.9.13 SPI Pin Control Register 7(SPIPC7)                                       |     |

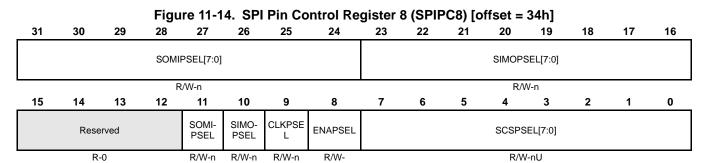

|      | 11.9.14 SPI Pin Control Register 8(SPIPC8)                                       |     |

|      | 11.9.15 SPI Transmit Data Register 0 (SPIDAT0)                                   |     |

|      | 11.9.16 SPI Transmit Data Register 1 (SPIDAT1)                                   |     |

|      | 11.9.17 SPI Receive Buffer Register (SPIBUF)                                     |     |

|      | 11.9.18 SPI Emulation Register (SPIEMU)                                          |     |

|      | 11.9.19 SPI Delay Register (SPIDELAY)                                            |     |

|      | 11.9.20 SPI Default Chip Select Register (SPIDEF)                                |     |

|      | 11.9.21 SPI Data Format Registers (SPIFMT[3:0])                                  |     |

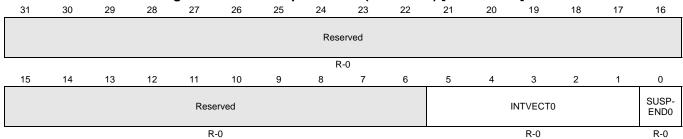

|      | 11.9.22 Interrupt Vector 0 (INTVECT0)                                            |     |

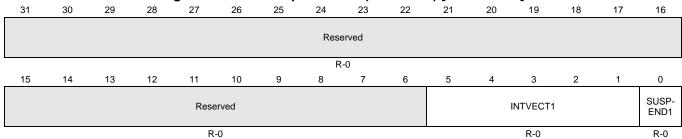

|      | 11.9.23 Interrupt Vector 1 (INTVECT1)                                            |     |

|      | 11.9.24 Parallel/Modulo Mode Control Register (SPIPMCTRL)                        |     |

|      | 11.9.25 Multi-buffer Mode Enable Register (MIBSPIE)                              |     |

|      | 11.9.26 TG Interrupt Enable Set Register (TGITENST)                              | 544 |

|      | 11.3.20 10 III. Grupt Eliable Set Negister (1011 Eliast)                         | J44 |

|                      |                                                                                                                                                                                                                                          | MibSPI TG Interrupt Enable Clear Register (TGITENCR)                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                     |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

|                      |                                                                                                                                                                                                                                          | Transfer Group Interrupt Level Set Register (TGITLVST)                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                     |

|                      | 11.9.29                                                                                                                                                                                                                                  | Transfer Group Interrupt Level Clear Register (TGITLVCR)                                                                                                                                                                                                                                                                                                                                                                                                       | 547                                                                                                                 |

|                      | 11.9.30                                                                                                                                                                                                                                  | Transfer Group Interrupt Flag Register (TGINTFLAG)                                                                                                                                                                                                                                                                                                                                                                                                             | 548                                                                                                                 |

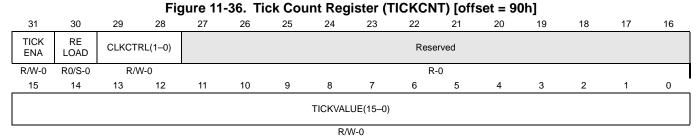

|                      | 11.9.31                                                                                                                                                                                                                                  | Tick Count Register (TICKCNT)                                                                                                                                                                                                                                                                                                                                                                                                                                  | 550                                                                                                                 |

|                      |                                                                                                                                                                                                                                          | Last TG End Pointer (LTGPEND)                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                     |

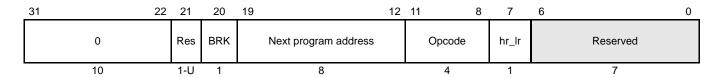

|                      |                                                                                                                                                                                                                                          | TGx Control Registers (TGxCTRL)                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                     |

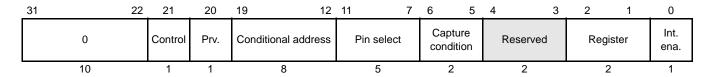

|                      |                                                                                                                                                                                                                                          | DMA Channel Control Register (DMAxCTRL)                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                     |

|                      |                                                                                                                                                                                                                                          | DMAxCOUNT Register (ICOUNT)                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                     |

|                      |                                                                                                                                                                                                                                          | DMA Large Count (DMACNTLEN)                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                     |

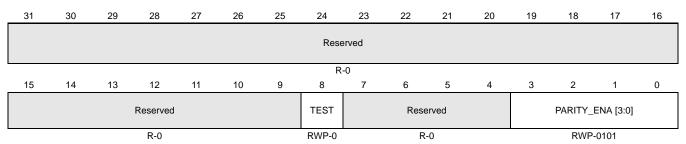

|                      |                                                                                                                                                                                                                                          | Multi-buffer RAM Uncorrectable Parity Error Control Register (UERRCTRL)                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                     |

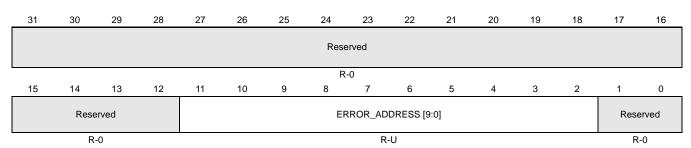

|                      |                                                                                                                                                                                                                                          | Multi-buffer RAM Uncorrectable Parity Error Status Register (UERRSTAT)                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                     |

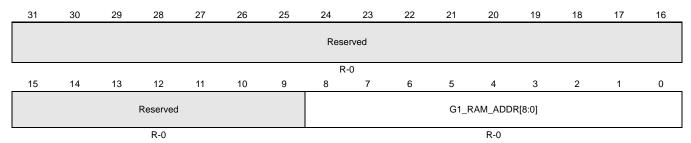

|                      |                                                                                                                                                                                                                                          | RXRAM Uncorrectable Parity Error Address Register (UERRADDR1)                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                     |

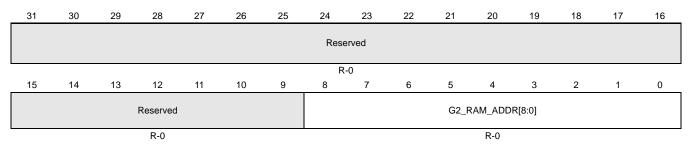

|                      |                                                                                                                                                                                                                                          | TXRAM Uncorrectable Parity Error Address Register (UERRADDR0)                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                     |

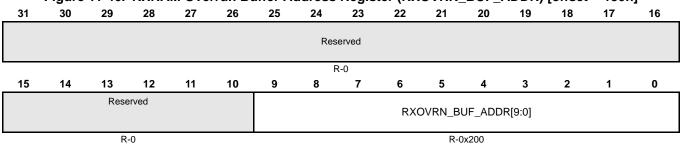

|                      |                                                                                                                                                                                                                                          | RXRAM Overrun Buffer Address Register (RXOVRN_BUF_ADDR)                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                     |

|                      |                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                     |

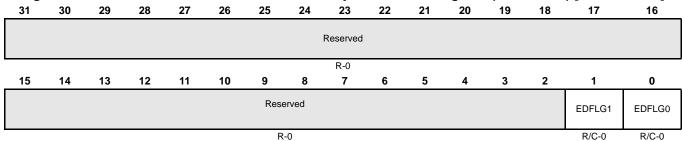

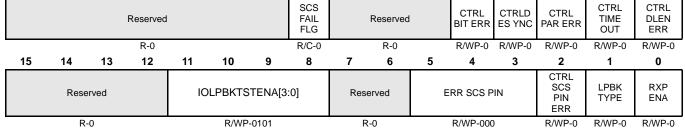

| 44 46                |                                                                                                                                                                                                                                          | I/O-Loopback Test Control Register (IOLPBKTSTCR)                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                     |

| 11.10                |                                                                                                                                                                                                                                          | Buffer RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                     |

|                      |                                                                                                                                                                                                                                          | Multi-Buffer RAM Auto Initialization                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                     |

|                      |                                                                                                                                                                                                                                          | Multi-buffer RAM Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                     |

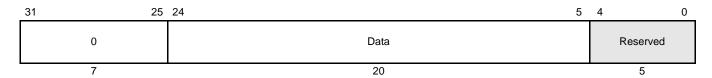

|                      |                                                                                                                                                                                                                                          | Multi-buffer RAM Transmit Data Register                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                     |

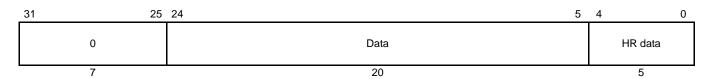

|                      |                                                                                                                                                                                                                                          | Multi-buffer RAM Receive Buffer Register                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                     |

| 11.11                | •                                                                                                                                                                                                                                        | Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                     |

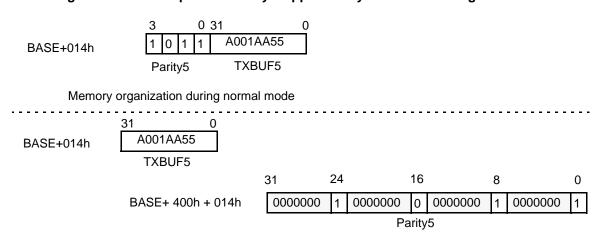

|                      |                                                                                                                                                                                                                                          | Example of Parity Memory Organization                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                     |

| 11.12                |                                                                                                                                                                                                                                          | PI Pin Timing Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                     |

|                      |                                                                                                                                                                                                                                          | Master Mode Timings for SPI/MibSPI                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                     |

|                      |                                                                                                                                                                                                                                          | Slave Mode Timings for SPI/MibSPI                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                     |

|                      | 11 12 3                                                                                                                                                                                                                                  | Timing Parameters of SPI/MibSPI pins in all the modes                                                                                                                                                                                                                                                                                                                                                                                                          | 580                                                                                                                 |

|                      | 11.12.0                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 503                                                                                                                 |

|                      |                                                                                                                                                                                                                                          | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                     |

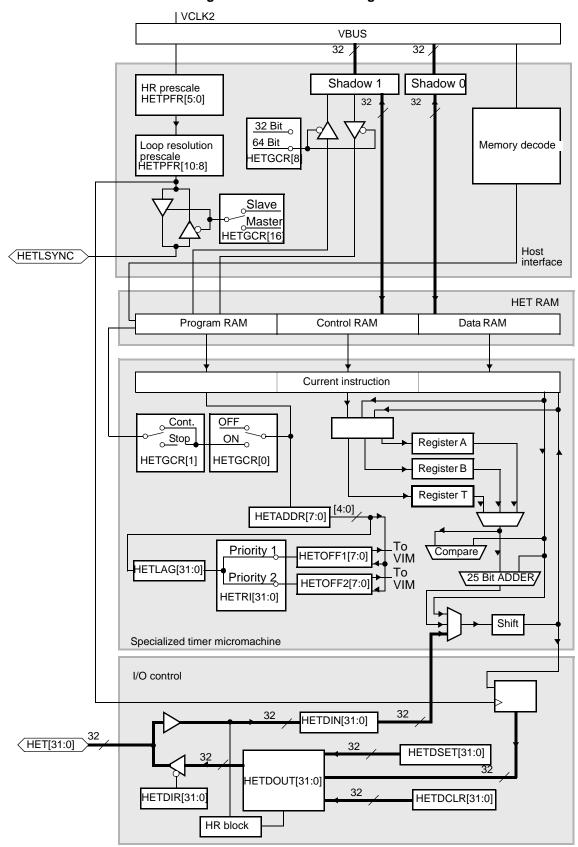

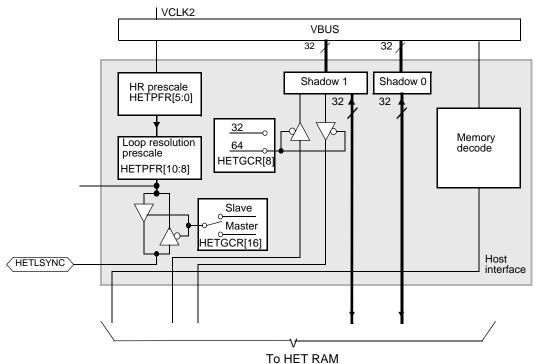

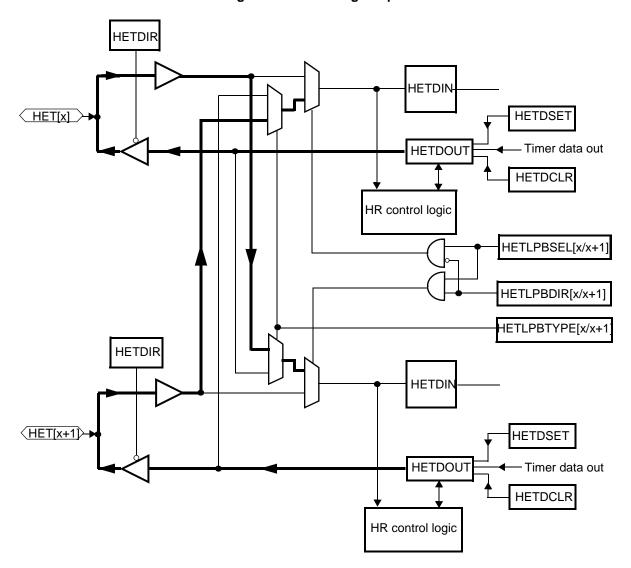

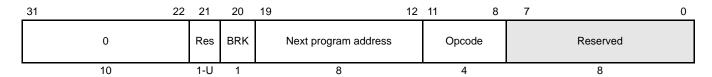

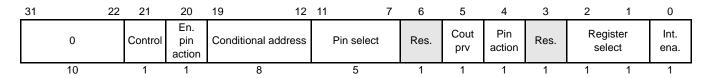

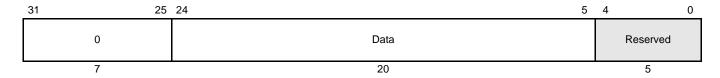

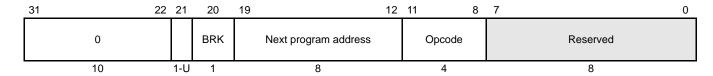

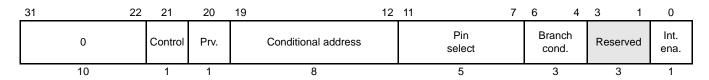

|                      | -End Ti                                                                                                                                                                                                                                  | mer w/Parity (HET) Module                                                                                                                                                                                                                                                                                                                                                                                                                                      | 591                                                                                                                 |

| 12.1                 | -End Ti<br>Featur                                                                                                                                                                                                                        | mer w/Parity (HET) Modulees                                                                                                                                                                                                                                                                                                                                                                                                                                    | 591<br>592                                                                                                          |

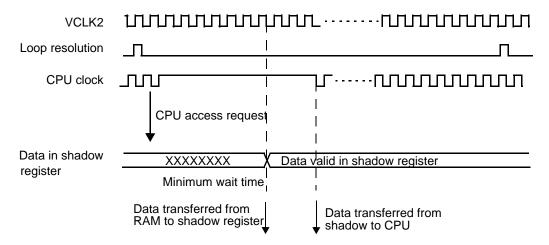

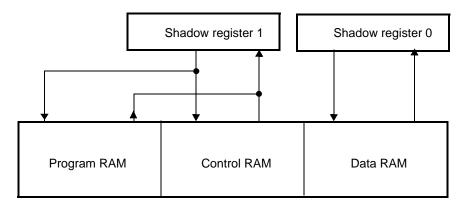

| 12.1                 | -End Ti<br>Featur<br>Overvi                                                                                                                                                                                                              | mer w/Parity (HET) Modulees                                                                                                                                                                                                                                                                                                                                                                                                                                    | 591<br>592<br>593                                                                                                   |

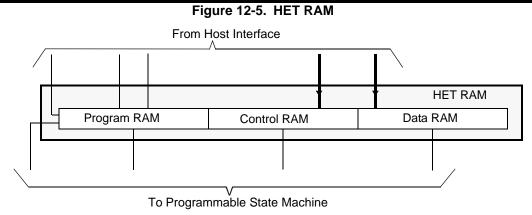

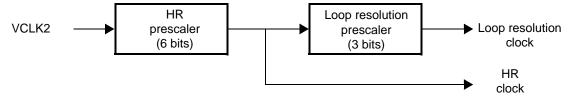

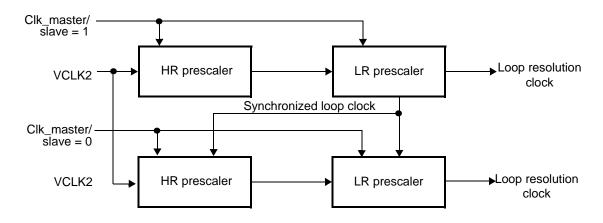

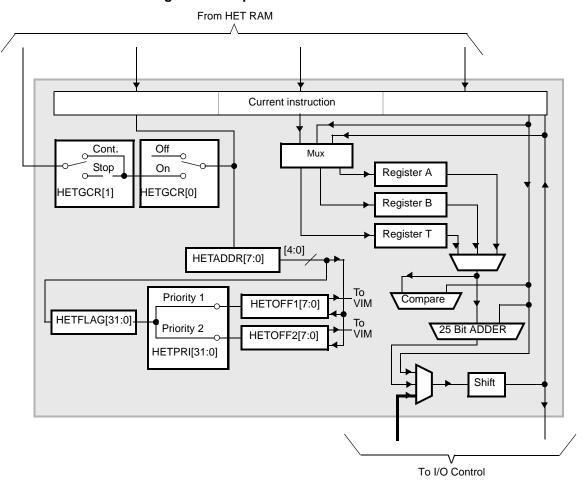

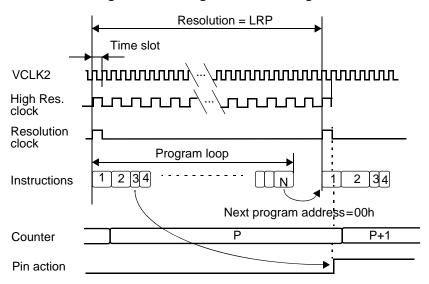

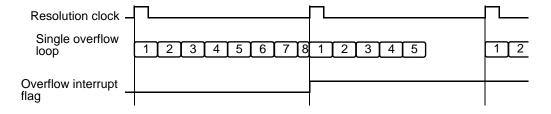

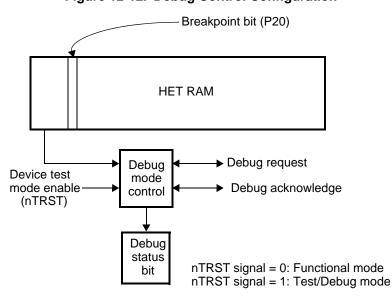

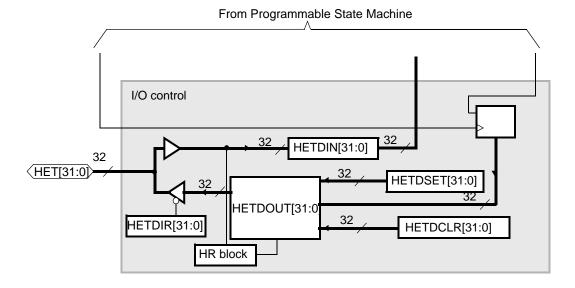

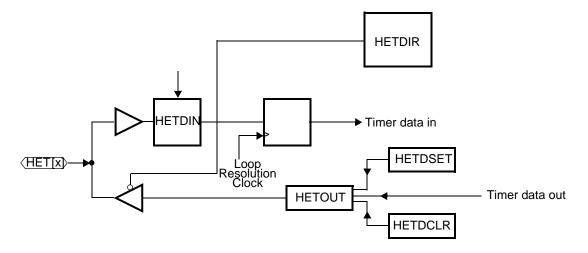

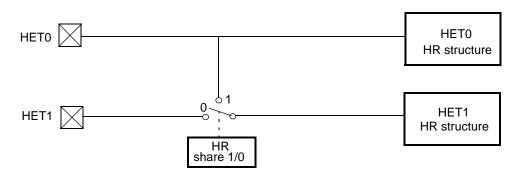

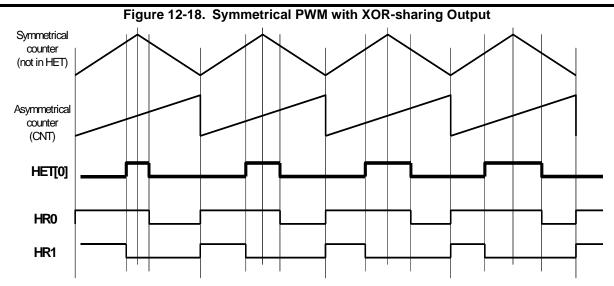

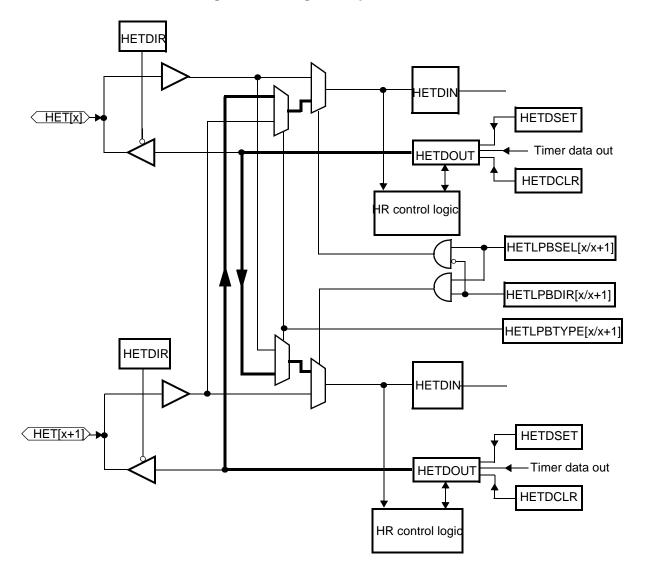

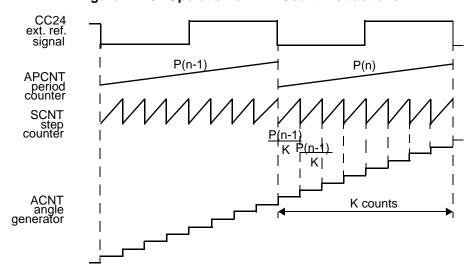

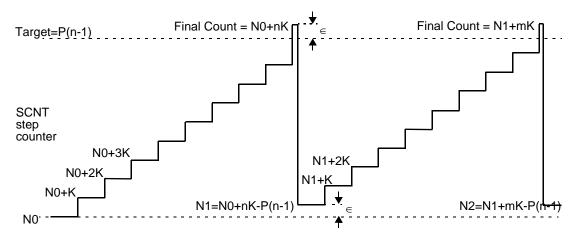

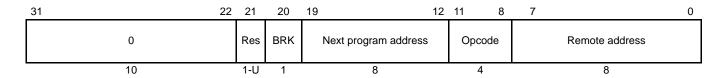

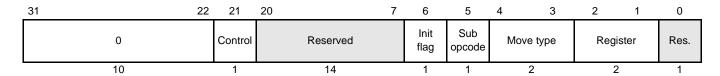

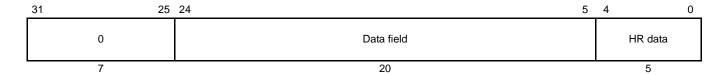

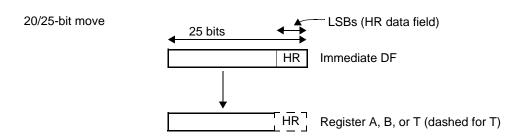

| 12.1                 | -End Ti<br>Featur<br>Overvi<br>12.2.1                                                                                                                                                                                                    | mer w/Parity (HET) Module es ew Timer Module Structure and Execution                                                                                                                                                                                                                                                                                                                                                                                           | <b>591</b><br><b>592</b><br><b>593</b><br>593                                                                       |

| 12.1                 | -End Ti<br>Featur<br>Overvi<br>12.2.1<br>12.2.2                                                                                                                                                                                          | mer w/Parity (HET) Module es ew Timer Module Structure and Execution Major Advantages                                                                                                                                                                                                                                                                                                                                                                          | <b>591</b><br><b>592</b><br><b>593</b><br>594                                                                       |

| 12.1                 | -End Ti<br>Featur<br>Overvi<br>12.2.1<br>12.2.2<br>12.2.3                                                                                                                                                                                | mer w/Parity (HET) Module es ew Timer Module Structure and Execution Major Advantages Performance                                                                                                                                                                                                                                                                                                                                                              | <b>591</b><br><b>592</b><br><b>593</b><br>594<br>594                                                                |

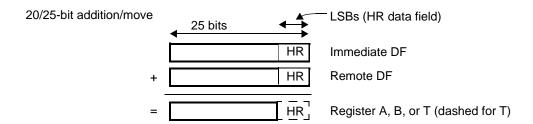

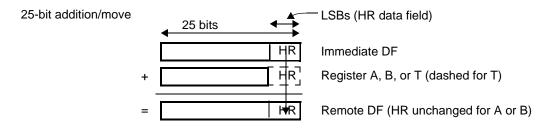

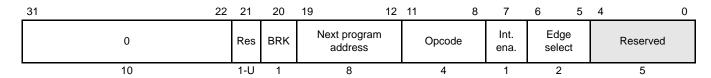

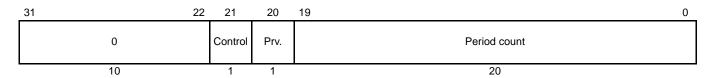

| 12.1                 | -End Ti<br>Featur<br>Overvi<br>12.2.1<br>12.2.2<br>12.2.3<br>12.2.4                                                                                                                                                                      | mer w/Parity (HET) Module es Timer Module Structure and Execution Major Advantages Performance. Instructions Features                                                                                                                                                                                                                                                                                                                                          | <b>591</b><br><b>592</b><br><b>593</b><br>594<br>594                                                                |

| 12.1                 | -End Ti<br>Featur<br>Overvi<br>12.2.1<br>12.2.2<br>12.2.3<br>12.2.4                                                                                                                                                                      | mer w/Parity (HET) Module es ew Timer Module Structure and Execution Major Advantages Performance                                                                                                                                                                                                                                                                                                                                                              | <b>591</b><br><b>592</b><br><b>593</b><br>594<br>594                                                                |

| 12.1                 | -End Ti<br>Featur<br>Overvi<br>12.2.1<br>12.2.2<br>12.2.3<br>12.2.4<br>12.2.5                                                                                                                                                            | mer w/Parity (HET) Module es Timer Module Structure and Execution Major Advantages Performance. Instructions Features                                                                                                                                                                                                                                                                                                                                          | 591<br>593<br>593<br>594<br>594<br>594                                                                              |

| 12.1<br>12.2         | -End Ti<br>Featur<br>Overvi<br>12.2.1<br>12.2.2<br>12.2.3<br>12.2.4<br>12.2.5<br>12.2.6                                                                                                                                                  | mer w/Parity (HET) Module es ew Timer Module Structure and Execution Major Advantages Performance Instructions Features Parity Support.                                                                                                                                                                                                                                                                                                                        | <b>591 593</b> 593 594 594 595                                                                                      |