# TSW6011EVM

This document outlines the basic steps and functions that are required for the proper operation of the TSW6011 evaluation module (EVM) system. The <u>TSW6011EVM</u> is a single RX channel board that can be used to demonstrate a <u>TRF371125</u> integrated direct downconversion receiver interfacing to an <u>ADS5282</u> octal analog-to-digital converter (ADC). This guide helps the user to evaluate the performance of various modes of operation of the TSW6011EVM. Throughout this document, the term *evaluation module* and the abbreviation *EVM* are synonymous with the TSW6011EVM.

### Contents

| 1 Overview |        | ew                                  | 2  |

|------------|--------|-------------------------------------|----|

|            | 1.1    | EVM Frequency Configuration Options | 2  |

|            | 1.2    | TSW6011EVM Block Diagram            | 2  |

|            | 1.3    | Digital Processing Block Diagram    | 3  |

| 2          | Softwa | re Installation                     | 5  |

|            | 2.1    | Installation Instructions           | 5  |

| 3          | EVM T  | est Configuration                   | 5  |

|            | 3.1    | Test Equipment                      | 5  |

|            | 3.2    | Calibration                         | 6  |

| 4          | Board  | Bring Up                            | 6  |

|            | 4.1    | Power Up                            | 6  |

|            | 4.2    | Basic RF Test                       | 7  |

|            | 4.3    | Software Operation                  | 8  |

|            | 4.4    | Device Initialization               | 9  |

|            | 4.5    | Digital Processing Block Functions  | 13 |

| 5          | TR371  | 125 Register Definitions            | 14 |

|            | 5.1    | Register 1                          | 14 |

|            | 5.2    | Register 2                          | 14 |

|            | 5.3    | Register 3                          | 14 |

|            | 5.4    | Register 5                          | 14 |

| Appen      | dix A  |                                     | 15 |

### List of Figures

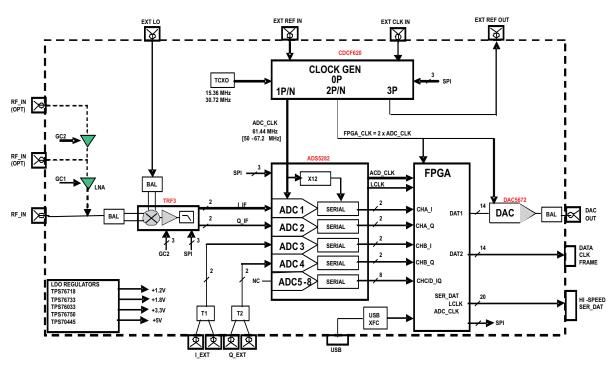

| 1  | TSW6011EVM System Block Diagram                          | 3  |

|----|----------------------------------------------------------|----|

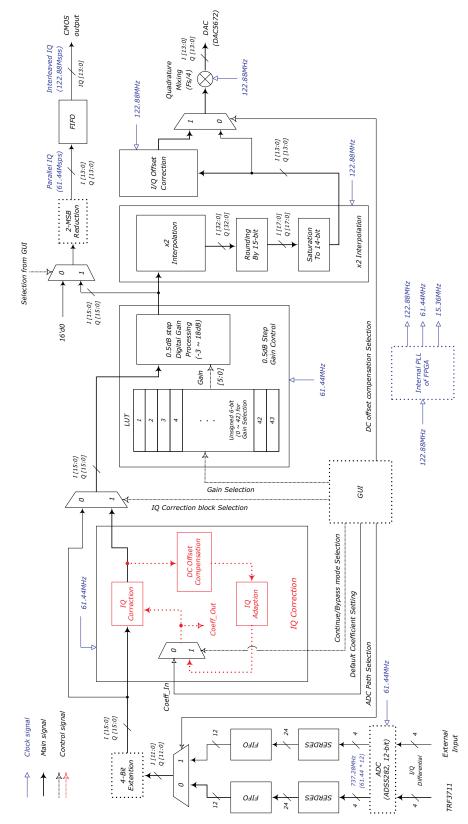

| 2  | FPGA Digital Processing Block Diagram                    | 4  |

| 3  | TSW6011EVM Board Top View                                | 7  |

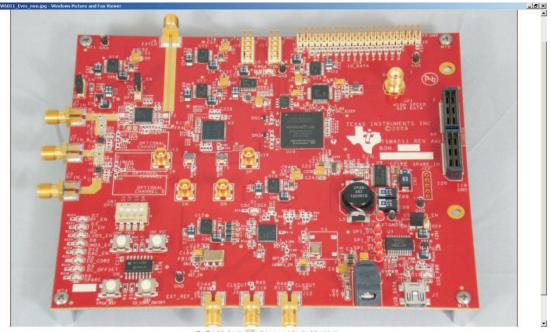

| 4  | TSW6011EVM Software GUI Front Panel                      | 8  |

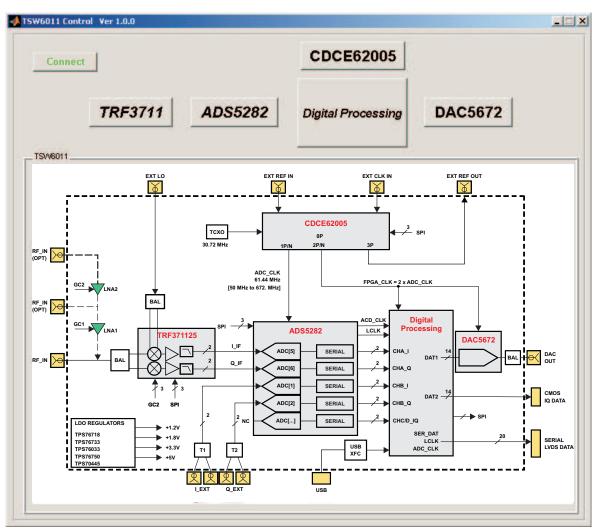

| 5  | GUI Communication Error                                  | 8  |

| 6  | ADS5282 Control Panel                                    | 9  |

| 7  | TR371125 Control Panel                                   | 10 |

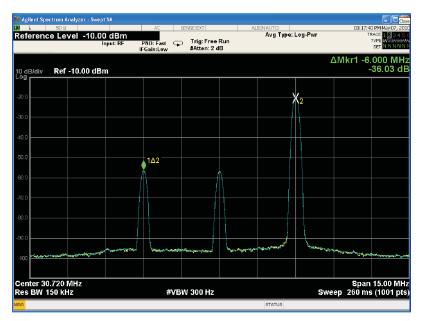

| 8  | Test Tone From DAC5672 Output                            | 11 |

| 9  | Digital Processing Control Panel                         | 12 |

| 10 | Test Tone After IQ Correction and DC Offset Compensation | 13 |

MATLAB is a registered trademark of The MathWorks. All other trademarks are the property of their respective owners.

### 1 Overview

The TSW6011EVM board provides options to send an input RF signal directly to the TR371125 or through one or two low-noise amplifiers (LNAs) by moving two resistors. Additionally, there is an option to drive two of the ADCs with an external source. This source can be single-ended (board default through a transformer) or a differential signal (from a TRF3711xxEVM, for example). There also is an option to bypass the onboard oscillator with an external source. The EVM contains a TRF371125, an ADS5282 for data conversion, an FPGA for digital processing, a CDCE62005 for system clocks, and a DAC5672A to allow for data evaluation using just a spectrum analyzer.

# 1.1 EVM Frequency Configuration Options

The TR371125 device is inherently broadband; however, the radio frequency (RF) and local oscillator (LO) inputs require differential signals which are achieved with the use of RF baluns. This EVM can be configured with a different balun to facilitate operation in the desired band. The default configuration includes 2-GHz baluns for both inputs. Table 1 summarizes the TRF3711xx device frequency options and lists the recommended balun for each device.

| Frequency | Device               | Recommended Balun      |

|-----------|----------------------|------------------------|

| 700 MHz   | TRF371125            | Murata LDB21897M05C    |

| 880 MHz   | TRF371125            | Murata LDB21881M05C    |

| 940 MHz   | TRF371125            | Murata LDB21942M05C    |

| 1740 MHz  | TRF371125, TRF371135 | Murata LDB211G8005C    |

| 1950 MHz  | TRF371125, TRF371135 | Murata LDB211G9005C    |

| 2025 MHz  | TRF371125, TRF371135 | Murata LDB211G9005C    |

| 2500 MHz  | TRF371125, TRF371135 | Murata LDB212G4005C    |

| 3550 MHz  | TRF371125, TRF371135 | Johanson 3600BL14M050E |

| 5400 MHz  | TRF371135            | Johanson 5400BL15B050E |

### Table 1. TRF3711xx Device Frequencies and Recommended Baluns<sup>(1)</sup>

<sup>(1)</sup> There is considerable overlap in the operating frequency range of the TRF3711xx family of devices. Refer to the specific device data sheet and compare performance parameters at the frequencies of interest to select the best part for a particular application.

## 1.2 TSW6011EVM Block Diagram

The TSW6011EVM system block diagram is shown in Figure 1.

Output data can also be analyzed through the use of two other outputs. One output is a connector which provides unprocessed CMOS digital data. This interface has an RC network on every data and clock signal to allow the user to plug an Agilent-style logic analyzer pod directly to the connector.

Another option for capturing data is to use a TSW1200EVM data capture card from Texas Instruments. Connector J21 on the TSW6011 contains unprocessed LVDS data that can be received by a TSW1200 device. The LVDS input connector on the TSW1200 plugs directly into J21 of the TSW6011. This interface can be used to capture data from all four of the ADCs used by this design. The FPGA reformats the output to unsigned binary data, which is required by the TSW1200.

Figure 1. TSW6011EVM System Block Diagram

# 1.3 Digital Processing Block Diagram

The FPGA receives the digital data from the ADCs and converts it from serial to parallel format. The data are then split into two paths. One path converts the data back to unsigned serial data and determines which ADC output to route to the LVDS connector. The other path either bypasses or goes through the I/Q correction block (currently not available). From there, the data is interpolated by 2, processed through a finite impulse response (FIR) filter, then mixed to  $f_s/4$  (30.72 MHz). The output rate of the DAC is at 122.88 MHz, and the ADC sample rate is at 61.44 MHz.

The FPGA allows the user to perform the following functions:

- Select TR371125 or SMA data to be processed

- Enable or disable the LVDS and CMOS data outputs

- Bypass the IQ correction algorithm (algorithm to be added by end of 2Q 2010)

- Program ADC, CDC, and TR371125 registers

- Provide dc offset correction to remove LO image

- Set the LNA gain

- Provide attenuation setting for TRF371125

The FPGA digital processing block diagram is shown in Figure 2.

Figure 2. FPGA Digital Processing Block Diagram

# 2 Software Installation

### 2.1 Installation Instructions

- Step 1. On the CD provided with the EVM kit, copy the *MCRinstaller.exe* and *TSW6011GUI\_setup\_1p00.exe* programs to the local drive on the host PC.

- Step 2. Click on the *MCRinstaller.exe* on the host PC to install the required MATLAB® runtime library.

- Step 3. Next, run the setup file called *TSW6011GUI\_setup\_1p00.exe*. Follow the on-screen instructions.

- Step 4. Once installed, go to the following directory: C:\TSW6011GUI. To start the GUI, double-click on the TSW6011\_control\_panel.exe program.

# 3 EVM Test Configuration

# 3.1 Test Equipment

The following equipment is required to operate the TSW6011:

- 6-VDC power supply (provided)

- Signal generator for input signal (Agilent E4438C or equivalent)

- Signal generator for LO signal

- Spectrum analyzer

- Programming computer

- USB cable (provided)

- RF cables

- (Agilent E4438C or equivalent)

- (Agilent E4440A or equivalent)

### 3.2 Calibration

The RF cables must be good quality because of the high-frequency signals.

- Measure the insertion loss of the RF input cable and use this value to compensate for the desired input power.

- Measure the insertion loss of the LO input cable and use this value to compensate for the desired LO power.

**NOTE:** Approximately 1 dB of insertion loss for the input traces and balun is on the printed-circuit board (PCB).

# 4 Board Bring Up

## 4.1 Power Up

• Plug one end of the provided +6-VDC power supply to a 110-VAC to 120-VAC source and the output to J9. (See the board top-view drawing as shown in Figure 3.)

Verify that the jumpers are configured as follows:

JP1: Pins 1 and 2 (applies power to TR371125 Chip\_EN input pin).

JP2: Pins 2 and 3 (disables LNA power regulator U13).

JP3: Pins 1 and 2 (enables USB to parallel interface device power regulator U21).

SJP1: Pins 2 and 3 (selects SMA J1 to be the RF input source to the TRF371125).

SJP2: Pins 1 and 2 (selects LNA U2 output).

SJP3: Open (used to select source for LNA U2 GAIN\_SEL input).

SJP4: Pins 2 and 3 (enables primary reference source Y2 for the CDCE62005).

SJP5: Open. (used to select source for LNA U8 GAIN\_SEL input).

SJP6: Pins 2 and 3 (selects CDCE62005 power down source).

SJP7: Pins 1 and 2 (disables CDCE62005 AUX\_IN source Y4).

SJP8: Pins 1 and 2 (selects DAC5672 SLEEP input source).

SJP9: Pins 1 and 2 (selects USB to parallel interface device power source).

SJP10: Pins 2 and 3 (selects DAC5672 input clock source).

- Note that the following LE's are now illuminated:

- D6: +6V power present

- D1: CDC is locked to reference source

- D10: USB powered up

- D11: FPGA is configured

- D7: TR371125 enabled

- D3: DAC input data enabled

- D12: DAC enabled

(This is the board default power-up mode.)

- Plug the USB cable into the host PC and connector J7 on the TSW6011.

- When plugging in the USB cable for the first time, the user is be prompted to install the USB drivers.

- When a pop-up screen opens, select *Continue Downloading*.

- Follow the on-screen instructions to install the USB drivers.

- If needed, the USB drivers can be accessed in the following directory: C:\TSW6011GUI\FTD245\_Drivers\

### 4.2 Basic RF Test

Follow these steps to perform a basic RF test.

- Step 1. Inject a LO signal at J4 at a frequency of 2150 MHz at 0 dBm. Compensate for RF cable losses, including about 1 dB for input balun and transmission line losses.

- Step 2. Since the board default configuration bypasses the two LNAs, inject an RF signal at J1 at 2153 MHz at –15 dBm. Compensate for cable loss, including about 1 dB for input transmission line losses and balun.

- Step 3. Connect a spectrum analyzer to J6.

- Step 4. Set up the spectrum analyzer as follows:

- Set span to 20 MHz

- Set center frequency to 30.72 MHz

- Set reference level to -10 dBm

- Set attenuation to 15 dB

- Set sweep time to 2.5 ms

- Set RBW to 300 kHz

- Set VBW to 1 MHz

0 0 × 4 7 × 4 × 4 6 9

Figure 3. TSW6011EVM Board Top View

7

Board Bring Up

### 4.3 Software Operation

When the GUI first starts, the front control panel appears as shown in Figure 4.

Figure 4. TSW6011EVM Software GUI Front Panel

To enable the GUI, the user must click on the button labeled **Connect** in the upper left-hand corner. If communication between the GUI and TSW6011 is successful, the button changes to display **Disconnect**. Clicking on this button again disconnects the GUI, and the button displays **Connect** once more. If there is a problem with the connection, an error message appears, as shown in Figure 5.

Figure 5. GUI Communication Error

If this message appears, make sure the USB cable is installed, the USB drivers are installed, and verify that the board is powered up. If this problem persists, unplug the USB cable from the EVM, then reconnect it. If this procedure does not correct the problem, close the GUI and reboot the host computer.

### 4.4 Device Initialization

Click on the GUI button labeled ADS5282. This opens the ADS5282 control panel as shown in Figure 6.

| ADC Control |            |                          | _ 🗆 X |

|-------------|------------|--------------------------|-------|

| ADS5282     | Power Down | Low Noise<br>Suppression |       |

| ADC Channe  | 11 🗖       |                          |       |

| ADC Channe  | 12 🗖       |                          |       |

|             |            |                          | ī     |

| ADC Channel | 5 🗖        |                          |       |

| ADC Channel | 6 🗆        |                          |       |

|             |            |                          |       |

|             | Reset ADC  |                          |       |

Figure 6. ADS5282 Control Panel

- When the control panel opens, the ADS5282 is initialized by the software automatically. The TSW6011 routes external signals from the SMAs to ADC channels 1 and 2. The TR371125 outputs are routed to channels 5 and 6. Channels 3, 4, 7, and 8 are not used. The following sequence is performed every time this GUI window is opened:

- Reset the device.

- Power up ADC Channels 1, 2, 5, and 6. Power down ADC channels 3, 4, 7, and 8.

- Set the serial output stream to send MSB first.

- Set the data format to twos complement.

- Set the input clock to differential mode.

- To power down any of the four channels, click on the respective box in the *Power Down* column.

- To activate the respective channel Low Noise Suppression, click on the box.

- To issue a device reset, click on the **Reset ADC** button.

- Click on the X in the upper right-hand corner to close the panel.

Click on the TRF3711 button of the GUI to open the TR371125 control panel as shown in Figure 7.

| 📣 IQ Demodulator Control                                                               | _ 🗆 X                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BB Gain 15<br>LPF Adj 128<br>~20MHz                                                    | Auto Cal IV IDAC 128<br>EN Auto Cal IV Q DAC 128<br>Cal Clk Sel Int IV 128                                                                                                                            |

| En FastGain<br>GainSelect X1<br>3dB Attn<br>Det Filter (kHz) 1                         | Osc Freq (kHz) × 900<br>Clk Div × 1024<br>IDet (uA) × 50                                                                                                                                              |

| RF Pwd I<br>BUF Pwd I<br>BB Pwd I<br>Osc Test I<br>DC OFF DIG Pwd I<br>Filter Bypass I | ILoad A $\stackrel{*}{\downarrow}$ 0<br>ILoad B $\stackrel{*}{\downarrow}$ 0<br>QLoad A $\stackrel{*}{\downarrow}$ 0<br>QLoad B $\stackrel{*}{\downarrow}$ 0<br>FLT Ctrl $\stackrel{*}{\downarrow}$ 1 |

| REGISTER 1 0700FC89 REGIS<br>REGISTER 2 7B20200A REGIS                                 |                                                                                                                                                                                                       |

Figure 7. TR371125 Control Panel

- When the control panel opens, the TR371125 is initialized by the software automatically. The default settings are those shown in the control panel when it opens. Every time this panel is opened, the default values are loaded. This process is reported by the message in red: DEFAULTS RE-LOADED (as shown in Figure 7).

- Click on the **BB Gain** field and set the gain to 5.

- Click the Filter Bypass checkbox to bypass the TR371125 LPF internal filter.

Figure 8. Test Tone From DAC5672 Output

• Click on the GUI button labeled **Digital Processing**. This opens a control panel that is shown in Figure 9.

| 4 | 🛃 Digital Processing Control               |                                |                               |  |  |

|---|--------------------------------------------|--------------------------------|-------------------------------|--|--|

|   | -                                          | cessing Control<br>are Version |                               |  |  |

|   | Channel Select                             | DAC Data Enable<br>DAC Enable  | <ul><li>✓</li><li>✓</li></ul> |  |  |

|   | LNA "A" Enable                             | CMOS Enable                    |                               |  |  |

|   | LNA "B" Enable 📃                           | LVDS Enable                    |                               |  |  |

| [ | Digital Gain (0.5dB step)<br>(-3dB ~ 18dB) | CDC Ext Ref                    |                               |  |  |

|   | OFFSET Compensation                        | IQ Correction Enable           |                               |  |  |

|   |                                            | IQ Correction Tap Shift Avg    | 13                            |  |  |

Figure 9. Digital Processing Control Panel

• The values selected in the control panel are the default values loaded at power up. The controls are defined as follows:

| Firmware Version:       | Displays the version of the firmware loaded in the FPGA                                                                                                                                                                                                                                                                                          |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Channel select:         | When not selected, the output of the TR371125 is used by the digital processing path and sent to the DAC. When selected, the external SMA inputs are used by the digital processing path.                                                                                                                                                        |

| LNA "A" Enable:         | When selected, places LNA U2 into low gain mode (-3 dB typ). When not selected, the LNA is in high gain mode (14.5 dB typ).                                                                                                                                                                                                                      |

| LNA "B" Enable:         | When selected, places LNA U8 into low gain mode (-3 dB typ). When not selected, the LNA is in high gain mode (14.5 dB typ).                                                                                                                                                                                                                      |

| DAC Data Enable:        | When selected, enables data through digital processing path to be routed to the DAC. When disabled, no data are routed to the DAC.                                                                                                                                                                                                               |

| DAC Enable:             | When selected, the DAC is enabled. When disabled, the DAC is in sleep mode.                                                                                                                                                                                                                                                                      |

| CMOS Enable:            | When selected, enables unprocessed data to be routed to the CMOS data connectors. When disabled, no data are routed to the connectors.                                                                                                                                                                                                           |

| LVDS Enable:            | When selected, enables unprocessed data to be routed to the LVDS connector.<br>When disabled, no data are routed to the connector.                                                                                                                                                                                                               |

| CDC Ext Ref:            | Disabled. Currently not used.                                                                                                                                                                                                                                                                                                                    |

| IQ Correction Enable:   | When selected, IQ Correction is enabled. When disabled, IQ Correction block is bypassed.                                                                                                                                                                                                                                                         |

|                         | Digital gain can be controlled in 0.5-dB steps from –3 dB to 18 dB. For better signal quality such as EVM improvement, users need to increase the digital dynamic range of the input signal to the DAC. Default value is '0,' and this value must be sent to the FPGA on the TSW6011 by pressing "Enter" from the user's personal computer (PC). |

|                         | When selected, the DC offset compensation is enabled. When disabled, the DC offset compensation block is bypassed.                                                                                                                                                                                                                               |

| IQ Correction Tap Shift | Initial value is 13, which is coarse adaption. Users can choose the value of 18, which slows the adaption algorithm.                                                                                                                                                                                                                             |

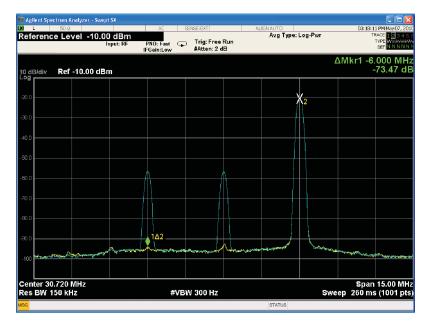

Figure 10. Test Tone After IQ Correction and DC Offset Compensation

The buttons labeled **CDCE62005** and **DAC5672** do not have control panel associations. The CDC is loaded at power up, and no internal registers are within the DAC5672. Contact TI if settings other than the default are required for the CDCE62005.

# 4.5 Digital Processing Block Functions

The FPGA receives the digital data from the ADC and converts it from serial to parallel format. The data then are split into two paths. One path converts the data back to unsigned serial data and determines which ADC output to route to the LVDS connector. The other path either bypasses or goes through the IQ Correction block. After IQ Correction processing, the data are interpolated by 2, processed through a finite impulse response (FIR) and then mixed to fs/4 (30.72 MHz). DAC sample rate is 122.88 MHz, and ADC sample rate is 61.44 MHz.

The FPGA allows the user to perform the following functions.

- Select the processing path between TRF3711 and SMA

- Enable or disable the LVDS and CMOS data outputs

- Enable or disable the IQ Correction algorithm

- Digital gain control by 0.5dB step

- Program ADC, PLL, and TRF371125 registers

- Enable or disable the DC offset compensation algorithm

- Set the LNA gain

- Provide attenuation setting for TRF371125

## 5 TR371125 Register Definitions

### 5.1 Register 1

- BB Gain: The PGA (Programmable Gain Amplifier) setting; range is 0 to 24.

- LPFAdj: Sets the bandwidth of the BB filters. Setting 0 is maximum bandwidth (~29.6 MHz); setting 254 is minimum

(~ 1.27 MHz). See the product data sheet (SLWS219) for comprehensive curves.

- EN\_FastGain: Enables the fast gain option to adjust PGA gain with external bits.

- Gain Select: Selects whether each bit in the fast gain control is either 1 dB or 2 dB.

- 3 dB Attn: Engages the 3-dB attenuator at the baseband output.

- Det Filter: Selects the internal detector filter used in dc offset calibration.

- RF Pwd: Enables SW controlled power down of RF stages inside device.

- BUF Pwd: Enables power down on test buffer for mixer output; default is powered down.

- Osc\_Test: Enables dc offset oscillator to the Readback pin.

- DC\_Off\_DIG Enables SW controlled power down of dc offset correction circuitry. Pwd:

## 5.2 Register 2

- Auto Cal: Manual mode allows the dc offset DACs to be user configurable; Auto mode uses the internally stored values.

- En Auto Cal: When toggled, an Auto Cal is initiated. Note, Auto Cal must be in Auto mode.

- I/Q DAC: Shows the setting of the dc offset I and Q DAC when in Manual mode; range is 0 to 255

- Cal Clk Sel: Toggle between using an externally supplied SPI clock or internal oscillator clock.

Osc. Freq: Selects the oscillator frequency for the internal clock.

- Clk Div: Sets the clock divider if the control clocks need to be slowed down. Value chosen in conjunction with Det Filter setting for optimal averaging.

- I Det: Selects the resolution of the I and Q DAC.

# 5.3 Register 3

- I/QLoadA/B: Selects the mixer gain for the differential BB paths. Typically, these registers do not need to be modified, but minor I/Q amplitude adjustments are allowed.

- Filter Ctrl: Trims the peaking response of the BB LPF response.

- Filter Bypass Engages the bypass feature of the BB LPF.

## 5.4 Register 5

- Mix GM Trim No adjustment of this register required

- Mix LO Trim No adjustment of this register required

- LO Trim No adjustment of this register required

- Mix Buff Trim No adjustment of this register required

- Filter Trim No adjustment of this register required

- Out Buff Trim No adjustment of this register required

The hex values in the Register # boxes are the actual values loaded into the TRF371125.

# Appendix A

# A.1 LED Definitions

D1: CDC locked to reference D6: +6V present D10: USB device powered up D11: FPGA configured D7: TR371125 enabled D3: DAC input data enabled D12: DAC powered up D4: DC Offset compensation enabled with blinking D5: IQ Correction enabled with blinking

## A.2 Connector Descriptions

| Designator | Description                                                     |

|------------|-----------------------------------------------------------------|

| J1         | RF input. Bypasses both LNAs.                                   |

| J2         | RF input to LNA #2. Bypasses LNA #1.                            |

| J3         | RF input to LNA #1.                                             |

| J4         | TR371125 LO input source                                        |

| J13        | ADC #1 analog input. Positive analog input when T4 is bypassed. |

| J14        | ADC #1 negative analog input when T4 is bypassed.               |

| J16        | ADC #2 analog input. Positive analog input when T5 is bypassed. |

| J17        | ADC #2 negative analog input when T5 is bypassed.               |

| J8         | External reference for CDCE62005.                               |

| J5         | Spare output from CDCE62005                                     |

| J12        | Spare output from CDCE62005                                     |

| J6         | DAC5672 output.                                                 |

| J21        | LVDS outputs. Mates with TSW1200 LVDS input connector.          |

| J19        | CMOS output data.                                               |

| J22        | Test connector.                                                 |

| J9         | +6-VDC input power connector.                                   |

| J7         | USB connector.                                                  |

| J18        | FPGA JTAG connector.                                            |

| J15        | FPGA PROM programming connector.                                |

# A.3 Jumper and Switch Descriptions

| Designator | Description                                                                                                                | Default Position        |

|------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------|

| SJP3       | Selects gain for LNA #1. Logic high sets typ gain to 14.5 dB. Logic low sets typ gain to -3.0 dB.                          | FPGA control (Low Gain) |

| SJP5       | Selects gain for LNA #2. Logic high sets typ gain to 14.5 dB. Logic low sets typ gain to $-3.0$ dB.                        | FPGA control (Low Gain) |

| SJP2       | LNA #1 bypass. Jumper 1-2 to use LNA #1, 2-3 to bypass LNA #1.                                                             | 1-2                     |

| SJP1       | LNA #2 bypass. Jumper 1-2 to use LNA #1, 2-3 to bypass LNA #1.                                                             | 2-3                     |

| JP1        | TR371125 enable. Installed to enable device.                                                                               | 1-2                     |

| SJP7       | CDCE62005 AUX oscillator power. Set to 1-2 to power down oscillator, 2-3 to power up.                                      | 1-2                     |

| SJP4       | CDCE62005 primary reference enable. Set to 1-2 to power down oscillator, 2-3 to power up.                                  | 2-3                     |

| SJP6       | CDCE62005 power down. Set to 2-3 to enable CDC, set to 1-2 for FPGA control of power down mode.                            | 2-3                     |

| SJP10      | DAC5672 clock source. Set to 1-2 for CDCE62005, set to 2-3 for FPGA source.                                                | 2-3                     |

| SJP8       | DAC5672 sleep mode. Set to 1-2 for FPGA control, set to 2-3 to keep device active.                                         | 1-2                     |

| JP2        | LNA power enable. Set to 1-2 to enable LNA regulator, 2-3 to disable regulator.                                            | 2-3                     |

| JP3        | USB device power regulator enable. Set to 1-2 to enable regulator, 2-3 to disable.                                         | 1-2                     |

| SJP9       | USB device power select. Set to 1-2 to power device from onboard regulator, set to 2-3 to power device from USB connector. | 1-2                     |

| SW1        | Spare dip switches. Currently not used.                                                                                    |                         |

| SW3        | Turn I/Q correction on/off. Currently not used                                                                             |                         |

| SW4        | Not Used                                                                                                                   |                         |

| SW5        | FPGA Reset. Reset all FPGA registers.                                                                                      |                         |

| SW6        | CDC Reset                                                                                                                  |                         |

# **REVISION HISTORY**

| Cł | Changes from Original (February, 2010) to A Revision                  |     |  |

|----|-----------------------------------------------------------------------|-----|--|

| •  | Changed device name in document title to correspond with product name |     |  |

| •  | Revised Overview section                                              | . 2 |  |

| •  | Added Table 1                                                         | . 2 |  |

| •  | Updated Figure 1 for clarity                                          | . 3 |  |

| •  | Updated Figure 4 for clarity                                          | . 8 |  |

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

### Changes from A Revision (March 2010) to B Revision

#### Page

| • | Deleted TRF311 Att and IQ Offset values on page 9 | 12 |

|---|---------------------------------------------------|----|

| • | Added 4 values in the control panel               | 12 |

| • | Deleted Section 6. Optional Configurations        | 15 |

| • | Deleted LED definitions, D8, D2, D9               | 15 |

| • | Changed D4 definition                             | 15 |

| • | Added D5: IQ correction enabled with blinking     | 15 |

|   |                                                   |    |

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

### **Evaluation Board/Kit Important Notice**

Texas Instruments (TI) provides the enclosed product(s) under the following conditions:

This evaluation board/kit is intended for use for ENGINEERING DEVELOPMENT, DEMONSTRATION, OR EVALUATION PURPOSES ONLY and is not considered by TI to be a finished end-product fit for general consumer use. Persons handling the product(s) must have electronics training and observe good engineering practice standards. As such, the goods being provided are not intended to be complete in terms of required design-, marketing-, and/or manufacturing-related protective considerations, including product safety and environmental measures typically found in end products that incorporate such semiconductor components or circuit boards. This evaluation board/kit does not fall within the scope of the European Union directives regarding electromagnetic compatibility, restricted substances (RoHS), recycling (WEEE), FCC, CE or UL, and therefore may not meet the technical requirements of these directives.

Should this evaluation board/kit not meet the specifications indicated in the User's Guide, the board/kit may be returned within 30 days from the date of delivery for a full refund. THE FOREGOING WARRANTY IS THE EXCLUSIVE WARRANTY MADE BY SELLER TO BUYER AND IS IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED, IMPLIED, OR STATUTORY, INCLUDING ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE.

The user assumes all responsibility and liability for proper and safe handling of the goods. Further, the user indemnifies TI from all claims arising from the handling or use of the goods. Due to the open construction of the product, it is the user's responsibility to take any and all appropriate precautions with regard to electrostatic discharge.

EXCEPT TO THE EXTENT OF THE INDEMNITY SET FORTH ABOVE, NEITHER PARTY SHALL BE LIABLE TO THE OTHER FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES.

TI currently deals with a variety of customers for products, and therefore our arrangement with the user is not exclusive.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein.

Please read the User's Guide and, specifically, the Warnings and Restrictions notice in the User's Guide prior to handling the product. This notice contains important safety information about temperatures and voltages. For additional information on TI's environmental and/or safety programs, please contact the TI application engineer or visit www.ti.com/esh.

No license is granted under any patent right or other intellectual property right of TI covering or relating to any machine, process, or combination in which such TI products or services might be or are used.

### **FCC Warning**

This evaluation board/kit is intended for use for **ENGINEERING DEVELOPMENT, DEMONSTRATION, OR EVALUATION PURPOSES ONLY** and is not considered by TI to be a finished end-product fit for general consumer use. It generates, uses, and can radiate radio frequency energy and has not been tested for compliance with the limits of computing devices pursuant to part 15 of FCC rules, which are designed to provide reasonable protection against radio frequency interference. Operation of this equipment in other environments may cause interference with radio communications, in which case the user at his own expense will be required to take whatever measures may be required to correct this interference.

#### **EVM Warnings and Restrictions**

It is important to operate this EVM within the input voltage range of 6 VDC to 6.5 V DC and the output voltage range of 3.3 VDC to 3.5 VDC.

Exceeding the specified input range may cause unexpected operation and/or irreversible damage to the EVM. If there are questions concerning the input range, please contact a TI field representative prior to connecting the input power.

Applying loads outside of the specified output range may result in unintended operation and/or possible permanent damage to the EVM. Please consult the EVM User's Guide prior to connecting any load to the EVM output. If there is uncertainty as to the load specification, please contact a TI field representative.

During normal operation, some circuit components may have case temperatures greater than +85°C. The EVM is designed to operate properly with certain components above +85°C as long as the input and output ranges are maintained. These components include but are not limited to linear regulators, switching transistors, pass transistors, and current sense resistors. These types of devices can be identified using the EVM schematic located in the EVM User's Guide. When placing measurement probes near these devices during operation, please be aware that these devices may be very warm to the touch.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2010, Texas Instruments Incorporated

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications                  |                                   |

|-----------------------------|------------------------|-------------------------------|-----------------------------------|

| Amplifiers                  | amplifier.ti.com       | Audio                         | www.ti.com/audio                  |

| Data Converters             | dataconverter.ti.com   | Automotive                    | www.ti.com/automotive             |

| DLP® Products               | www.dlp.com            | Communications and<br>Telecom | www.ti.com/communications         |

| DSP                         | dsp.ti.com             | Computers and<br>Peripherals  | www.ti.com/computers              |

| Clocks and Timers           | www.ti.com/clocks      | Consumer Electronics          | www.ti.com/consumer-apps          |

| Interface                   | interface.ti.com       | Energy                        | www.ti.com/energy                 |

| Logic                       | logic.ti.com           | Industrial                    | www.ti.com/industrial             |

| Power Mgmt                  | power.ti.com           | Medical                       | www.ti.com/medical                |

| Microcontrollers            | microcontroller.ti.com | Security                      | www.ti.com/security               |

| RFID                        | www.ti-rfid.com        | Space, Avionics & Defense     | www.ti.com/space-avionics-defense |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        | Video and Imaging             | www.ti.com/video                  |

|                             |                        | Wireless                      | www.ti.com/wireless-apps          |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2010, Texas Instruments Incorporated