**PGA280**

SBOS487A – JUNE 2009 – REVISED SEPTEMBER 2009

# Zerø-Drift, High-Voltage, Programmable Gain INSTRUMENTATION AMPLIFIER

Check for Samples: PGA280

# FEATURES

www.ti.com

- WIDE INPUT RANGE: ±15.5V at ±18V SUPPLY

- BINARY GAIN STEPS: 128V/V to 1/8V/V

- ADDITIONAL SCALING FACTOR: 1V/V and 1%V/V

- LOW OFFSET VOLTAGE: 3µV at G = 128

- NEAR-ZERO LONG-TERM DRIFT OF OFFSET VOLTAGE

- NEAR-ZERO GAIN DRIFT: 0.5ppm/°C

- EXCELLENT LINEARITY: 1.5ppm

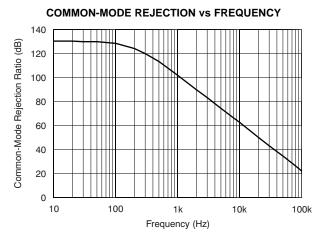

- EXCELLENT CMRR: 140dB

- HIGH INPUT IMPEDANCE

- VERY LOW 1/f NOISE

- DIFFERENTIAL SIGNAL OUTPUT

- OVERLOAD DETECTION

- INPUT CONFIGURATION SWITCH MATRIX

- WIRE BREAK TEST CURRENT

- EXPANDABLE SPI™ WITH CHECKSUM

- GENERAL-PURPOSE I/O PORT

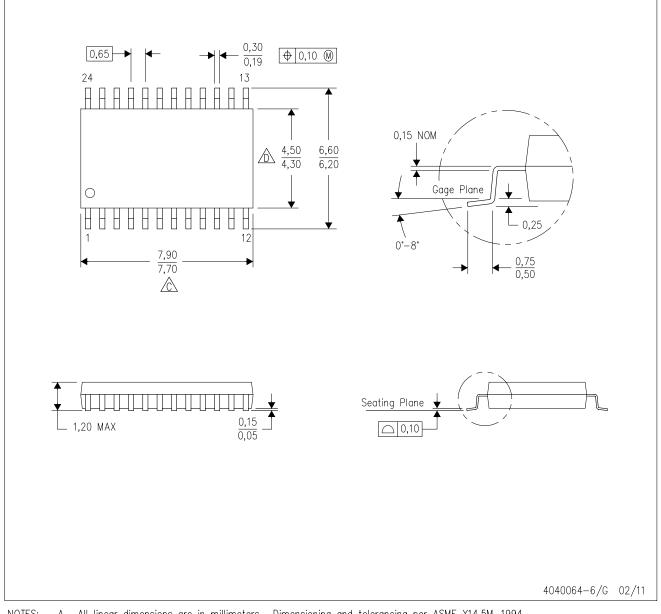

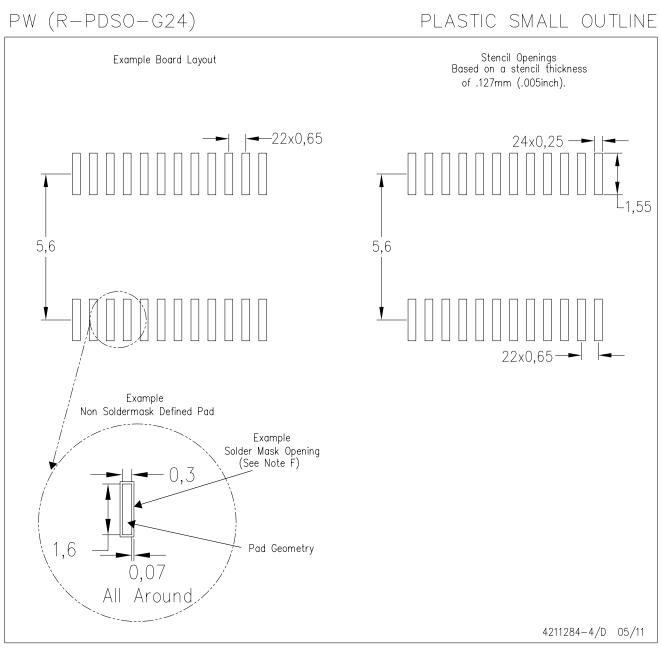

- TSSOP-24 PACKAGE

# **APPLICATIONS**

- HIGH-PRECISION SIGNAL INSTRUMENTATION

- MULTIPLEXED DATA ACQUISITION

- HIGH-VOLTAGE ANALOG INPUT AMPLIFIER

- UNIVERSAL INDUSTRIAL ANALOG INPUT

# DESCRIPTION

The PGA280 is a high-precision instrumentation amplifier with digitally-controllable gain and signal integrity test capability. This device offers low offset voltage, near-zero offset and gain drift, excellent linearity, and nearly no 1/f noise with superior common-mode and supply rejection to support high-resolution precision measurement. The 36V supply capability and wide, high-impedance input range comply with requirements for universal signal measurement.

Special circuitry prevents inrush currents from multiplexer (MUX) switching. In addition, the input switch matrix enables easy reconfiguration and system-level diagnostics—overload conditions are indicated.

The configurable general-purpose input/output (GPIO) offers several control and communication features. The SPI can be expanded to communicate with more devices, supporting isolation with only four ISO couplers. The PGA280 is available in a TSSOP-24 package and is specified from  $-40^{\circ}$ C to  $+105^{\circ}$ C.

#### **RELATED PRODUCTS**

| FEATURES                                                                  | PRODUCT |

|---------------------------------------------------------------------------|---------|

| 23-bit resolution, $\Delta\Sigma$ analog-to-digital converter             | ADS1259 |

| Chopper-stabilized instrumentation amplifier,<br>RR I/O, 5V single-supply | INA333  |

| High-precision PGA, G = 1, 10, 100, 1000                                  | PGA204  |

| High-precision PGA, JFET Input, G = 1, 2, 4, 8                            | PGA206  |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. SPI is a trademark of Motorola.

All other trademarks are the property of their respective owners.

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

|         | PACKAGE INFORMATION <sup>(1)</sup> |                       |                    |  |  |  |  |  |  |  |

|---------|------------------------------------|-----------------------|--------------------|--|--|--|--|--|--|--|

| PRODUCT | PACKAGE-LEAD                       | PACKAGE<br>DESIGNATOR | PACKAGE<br>MARKING |  |  |  |  |  |  |  |

| PGA280  | TSSOP-24                           | PW                    | PGA280A            |  |  |  |  |  |  |  |

(1) For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

# ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

Over operating free-air temperature range, unless otherwise noted.

|                    |                                | PGA280                 | UNIT |

|--------------------|--------------------------------|------------------------|------|

| Supply Voltogo     | VSN to VSP                     | 40                     | V    |

| Supply Voltage     | VSON to VSOP, and DGND to DVDD | 6                      | V    |

| Signal Input Termi | inals, Voltage <sup>(2)</sup>  | VSN – 0.5 to VSP + 0.5 | V    |

| Signal Input Termi | inals, Current <sup>(2)</sup>  | ±10                    | mA   |

| Output Short-Circu | uit <sup>(3)</sup>             | Continuous             |      |

| Operating Temper   | rature                         | -55 to +140            | °C   |

| Storage Temperat   | ure                            | -65 to +150            | °C   |

| Junction Tempera   | ture                           | +150                   | °C   |

| ESD Ratings        | Human Body Model (HBM)         | 2000                   | V    |

(1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

(2) Terminals are diode-clamped to the power-supply (VON and VOP) rails. Signals that can swing more than 0.5V beyond the supply rails must be current-limited.

(3) Short-circuit to VSON or VSOP, respectively, DGND or DVDD.

www.ti.com

# **ELECTRICAL CHARACTERISTICS**

**Boldface** limits apply over the specified temperature range,  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ . At  $T_A = +25^{\circ}C$ , VSP = +15V, VSN = -15V, VSON = 0V, VSOP = 5V, DVDD = +3V, DGND = 0V,  $R_L = 2.5k\Omega$  to VSOP/2 = VOCM, G = 1V/V, using internal clock, BUF inactive,  $V_{CM} = 0V$ , and differential input and output, unless otherwise noted.

|                                       |                      |                                                |             | PGA280 |             |                  |

|---------------------------------------|----------------------|------------------------------------------------|-------------|--------|-------------|------------------|

| PARAMETER                             |                      | CONDITIONS                                     | MIN         | TYP    | MAX         | UNIT             |

| INPUT                                 |                      |                                                |             |        |             |                  |

| Offset Voltage, RTI <sup>(1)</sup>    | V <sub>OS</sub>      | Gain = 1V/V, 1.375V/V                          |             | ±50    | ±250        | μV               |

|                                       |                      | Gain = 128V/V                                  |             | ±3     | ±15         | μV               |

| vs Temperature <sup>(2)</sup>         | dV <sub>os</sub> /dT | Gain = 1V/V                                    |             | ±0.2   | ±0.6        | μV/°C            |

|                                       |                      | Gain = 128V/V                                  |             | ±0.03  | ±0.17       | μV/°C            |

| vs Power Supply, RTI                  | PSR                  | VSP – VSN = 10 and 36V,<br>Gain = 1V/V, 128V/V |             | ±0.3   | ±3          | μV/V             |

| vs External Clock, RTI <sup>(3)</sup> | dV <sub>OS</sub> /df | 0.8MHz to 1.2MHz, Gain = 1V/V                  |             | ±0.05  |             | µV/kHz           |

|                                       |                      | 0.8MHz to 1.2MHz, Gain = 128V/V                |             | ±0.001 |             | µV/kHz           |

| Long-Term Stability <sup>(4)</sup>    |                      | Gain=128                                       |             | 3.5    |             | nV/month         |

| Input Impedance                       |                      | Single-ended and Differential                  |             | >1     |             | GΩ               |

| Input Capacitance, IN1 / IN2          |                      | Single-ended                                   |             | 12 / 8 |             | pF               |

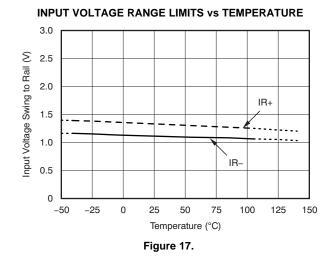

| Input Voltage Range                   |                      | Gain = 1V/V, Gain = 128V/V                     | (VSN) + 2.5 |        | (VSP) – 2.5 | v                |

| Common-Mode Rejection, RTI            | CMR                  | Gain = 1V/V                                    |             | ±0.3   | ±3          | μV/V             |

|                                       |                      | Gain = 128V/V                                  |             | ±0.08  | ±0.8        | μV/V             |

| Over Temperature                      |                      | Gain = 128V/V                                  |             | ±0.1   | ±1.5        | μ٧/٧             |

| SINGLE-ENDED OUTPUT<br>CONNECTION     |                      |                                                |             |        |             |                  |

| Offset Voltage, RTI, SE Out           | V <sub>OS</sub>      | Gain = 1V/V, 1.375V/V, SE                      |             | ±120   |             | μV               |

|                                       |                      | Gain = 128V/V, SE                              |             | ±3     |             | μV               |

| vs Temperature, SE Out                | dV <sub>os</sub> /dT | Gain = 1V/V, SE                                |             | 0.6    |             | μV/°C            |

|                                       |                      | Gain = 64V/V, SE                               |             | 0.05   |             | μV/°C            |

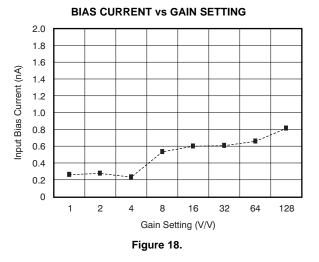

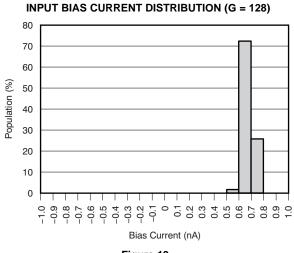

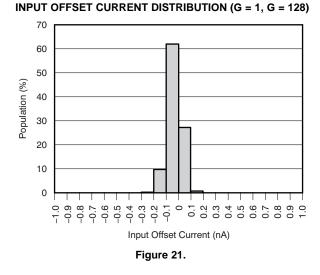

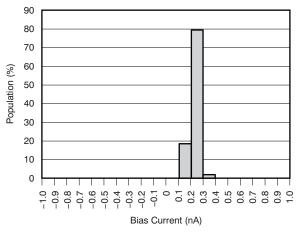

| INPUT BIAS CURRENT <sup>(3)</sup>     |                      |                                                |             |        |             |                  |

| Bias Current                          | Ι <sub>Β</sub>       | Gain = 1V/V                                    |             | ±0.3   | ±1          | nA               |

|                                       |                      | Gain = 128V/V                                  |             | ±0.8   | ±2          | nA               |

| Over Temperature                      | I <sub>B</sub>       | Gain = 1V/V, Gain = 128V/V                     |             | ±0.6   | ±2          | nA               |

| Offset Current                        | I <sub>OS</sub>      | Gain = 1V/V, Gain = 128V/V                     |             | ±0.1   | ±0.5        | nA               |

| Over Temperature                      | I <sub>os</sub>      | Gain = 1V/V, Gain = 128V/V                     |             | ±0.9   | ±2          | nA               |

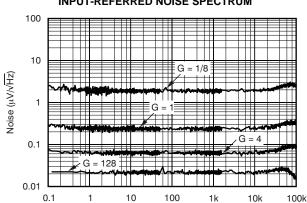

| NOISE                                 |                      |                                                |             |        |             |                  |

| Voltage Noise, RTI; Target            | e <sub>NI</sub>      |                                                |             |        |             |                  |

| f = 0.01Hz to 10Hz                    |                      | $R_S = 0\Omega, G = 128$                       |             | 420    |             | nV <sub>PP</sub> |

| f = 1kHz                              |                      | $R_{S} = 0\Omega, G = 128$                     |             | 22     |             | nV/√Hz           |

| f = 0.01Hz to 10Hz                    |                      | $R_S = 0\Omega, G = 1$                         |             | 4.5    |             | μV <sub>PP</sub> |

| f = 1kHz                              |                      | $R_S = 0\Omega, G = 1$                         |             | 240    |             | nV/√Hz           |

| Current Noise, RTI                    | I <sub>N</sub>       |                                                |             |        |             |                  |

| f = 0.01Hz to 10Hz                    |                      | $R_{S} = 10M\Omega, G = 128$                   |             | 1.7    |             | рА <sub>РР</sub> |

| f = 1kHz                              |                      | $R_{S} = 10M\Omega, G = 128$                   |             | 90     |             | fA/√Hz           |

RTI: Referred to input. (1)

(2) Specified by design; not production tested.

(3)

See *Application Information* section and typical characteristic graphs. 300-hour life test at +150°C demonstrated randomly distributed variation in the range of measurement limits. (4)

www.ti.com

# ELECTRICAL CHARACTERISTICS (continued)

**Boldface** limits apply over the specified temperature range,  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ . At  $T_A = +25^{\circ}C$ , VSP = +15V, VSN = -15V, VSON = 0V, VSOP = 5V, DVDD = +3V, DGND = 0V,  $R_L = 2.5k\Omega$  to VSOP/2 = VOCM, G = 1V/V, using internal clock, BUF inactive, V<sub>CM</sub> = 0V, and differential input and output, unless otherwise noted.

|                                                         |                 |                                            |                 | PGA280          |                 |        |  |

|---------------------------------------------------------|-----------------|--------------------------------------------|-----------------|-----------------|-----------------|--------|--|

| PARAMETER                                               |                 | CONDITIONS                                 | MIN             | TYP             | MAX             | UNIT   |  |

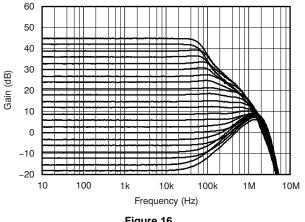

| GAIN                                                    |                 | Output Swing: ±4.5V <sup>(5)</sup>         |                 |                 |                 |        |  |

| Range of Input Gain                                     |                 |                                            |                 | 1∕8 to 128      |                 | V/V    |  |

| Range of Output Gain: 1V/V and 1%                       |                 |                                            |                 | 1 and 1%        |                 | V/V    |  |

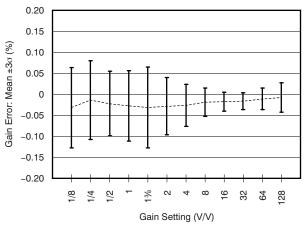

| Gain Error, All Binary Steps                            |                 | All Gains                                  |                 | ±0.03           | ±0.15           | %      |  |

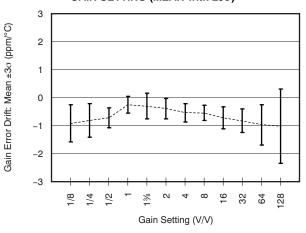

| vs Temperature <sup>(6) (7)</sup>                       |                 | No Load, All Gains Except G = 128V/V       |                 | -0.5            | ±2              | ppm/°C |  |

|                                                         |                 | No Load, G = 128V/V                        |                 | -1              | ±3              | ppm/°C |  |

| Gain Step Matching <sup>(8)</sup> (Gain to gain)        |                 | No Load, All Gains                         | See T           | ypical Characte | eristics        |        |  |

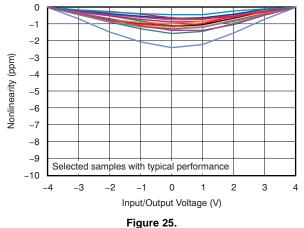

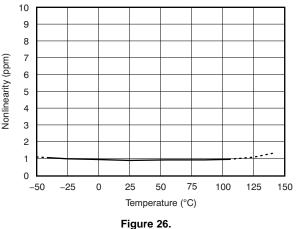

| Nonlinearity                                            |                 | No Load, All Gains <sup>(9)</sup>          |                 | 1.5             | 10              | ppm    |  |

| Over Temperature <sup>(6)</sup>                         |                 | No Load, All Gains                         |                 | 3               |                 | ppm    |  |

| OUTPUT                                                  |                 |                                            |                 |                 |                 |        |  |

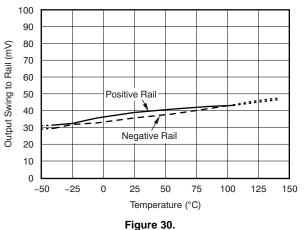

| Voltage Output Swing from Rail <sup>(8)</sup>           |                 | VSOP = 5V, Load Current 2mA                |                 | 40              | 100             | mV     |  |

|                                                         |                 | VSOP = 2.7V, Load Current 1.5mA            |                 |                 | 100             | mV     |  |

| Capacitive Load Drive                                   |                 |                                            |                 | 500             |                 | pF     |  |

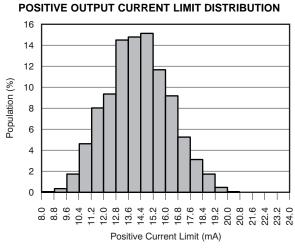

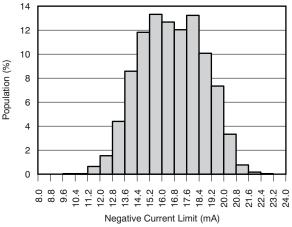

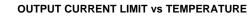

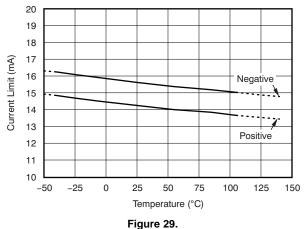

| Short-Circuit Current                                   | I <sub>SC</sub> | To VSOP/2, Gain = 1.375V/V                 | 7               | 15              | 25              | mA     |  |

| Output Resistance                                       |                 | Each output VOP and VON                    |                 | 200             |                 | mΩ     |  |

| VOLTAGE RANGE FOR VOCM                                  |                 | VSP-2V > VOCM                              | (VSON) +<br>0.1 |                 | (VSOP) –<br>0.1 | v      |  |

| Bias Current into VOCM                                  | Ι <sub>Β</sub>  |                                            |                 | 3               | 100             | nA     |  |

| VOCM Input Resistance                                   |                 |                                            |                 | 1               |                 | GΩ     |  |

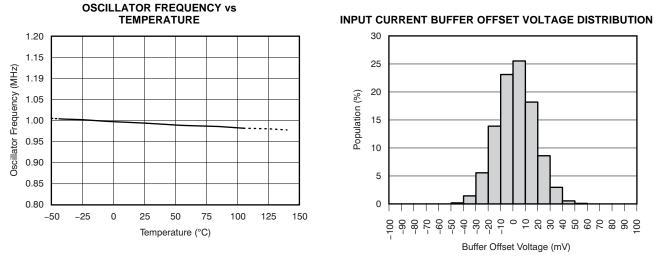

| INTERNAL OSCILLATOR                                     |                 |                                            |                 |                 |                 |        |  |

| Frequency of Internal Clock <sup>(6)</sup> (8)          |                 |                                            | 0.8             | 1               | 1.2             | MHz    |  |

| Ext. Oscillator Frequency Range                         |                 |                                            | 0.8             | 1               | 1.2             | MHz    |  |

| FREQUENCY RESPONSE                                      |                 |                                            |                 |                 |                 |        |  |

| Gain Bandwidth Product <sup>(8)</sup>                   | GBP             | G > 4                                      |                 | 6               |                 | MHz    |  |

| Slew Rate <sup>(8)</sup> , 4V <sub>PP</sub> Output Step | SR              | G = 1, C <sub>L</sub> = 100pF, BUF On      |                 | 1               |                 | V/µs   |  |

|                                                         |                 | G = 8, C <sub>L</sub> = 100pF              |                 | 2               |                 | V/µs   |  |

|                                                         |                 | G = 128, C <sub>L</sub> = 100pF            |                 | 1               |                 | V/µs   |  |

| Settling Time <sup>(8)</sup>                            | ts              |                                            |                 |                 |                 |        |  |

| 0.01%                                                   |                 | $G = 8$ , $V_O = 8V_{PP}$ Step             |                 | 20              |                 | μs     |  |

| 0.001%                                                  |                 | $G = 8$ , $V_O = 8V_{PP}$ Step             |                 | 30              |                 | μs     |  |

| 0.01%                                                   |                 | G = 128, $V_O = 8V_{PP}$ Step              |                 | 40              |                 | μs     |  |

| 0.001%                                                  |                 | $G = 128$ , $V_O = 8V_{PP}$ Step           |                 | 40              |                 | μs     |  |

| Overload Recovery, Input <sup>(8)</sup>                 |                 | 0.5V Over Supply, $G = \frac{1}{6}$ to 128 |                 | 8               |                 | μs     |  |

| Overload Recovery, Output <sup>(8)</sup>                |                 | $\pm 5.5 V_P$ Input, G = 1V/V              |                 | 6               |                 | μs     |  |

| INPUT MULTIPLEXER (Two-Channel)                         |                 |                                            |                 |                 |                 |        |  |

| Crosstalk, INP1 to INP2                                 |                 | At dc; Gain = 128V/V                       |                 | < -130          |                 | dB     |  |

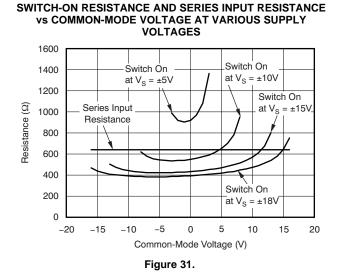

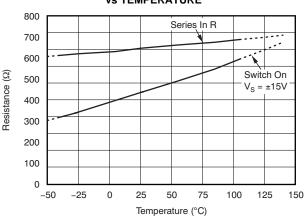

| Series-Resistance <sup>(8)</sup> —see Figure 44         |                 |                                            |                 | 600             |                 | Ω      |  |

| Switch On-Resistance <sup>(8)</sup>                     |                 |                                            |                 | 450             |                 | Ω      |  |

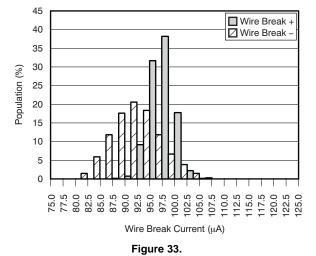

| Current Source and Sink <sup>(8)</sup>                  |                 | To GND                                     | 70              | 95              | 125             | μA     |  |

| INPUT CURRENT BUFFER (BUF)                              |                 |                                            |                 |                 |                 | -      |  |

| Offset Voltage <sup>(8)</sup>                           | V <sub>os</sub> | Buffer Active                              |                 | 15              |                 | mV     |  |

Gains smaller than 1/2 are measured with smaller output swing. (5)

(6) Specified by design; not production tested.

(7) See Figure 10 for typical gain error drift of various gain settings.

See Application Information section and typical characteristic graphs. (8)

(9) Only G = 1 is production tested.

#### www.ti.com

# **ELECTRICAL CHARACTERISTICS (continued)**

**Boldface** limits apply over the specified temperature range,  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ . At  $T_A = +25^{\circ}C$ , VSP = +15V, VSN = -15V, VSON = 0V, VSOP = 5V, DVDD = +3V, DGND = 0V,  $R_L = 2.5k\Omega$  to VSOP/2 = VOCM, G = 1V/V, using internal clock, BUF inactive,  $V_{CM} = 0V$ , and differential input and output, unless otherwise noted.

|                                                  |                                                  |            | PGA280                |            |      |

|--------------------------------------------------|--------------------------------------------------|------------|-----------------------|------------|------|

| PARAMETER                                        | CONDITIONS                                       | MIN        | TYP                   | MAX        | UNIT |

| DIGITAL I/O                                      | Supply: 2.7V to 5.5V                             |            |                       |            |      |

| Input (Logic Low Threshold)                      |                                                  | 0          |                       | (DVDD)x0.2 | V    |

| Input (Logic High Threshold)                     |                                                  | 0.8x(DVDD) |                       | DVDD       | V    |

| Output (Logic Low)                               | I <sub>OUT</sub> = 4mA, Sink                     |            |                       | 0.7        | V    |

| Output (Logic High)                              | I <sub>OUT</sub> = 2mA, Source                   | DVDD - 0.5 |                       |            | V    |

| SCLK, Frequency                                  |                                                  |            |                       | 10         | MHz  |

| POWER SUPPLY: Input Stage (VSN – VSP)            |                                                  |            |                       |            |      |

| Specified Voltage Range                          |                                                  | 10         |                       | 36         | v    |

| Operating Voltage Range                          |                                                  |            | 10 to 38              |            | V    |

| Quiescent Current (VSP) I <sub>Q</sub>           |                                                  |            | 2.4                   | 3          | mA   |

| Quiescent Current (VSN) I <sub>Q</sub>           |                                                  |            | 2.1                   | 3          | mA   |

| POWER SUPPLY: Output Stage (VSOP – VSON)         |                                                  |            |                       |            |      |

| Specified Voltage Range                          | VSP – 1.5V ≥ VSOP                                | 2.7        |                       | 5.5        | v    |

| Voltage Range for VSOP, Upper Limit              | (VSP - 2V) > VOCM, (VSP - 5V) > VSON             |            | (VSP)                 |            | V    |

| Voltage Range for VSON                           | $(VSP - 2V) > VOCM, VSP \ge VSOP$                |            | (VSN) to<br>(VSP) – 5 |            | V    |

| Quiescent Current I <sub>Q</sub>                 | VSOP                                             |            | 0.75                  | 1          | mA   |

| POWER SUPPLY: Digital (DVDD – DGND)              |                                                  |            |                       |            |      |

| Specified Voltage Range                          |                                                  | 2.7        |                       | 5.5        | v    |

| Voltage Range for DVDD, Upper Limit              |                                                  |            | (VSP) – 1             |            | V    |

| Voltage Range for DGND, Lower Limit              |                                                  |            | (VSN)                 |            | V    |

| Quiescent Current <sup>(10)</sup> I <sub>Q</sub> | Static Condition, No External Load,<br>DVDD = 3V |            | 0.07                  | 0.13       | mA   |

| TEMPERATURE RANGE                                |                                                  |            |                       |            |      |

| Specified Range                                  |                                                  | -40        |                       | +105       | °C   |

| Operating Range                                  |                                                  | -55        |                       | +140       | °C   |

| Thermal Resistance θ <sub>JA</sub>               |                                                  |            |                       |            |      |

| SSOP                                             | High-K Board, JESD51                             |            | 80                    |            | °C/W |

(10) See Application Information section and typical characteristic graphs.

www.ti.com

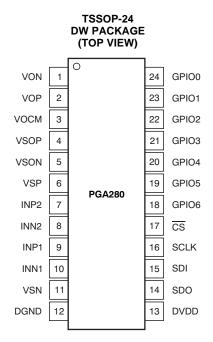

# **PIN CONFIGURATION**

# **PIN DESCRIPTIONS**

| PIN NO. | NAME | DESCRIPTION                       | PIN NO. | NAME  | DESCRIPTION                        |

|---------|------|-----------------------------------|---------|-------|------------------------------------|

| 1       | VON  | Inverting signal output           | 13      | DVDD  | Digital supply                     |

| 2       | VOP  | Noninverting signal output        | 14      | SDO   | SPI slave data output              |

| 3       | VOCM | Input, output common-mode voltage | 15      | SDI   | SPI slave data input               |

| 4       | VSOP | Positive supply for output        | 16      | SCLK  | SPI clock input                    |

| 5       | VSON | Negative supply for output, AGND  | 17      | CS    | SPI chip select input; active low  |

| 6       | VSP  | Positive high-voltage supply      | 18      | GPIO6 | GPIO 6, SYNC (in), OSC (out), ECS6 |

| 7       | INP2 | AUX input, noninverting           | 19      | GPIO5 | GPIO 5, BUFA (out), ECS5           |

| 8       | INN2 | AUX input, inverting              | 20      | GPIO4 | GPIO 4, BUFT (in), ECS4            |

| 9       | INP1 | Signal input, noninverting        | 21      | GPIO3 | GPIO 3, EF (out), ECS3             |

| 10      | INN1 | Signal input, inverting           | 22      | GPIO2 | GPIO 2, ECS2, MUX2                 |

| 11      | VSN  | Negative high-voltage supply      | 23      | GPIO1 | GPIO 1, ECS1, MUX1                 |

| 12      | DGND | Digital ground                    | 24      | GPIO0 | GPIO 0, ECS0, MUX0                 |

**FEXAS**

INSTRUMENTS

# **TYPICAL CHARACTERISTICS**

At  $T_A = +25^{\circ}C$ , VSP = +15V, VSN = -15V, VSON = 0V, VSOP = 5V, DVDD = +3V, DGND = 0V,  $R_L = 2.5k\Omega$  to VSOP/2 = VOCM, G = 1V/V, using internal clock, BUF inactive, V<sub>CM</sub> = 0V, and differential input and output, unless otherwise noted.

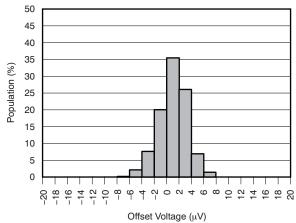

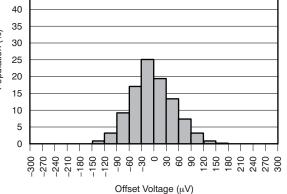

# OFFSET VOLTAGE PRODUCTION DISTRIBUTION (G = 128)

Figure 1.

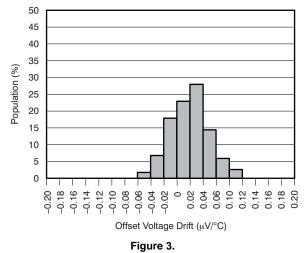

**OFFSET VOLTAGE DRIFT DISTRIBUTION (G = 128)**

50 45 40 35 Population (%) 30 25 20 15

OFFSET VOLTAGE PRODUCTION DISTRIBUTION (G = 1)

OFFSET VOLTAGE DRIFT DISTRIBUTION (G = 1)

Figure 4.

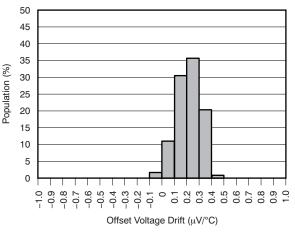

# **TYPICAL CHARACTERISTICS (continued)**

At  $T_A = +25^{\circ}C$ , VSP = +15V, VSN = -15V, VSON = 0V, VSOP = 5V, DVDD = +3V, DGND = 0V,  $R_L = 2.5k\Omega$  to VSOP/2 = VOCM, G = 1V/V, using internal clock, BUF inactive, V<sub>CM</sub> = 0V, and differential input and output, unless otherwise noted.

8

www.ti.com

#### SBOS487A – JUNE 2009 – REVISED SEPTEMBER 2009

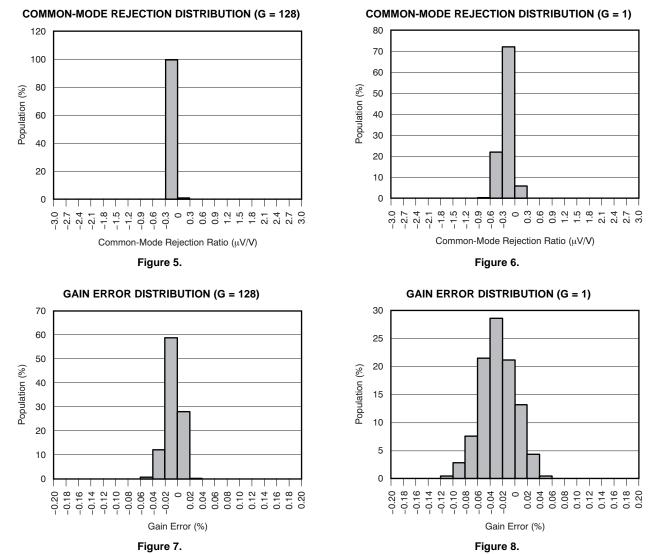

# **TYPICAL CHARACTERISTICS (continued)**

At  $T_A = +25^{\circ}C$ , VSP = +15V, VSN = -15V, VSON = 0V, VSOP = 5V, DVDD = +3V, DGND = 0V,  $R_L = 2.5k\Omega$  to VSOP/2 = VOCM, G = 1V/V, using internal clock, BUF inactive,  $V_{CM} = 0V$ , and differential input and output, unless otherwise noted.

Figure 9.

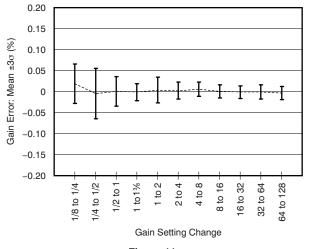

MAXIMUM GAIN ERROR DEVIATION BETWEEN SEQUENTIAL GAIN SETTINGS (MEAN with  $\pm 3\sigma$ )

Figure 11.

GAIN ERROR DRIFT DISTRIBUTION vs GAIN SETTING (MEAN with ±3σ)

Figure 10.

GAIN ERROR DISTRIBUTION vs GAIN SETTING (MEAN with  $\pm 3\sigma$ )

Figure 12.

# ÈXAS **INSTRUMENTS**

www.ti.com

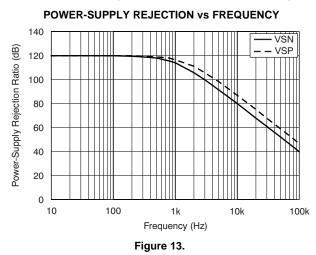

At  $T_A = +25^{\circ}C$ , VSP = +15V, VSN = -15V, VSON = 0V, VSOP = 5V, DVDD = +3V, DGND = 0V,  $R_L = 2.5k\Omega$  to VSOP/2 = VOCM, G = 1V/V, using internal clock, BUF inactive, V<sub>CM</sub> = 0V, and differential input and output, unless otherwise noted.

**INPUT-REFERRED NOISE SPECTRUM**

Frequency (Hz)

#### SBOS487A – JUNE 2009 – REVISED SEPTEMBER 2009

www.ti.com

# **TYPICAL CHARACTERISTICS (continued)**

At  $T_A = +25^{\circ}C$ , VSP = +15V, VSN = -15V, VSON = 0V, VSOP = 5V, DVDD = +3V, DGND = 0V,  $R_L = 2.5k\Omega$  to VSOP/2 = VOCM, G = 1V/V, using internal clock, BUF inactive,  $V_{CM} = 0V$ , and differential input and output, unless otherwise noted.

#### Figure 19.

#### INPUT BIAS CURRENT DISTRIBUTION (G = 1)

#### Figure 20.

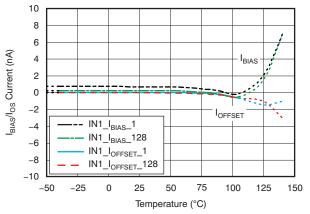

#### INPUT BIAS CURRENT AND INPUT OFFSET CURRENT vs TEMPERATURE

Figure 22.

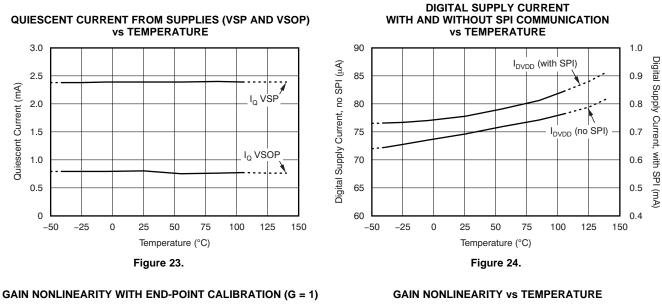

# **TYPICAL CHARACTERISTICS (continued)**

At  $T_A = +25^{\circ}C$ , VSP = +15V, VSN = -15V, VSON = 0V, VSOP = 5V, DVDD = +3V, DGND = 0V,  $R_L = 2.5k\Omega$  to VSOP/2 = VOCM, G = 1V/V, using internal clock, BUF inactive, V<sub>CM</sub> = 0V, and differential input and output, unless otherwise noted.

**FEXAS**

www.ti.com

Current,

, with

Texas

INSTRUMENTS

# **TYPICAL CHARACTERISTICS (continued)**

At  $T_A = +25^{\circ}C$ , VSP = +15V, VSN = -15V, VSON = 0V, VSOP = 5V, DVDD = +3V, DGND = 0V,  $R_L = 2.5k\Omega$  to VSOP/2 = VOCM, G = 1V/V, using internal clock, BUF inactive,  $V_{CM} = 0V$ , and differential input and output, unless otherwise noted.

Figure 27.

SBOS487A-JUNE 2009-REVISED SEPTEMBER 2009

OUTPUT SWING TO RAIL vs TEMPERATURE (VSOP – VSON = 5V)

# **TYPICAL CHARACTERISTICS (continued)**

At  $T_A = +25^{\circ}C$ , VSP = +15V, VSN = -15V, VSON = 0V, VSOP = 5V, DVDD = +3V, DGND = 0V,  $R_L = 2.5k\Omega$  to VSOP/2 = VOCM, G = 1V/V, using internal clock, BUF inactive,  $V_{CM} = 0V$ , and differential input and output, unless otherwise noted.

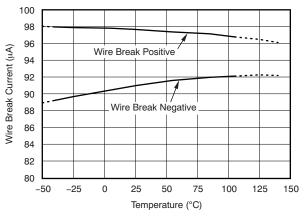

WIRE BREAK CURRENT DISTRIBUTION

SWITCH-ON RESISTANCE AND SERIES INPUT RESISTANCE vs TEMPERATURE

WIRE BREAK CURRENT MAGNITUDE vs TEMPERATURE

Figure 34.

www.ti.com

#### www.ti.com

Texas

INSTRUMENTS

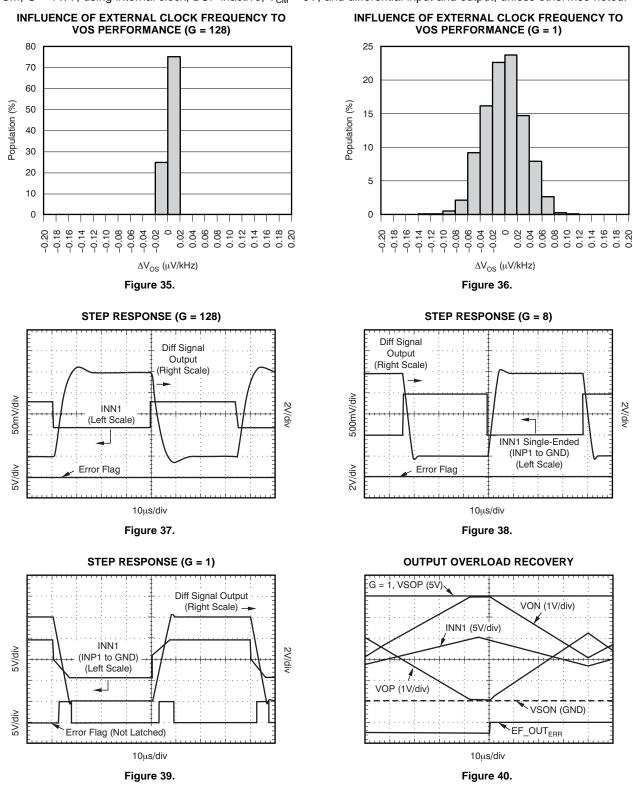

#### **TYPICAL CHARACTERISTICS (continued)**

At  $T_A = +25^{\circ}C$ , VSP = +15V, VSN = -15V, VSON = 0V, VSOP = 5V, DVDD = +3V, DGND = 0V,  $R_L = 2.5k\Omega$  to VSOP/2 = VOCM, G = 1V/V, using internal clock, BUF inactive,  $V_{CM} = 0V$ , and differential input and output, unless otherwise noted.

# **TYPICAL CHARACTERISTICS (continued)**

At  $T_A = +25^{\circ}C$ , VSP = +15V, VSN = -15V, VSON = 0V, VSOP = 5V, DVDD = +3V, DGND = 0V,  $R_L = 2.5k\Omega$  to VSOP/2 = VOCM, G = 1V/V, using internal clock, BUF inactive, V<sub>CM</sub> = 0V, and differential input and output, unless otherwise noted.

Figure 41.

Figure 42.

www.ti.com

#### SBOS487A-JUNE 2009-REVISED SEPTEMBER 2009

# **APPLICATION INFORMATION**

# DESCRIPTION

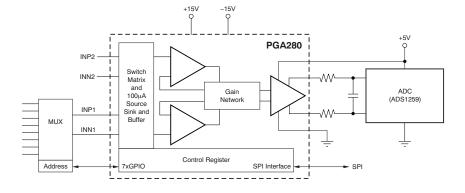

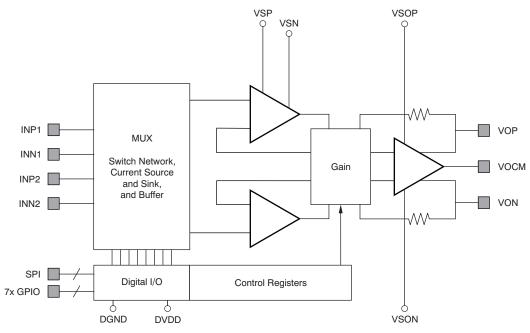

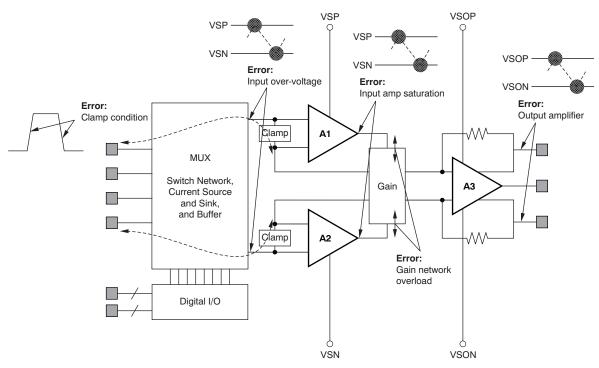

The PGA280 is a universal high-voltage instrumentation amplifier with digital gain control. It offers excellent dc precision and long-term stability using modern chopper technology with internal filters that minimize chopper-related noise. The input gain extends from ½V/V (attenuation) to 128V/V in binary steps. The output stage offers a gain multiplying factor of 1V/V and 1½V/V for optimal gain adjustment. The output stage connects to the low-voltage (5V or 3V) supply. Figure 43 shows a block diagram of the device.

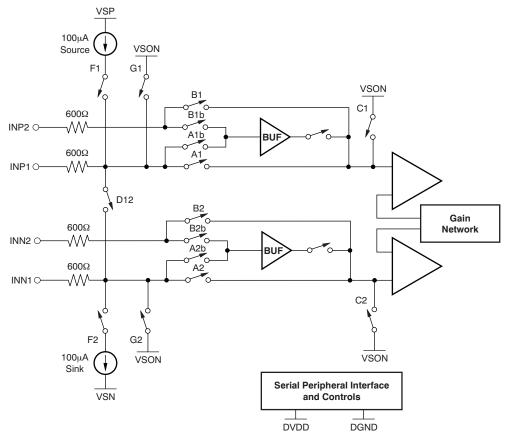

Figure 43. PGA280 Block Diagram

A signal multiplexer provides two differential inputs. Several signal switches allow signal diagnosis of wire break, input disconnect, single-ended (versus differential), and shorted inputs.

The supply voltage of up to ±18V offers a wide common-mode range with high input impedance; therefore, large common-mode noise signals and offsets can be suppressed.

A pair of high-speed current buffers can be activated to avoid inrush currents during fast signal transients, such as those generated from switching the signal multiplexers. This feature minimizes discharge errors in passive signal input filters in front of the multiplexer.

The fully differential signal output matches the inputs of modern high-resolution and high-accuracy analog-to-digital converters (ADCs), including Delta-Sigma ( $\Delta\Sigma$ ) as well as successive-approximation response (SAR) converters. The supply voltage for the output stage is normally connected together with the converter supply, thus preventing signal overloads from the high-voltage analog supply.

Internal error detection in the input and output stage provides individual information about the signal condition. Integrating ADCs may hide momentary overloads. Together with the input switch matrix, extensive signal and error diagnosis is made possible.

The serial peripheral interface (SPI) provides write and read access to internal registers. These registers control gain, the current buffer, input switches, and the general-purpose input/output (GPIO) or special function pins, as well as configuration and diagnostics.

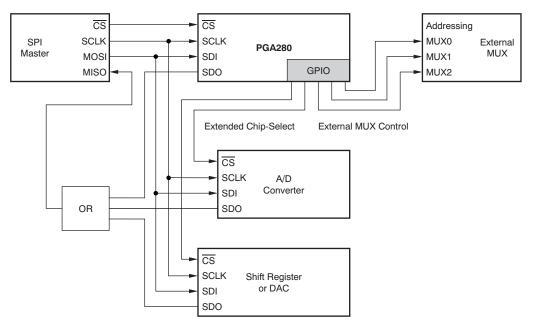

The GPIO port controls the multiplexer (MUX) and switches and indicates internal conditions; it can also be individually configured for output or input. A special CS mode for the GPIO extends the communication to other external SPI devices, such as data converters or shift registers. This special function is intended for SPI communication via a minimum number of isolation couplers. Additional proof for communication integrity is provided by an optional checksum byte following each communication block.

Copyright © 2009, Texas Instruments Incorporated

# FUNCTIONAL BLOCKS

Both high-impedance input amplifiers are symmetrical, and have low noise and excellent dc precision. These amplifiers are connected to a resistor network and provide a gain range from 128V/V down to an attenuation of 1%. The PGA280 architecture rejects common-mode offsets and noise over a wide bandwidth.

The PGA280 features additional current buffers placed in front of the precision amplifier that can be activated on demand. When activated, these additional current buffers avoid problems that result from input current during dynamic overloads, such as the fast signal transient that follows the channel switching from a multiplexer. Without the use of the additional current buffers, the fast signal transient would overload the precision amplifiers and high bias currents could flow into the protection clamp until the amplifiers recover from the overload. This momentary current can influence the signal source or passive filters in front of the multiplexer and generate long settling tails. Activating this current buffer avoids such an overload current pulse. The buffer disconnects automatically after an adjustable time. For continuous signal measurement, the additional current buffers are not used.

The switches in the input provide signal diagnostic capability and offer an auxiliary input channel (INP2 and INN2; see Figure 44). Both channels can be switched to diagnose or test conditions, such as a ground-referred, single-ended voltage measurement for either input. In this mode, each of the signal inputs can be observed to analyze common-mode offsets and noise.

The primary input channel [INP1 and INN1] provides switches and current sources for a wire break test. A switch can short both inputs. It can also discharge a filter capacitor after a wire break test, for example.

The signal inputs are diode-clamped to the supply rails. External resistors can be placed in series to the inputs to provide overvoltage protection. Current into the input pins should be limited to  $\leq$  10mA.

The output stage offers a fully-differential signal around the output reference pin, VOCM. The VOCM pin is a high-impedance input and expects an external voltage, typically close to midsupply. The 3V or 5V supply of the converter or amplifier, following the PGA280 outputs, is normally connected to VSOP and VSON; this configuration shares a common supply voltage and protects the circuit from overloads. The fully-differential signal avoids coupling of noise and errors from the supply and ground, and allows large signal swing without the risk of nonlinearities that arise when driving near the supply rails.

The PGA280 signal path has several test points for critical overload conditions. The input amplifiers detect signal overvoltage and overload as a result of high gain. The output stage also detects clipping. These events are filtered with adjustable suppression delays and then stored for readout. A GPIO pin can be dedicated for external indication either as an interrupt or in a monitor mode.

A serial peripheral interface (SPI) controls the gain setting and switches, as well as the operation modes and the GPIO port pins. The SPI allows read and write access to the internal registers. These registers contain conditions, flags, and settings, as described in the *SPI and Register Description* section. They represent the gain setting for the input stage from 128V/V to the attenuation of ½V/V in binary steps and the output stage gain of 1V/V and 1.375V/V (1%). The input MUX and switches and the input buffers are also controlled by registers. Internal error conditions are stored and may be masked to activate an external pin in the GPIO port.

This GPIO port can be configured individually for either input or <u>output</u> or for a special function. In special function mode, the port indicates an error condition, generates  $\overline{CS}$  signal, controls an external MUX, and connects to the buffer control and oscillator.

The port pin can act as a  $\overline{CS}$  for an external SPI device. This mode connects other SPI devices [such as an analog-to-digital (A/D) converter] to the primary four-wire SPI. This feature is especially desirable when using galvanically-isolated SPI communication. An optional checksum byte further improves communications integrity.

PGA280

#### www.ti.com

#### Input Switch Network

Figure 44 shows the arrangement of the input switches. They are controlled individually via the digital SPI. The switches B1b, B2b, A1b, and A2b are controlled automatically with the buffer (BUF) operation.

Figure 44. Input Switch Diagram

Switches A and B select the signal input. Input 1 (INP1 and INN1) provides two current sources and two switches that connect to VSON (which is typically the analog ground). This configuration is intended for wire break diagnosis. D12 can discharge an external capacitor or generate a starting condition.

Switches C1 and C2 are used to measure the input voltage referred to GND (VSON); for example, with A1 and C2 closed. This scheme measures the voltage signal connected to the input pin (INP1) referred to a common ground. The BUF output is protected against a short to VSON. See the *SPI and Register Description* section for more information about switch control.

#### Input Amplifier, Gain Network and Buffer

The high-precision input amplifiers present very low dc error and drift as a result of a modern chopper technology with an embedded synchronous filter that removes virtually all chopping noise. This topology reduces flicker noise to a minimum and therefore enables the precise measurement of small dc-signals with high resolution, accuracy, and repeatability. The chopper frequency of 250kHz is derived from an internal 1MHz clock. An external clock can also be connected, if desired.

The gain network for the binary gain steps connects to the input amplifiers, thus providing the best possible signal-to-noise ratio (SNR) and dc accuracy up to the highest gains. Gain is controlled by Register 0. This register can control the gain and address for an external MUX in one byte. Selectable gains (in V/V) are : 128, 64, 32, 16, 8, 4, 2, 1, ½, ¼, and ⅓. The gain is set to 1/8V/V after device reset or power-on.

Copyright © 2009, Texas Instruments Incorporated

Programmable gain amplifiers such as the PGA280 use internal resistors to set the gain. Consequently, quiescent current is increased by the current that passes through these resistors. The largest amplitude could increase the supply current by  $\pm 0.4$ mA. In maximum overload, gain of 128V/V and each or the inputs connected to the opposite supply voltage, a current of approximately 27mA was measured. External resistors in series with the input pins that are normally present avoid this extreme condition. This current is only limited by the internal 600 $\Omega$  and the switch-on resistance (see Figure 44).

### **Current Buffer**

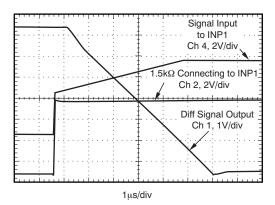

Designed for highest accuracy and low noise, both amplifier inputs are protected from dynamic overvoltages through clamps. The amplifier fast input slew rate (approximately 1V/µs) normally prevents these clamps from turning on, provided adequate signal filtering is placed before the input. However, the fast channel switching-transient of a multiplexer or switch is much steeper, and cannot be filtered; this type of transient generates a dynamic overload. The current buffers (BUF) prevent this dynamic overload condition of the input.

With the buffers not activated, Figure 45 indicates the clamp current flowing as a result of a fast signal change. The ramp in the signal, measured at the input pins (INP1), is the resulting voltage drop across the  $1.5k\Omega$  resistor. In the example measurement, this resistor is placed between the signal generator and the input pin of the PGA280.

Figure 45. Buffer OFF: Input Clamp Current Flowing

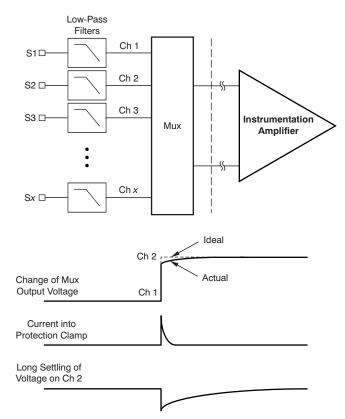

Figure 46 shows a typical block diagram for multiplexed data acquisition. The transient from channel 1 to channel 2, shown as a voltage step, dynamically overloads the amplifier. A current pulse results from the input protection clamp. Without the activation of the buffers (see BUF, Figure 44), the clamp current charges the filter and the signal source. Input low-pass filters are often set to settling times in the millisecond range; therefore, discharge currents from dynamic overload would produce long settling delays.

SBOS487A-JUNE 2009-REVISED SEPTEMBER 2009

Note: Current from the protection clamp into the signal source and filter produces a long settling delay.

#### Figure 46. Typical Block Diagram for Multiplexed Data Acquisition

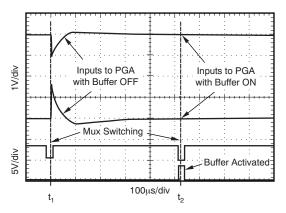

Together with the switching command of the multiplexer or internal switching, the current buffers (BUF) can be activated to prevent such clamp currents. The buffers do not have clamps as long as the signal remains within the supply boundaries. Figure 47 shows an example of the input signal settling for both conditions: without and with the buffer activated.

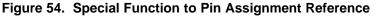

Without the buffer, there is an obvious long settling, depending on signal and filter impedance. With the buffer activated, only the amplifier has to settle and no distorting current is reflected into the signal source and filter; no glitch is visible in this plot. The plot shows the resulting settling of the input signal for a positive and a negative signal step as indicated in Figure 46; also shown are the SPI signal and the BUFA signal.

Figure 47. Example for Amplifier Settling Without (t1) and With (t2) Buffer (BUF) Activated

SBOS487A – JUNE 2009 – REVISED SEPTEMBER 2009

www.ti.com

The buffers turn off automatically after a preset time (see Register 3, BUFTIM). They are activated from bit 5 ('T') within the command byte. They can also be triggered by an external pin (BUFTin on GPIO4). The BUFA bit is active in conjunction with the buffer, indicating that the buffer is busy (see Figure 55).

Error detection circuits observe the signal path for signal overvoltage (IOVerr), amplifier output clipping (IARerr), and gain overload (GAINerr). The Input Clamp Activation indicator ICAerr indicates that current was conducted into the dynamic clamp circuit. These indicators help prevent misinterpretation of the analog signal and diagnose critical input signal conditions, such as those that occur with integrating analog-to-digital converters that may hide momentary overloads and present inaccurate results.

The buffers (BUF) prevent current flowing from the signal source with a compromise of offset voltage. As soon as the buffers are turned off, the amplifiers settle back to high precision. For signal measurement without (multiplexer) switching transients, the buffer is not used.

#### Input Protection

The input terminals are protected with internal diodes connected to VSP and VSN. If the input signal voltage exceeds the power-supply voltage (VSP and VSN), the current should be limited to less than 10mA to protect the internal clamp diodes. This current-limiting can generally be accomplished with a series input resistor.

#### EMI Susceptibility

Amplifiers vary in susceptibility to electromagnetic interference (EMI), but good layout practices play a critical role. EMI can generally be identified as a variation in offset voltage shifts. The PGA280 has been specifically designed to minimize susceptibility to EMI by incorporating an internal low-pass filter. Additional EMI filters may be required next to the signal inputs of the system, as well as known good practices such as using short traces, low-pass filters, and damping resistors combined with parallel and shielded signal routing, depending on the end system requirements.

#### Output Stage

The output stage power is connected to the low-voltage supply (normally 3V or 5V) that is used by the subsequent signal path of the system. This design prevents overloading of the low-voltage signal path.

The output signal is fully differential around a common-mode voltage (VOCM). The VOCM input pin is typically connected to midsupply voltage to offer the widest signal amplitude range. VOCM is a high-impedance input that requires an external connection to a voltage within the supply boundaries. The usable voltage range for the VOCM input is specified in the Electrical Characteristics and must be observed.

The output stage can be set to a gain of 1V/V and 1%V/V. It is set to 1V/V after device reset or power-on, and is controlled by the gain multiplication factor.

Both signal outputs, VOP and VON, swing symmetrically around VOCM. The signal is represented as the voltage between the two outputs and does not require an accurate VOCM. Therefore, the signal output does not include ground noise or grounding errors. Noise or drift on VOCM is normally rejected by the common-mode rejection capability of the subsequent signal stage.

The signal that passes through the output stage is internally monitored for two error conditions: clipping of the signal to the supply rail and overcurrent. In fault conditions, an error flag bit is set (OUTerr).

#### **Output Filter**

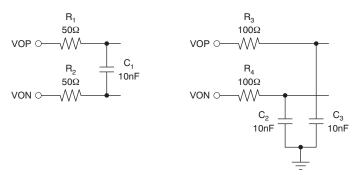

The PGA280 uses chopper technology for excellent dc stability over temperature and life of operation. It also avoids 1/f frequency (flicker) noise, and therefore enables both high resolution and high repeatability for dc measurements. While the chopper noise components are internally filtered, a minimal residual amount of high-frequency switching noise appears at the signal outputs. An external, passive, low-pass filter after the output stage is recommended to remove this switching noise; Figure 48 shows two examples. This filter can also be used to isolate or decouple the charge switching pulses of an A/D converter input.

Figure 48. Typical Examples of Recommended Output Filters

#### Single-Ended Output

The output stage of PGA280 is designed for highest precision. The fully-differential output avoids grounding errors and noise, and delivers twice the signal amplitude compared to single-ended signals. However, if desired, the output can be taken single-ended from one of the output pins referred to the voltage at the VOCM pin. The output stage errors now relate to half the signal amplitude and half the signal gain. The unused output is unconnected, but not disconnected from error detection. The usable voltage range for the VOCM input is specified in the Electrical Characteristics and must be observed: the output swing (of both outputs) should not saturate to the supply. Separate specifications for offset voltage and drift indicate higher offset voltage at lower gains, because some error sources are not cancelled in the output stage connected in single-ended mode. Note that the gain is one-half of the gain set in reference to the gain table (see Table 2).

#### **Error Detection**

The PGA280 is designed for high dc precision and universal use, but it also allows monitoring of signal integrity. The device contains an input switch network for signal tests and sense points that can indicate critical conditions. These added features support fully automated system setup and diagnostic capability. Out-of linear range conditions are detected and stored in the Error Status Register (Register 4) until reset. The input switches shown in Figure 44 can be used to short the input to GND, disconnect the signal, insert a 100µA test current, discharge external capacitance, and switch to a ground (VSON)-referenced signal measurement to observe the signal at the pin (versus the differential measurement). Figure 49 illustrates the diagnostic points available for error detection in the device architecture.

All switches are controlled through the SPI. The error signals can be combined using a logic *OR* function to an output pin and eventually be used as an error interrupt signal. Errors are normally latched, unless the LTD bit (latch disable) is set.

The error sensors are filtered with a suppression delay (Register 11). These error signals are normally suppressed during the buffer (BUFA) active time.

SBOS487A-JUNE 2009-REVISED SEPTEMBER 2009

Note: The signal path is observed for possible limitations; flags are stored and indicated in Register 4.

Figure 49. Diagnostic Points for Error Detection

# ERROR INDICATORS

#### Input Clamp Conduction (ICAerr)

The input clamp protects the precision input amplifier from large voltages between the inputs that occur from a fast signal slew rate in the input. This clamp circuit pulls current from the input pins while active. Current flowing through the clamp can influence the signal source and cause long settling delays on passive signal filters. The current is limited by internal resistors of approximately  $2.4k\Omega$ . Dynamic overload can result from the difference signal as well as the common-mode signal.

The input clamp turns on when the input signal slew rate is faster than the amplifier slew rate (see the Electrical Characteristics specification) and larger than  $\pm 1V$ . Appropriate input filtering avoids the activation. However, transients from MUX switching, internal switches, and gain switching action cannot be filtered; therefore, to avoid these transients, it is recommended that the current buffer (BUF) be activated. The buffer isolates the signal input from the clamp, and therefore avoids the current pulse (see Figure 44).

#### Input Overvoltage (IOVerr)

The input amplifier can only operate at high performance within a certain input voltage range to the supply rail. The IOVerr flag indicates a loss of performance because of the input voltage or the amplifier output approaching the rail.

#### Gain Network Overload (GAINerr)

The gain setting network is protected against overcurrent conditions that arise because of an improper gain setting. The current into the resistors is proportional to the voltage between both inputs and the internal resistor; a low resistor value results in high gains. This error flag indicates such an overload condition that is the result of an improper gain setting.

# Output Amplifier (OUTerr)

The output stage is monitored for signal clipping to the supply rail and for overcurrent conditions.

#### CheckSum Error (CRCerr)

SPI communication can include a checksum byte for increased data integrity, when enabled. It is especially useful for an isolated SPI. This error detection is only active with the checksum activated. See the *Checksum* section for details.

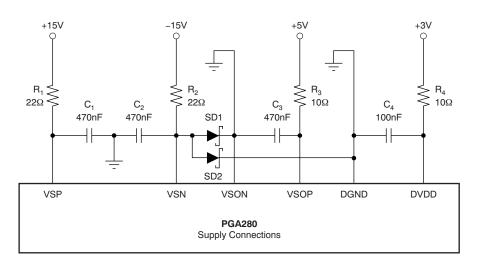

# POWER SUPPLY

The PGA280 can connect to three supply voltages: the high-voltage analog supply, the low-voltage output amplifier supply, and the digital I/O supply. This architecture allows an optimal interface (level-shift) to the different supply domains.

The high-voltage analog supply, VSP and VSN, powers the high-voltage input section. The substrate of the IC is connected to VSN; therefore, it must be connected to the most negative potential.

The low-voltage analog output supply, VSOP and VSON, can operate within the high-voltage supply boundaries with two minimal limitations:

- 1. The usable range for VSON is from a minimum 5V below VSP to as low as VSN. This 5V provides the headroom for the output supply voltage of +2.7V to +5V. Even with less than 5V supply, this voltage difference is required for proper operation.

- 2. The common-mode control input, VOCM, requires a voltage at least 2V from VSP, in order to support internal rail-to-rail performance.

These limits may only come into consideration when using a minimum supply or an extremely asymmetrical high-voltage supply. In most practical cases, VSON is connected to the ground of the system 3V or 5V supply.

VSOP can be turned on first or can be higher than VSP without harm, but operation fails if VSP and VSN are not present.

Observe the maximum voltage applied between VSOP and VSON, because there is no internal protection. This consideration is the same as with other standard operational amplifier devices.

The digital supply, DGND and DVDD, can also be set within the boundaries of VSP and VSN. Only the positive supply, DVDD, cannot be closer than 1V below VSP. It can be turned on without the analog supply being present and is operational, but limited to digital functions in this case. The maximum supply voltage must be observed because there is no internal protection. VSOP and VSON can be connected with DVDD and DGND, if desired.

Current consumption of the digital supply is very low under static conditions, but increases with communications activity. Assuming no external load except the 20pF load to SDO, with an SCLK = 10MHz and a 3V supply, the current momentarily increases by approximately 0.6mA when reading a register (for example, reading Register 14). With a 5V digital supply, the increase is in the range of 0.8mA. This additional current is only required during communication; a larger bypass capacitor can supply this current. Driving current into SDO would further increase the current demand.

VSN is connected to the substrate; therefore, the voltage at VSON or DGND must not turn on the substrate diode to VSN. Use external Schottky diodes from VSON to VSN and from DGND to VSN (refer to Figure 50) to prevent such a condition.

The PGA280 uses an internal chopper technology and therefore works best with good supply decoupling. Series resistors in the supply are recommended to build an RC low-pass filter. With the small supply current, these series resistors can be in the range of  $15\Omega$  to  $22\Omega$ . The RC filter also prevents a very fast rise time of the supply voltage, thus avoiding parasitic currents in the IC. Connecting supply wires into an already-turned on supply (very fast rise time) without such a filter can damage the IC as a result of voltage overshoot and parasitic charge currents. Figure 50 shows an example of a supply connection using RC bypass filters. DVDD may not need decoupling, but if the digital supply is noisy, a filter is recommended at C<sub>4</sub> and R<sub>4</sub>.

#### NOTE

Rise and fall times for the high-voltage supplies must be slower than 1V/µs.

TEXAS INSTRUMENTS

www.ti.com

SBOS487A-JUNE 2009-REVISED SEPTEMBER 2009

Note: In this example, the Schottky diodes prevent substrate reversing. The supply voltages shown are only example values.

#### Figure 50. Supply Connection Example Using RC Bypass Filters for Good Decoupling

# External Clock Synchronization

The PGA280 uses an internal oscillator of 1MHz, nominally. This clock can be brought out to pin GPIO6 if configured by the internal register setting to allow synchronization of external systems to this clock. If the PGA280 must be controlled by an external clock, GPIO06 can be configured as an oscillator input, thus overriding the internal oscillator. The frequency range must be within the specified range shown in the Electrical Characteristics in order to maintain stable device performance. The clock pulse width is not critical, because it is internally divided down; however, less than 30% deviation is recommended. The GPIO6 input assumes a standard logic signal. Prevent overshoot at this pin, and provide approximately equal rise and fall time for the lowest influence on offset voltage as a result of coupled noise.

Expect a small amount of additional noise during the transition from internal to external clock, or vice-versa, for approximately eight clock periods because of phase mismatch.

#### Quiescent Current

The PGA280 uses internal resistor networks and switches to set the signal gain. Consequently, the current through the resistor network may vary with the gain and signal amplitude. Under normal operation, the gain-related current is low (less than  $400\mu$ A). However, in signal overload conditions while a high gain is selected, this amount of current can increase.

#### Settling Time

The PGA280 provides very low drift and low noise, and therefore allows repeatable settling to a precise value with a negligible tail. Signal-related load and power dissipation variables have minimal effect on the device accuracy.

#### **Overload Recovery**

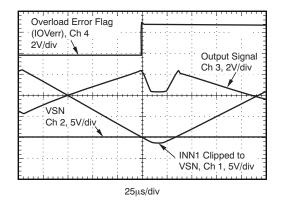

Overload conditions can vary widely, and there are multiple points in an instrumentation amplifier that can be overloaded. During input overload, the PGA280 folds the output signal partially back as a result of the differential signal structure and summing, but the error flags indicate such fault conditions. The amplifier recovers safely after removing the overload condition, as long as it is within the specified operating range as shown in Figure 51.

Avoid dynamic overload by using adequate signal filtering that reduces the input slew rate to the slew rate of the amplifier. Fast signal jumps produced from multiplexed signal sources or gain changes cannot normally be filtered, but the current buffer (BUF) stage can be activated to prevent current flowing through the input into the protection clamp in such situations.

SBOS487A - JUNE 2009 - REVISED SEPTEMBER 2009

Figure 51. Input Clipping: Negative Side

# **SPI and Register Description**

The serial peripheral interface uses four wires: CS (input), clock (SCLK, input), data in (SDI, or slave data input), and data out (SDO, or slave data output) and operates as a slave.

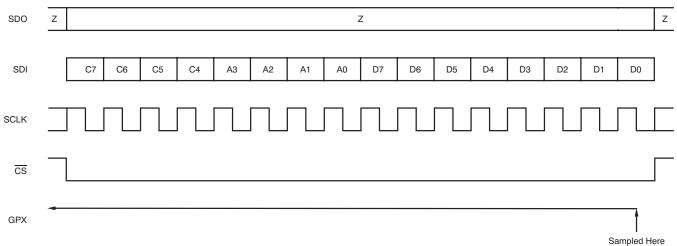

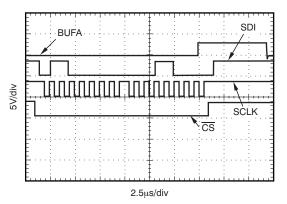

CS is active low; data are sampled with the negative clock edge. It is insensitive to the starting condition of SCLK polarity (SPOL = 1 or 0). See Figure 52 and Figure 53.

The SPI communicates to the internal registers, starting with a byte for command and address. It is followed by a single data byte (exception: 11tx Occc requires no data byte). The communication can include a checksum byte. When enabled, this byte follows the last valid byte. Either power on reset or software reset (SftwrRst) disables the checksum mode. Writing to Register 11 enables or disables checksum mode.

On a read command, the device responds with the data byte and the checksum byte. If the checksum is not desired, setting  $\overline{CS}$  to high terminates the transmission.

Multiple commands can be chained by holding CS low and sending the additional commands after the checksum byte (if checksum is disabled, send a dummy byte). In this mode, read and write instructions can be mixed.

This interface allows clock rates up to 10MHz. Such high clock rates require careful board layout, short wire lengths, and low parasitic capacitance and inductance. Observe delays and distortion generated from isolation couplers. External drivers may be required to drive long and terminated cables.

www.ti.com

# COMMAND STRUCTURE AND REGISTER OVERVIEW

Bit 7 is the most significant bit (MSB); bit 0 is the least significant bit (LSB). Binary numbers are denoted with 'b'. 'aaaa' is used to denote the encoded register pointer, 0000b to 1111b. 'T' denotes the buffer trigger bit. Writing to unassigned bits is ignored, but it is recommend to write a '0' for all unassigned bits. PGA280 registers, addresses, and functional information are summarized in the Register Map (Table 1).

# Command Byte

#### 01T0 aaaa dddd dddd: Write

Write 'dddd dddd' to internal PGA280 register at address aaaa

#### 1000 aaaa 0000 0000: Read

Read from specified internal PGA280 register at address *aaaa* [no BUFT on read]. The number of trailing zeros provides the clock for reading data. 16 SCLK pulses are required when reading the data byte plus checksum.

#### 00T0 aaaa:

Factory-reserved commands.

#### 11T0 0ccc: Direct CS Command

Controls  $\overline{CS}$  to pin (all pins are  $\overline{CS}$ -capable, but not simultaneously; only one at a time) for ccc = 0 to 6, corresponding to GPIO0 to GPIO6, if  $\overline{CS}$  mode is activated.

Within the command byte, T = 1 triggers the current buffer (BUF). Each command is terminated with setting  $\overline{CS}$  to high; commands can be chained within a period of  $\overline{CS}$  active low, but require a checksum byte, or a dummy byte when checksum mode is disabled.

#### NOTE

BUF cannot be triggered during a read command.

Here are several examples (discrete commands):

#### **Read Register 3:**

Send 0x8300; response: 0xzz19 (this value is the initial setting of BUFTIM).

The first byte zz contains the line state (3-state) of SDO. The second byte is data.

### NOTE

The PGA280 sends the CHKsum, if clocks are available while  $\overline{\text{CS}}$ : Send 0x830000. Response: 0xzz1937

#### Write Register 0:

Send 0x4018; set gain to 1V/V.

#### Write Register 4:

Send 0x44FF; reset all error flags.

Read Register 4:

Send 0x8400; response: 0xzz00 (no error flags set).

# Extended CS

The PGA280 can generate an extended chip select (ECS) for other devices that are connected to the same SPI wires: SDO, SDI, and SCLK. This ECS signal redirects the SPI communication to the connected device, while the PGA280 ignores data and SCLK. The CS signal to the PGA280 must stay low during such communication; as soon as CS returns high, SPI communication is terminated. See the *GPIO Operation Mode* section for details.

| REGISTER<br>(Decimal,<br>[Hex]) <sup>(2)</sup> | aaaa<br>(Binary) | R/W | B7           | B6            | В5                | В4            | B3                  | B2            | B1             | В0                 | DESCRIPTION                                       | RESET<br>VALUES <sup>(3)</sup> |

|------------------------------------------------|------------------|-----|--------------|---------------|-------------------|---------------|---------------------|---------------|----------------|--------------------|---------------------------------------------------|--------------------------------|

| 0                                              | 0000             | W/R | G4           | G3            | G2                | G1            | G0                  | MUX2          | MUX1           | MUX0               | Gain and optional MUX register                    | 0000 0000b                     |

| 1                                              | 0001             | W   |              |               |                   |               |                     |               |                | SftwrRst<br>Note2x | Write-only register, soft reset, write 1          | 0000 0000b                     |

| 2                                              | 0010             | W/R |              | CP6           | CP5               | CP4           | CP3                 | CP2           | CP1            | CP0                | SPI-MODE selection to GPIO-pin                    | 0000 0000b                     |

| 3                                              | 0011             | W/R |              |               | BUFTIM5           | BUFTIM<br>4   | <b>BUFTIM3</b>      | BUFTIM<br>2   | BUFTIM1        | BUFTIM<br>0        | Set BUF time-out                                  | 0001 1001b                     |

| 4                                              | 0100             | W/R | CHKerr       | IARerr        | BUFA              | ICAerr        | EF                  | OUTerr        | GAINerr        | lOVerr             | Error Register; reset error bit: write 1          | 0000 0000b                     |

| 5                                              | 0101             | W/R |              | GPIO6         | GPIO5             | GPIO4         | GPIO3               | GPIO2         | GPIO1          | GPIO0              | GPIO Register Data force out or sense             | 0000 0000b                     |

| 6                                              | 0110             | W/R |              | SW-A1         | SW-A2             | SW-B1         | SW-B2               | SW-C1         | SW-C2          | SW-D12             | Input switch control                              | 0110 0000b                     |

| 7                                              | 0111             | W/R |              |               |                   |               | SW-F1               | SW-F2         | SW-G1          | SW-G2              | Input switch control                              | 0000 0000b                     |

| 8                                              | 1000             | W/R |              | DIR6          | DIR5              | DIR4          | DIR3                | DIR2          | DIR1           | DIR0               | Configure pin to $out = 1$ or $in = 0$            | 0000 0000b                     |

| 9                                              | 1001             | W/R |              | ECS6          | ECS5              | ECS4          | ECS3                | ECS2          | ECS1           | ECS0               | Extended $\overline{CS}$ mode (1 = enable)        | 0000 0000b                     |

| 10 [A]                                         | 1010             | W/R | MUX-D<br>dis | IARerr<br>dis | BUFAPol<br>at pin | ICAerr<br>dis | ED BUFA<br>suppress | OUTerr<br>dis | GAINerr<br>dis | IOVerr<br>dis      | Various configuration settings                    | 0000 0000b                     |

| 11 [B]                                         | 1011             | W/R | LTD          |               | FLGTIM3           | FLGTIM<br>2   | FLGTIM1             | FLGTIM<br>0   | Reserved       | CHKsu<br>mE        | Various configuration settings                    | 0001 0000b                     |

| 12 [C]                                         | 1100             | W/R | OSCout       | SYNCin        | BUFAout           | BUFTin        | EFout               | MUX2          | MUX1           | MUX0               | Special function register                         | 0000 0000b                     |

|                                                | PIN              |     |              | GPIO6         | GPIO5             | GPIO4         | GPIO3               | GPIO2         | GPIO1          | GPIO0              | Register bit reference to GPIO pin <sup>(4)</sup> |                                |

# Table 1. REGISTER MAP<sup>(1)</sup>

(1) Blank register bits are ignored and undefined.

(2) Registers 13 to 15 are for test purposes; read-only.

(3) Power-on reset values are SftwrRst values.

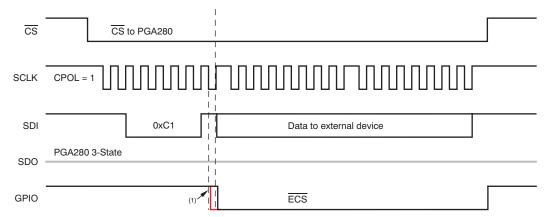

(4) Details for GPIO pin assignments are shown in Figure 54.

www.ti.com

#### SPI Timing Diagrams (Read and Write)

# (SCLK—Data—CS)

# Figure 52. Write (to Device) Timing (GPX: Command Decoding); No Checksum Enabled. With Checksum, Command Decoding Occurs After 24th Falling Edge of SCLK

|      |   |     |    |    |    |    |    |    |          | _   | _         | _         |     |     |     |     |     | - |

|------|---|-----|----|----|----|----|----|----|----------|-----|-----------|-----------|-----|-----|-----|-----|-----|---|

| SDO  | Z |     |    |    |    | Z  |    |    |          | DO7 | DO6       | DO5       | DO4 | DO3 | DO2 | DO1 | DO0 | z |

|      |   |     |    |    |    |    |    |    |          |     |           |           |     |     |     |     |     |   |

| SDI  |   | CB7 | B6 | B5 | B4 | A3 | A2 | A1 | A0       | х   | х         | х         | х   | х   | х   | х   | х   |   |

|      |   |     |    | -  |    |    |    |    | -        | _   | -         | -         |     |     | -   |     | -   |   |

| SCLK |   |     |    |    |    |    |    |    |          |     | $\square$ | $\square$ |     |     |     |     |     |   |

|      |   |     |    |    |    |    |    |    |          |     |           |           |     |     |     |     |     |   |

| CS   |   |     |    |    |    |    |    |    |          |     |           |           |     |     |     |     |     |   |

|      |   |     |    |    |    |    |    |    |          |     |           |           |     |     |     |     |     | - |

| GPX  | - |     |    |    |    |    |    |    | Ì        |     |           |           |     |     |     |     |     |   |

|      |   |     |    |    |    |    |    | Sa | ampled H | ere |           |           |     |     |     |     |     |   |

Figure 53. Read (From Register) Timing (GPX: Command Decoding); No Checksum Enabled. Falling Edge of SCLK Controls Logic

#### **GPIO Pin Reference**

As shown in Figure 54, the PGA280 has seven multi-function pins labeled GPIO0 through GPIO6. These pins can function as general purpose input-output (GPIO) pins either to read a digital input or to output a digital signal as an interrupt or control. GPIO functions are controlled through Register 5 and Register 8.

These pins can also be programmed to have additional special functions for the PGA280. Each of these seven pins can be used as an output for the extended chip select function (ECS), using the PGA280 to redirect the SPI communications to other connected devices.  $\overline{CS}$  Configuration Mode is enabled through Register 9. Additionally, Register 2 controls the clock polarity (CP) of each ECS. For each bit set to '1', a positive edge of SCLK follows  $\overline{CS}$  (CP = 0); for each bit set to '0', a negative edge of SCLK follows  $\overline{CS}$  (CP = 1).

Together with the GPIO and ECS functions, the seven pins can perform more specialized input and output tasks as controlled by Register 12, the Special Functions Register.

GPIO0, GPIO1, and GPIO2 can be used to control an external multiplexer. If the MUX function is enabled in the first three bits of Register 12, the output value on the MUX pins is controlled through Register 0. This configuration allows for simultaneous control of the PGA280 gain and external multiplexer settings by writing to a single register.

GPIO3 can be used to output an error flag. As with bit 3 of Register 4, this option would be the logical OR of the error bits in Register 10 (IARerr, ICAerr, OUTerr, GAINerr, and IOVerr).

GPIO4 can be used as an input to trigger the current buffer. The low-to-high edge of a pulse starts the buffer with a delay of three to four clock cycles. If held high, the buffer [BUFA] remains active. It is extended by a minimum of three to four clock cycles in addition to the time set with FLAGTIM.

GPIO5 can be configured as an output to indicate a buffer active condition. The polarity is controlled by BUFApol of bit 5 in Register 10.

GPIO6 can be configured as either an output or an input with the Special Functions Register. With Bit 7, OSCOUT connects the internal oscillator to GPIO6. With Bit 6, SYNCIN allows an external oscillator to provide the master clock to the PGA280.

To use any of these functions, Register 8 must first be set to '0' for input or to '1' for an output (for GPIO, ECS, or special function).

Once set, any 1s in Register 9 supersede the GPIO function for the related pin, allowing for  $\overline{CS}$  configuration.

Likewise, any 1s in Register 12 supersede the GPIO function and  $\overline{CS}$  configuration, allowing for any of the pin-specific special functions to operate.

# **REGISTER INFORMATION**

# **REGISTER DETAILS**

# Register 0: Gain and External MUX Address (Read = 0x8000; Write with BUF Off = 0x40, Write with BUF On = 0x60)

|           | 61 = 6000 |    |    |    |    |      |      |      |  |  |  |  |

|-----------|-----------|----|----|----|----|------|------|------|--|--|--|--|

| Bit #     | D7        | D6 | D5 | D4 | D3 | D2   | D1   | D0   |  |  |  |  |

| Bit Name  | G4        | G3 | G2 | G1 | G0 | MUX2 | MUX1 | MUX0 |  |  |  |  |

| POR Value | 0         | 0  | 0  | 0  | 0  | 0    | 0    | 0    |  |  |  |  |

#### **Bit Descriptions:**

G4: Output stage gain setting. This setting is independent of the gain selected in the input stage and acts as a multiplication factor to the input gain.

0 = 1V/V output gain (power-on default)

1 = 1.375V/V output gain (= 1%V/V)

G[3:0]: Input stage gain setting. Refer to Table 2.

MUX[2:0]: These ports can be used to control an external multiplexer.

# Table 2. INPUT STAGE GAIN SETTINGS

| G3 | G2 | G1 | G0 | Gain     |

|----|----|----|----|----------|

| 0  | 0  | 0  | 0  | 1/8      |

| 0  | 0  | 0  | 1  | 1/4      |

| 0  | 0  | 1  | 0  | 1/2      |

| 0  | 0  | 1  | 1  | 1        |

| 0  | 1  | 0  | 0  | 2        |

| 0  | 1  | 0  | 1  | 4        |

| 0  | 1  | 1  | 0  | 8        |

| 0  | 1  | 1  | 1  | 16       |

| 1  | 0  | 0  | 0  | 32       |

| 1  | 0  | 0  | 1  | 64       |

| 1  | 0  | 1  | 0  | 128      |

| 1  | 0  | 1  | 1  | Reserved |

| 1  | 1  | 0  | 0  | Reserved |

| 1  | 1  | 0  | 1  | Reserved |

| 1  | 1  | 1  | 0  | Reserved |

| 1  | 1  | 1  | 1  | Reserved |

SBOS487A – JUNE 2009 – REVISED SEPTEMBER 2009

#### Register 1: Software Reset Register (Write = 0x4101; Write with Checksum = 0x4101DD)

| Bit #     | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0       |

|-----------|----|----|----|----|----|----|----|----------|

| Bit Name  | _  | _  | —  | —  | —  | —  | _  | SftwrRst |

| POR Value | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0        |

#### **Bit Descriptions:**

SftwrRst: Software Reset.

Setting this bit to '1' generates a system reset that has the same effect as a power-on reset. All registers are reset to the respective default values; this bit self-clears.

#### Register 2: SPI: MODE Selection to GPIO-Pin (Read = 0x8200, Write = 0x012)

|           | U  |     |     |     |     | ,   |     |     |

|-----------|----|-----|-----|-----|-----|-----|-----|-----|

| Bit #     | D7 | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| Bit Name  | _  | CP6 | CP5 | CP4 | CP3 | CP2 | CP1 | CP0 |

| POR Value | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

#### **Bit Descriptions:**

CP[6:0] SPI mode1 or mode2 can be configured for each individual  $\overline{\text{ECS}}$  (extended CS) output if activated in Register 9. See  $\overline{\text{CS}}$  *Mode* in GPIO Operation Mode for details. CP6 controls ECS6, for example. For SPI mode1, set the respective bit to '1': a positive edge of SCLK follows  $\overline{\text{CS}}$  (Clock Polarity, CP = 0). For SPI mode2, set the respective bit to '0': a negative edge of SCLK follows  $\overline{\text{CS}}$  (CP = 1). See also Figure 56.

#### Register 3: BUF Timeout Register (Read = 0x8300, Write = 0x43)