# LM94022 Evaluation Board User's Guide Table of Contents

| Table of Contents                             | 2 |

|-----------------------------------------------|---|

| References                                    | 3 |

| 1.0 Introduction                              | 4 |

| 1.1 Block Diagram                             | 4 |

| 2.0 Quick Start                               | 5 |

| 2.1 Quick Start Diagram                       | 5 |

| 3.0 Functional Description                    | 6 |

| 3.1 LM95022 Evaluation Board Connection Table | 6 |

| 4.0 Electrical and Mechanical Specifications  | 7 |

| 4.1 Electrical Specifications                 | 7 |

| 4.2 Electrical Schematic                      | 7 |

| 4.3 Evaluation Board Layout                   | 8 |

| 4.4 Bill of Materials                         | 9 |

| 4.5 Mechanical Specifications                 | 9 |

## LM94022 Evaluation Board User's Guide

## References

1. "LM94022 1.5V, SC70, Multi-Gain Analog Temperature Sensor with Class-AB Output" datasheet.

The latest copy of the LM94022 datasheet can be obtained by going to the National Semiconductor website<u>www.national.com</u>, by searching on "LM94022", and then downloading the LM94022.pdf file.

## **1.0 Introduction**

The LM94022 Evaluation Board offers the user a convenient way to experiment with the operation of the LM94022 Multi-Gain Temperature Sensor.

There are jumpers that allow the selection of the temperature-to-output voltage gain. The default condition for the Gain Select 0 jumper (JP1) is for the shunt to be across pins 2 and 3. The default condition for the Gain Select 1 jumper (JP2) is also for the shunt to be across pins 2 and 3. By default, jumper JP6 is installed, connecting the LM94022 output to pin JP4. The evaluation board can be configured with an output capacitor by installing C2 and shorting jumper JP7. Resistor R1 can be installed and JP6 removed to insert it in series with the output. See the datasheet for recommended values for R1 and C2.

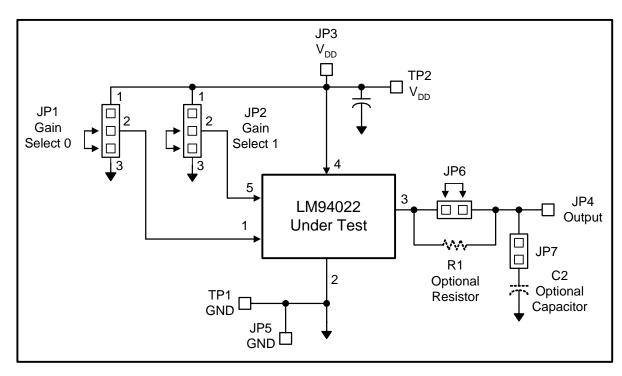

The block diagram below shows the jumpers in the default condition.

4

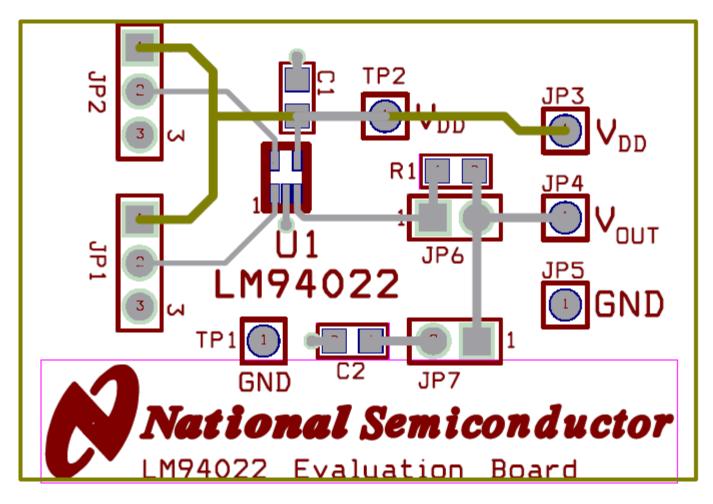

### 1.1 Block Diagram

# 2.0 Quick Start

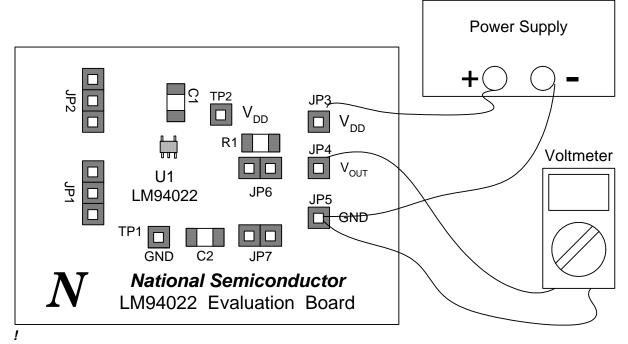

The diagram below shows how the LM94022 is connected in a typical bench test configuration.

Before applying power directly to the LM94022 Evaluation Board, make sure that the voltage is between +1.5 VDC and +5.5 VDC. Also make sure that JP1 and JP2 are jumpered for the desired gain. Make sure that JP6 is jumpered for a direct connection to the output.

Apply power to the LM94022 evaluation board. Measure the output voltage connected between to output pin (JP4) and ground.

5

#### 2.1 Quick Start Diagram

# **3.0 Functional Description**

Selecting the LM94022's various output gains is described in detail in the LM94022 datasheet.

The inversely proportional output voltage vs temperature characteristic has different slopes depending on the gain select. See the datasheet for details.

### 3.1 LM94022 Evaluation Board Connection Table

| Connector<br>Label | Connector<br>Name       | Pin<br>Number | Description                                                                                                |  |

|--------------------|-------------------------|---------------|------------------------------------------------------------------------------------------------------------|--|

|                    |                         | 1 - 2         | If pins 1 and 2 are jumpered then Gain Select 0 is connected to $V_{DD}$ .                                 |  |

| JP1 Gain Select 0  |                         | 2 - 3         | If Pins 2 and 3 are jumpered then Gain Select 0 is connected to GND. Default: pins 2 and 3 are jumpered.   |  |

| JP2 Gai            |                         | 1 -2          | If pins 1 and 2 are jumpered then Gain Select 1 is connected to $V_{DD}$ .                                 |  |

|                    | Gain Select 1           | 2 - 3         | If Pins 2 and 3 are jumpered then Gain Select 1 is connected to GND. Default: pins 2 and 3 are jumpered.   |  |

| JP3                | $V_{DD}$ Input          |               | Supply +1.5 to 5.5 VDC to this pin.                                                                        |  |

| JP4                | V <sub>OUT</sub> Output |               | This is the output pin. See the schematic and description within this document.                            |  |

| JP5                | GND Input               |               | This is Power Supply return for $V_{DD}$ Input (JP3).                                                      |  |

| JP6                | Series Output           | 1 - 2         | Jumper is installed across pins 1 and 2 by default.<br>Otherwise resistor R1 is in series with the output. |  |

| JP7                | Parallel<br>Output      | 1 - 2         | Jumper is <b>not</b> installed across pins 1 and 2 by default. Otherwise capacitor C2 shunts the output.   |  |

| TP1                | Test Point 1            |               | This is the GND test point                                                                                 |  |

| TP2                | Test Point 2            |               | This is the V <sub>DD</sub> test point.                                                                    |  |

## 4.0 Electrical and Mechanical Specifications

#### **4.1 Electrical Specifications**

| Power Requirements                                                     |             |

|------------------------------------------------------------------------|-------------|

| The Board uses the +1.5 VDC to +5.5 VDC and GND lines from an external | +1.5 VDC to |

| low-noise power supply.                                                | +5.5 VDC    |

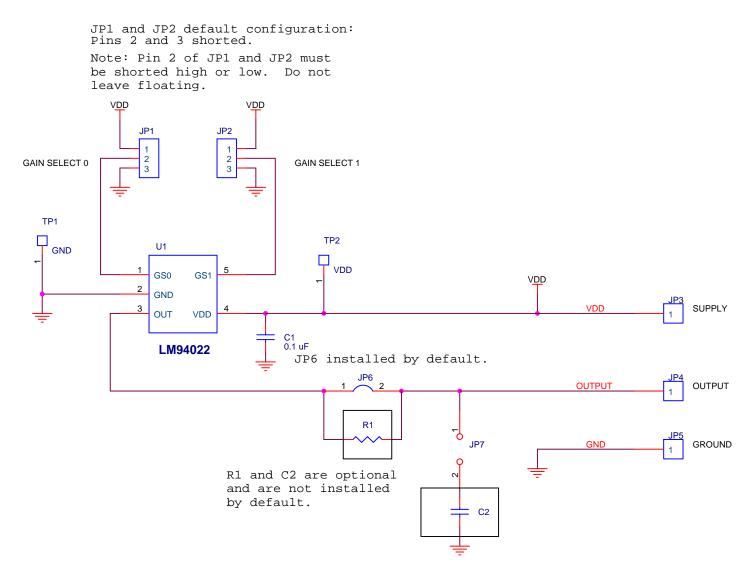

#### **4.2 Electrical Schematic**

Figure 4.2 Schematic Diagram of the LM94022 Evaluation Board

## 4.3 Evaluation Board Layout

Figure 4.3 Layout diagram of the LM94022 Evaluation Board

#### 4.4 Bill of Materials for LM94022 Evaluation Board

| Item | Quantity | Reference     | Part                                                        |

|------|----------|---------------|-------------------------------------------------------------|

| 1    | 1        | C1            | Capacitor, Ceramic, 0.1uF                                   |

| 2    | 1        | C2            | Capacitor (not stuffed)                                     |

| 3    | 2        | JP1, JP2      | Header, 1X3, 0.1 in centers                                 |

| 4    | 3        | JP3, JP4, JP5 | Header, 1X1, 0.1 in centers                                 |

| 5    | 2        | JP6, JP7      | Header, 1X2, 0.1 in centers                                 |

| 6    | 3        |               | Shunts, 1X2, 0.1 in centers,                                |

| 7    | 1        | R1            | Resistor, (not stuffed)                                     |

| 8    | 2        | TP1-TP2       | Test Points (1X1 Headers)                                   |

| 9    | 1        | U1            | LM94022CIMF Device Under Test (DUT)                         |

| 10   | 1        |               | Circuit Board, Fabricated, LM94022 Evaluation Board, Rev. 1 |

#### 4.5 Mechanical Specifications

| 4.5.1 Operating Mechanical and Environmental Specifications |

|-------------------------------------------------------------|

|-------------------------------------------------------------|

|             | Minimum | Typical | Maximum |

|-------------|---------|---------|---------|

| Temperature | 0°C     | 25°C    | 70°C    |

#### 4.5.2 Evaluation Board Basic Dimensions

#### 4.5.3 Electrostatic Discharge (ESD) Precautions

The user shall use ESD precautions as specified in National Semiconductor ESD document (SC)CSI-3-038 available through www.national.com.

BY USING THIS PRODUCT, YOU ARE AGREEING TO BE BOUND BY THE TERMS AND CONDITIONS OF NATIONAL SEMICONDUCTOR'S END USER LICENSE AGREEMENT. DO NOT USE THIS PRODUCT UNTIL YOU HAVE READ AND AGREED TO THE TERMS AND CONDITIONS OF THAT AGREEMENT. IF YOU DO NOT AGREE WITH THEM, CONTACT THE VENDOR WITHIN TEN (10) DAYS OF RECEIPT FOR INSTRUCTIONS ON RETURN OF THE UNUSED PRODUCT FOR A REFUND OF THE PURCHASE PRICE PAID, IF ANY.

The LM94022 Evaluation Boards are intended for product evaluation purposes only and are not intended for resale to end consumers, are not authorized for such use and are not designed for compliance with European EMC Directive 89/336/EEC, or for compliance with any other electromagnetic compatibility requirements.

National Semiconductor Corporation does not assume any responsibility for use of any circuitry or software supplied or described. No circuit patent licenses are implied.

## LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user. 2. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### BANNED SUBSTANCE COMPLIANCE

National Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

National Semiconductor Corporation Americas Customer Support Center Tel: 1-800-272-9959 Email: new.feedback@nsc.com

National Semiconductor Europe

Customer Support Center

Fax: +49 (0) 1 80-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 699508 6208

English Tel: +49 (0) 870 24 0 2171

Français Tel: +49 (0) 141 91 8790

National Semiconductor Asia Pacific Customer Support Center

ap.support@nsc.com

Email:

National Semiconductor Japan Customer Support Center Tel: 81-3-5639-7560 Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com

National does not assume any responsibility for any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.