SBAS094B - MAY 2002

# Speed 12-Bit, 165MSPS DIGITAL-TO-ANALOG CONVERTER

# **FEATURES**

SINGLE +5V OR +3V OPERATION

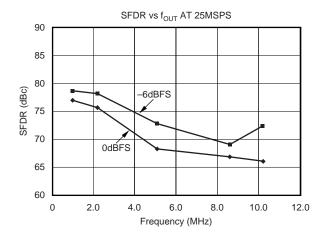

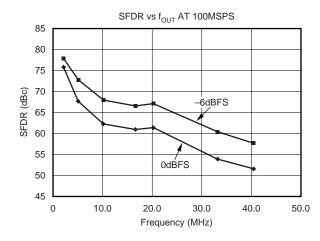

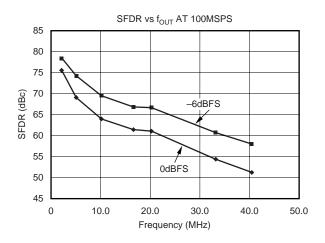

HIGH SFDR: 5MHz Output at 100MSPS: 67dBc

● LOW GLITCH: 3pV-s

● LOW POWER: 170mW at +5V

• INTERNAL REFERENCE:

Optional Ext. Reference

Adjustable Full-Scale Range

**Multiplying Option**

# **DESCRIPTION**

The DAC902 is a high-speed, Digital-to-Analog Converter (DAC) offering a 12-bit resolution option within the *SpeedPlus* Family of high-performance converters. Featuring pin compatibility among family members, the DAC908, DAC900, and DAC904 provide a component selection option to an 8-, 10-, and 14-bit resolution, respectively. All models within this family of DACs support update rates in excess of 165MSPS with excellent dynamic performance, and are especially suited to fulfill the demands of a variety of applications.

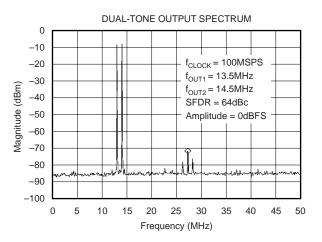

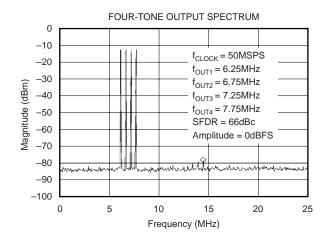

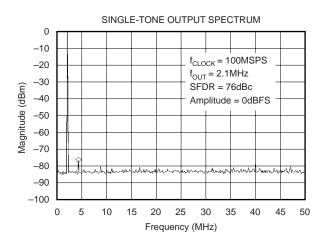

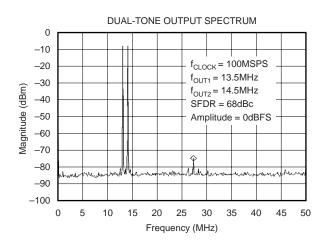

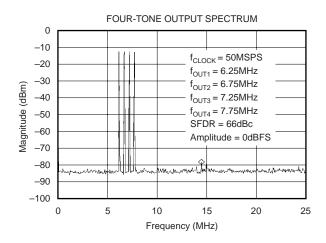

The advanced segmentation architecture of the DAC902 is optimized to provide a high Spurious-Free Dynamic Range (SFDR) for single-tone, as well as for multi-tone signals—essential when used for the transmit signal path of communication systems.

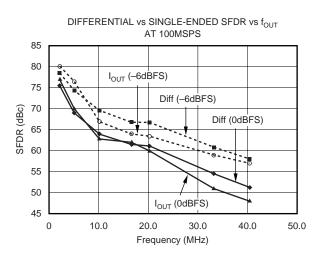

The DAC902 has a high impedance ( $200k\Omega$ ) current output with a nominal range of 20mA and an output compliance of up to 1.25V. The differential outputs allow for both a differential or single-ended analog signal interface. The close matching of the current outputs ensures superior dynamic performance in the differential configuration, which can be implemented with a transformer.

Utilizing a small geometry CMOS process, the monolithic DAC902 can be operated on a wide, single-supply range of +2.7V to +5.5V. Its low power consumption allows for use in portable and battery-operated systems. Further optimization can be realized by lowering the output current with the adjustable full-scale option.

### **APPLICATIONS**

- COMMUNICATION TRANSMIT CHANNELS: WLL, Cellular Base Station Digital Microwave Links Cable Modems

- WAVEFORM GENERATION:

Direct Digital Synthesis (DDS)

Arbitrary Waveform Generation (ARB)

- MEDICAL/ULTRASOUND

- HIGH-SPEED INSTRUMENTATION AND CONTROL

- VIDEO, DIGITAL TV

For noncontinuous operation of the DAC902, a power-down mode results in only 45mW of standby power.

The DAC902 comes with an integrated 1.24V bandgap reference and edge-triggered input latches, offering a complete converter solution. Both +3V and +5V CMOS logic families can be interfaced to the DAC902.

The reference structure of the DAC902 allows for additional flexibility by utilizing the on-chip reference, or applying an external reference. The full-scale output current can be adjusted over a span of 2mA to 20mA, with one external resistor, while maintaining the specified dynamic performance.

The DAC902 is available in the SO-28 and TSSOP-28 packages.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

#### **ABSOLUTE MAXIMUM RATINGS**

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

|------------------------------------------------------|

| •                                                    |

|                                                      |

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### PACKAGE/ORDERING INFORMATION

| PRODUCT | PACKAGE  | PACKAGE<br>DRAWING<br>NUMBER | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER <sup>(1)</sup> | TRANSPORT<br>MEDIA |

|---------|----------|------------------------------|-----------------------------------|--------------------|-----------------------------------|--------------------|

| DAC902U | SO-28    | 217                          | -40°C to +85°C                    | DAC902U            | DAC902U                           | Rails              |

| "       | "        | "                            | II .                              | "                  | DAC902U/1K                        | Tape and Reel      |

| DAC902E | TSSOP-28 | 360                          | -40°C to +85°C                    | DAC902E            | DAC902E                           | Rails              |

| "       | "        | "                            | II .                              | "                  | DAC902E/2K5                       | Tape and Reel      |

NOTE: (1) Models with a slash (/) are available only in Tape and Reel in the quantities indicated (e.g., /2K5 indicates 2500 devices per reel). Ordering 2500 pieces of "DAC902E/2K5" will get a single 2500-piece Tape and Reel.

#### **DEMO BOARD ORDERING INFORMATION**

| PRODUCT            | DEMO BOARD<br>ORDERING NUMBER | COMMENT                                                                                                                                         |

|--------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| DAC902U<br>DAC902E | DEM-DAC90xU<br>DEM-DAC902E    | Populated evaluation board without the DAC. Order sample of desired DAC90x model separately.  Populated evaluation board including the DAC902E. |

# **ELECTRICAL CHARACTERISTICS**

At  $T_A = \text{full}$  specified temperature range,  $+V_A = +5V$ ,  $+V_D = +5V$ , differential transformer coupled output,  $50\Omega$  doubly terminated, unless otherwise specified.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                     |                   | DAC902U/E                                |               |                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------|------------------------------------------|---------------|-----------------------------------------|

| PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CONDITIONS                                                                          | MIN               | TYP                                      | MAX           | UNITS                                   |

| RESOLUTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                     |                   | 12                                       |               | Bits                                    |

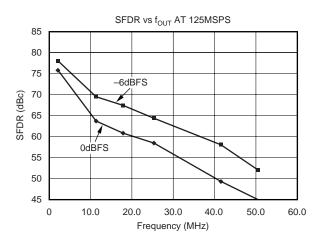

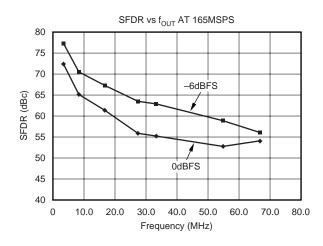

| OUTPUT UPDATE RATE Output Update Rate (f <sub>CLOCK</sub> ) Full Specified Temperature Range, Operating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.7V to 3.3V<br>4.5V to 5.5V<br>Ambient, T <sub>A</sub>                             | 125<br>165<br>–40 | 165<br>200                               | +85           | MSPS<br>MSPS<br>°C                      |

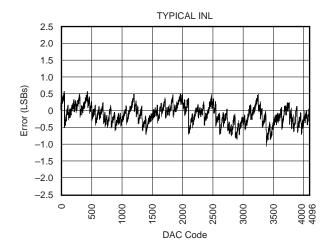

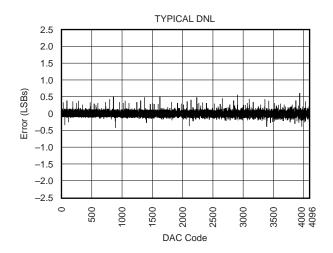

| STATIC ACCURACY <sup>(1)</sup> Differential Nonlinearity (DNL) Integral Nonlinearity (INL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $T_A = +25^{\circ}\text{C}$<br>$f_{CLOCK} = 25\text{MSPS}, f_{OUT} = 1.0\text{MHz}$ | -1.75<br>-2.5     | ±0.5<br>±1.0                             | +1.75<br>+2.5 | LSB<br>LSB                              |

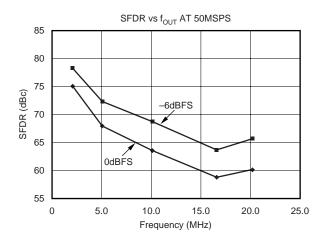

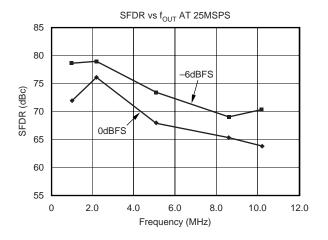

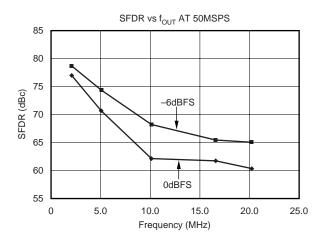

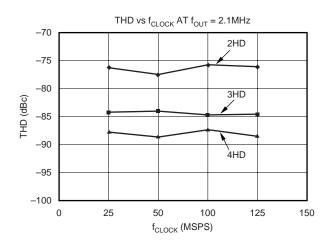

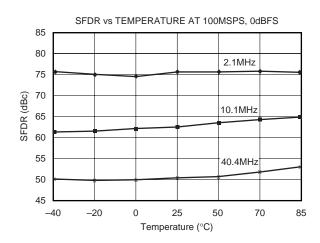

| DYNAMIC PERFORMANCE  Spurious-Free Dynamic Range (SFDR)  fout = 1MHz, fclock = 25MSPS  fout = 2.1MHz, fclock = 50MSPS  fout = 5.04MHz, fclock = 50MSPS  fout = 5.04MHz, fclock = 100MSPS  fout = 20.2MHz, fclock = 100MSPS  fout = 20.2MHz, fclock = 125MSPS  fout = 25.3MHz, fclock = 125MSPS  fout = 27.4MHz, fclock = 165MSPS  fout = 27.4MHz, fclock = 165MSPS  Spurious-Free Dynamic Range within a Window  fout = 5.04MHz, fclock = 50MSPS  fout = 5.04MHz, fclock = 100MSPS  Total Harmonic Distortion (THD)  fout = 2.1MHz, fclock = 50MSPS  fout = 2.1MHz, fclock = 125MSPS  Two Tone  fout = 13.5MHz, fout = 125MSPS | T <sub>A</sub> = +25°C<br>To Nyquist<br>2MHz Span<br>4MHz Span                      | 71                | 77 75 68 67 61 61 57 60 53 80 80 -74 -75 |               | dBc |

# **ELECTRICAL CHARACTERISTICS (Cont.)**

At  $T_A$  = full specified temperature range,  $+V_A$  = +5V,  $+V_D$  = +5V, differential transformer coupled output,  $50\Omega$  doubly terminated, unless otherwise specified.

|                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                  |                                                       | DAC902U/E                                         |                                                        |                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------|

| PARAMETER                                                                                                                                                                                                                                                                                            | CONDITIONS                                                                                                                                                                                                                                                                       | MIN                                                   | TYP                                               | MAX                                                    | UNITS                                                                                   |

| DYNAMIC PERFORMANCE (Cont.) Output Settling Time <sup>(2)</sup> Output Rise Time <sup>(2)</sup> Output Fall Time <sup>(2)</sup> Glitch Impulse                                                                                                                                                       | to 0.1%<br>10% to 90%<br>10% to 90%                                                                                                                                                                                                                                              |                                                       | 30<br>2<br>2<br>2<br>3                            |                                                        | ns<br>ns<br>ns<br>pV-s                                                                  |

| DC-ACCURACY Full-Scale Output Range <sup>(3)</sup> (FSR) Output Compliance Range Gain Error Gain Error Gain Drift Offset Error Offset Drift Power-Supply Rejection, +V <sub>A</sub> Power-Supply Rejection, +V <sub>D</sub> Output Noise Output Resistance Output Capacitance                        | All Bits High, I <sub>OUT</sub> With Internal Reference With External Reference With Internal Reference With Internal Reference With Internal Reference With Internal Reference  I <sub>OUT</sub> = 20mA, R <sub>LOAD</sub> = 50Ω  I <sub>OUT</sub> , I <sub>OUT</sub> to Ground | 2.0<br>-1.0<br>-10<br>-10<br>-0.025<br>-0.2<br>-0.025 | ±1<br>±2<br>±120<br>±0.1<br>50<br>200<br>12       | 20.0<br>+1.25<br>+10<br>+10<br>+0.025<br>+0.2<br>+0.25 | mA<br>V<br>%FSR<br>%FSR<br>ppmFSR/°C<br>%FSR/<br>pFSR/V<br>%FSR/V<br>pA/√Hz<br>kΩ<br>pF |

| REFERENCE Reference Voltage Reference Tolerance Reference Voltage Drift Reference Output Current Reference Input Resistance Reference Input Compliance Range Reference Small-Signal Bandwidth <sup>(4)</sup>                                                                                         |                                                                                                                                                                                                                                                                                  | 0.1                                                   | +1.24<br>±5<br>±50<br>10<br>1                     | 1.25                                                   | V<br>%<br>ppmFSR/°C<br>μA<br>MΩ<br>V<br>MHz                                             |

| DIGITAL INPUTS Logic Coding Latch Command Logic High Voltage, V <sub>IH</sub> Logic Low Voltage, V <sub>IL</sub> Logic High Voltage, V <sub>IL</sub> Logic Low Voltage, V <sub>IL</sub> Logic Low Voltage, V <sub>IL</sub> Logic High Current I <sub>IH</sub> (5) Logic Low Current, I <sub>IL</sub> | $+V_{D} = +5V$ $+V_{D} = +5V$ $+V_{D} = +3V$ $+V_{D} = +3V$ $+V_{D} = +5V$ $+V_{D} = +5V$                                                                                                                                                                                        | 3.5<br>2                                              | Straight Binary sing Edge of Cl 5 0 3 0 ±20 ±20 5 |                                                        | V<br>V<br>V<br>μΑ<br>μΑ<br>pF                                                           |

| POWER SUPPLY Supply Voltages $+V_A$ $+V_D$ Supply Current <sup>(6)</sup> $I_{VA}$ $I_{VA}$ , Power-Down Mode $I_{VD}$ Power Dissipation  Power Dissipation, Power-Down Mode Thermal Resistance, $\theta_{JA}$ SO-28 TSSOP-28                                                                         | +5V, I <sub>OUT</sub> = 20mA<br>+3V, I <sub>OUT</sub> = 2mA                                                                                                                                                                                                                      | +2.7<br>+2.7                                          | +5<br>+5<br>24<br>1.1<br>8<br>170<br>50<br>45     | +5.5<br>+5.5<br>30<br>2<br>15<br>230                   | V<br>V<br>MA<br>MA<br>MW<br>MW<br>MW                                                    |

NOTES: (1) At output  $I_{OUT}$ , while driving a virtual ground. (2) Measured single-ended into  $50\Omega$  Load. (3) Nominal full-scale output current is  $32 \cdot I_{REF}$ ; see Application Section for details. (4) Reference bandwidth depends on size of external capacitor at the BW pin and signal level. (5) Typically  $45\mu$ A for the PD pin, which has an internal pull-down resistor. (6) Measured at  $f_{CLOCK} = 50$ MSPS and  $f_{OUT} = 1.0$ MHz.

### **PIN CONFIGURATION**

### **PIN DESCRIPTIONS**

| PIN | DESIGNATOR        | DESCRIPTION                                                                   |

|-----|-------------------|-------------------------------------------------------------------------------|

| 1   | Bit 1             | Data Bit 1 (D11), MSB                                                         |

| 1   |                   | . "                                                                           |

| 2   | Bit 2             | Data Bit 2 (D10)                                                              |

| 3   | Bit 3             | Data Bit 3 (D9)                                                               |

| 4   | Bit 4             | Data Bit 4 (D8)                                                               |

| 5   | Bit 5             | Data Bit 5 (D7)                                                               |

| 6   | Bit 6             | Data Bit 6 (D6)                                                               |

| 7   | Bit 7             | Data Bit 7 (D5)                                                               |

| 8   | Bit 8             | Data Bit 8 (D4)                                                               |

| 9   | Bit 9             | Data Bit 9 (D3)                                                               |

| 10  | Bit 10            | Data Bit 10 (D2)                                                              |

| 11  | Bit 11            | Data Bit 11 (D1)                                                              |

| 12  | Bit 12            | Data Bit 12 (D0), LSB                                                         |

| 13  | NC                | No Connection                                                                 |

| 14  | NC                | No Connection                                                                 |

| 15  | PD                | Power Down, Control Input; Active                                             |

|     |                   | HIGH. Contains internal pull-down circuit;                                    |

| 16  | ĪNT/EXT           | may be left unconnected if not used.                                          |

| 16  | IN I/EAI          | Reference Select Pin; Internal ( = 0) or External ( = 1) Reference Operation. |

| 17  | REF <sub>IN</sub> | Reference Input/Ouput. See Applica-                                           |

|     |                   | tions section for further details.                                            |

| 18  | FSA               | Full-Scale Output Adjust                                                      |

| 19  | BW                | Bandwidth/Noise Reduction Pin:                                                |

|     |                   | Bypass with 0.1μF to +V <sub>A</sub> for Optimum                              |

|     | ACNID             | Performance.                                                                  |

| 20  | AGND              | Analog Ground                                                                 |

| 21  | I <sub>OUT</sub>  | Complementary DAC Current Output                                              |

| 22  | OUT               | DAC Current Output                                                            |

| 23  | BYP               | Bypass Node: Use 0.1μF to AGND                                                |

| 24  | +V <sub>A</sub>   | Analog Supply Voltage, 2.7V to 5.5V                                           |

| 25  | NC                | No Connection                                                                 |

| 26  | DGND              | Digital Ground                                                                |

| 27  | +V <sub>D</sub>   | Digital Supply Voltage, 2.7V to 5.5V                                          |

| 28  | CLK               | Clock Input                                                                   |

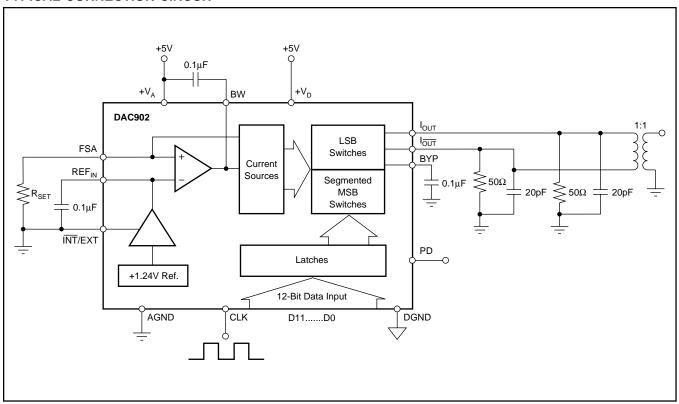

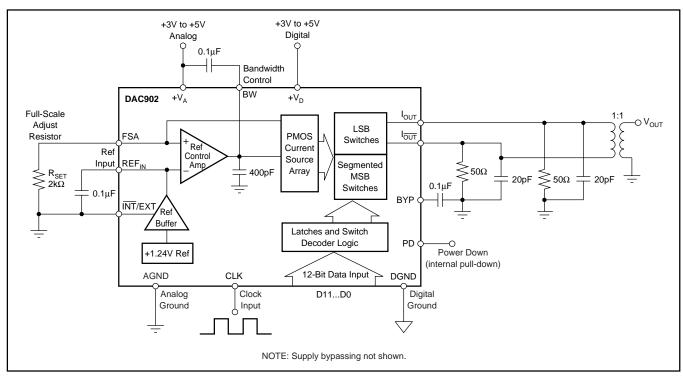

#### TYPICAL CONNECTION CIRCUIT

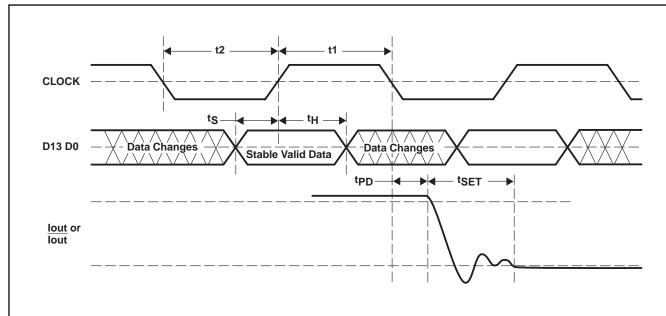

### **TIMING DIAGRAM**

| SYMBOL           | DESCRIPTION                  | MIN | TYP  | MAX | UNITS |

|------------------|------------------------------|-----|------|-----|-------|

| t <sub>1</sub>   | Clock Pulse HIGH Time        |     | 3.0  |     | ns    |

| t <sub>2</sub>   | Clock Pulse LOW Time         |     | 3.0  |     | ns    |

| t <sub>S</sub>   | Data Setup Time              |     | 1.0  |     | ns    |

| t <sub>H</sub>   | Data Hold Time               |     | 1.5  |     | ns    |

| t <sub>PD</sub>  | Propagation Delay Time       |     | 1    |     | ns    |

| t <sub>SET</sub> | Output Settling Time to 0.1% |     | 30.0 |     | ns    |

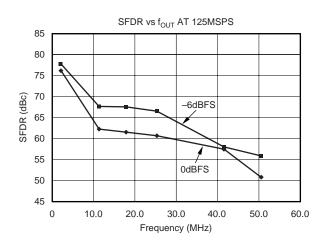

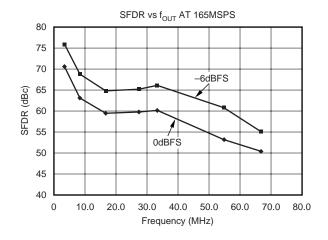

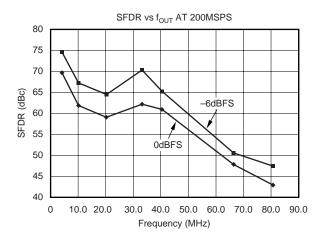

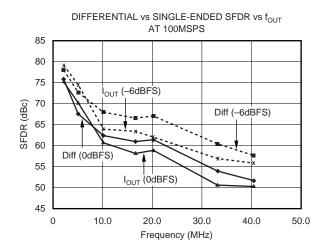

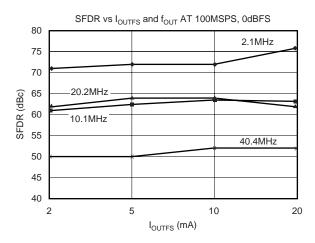

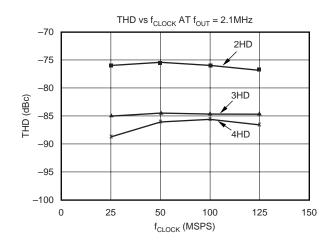

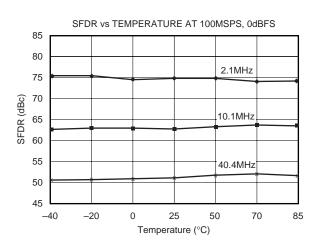

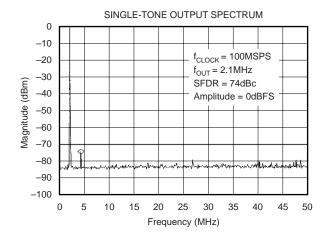

# TYPICAL CHARACTERISTICS: $V_D = V_A = +5V$

# TYPICAL CHARACTERISTICS: $V_D = V_A = +5V$ (Cont.)

# TYPICAL CHARACTERISTICS: $V_D = V_A = +5V$ (Cont.)

# TYPICAL CHARACTERISTICS: $V_D = V_A = +3V$

# TYPICAL CHARACTERISTICS: $V_D = V_A = +3V$ (Cont.)

# **APPLICATION INFORMATION**

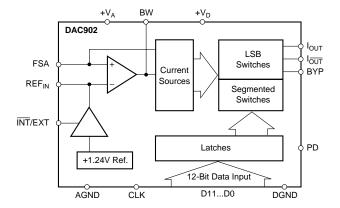

#### THEORY OF OPERATION

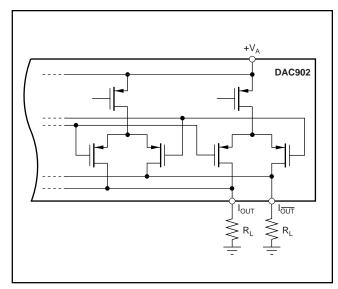

The architecture of the DAC902 uses the current steering technique to enable fast switching and a high update rate. The core element within the monolithic DAC is an array of segmented current sources that are designed to deliver a full-scale output current of up to 20mA, as shown in Figure 1. An internal decoder addresses the differential current switches each time the DAC is updated and a corresponding output current is formed by steering all currents to either output summing node,  $I_{OUT}$  or  $I_{\overline{OUT}}$ . The complementary outputs deliver a differential output signal that improves the dynamic performance through reduction of even-order harmonics, common-mode signals (noise), and double the peak-to-peak output signal swing by a factor of two, compared to single-ended operation.

The segmented architecture results in a significant reduction of the glitch energy, improves the dynamic performance (SFDR), and DNL. The current outputs maintain a very high output impedance of greater than  $200k\Omega$ .

The full-scale output current is determined by the ratio of the internal reference voltage (1.24V) and an external resistor,  $R_{\rm SET}$ . The resulting  $I_{\rm REF}$  is internally multiplied by a factor of 32 to produce an effective DAC output current that can range from 2mA to 20mA, depending on the value of  $R_{\rm SET}$ .

The DAC902 is split into a digital and an analog portion, each of which is powered through its own supply pin. The digital section includes edge-triggered input latches and the decoder logic, while the analog section comprises the current source array with its associated switches, and the reference circuitry.

#### DAC TRANSFER FUNCTION

The total output current,  $I_{OUTFS}$ , of the DAC902 is the summation of the two complementary output currents:

$$I_{OUTFS} = I_{OUT} + I_{\overline{OUT}}$$

(1)

The individual output currents depend on the DAC code and can be expressed as:

$$I_{OUT} = I_{OUTFS} \bullet (Code/4096) \tag{2}$$

$$I_{\overline{OUT}} = I_{OUTFS} \bullet (4095 - Code/4096) \tag{3}$$

where 'Code' is the decimal representation of the DAC data input word. Additionally,  $I_{OUTFS}$  is a function of the reference current  $I_{REF}$ , which is determined by the reference voltage and the external setting resistor,  $R_{SET}$ .

$$I_{OUTFS} = 32 \cdot I_{REF} = 32 \cdot V_{REF}/R_{SET}$$

(4)

In most cases the complementary outputs will drive resistive loads or a terminated transformer. A signal voltage will develop at each output according to:

$$V_{OUT} = I_{OUT} \cdot R_{LOAD}$$

(5)

$$V_{\overline{OUT}} = I_{\overline{OUT}} \bullet R_{LOAD}$$

(6)

FIGURE 1. Functional Block Diagram of the DAC902.

The value of the load resistance is limited by the output compliance specification of the DAC902. To maintain specified linearity performance, the voltage for  $I_{OUT}$  and  $I_{\overline{OUT}}$  should not exceed the maximum allowable compliance range.

The two single-ended output voltages can be combined to find the total differential output swing:

$$V_{\text{OUTDIFF}} = V_{\text{OUT}} - V_{\overline{\text{OUT}}} = \frac{(2 \bullet \text{Code} - 4095)}{4096} \bullet I_{\text{OUTFS}} \bullet R_{\text{LOAD}}$$

(7)

#### **ANALOG OUTPUTS**

The DAC902 provides two complementary current outputs,  $I_{OUT}$  and  $I_{\overline{OUT}}$ . The simplified circuit of the analog output stage representing the differential topology is shown in Figure 2. The output impedance of  $200k\Omega \parallel 12pF$  for  $I_{OUT}$  and  $I_{\overline{OUT}}$  results from the parallel combination of the differential switches, along with the current sources and associated parasitic capacitances.

FIGURE 2. Equivalent Analog Output.

The signal voltage swing that may develop at the two outputs,  $I_{OUT}$  and  $I_{\overline{OUT}}$ , is limited by a negative and positive compliance. The negative limit of -1V is given by the breakdown voltage of the CMOS process, and exceeding it will compromise the reliability of the DAC902, or even cause permanent damage. With the full-scale output set to 20mA, the positive compliance equals 1.25V, operating with  $+V_D=5V$ . Note that the compliance range decreases to about 1V for a selected output current of  $I_{OUTFS}=2\text{mA}$ . Care should be taken that the configuration of DAC902 does not exceed the compliance range to avoid degradation of the distortion performance and integral linearity.

Best distortion performance is typically achieved with the maximum full-scale output signal limited to approximately 0.5V. This is the case for a  $50\Omega$  doubly-terminated load and a 20mA full-scale output current. A variety of loads can be adapted to the output of the DAC902 by selecting a suitable transformer while maintaining optimum voltage levels at

$I_{OUT}$  and  $I_{\overline{OUT}}$ . Furthermore, using the differential output configuration in combination with a transformer will be instrumental for achieving excellent distortion performance. Common-mode errors, such as even-order harmonics or noise, can be substantially reduced. This is particularly the case with high output frequencies and/or output amplitudes below full-scale.

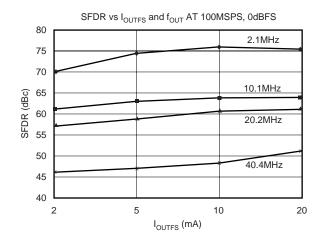

For those applications requiring the optimum distortion and noise performance, it is recommended to select a full-scale output of 20mA. A lower full-scale range down to 2mA may be considered for applications that require a low power consumption, but can tolerate a reduced performance level.

| INPUT CODE (D11 - D0) | I <sub>OUT</sub> | I <sub>OUT</sub> |

|-----------------------|------------------|------------------|

| 1111 1111 1111        | 20mA             | 0mA              |

| 1000 0000 0000        | 10mA             | 10mA             |

| 0000 0000 0000        | 0mA              | 20mA             |

TABLE I. Input Coding vs Analog Output Current.

#### **OUTPUT CONFIGURATIONS**

The current output of the DAC902 allows for a variety of configurations, some of which are illustrated below. As mentioned previously, utilizing the converter's differential outputs will yield the best dynamic performance. Such a differential output circuit may consist of an RF transformer or a differential amplifier configuration. The transformer configuration is ideal for most applications with ac coupling, while op amps will be suitable for a DC-coupled configuration.

The single-ended configuration may be considered for applications requiring a unipolar output voltage. Connecting a resistor from either one of the outputs to ground will convert the output current into a ground-referenced voltage signal. To improve on the DC linearity, an I-to-V converter can be used instead. This will result in a negative signal excursion and, therefore, requires a dual supply amplifier.

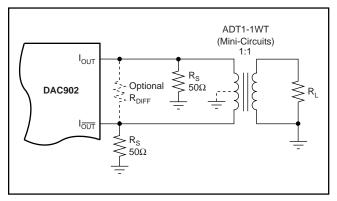

#### **DIFFERENTIAL WITH TRANSFORMER**

Using an RF transformer provides a convenient way of converting the differential output signal into a single-ended signal while achieving excellent dynamic performance (see Figure 3). The appropriate transformer should be carefully selected based on the output frequency spectrum and impedance requirements. The differential transformer configuration has the benefit of significantly reducing common-mode signals, thus improving the dynamic performance over a wide range of frequencies. Furthermore, by selecting a suitable impedance ratio (winding ratio), the transformer can be used to provide optimum impedance matching while controlling the compliance voltage for the converter outputs. The model shown in Figure 3 has a 1:1 ratio and may be used to interface the DAC902 to a  $50\Omega$  load. This results in a  $25\Omega$ load for each of the outputs,  $I_{OUT}$  and  $I_{\overline{OUT}}$ . The output signals are ac coupled and inherently isolated because of its magnetic coupling.

As shown in Figure 3, the transformer's center tap is connected to ground. This forces the voltage swing on  $I_{OUT}$  and  $I_{\overline{OUT}}$  to be centered at 0V. In this case the two resistors,  $R_S$ , may be replaced with one,  $R_{DIFF}$ , or omitted altogether. This approach should only be used if all components are close to each other, and if the VSWR is not important. A complete power transfer from the DAC output to the load can be realized, but the output compliance range should be observed. Alternatively, if the center tap is not connected, the signal swing will be centered at  $R_S \bullet I_{OUTFS}/2$ . However, in this case, the two resistors  $(R_S)$  must be used to enable the necessary DC-current flow for both outputs.

FIGURE 3. Differential Output Configuration Using an RF Transformer.

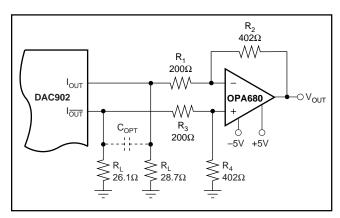

#### **DIFFERENTIAL CONFIGURATION USING AN OP AMP**

If the application requires a DC-coupled output, a difference amplifier may be considered, as shown in Figure 4. Four external resistors are needed to configure the voltage-feedback op amp OPA680 as a difference amplifier performing the differential to single-ended conversion. Under the shown configuration, the DAC902 generates a differential output signal of 0.5Vp-p at the load resistors,  $R_{\rm L}$ . The resistor values shown were selected to result in a symmetric  $25\Omega$  loading for each of the current outputs since the input impedance of the difference amplifier is in parallel to resistors  $R_{\rm L}$ , and should be considered.

FIGURE 4. Difference Amplifier Provides Differential to Single-Ended Conversion and DC-Coupling.

The OPA680 is configured for a gain of two. Therefore, operating the DAC902 with a 20mA full-scale output will produce a voltage output of  $\pm 1$ V. This requires the amplifier to operate off of a dual power supply ( $\pm 5$ V). The tolerance of the resistors typically sets the limit for the achievable common-mode rejection. An improvement can be obtained by fine tuning resistor  $R_4$ .

This configuration typically delivers a lower level of ac performance than the previously discussed transformer solution because the amplifier introduces another source of distortion. Suitable amplifiers should be selected based on their slew-rate, harmonic distortion, and output swing capabilities. High-speed amplifiers like the OPA680 or OPA687 may be considered. The ac performance of this circuit may be improved by adding a small capacitor, CDIFF, between the outputs I<sub>OUT</sub> and I<sub>OUT</sub> (as shown in Figure 4). This will introduce a real pole to create a low-pass filter in order to slew-limiting the DACs fast output signal steps that otherwise could drive the amplifier into slew-limitations or into an overload condition; both would cause excessive distortion. The difference amplifier can easily be modified to add a level shift for applications requiring the single-ended output voltage to be unipolar, i.e., swing between 0V and +2V.

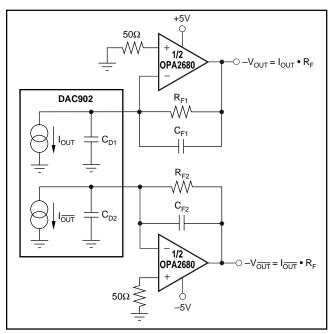

#### **DUAL TRANSIMPEDANCE OUTPUT CONFIGURATION**

The circuit example of Figure 5 shows the signal output currents connected into the summing junction of the OPA2680, which is set up as a transimpedance stage, or I-to-V converter. With this circuit, the DAC's output will be kept at a virtual ground, minimizing the effects of output impedance variations, which results in the best DC linearity (INL). However, as mentioned previously, the amplifier may be driven into slew-rate limitations, and produce unwanted distortion. This may occur especially at high DAC update rates.

FIGURE 5. Dual, Voltage-Feedback Amplifier OPA2680 Forms Differential Transimpedance Amplifier.

The DC gain for this circuit is equal to feedback resistor  $R_{\rm F}$ . At high frequencies, the DAC output impedance ( $C_{\rm D1}$ ,  $C_{\rm D2}$ ) will produce a zero in the noise gain for the OPA2680 that may cause peaking in the closed-loop frequency response.  $C_{\rm F}$  is added across  $R_{\rm F}$  to compensate for this noise-gain peaking. To achieve a flat transimpedance frequency response, the pole in each feedback network should be set to:

$$\frac{1}{2\pi R_F C_F} = \frac{\sqrt{GBP}}{4\pi R_F C_D} \tag{8}$$

with GBP = Gain Bandwidth Product of OPA

which will give a corner frequency f<sub>-3dB</sub> of approximately:

$$f_{-3dB} = \frac{\sqrt{GBP}}{2\pi R_F C_D} \tag{9}$$

The full-scale output voltage is simply defined by the product of  $I_{OUTFS} \bullet R_F$ , and has a negative unipolar excursion. To improve on the ac performance of this circuit, adjustment of  $R_F$  and/or  $I_{OUTFS}$  should be considered. Further extensions of this application example may include adding a differential filter at the OPA2680's output followed by a transformer, in order to convert to a single-ended signal.

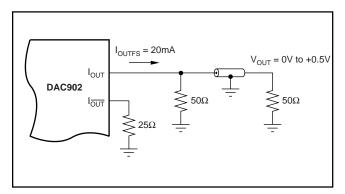

#### SINGLE-ENDED CONFIGURATION

Using a single load resistor connected to the one of the DAC outputs, a simple current-to-voltage conversion can be accomplished. The circuit in Figure 6 shows a  $50\Omega$  resistor connected to  $I_{OUT}$ , providing the termination of the further connected  $50\Omega$  cable. Therefore, with a nominal output current of 20mA, the DAC produces a total signal swing of 0V to 0.5V into the  $25\Omega$  load.

FIGURE 6. Driving a Doubly-Terminated  $50\Omega$  Cable Directly.

Different load resistor values may be selected as long as the output compliance range is not exceeded. Additionally, the output current,  $I_{\text{OUTFS}}$ , and the load resistor may be mutually adjusted to provide the desired output signal swing and performance.

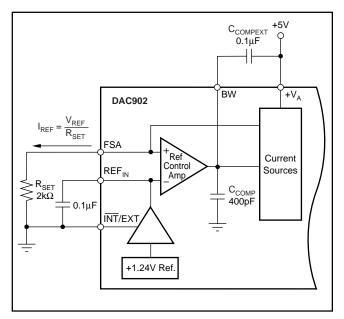

#### INTERNAL REFERENCE OPERATION

The DAC902 has an on-chip reference circuit that comprises a 1.24V bandgap reference and a control amplifier. Grounding pin 16,  $\overline{\text{INT/EXT}}$ , enables the internal reference operation. The full-scale output current,  $I_{\text{OUTFS}}$ , of the DAC902 is determined by the reference voltage,  $V_{\text{REF}}$ , and the value of resistor  $R_{\text{SET}}$ .  $I_{\text{OUTES}}$  can be calculated by:

$$I_{OUTFS} = 32 \cdot I_{REF} = 32 \cdot V_{REF} / R_{SET}$$

(10)

As shown in Figure 7, the external resistor  $R_{SET}$  connects to the FSA pin (Full-Scale Adjust). The reference control amplifier operates as a V-to-I converter producing a reference current,  $I_{REF}$ , which is determined by the ratio of  $V_{REF}$  and  $R_{SET}$ , as shown in Equation 10. The full-scale output current,  $I_{OUTES}$ , results from multiplying  $I_{REF}$  by a fixed factor of 32.

FIGURE 7. Internal Reference Configuration.

Using the internal reference, a  $2k\Omega$  resistor value results in a 20mA full-scale output. Resistors with a tolerance of 1% or better should be considered. Selecting higher values, the converter output can be adjusted from 20mA down to 2mA. Operating the DAC902 at lower than 20mA output currents may be desirable for reasons of reducing the total power consumption, improving the distortion performance, or observing the output compliance voltage limitations for a given load condition.

It is recommended to bypass the REF $_{\rm IN}$  pin with a ceramic chip capacitor of  $0.1\mu{\rm F}$  or more. The control amplifier is internally compensated, and its small signal bandwidth is approximately 3MHz. To improve the ac performance, an additional capacitor ( $C_{\rm COMPEXT}$ ) should be applied between the BW pin and the analog supply,  $+V_{\rm A}$ , as shown in Figure 7. Using a  $0.1\mu{\rm F}$  capacitor, the small-signal bandwidth and output impedance of the control amplifier is further diminished, reducing the noise that is fed into the current source array. This also helps shunting feedthrough signals more effectively, and improving the noise performance of the DAC902.

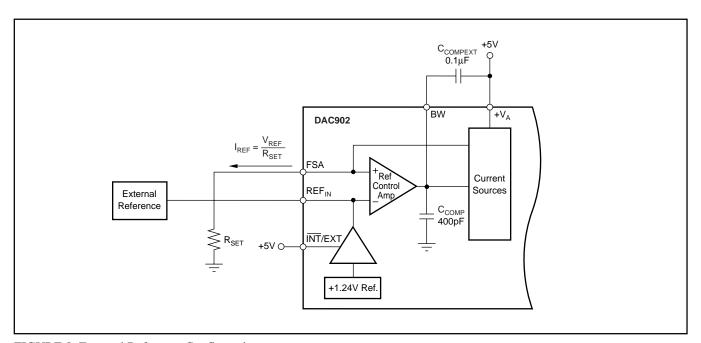

#### **EXTERNAL REFERENCE OPERATION**

The internal reference can be disabled by applying a logic HIGH ( $+V_A$ ) to pin  $\overline{\rm INT}/{\rm EXT}$ . An external reference voltage can then be driven into the REF<sub>IN</sub> pin, which in this case functions as an input, as shown in Figure 8. The use of an external reference may be considered for applications that require higher accuracy and drift performance, or to add the ability of dynamic gain control.

While a  $0.1\mu F$  capacitor is recommended to be used with the internal reference, it is optional for the external reference operation. The reference input, REF<sub>IN</sub>, has a high input impedance ( $1M\Omega$ ) and can easily be driven by various sources. Note that the voltage range of the external reference should stay within the compliance range of the reference input (0.1V to 1.25V).

#### **DIGITAL INPUTS**

The digital inputs, D0 (LSB) through D11 (MSB) of the DAC902 accepts standard-positive binary coding. The digital input word is latched into a master-slave latch with the rising edge of the clock. The DAC output becomes updated with the following falling clock edge (refer to the specification table and timing diagram for details). The best performance will be achieved with a 50% clock duty cycle, however, the duty cycle may vary as long as the timing specifications are met. Additionally, the setup and hold times may be chosen within their specified limits.

All digital inputs are CMOS compatible. The logic thresholds depend on the applied digital supply voltage such that they are set to approximately half the supply voltage;  $V^{th} = +V_D/2$  ( $\pm 20\%$  tolerance). The DAC902 is designed to operate over a supply range of 2.7V to 5.5V.

#### **POWER-DOWN MODE**

The DAC902 features a power-down function that can be used to reduce the supply current to less than 9mA over the specified supply range of 2.7V to 5.5V. Applying a logic HIGH to the PD pin will initiate the power-down mode, while a logic LOW enables normal operation. When left unconnected, an internal active pull-down circuit will enable the normal operation of the converter.

# GROUNDING, DECOUPLING AND LAYOUT INFORMATION

Proper grounding and bypassing, short lead length, and the use of ground planes are particularly important for high frequency designs. Multilayer pc-boards are recommended for best performance since they offer distinct advantages such as minimization of ground impedance, separation of signal layers by ground layers, etc.

The DAC902 uses separate pins for its analog and digital supply and ground connections. The placement of the decoupling capacitor should be such that the analog supply  $(+V_A)$  is bypassed to the analog ground (AGND), and the digital supply bypassed to the digital ground (DGND). In most cases 0.1uF ceramic chip capacitors at each supply pin are adequate to provide a low impedance decoupling path. Keep in mind that their effectiveness largely depends on the proximity to the individual supply and ground pins. Therefore, they should be located as close as physically possible to those device leads. Whenever possible, the capacitors should be located immediately under each pair of supply/ground pins on the reverse side of the pc-board. This layout approach will minimize the parasitic inductance of component leads and pcb runs.

FIGURE 8. External Reference Configuration.

Further supply decoupling with surface mount tantalum capacitors (1uF to 4.7uF) may be added as needed in proximity of the converter.

Low noise is required for all supply and ground connections to the DAC902. It is recommended to use a multilayer pc-board utilizing separate power and ground planes. Mixed signal designs require particular attention to the routing of the different supply currents and signal traces. Generally, analog supply and ground planes should only extend into analog signal areas, such as the DAC output signal and the reference signal. Digital supply and ground planes must be confined to areas covering digital circuitry, including the digital input lines connecting to the converter, as well as the clock signal. The analog and digital ground planes should be joined together at one point underneath the DAC. This can be realized with a short track of approximately 1/8" (3mm).

The power to the DAC902 should be provided through the use of wide pcb runs or planes. Wide runs will present a lower trace impedance, further optimizing the supply decoupling. The analog and digital supplies for the converter should only be connected together at the supply connector of the pc-board. In the case of only one supply voltage being available to power the DAC, ferrite beads along with bypass capacitors may be used to create an LC filter. This will generate a low-noise analog supply voltage that can then be connected to the  $+V_A$  supply pin of the DAC902.

While designing the layout, it is important to keep the analog signal traces separate from any digital line, in order to prevent noise coupling onto the analog signal path.

21-May-2010

#### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package Type | Package<br>Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup>    | Lead/<br>Ball Finish | MSL Peak Temp <sup>(3)</sup> | Samples<br>(Requires Login) |

|------------------|-----------------------|--------------|--------------------|------|-------------|----------------------------|----------------------|------------------------------|-----------------------------|

| DAC902E          | ACTIVE                | TSSOP        | PW                 | 28   | 50          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-2-260C-1 YEAR          |                             |

| DAC902E/2K5      | ACTIVE                | TSSOP        | PW                 | 28   | 2500        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-2-260C-1 YEAR          |                             |

| DAC902E/2K5G4    | ACTIVE                | TSSOP        | PW                 | 28   | 2500        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-2-260C-1 YEAR          |                             |

| DAC902EG4        | ACTIVE                | TSSOP        | PW                 | 28   | 50          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-2-260C-1 YEAR          |                             |

| DAC902U          | ACTIVE                | SOIC         | DW                 | 28   | 20          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-2-260C-1 YEAR          |                             |

| DAC902U/1K       | ACTIVE                | SOIC         | DW                 | 28   | 1000        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-2-260C-1 YEAR          |                             |

| DAC902U/1KG4     | ACTIVE                | SOIC         | DW                 | 28   | 1000        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-2-260C-1 YEAR          |                             |

| DAC902UG4        | ACTIVE                | SOIC         | DW                 | 28   | 20          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-2-260C-1 YEAR          |                             |

<sup>(1)</sup> The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

# **PACKAGE OPTION ADDENDUM**

21-May-2010

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com 20-Jul-2010

### TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| DAC902E/2K5 | TSSOP           | PW                 | 28 | 2500 | 330.0                    | 16.4                     | 6.9        | 10.2       | 1.8        | 12.0       | 16.0      | Q1               |

| DAC902U/1K  | SOIC            | DW                 | 28 | 1000 | 330.0                    | 32.4                     | 11.35      | 18.67      | 3.1        | 16.0       | 32.0      | Q1               |

www.ti.com 20-Jul-2010

#### \*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DAC902E/2K5 | TSSOP        | PW              | 28   | 2500 | 346.0       | 346.0      | 33.0        |

| DAC902U/1K  | SOIC         | DW              | 28   | 1000 | 346.0       | 346.0      | 49.0        |

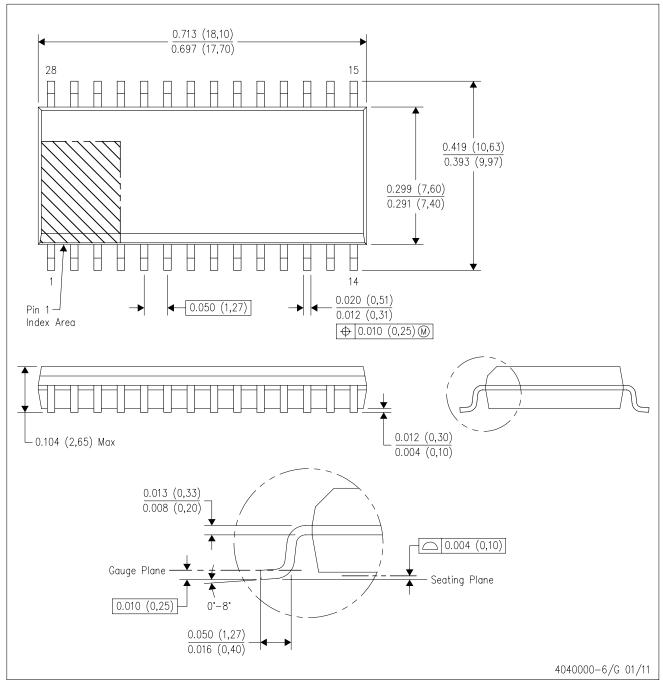

DW (R-PDSO-G28)

### PLASTIC SMALL OUTLINE

NOTES: A. All linear dimensions are in inches (millimeters). Dimensioning and tolerancing per ASME Y14.5M-1994.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

- D. Falls within JEDEC MS-013 variation AE.

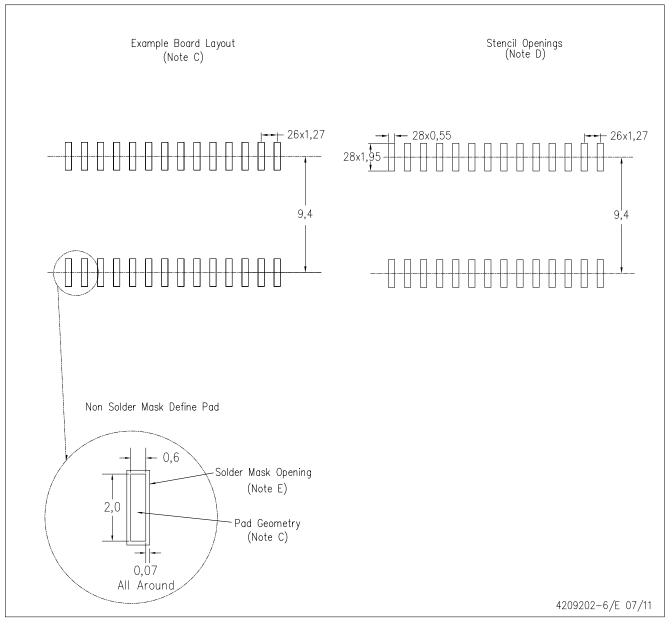

DW (R-PDSO-G28)

PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Refer to IPC7351 for alternate board design.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

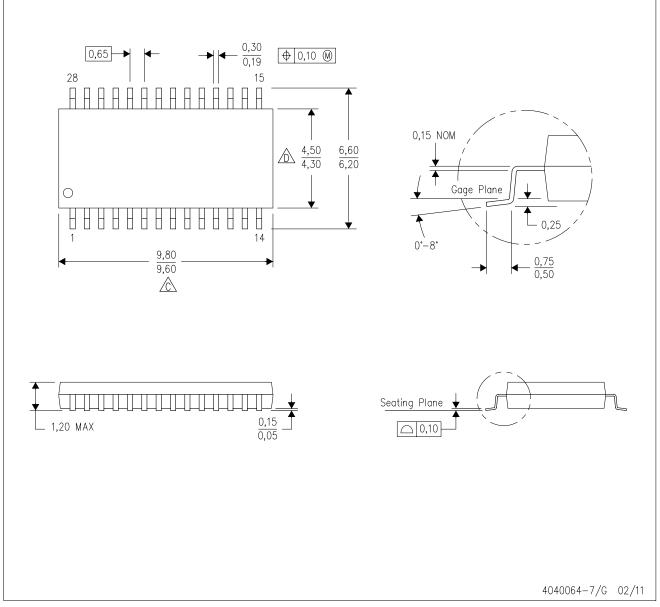

PW (R-PDSO-G28)

### PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M—1994.

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0,15 each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0,25 each side.

- E. Falls within JEDEC MO-153

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications                     |                                   |

|-----------------------------|------------------------|----------------------------------|-----------------------------------|

| Audio                       | www.ti.com/audio       | Communications and Telecom       | www.ti.com/communications         |

| Amplifiers                  | amplifier.ti.com       | Computers and Peripherals        | www.ti.com/computers              |

| Data Converters             | dataconverter.ti.com   | Consumer Electronics             | www.ti.com/consumer-apps          |

| DLP® Products               | www.dlp.com            | Energy and Lighting              | www.ti.com/energy                 |

| DSP                         | dsp.ti.com             | Industrial                       | www.ti.com/industrial             |

| Clocks and Timers           | www.ti.com/clocks      | Medical                          | www.ti.com/medical                |

| Interface                   | interface.ti.com       | Security                         | www.ti.com/security               |

| Logic                       | logic.ti.com           | Space, Avionics and Defense      | www.ti.com/space-avionics-defense |

| Power Mgmt                  | power.ti.com           | Transportation and<br>Automotive | www.ti.com/automotive             |

| Microcontrollers            | microcontroller.ti.com | Video and Imaging                | www.ti.com/video                  |

| RFID                        | www.ti-rfid.com        | Wireless                         | www.ti.com/wireless-apps          |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        |                                  |                                   |

**TI E2E Community Home Page**

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated

e2e.ti.com