### **General Description**

The MAX3910 is a 10.7Gbps transimpedance amplifier designed for SONET OC-192/SDH STM-64, DWDM, and 10Gbps systems employing optical amplifiers. Operating from a single +5V or -5.2V supply, it converts a photodiode current into a measurable differential voltage. This product has a linear gain for an input current up to 950µAp-p and a soft-limiting feature that provides an increasing output swing for an input current up to the 3.5mAp-p overload. An offset adjust circuit and output-level monitors allow system threshold adjustments. Additional features include back-terminated  $50\Omega$  outputs and an integrated  $200\Omega$  filter resistor to bias the photodiode.

The MAX3910 has a small-signal bandwidth of 9.1GHz and a small-signal transimpedance of  $1.65k\Omega$ . The part achieves an input sensitivity of 15.5µAp-p for a BER of 10-12, translating to an optical sensitivity of -19.3dBm for a PIN (r = 0.9, r<sub>e</sub> = 6.6) photo detector and -28.8dBm for an APD (M = 8,  $\rho$  = 0.9,  $r_e$  = 10) photo detector.

The MAX3910 is fabricated in Maxim's in-house SiGe process and is available in die form.

### **Applications**

**DWDM Systems**

OC-192/STM-64 Transmission Systems 10Gbps Systems Using Optical Amplifiers

10Gbps Optical Receivers

### **Features**

- ♦ 950µAp-p Linear Range

- ♦ 15.5µAp-p Sensitivity

- ♦ 3.5mAp-p Overload

- ♦ 1.65kΩ Transimpedance

- ♦ 9.1GHz Bandwidth

- ♦ 110mA Supply Current

- **♦ Output Offset Adjustment**

- **♦** Soft-Limiting Beyond Linear Input Range

- ♦ Single +5V or -5.2V Power Supply

- **♦ ESD Protection**

### **Ordering Information**

| PART       | TEMP RANGE   | PIN-PACKAGE |

|------------|--------------|-------------|

| MAX3910U/D | 0°C to +85°C | Dice*       |

<sup>\*</sup>Dice are designed to operate over a 0°C to +100°C junction temperature  $(T_J)$  range, but are tested and guaranteed at  $T_A =$ +25°C.

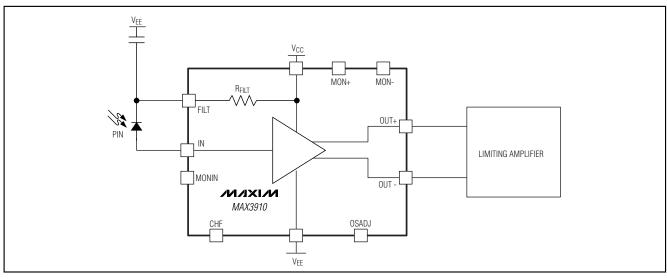

## Typical Operating Circuit

MIXIM

Maxim Integrated Products 1

### **ABSOLUTE MAXIMUM RATINGS**

| Power-Supply Voltage (VCC - VEE)0.5V to +6.0V | Storage Ambient Temperature Range (TSTG)55°C to +150°C |

|-----------------------------------------------|--------------------------------------------------------|

| Continuous Input Current (IN)4.2mA            | Die Attach Temperature+400°C                           |

| Continuous Input Current (FILT)9.8mA          | Operating Temperature Range                            |

| Continuous Output Current (OUT+, OUT-)35mA    | (Junction Temperature Range)20°C to +120°C             |

| Voltage at CHF, FILT, MON+, MON-,             |                                                        |

| MONIN, OSADJ(VEE - 0.5V) to the lesser        |                                                        |

| of +6 0V and $(V_{CC} + 0.5V)$                |                                                        |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} - V_{EE} = 4.75V \text{ to } 5.5V, T_J = 0^{\circ}\text{C to } + 100^{\circ}\text{C}. \text{ Typical values are at } V_{EE} = -5.2V, V_{CC} = GND, T_A = +25^{\circ}\text{C}, \text{ unless otherwise noted.})$  (Notes 1, 2)

| PARAMETER                             | SYMBOL           | CONDITIONS                                                           | MIN    | TYP                    | MAX                   | UNITS             |  |

|---------------------------------------|------------------|----------------------------------------------------------------------|--------|------------------------|-----------------------|-------------------|--|

| Supply Current                        | IEE              | V <sub>EE</sub> 2 open, Figure 1 (Note 3)                            |        | 95                     | 138                   | mA                |  |

| Supply Current                        | I <sub>EE</sub>  | V <sub>EE</sub> 2 connected to negative supply,<br>Figure 1 (Note 3) |        | 110                    | 158                   | mA                |  |

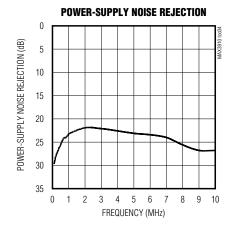

| Power-Supply Noise Rejection          | PSNR             | I <sub>IN</sub> ≤ 450μA <sub>P-P</sub> , f ≤ 1MHz                    |        | 23                     |                       | dB                |  |

| Fower-Supply Noise Rejection          | FOINT            | $I_{IN} \le 450\mu A_{P-P}$ , $f \le 10MHz$ (Note 4)                 |        | 22                     |                       | uБ                |  |

| Input Bias Voltage                    |                  |                                                                      |        | V <sub>EE</sub> + 0.95 | V <sub>EE</sub> + 1.1 | V                 |  |

|                                       |                  | I <sub>IN</sub> ≤ 450μA <sub>P-P</sub>                               | 1.40   | 1.65                   | 1.87                  |                   |  |

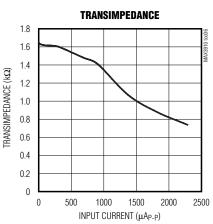

| Transimpedance (Note 5)               | $Z_F$            | $I_{IN} = 1.0 \text{mAp-p}$                                          |        | 1.37                   |                       | kΩ                |  |

|                                       |                  | $I_{IN} = 2.0 \text{mAp-p}$                                          |        | 0.84                   |                       |                   |  |

| Linear Input Current Range            | I <sub>LIN</sub> | (Note 5)                                                             | 450    | 950                    |                       | µA <sub>P-P</sub> |  |

| Law Francisco Cutoff                  |                  | CHF open, I <sub>IN</sub> ≤ 450µA <sub>P-P</sub>                     | 6 25   |                        | kHz                   |                   |  |

| Low-Frequency Cutoff                  |                  | CHF = 0.1µF, I <sub>IN</sub> ≤ 450µA <sub>P-P</sub>                  |        | 0.5                    |                       | KHZ               |  |

| Photodiode Filter Resistor            | RFILT            |                                                                      | 165    | 200                    | 240                   | Ω                 |  |

| Output Monitor Resistance             |                  | To OUT+ or OUT-                                                      |        | 10                     |                       | kΩ                |  |

| Single-Ended Output Resistance        |                  | To V <sub>CC</sub>                                                   | 42     | 50                     | 59                    | Ω                 |  |

| Maximum Differential Output<br>Swing  | V <sub>OD</sub>  | (Note 6)                                                             | 1.45   | 1.75                   | 1.90                  | V <sub>P-P</sub>  |  |

| Single-Ended Output Range             | Vos              | Outputs DC-coupled to $50\Omega$ to $V_{CC}$ (Note 6)                | -1.3   |                        | 0                     | V                 |  |

| Out - 1 DO O# - 1                     |                  | I <sub>IN</sub> = 7.5μA DC                                           | -7     |                        | +7                    | \/                |  |

| Output DC Offset                      |                  | I <sub>IN</sub> = 1.4mA DC                                           | -10    |                        | +10                   | mV                |  |

| OSADJ Input Resistance                |                  |                                                                      | 15     | 20                     |                       | kΩ                |  |

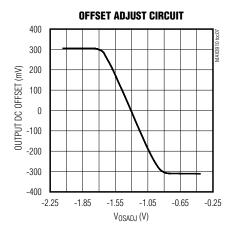

| OSADJ Input Range                     | Vosadj           |                                                                      | -2.1   |                        | -0.4                  | V                 |  |

| OSADJ Voltage for Zero Offset         |                  |                                                                      | -1.375 | -1.25                  | -1.125                | V                 |  |

| Minimum Differential Output<br>Offset |                  | $V_{OSADJ}$ = -0.4V, $R_L$ = $50\Omega$ to $V_{CC}$                  |        | -320                   | -250                  | mV                |  |

### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} - V_{EE} = 4.75V \text{ to } 5.5V, T_J = 0^{\circ}\text{C to } + 100^{\circ}\text{C}$ . Typical values are at  $V_{EE} = -5.2V, V_{CC} = GND, T_A = +25^{\circ}\text{C}$ , unless otherwise noted.) (Notes 1, 2)

| PARAMETER                             | SYMBOL | CONDITIONS                                         | MIN | TYP | MAX | UNITS |

|---------------------------------------|--------|----------------------------------------------------|-----|-----|-----|-------|

| Maximum Output Offset                 |        | $V_{OSADJ} = -2.1V$ , $R_L = 50\Omega$ to $V_{CC}$ | 250 | 320 |     | mV    |

| OSADJ Voltage Control Factor:<br>OUT+ |        | (ΔVosadj)/ΔVout+                                   | -3  | -2  |     | V/V   |

| OSADJ Voltage Control Factor:<br>OUT- |        | (ΔVosadj)/ΔVout-                                   |     | 2   | 3   | V/V   |

### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} - V_{EE} = 4.75V \text{ to } 5.5V, T_J = 0^{\circ}\text{C to } + 100^{\circ}\text{C}$ . Typical values are at  $V_{EE} = -5.2V, V_{CC} = GND, T_A = +25^{\circ}\text{C}$ , unless otherwise noted.) (Notes 1, 2)

| PARAMETER                                | SYMBOL            | CONDITIONS                                                                 | MIN | TYP   | MAX  | UNITS             |

|------------------------------------------|-------------------|----------------------------------------------------------------------------|-----|-------|------|-------------------|

| Bandwidth                                | BW <sub>3dB</sub> | I <sub>IN</sub> ≤ 450μA <sub>P-P</sub> (Notes 2, 11)                       | 8.2 | 9.1   |      | GHz               |

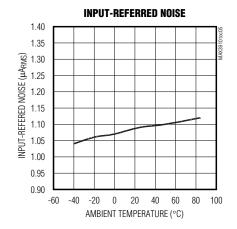

| Input-Referred Noise                     | IN                | (Notes 2, 7)                                                               |     | 1.1   | 1.62 | μARMS             |

| Input Sensitivity                        |                   | (Notes 2, 8)                                                               |     | 15.5  |      | µАр-р             |

|                                          | l                 | AC component (Note 9)                                                      | 2.5 | 3.5   |      | mA <sub>P-P</sub> |

| Input Overload                           | IOL               | DC component (Note 9)                                                      | 1.4 | 1.8   |      | mA                |

| Gain Flatness                            |                   | 100MHz - 4GHz, I <sub>IN</sub> ≤ 450μA <sub>P-P</sub> (Note 2)             |     | ±0.75 |      | dB                |

| Gain Ripple                              |                   | 4GHz - BW <sub>3dB</sub> , I <sub>IN</sub> ≤ 450μAp <sub>-P</sub> (Note 2) |     | 1.5   |      | dB                |

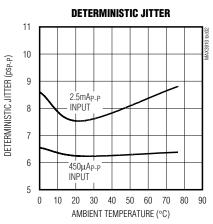

| Deterministic Jitter (Notes 2, 10)       |                   | I <sub>IN</sub> ≤ 450μΑρ-ρ                                                 |     | 6.2   | 10.7 | 202.5             |

|                                          |                   | $450\mu A_{P-P} \le I_{IN} \le 2.5mA_{P-P}$                                |     | 7.5   | 14.6 | psp-p             |

| Single-Ended Output Return Loss (Note 2) |                   | ≤7.5GHz                                                                    |     | 10    |      | dB                |

- Note 1: Default test conditions: V<sub>EE</sub>2 and CHF = open (Figure 1), R<sub>L</sub> = 50Ω to V<sub>CC</sub>, DC-coupled at each output, unless otherwise noted. AC characteristics are guaranteed by design and characterization.

- **Note 2:** Source capacitance = 0.25pF, source series resistance =  $20\Omega$ , and source series inductance = 0.6nH. Output series inductance = 0.5nH at each of the differential outputs.

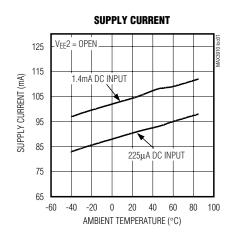

- Note 3: Supply current increases as average signal level increases. Maximum supply current is specified for I<sub>IN</sub> = 1.4mA average current. Typical supply current is specified for I<sub>IN</sub> ≤ 225µA average current.

- **Note 4:** PSNR is measured by detecting the differential output voltage  $\Delta V_{OUT}$  while applying  $\Delta V_{EE} = 55 \text{mV}_{P-P}$  signal on V<sub>EE</sub>1. PSNR =  $20 \log(\Delta V_{EE}/\Delta V_{OUT})$ . Output offset adjust feature disabled.

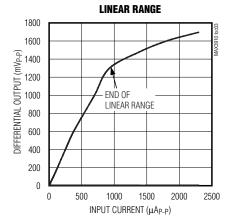

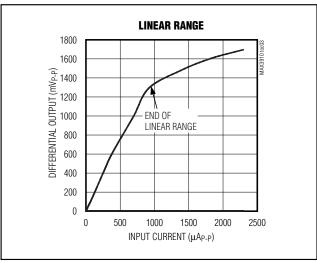

- Note 5: Transimpedance is defined as V<sub>OUT(P-P)</sub> / I<sub>IN(P-P)</sub> at 10MHz. Linear range is defined as the input signal level where the transimpedance deviates from the small-signal transimpedance value by no more than 10% (Figure 2).

- **Note 6:** Input current  $\leq 2.5 \text{mAp-p}$  and  $\leq 1.4 \text{mA DC}$ .

- Note 7: Measured with a 4th-order Bessel-Thompson filter with a cutoff frequency of 8GHz.

- **Note 8:** Input sensitivity calculated from  $S/N \ge 14.1$  (BER  $\le 10^{-12}$ ).

- Note 9: For input signal less than or equal to the input overload, deterministic jitter is guaranteed to be within specifications.

- Note 10: Deterministic jitter is characterized with 27 1 PRBS + 80 zeros + 80 ones at 10.7Gbps.

- Note 11: Bandwidth is measured in an electrical environment and corrected to match the conditions of Note 2.

## **Typical Operating Characteristics**

(VEE = -5.2V,  $V_{CC}$  = GND,  $T_A$  = +25°C, unless otherwise noted.)

### Typical Operating Characteristics (continued)

(VEE = -5.2V, VCC = GND,  $T_A = +25$ °C, unless otherwise noted.)

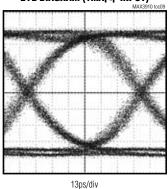

ELECTRICAL EYE DIAGRAM (1mA<sub>P-P</sub> INPUT)

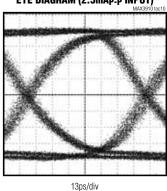

ELECTRICAL EYE DIAGRAM (2.5mA<sub>P-P</sub> INPUT)

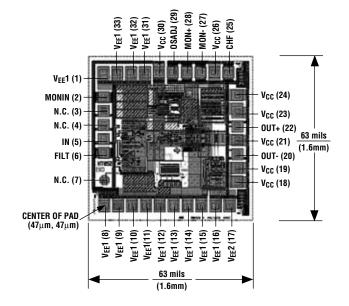

### **Pad Description**

| PAD                           | NAME              | FUNCTION                                                                                                                                         |  |

|-------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1, 8–16, 31,<br>32, 33        | V <sub>EE</sub> 1 | Main Negative Power-Supply Voltage*                                                                                                              |  |

| 2                             | MONIN             | Monitor Output Providing Replica Current from DC Offset Loop. Internally connected to $V_{CC}$ through $1k\Omega$ resistor.                      |  |

| 3, 4, 7                       | N.C.              | No Connection. Do not connect.                                                                                                                   |  |

| 5                             | IN                | Signal Input. Connected to photodiode anode.                                                                                                     |  |

| 6                             | FILT              | On-Chip Resistor for Photodiode Biasing. Internally connected to $V_{CC}$ through a $200\Omega$ resistor.                                        |  |

| 17                            | V <sub>EE</sub> 2 | Separate Power Supply for Output Offset Adjustment. Leave open to disable this feature. Offset ac feature must be disabled for AC-coupled load.* |  |

| 18, 19, 21,<br>23, 24, 26, 30 | Vcc               | Positive Power-Supply Voltage*                                                                                                                   |  |

| 20                            | OUT-              | Inverted Data Output with $50\Omega$ Back Termination                                                                                            |  |

| 22                            | OUT+              | Noninverted Data Output with $50\Omega$ Back Termination                                                                                         |  |

| 25                            | CHF               | Connect a capacitor to ground to increase the on-chip DC-cancellation loop time constant.                                                        |  |

| 27                            | MON-              | Monitors DC Voltage at OUT Internally connected to OUT- through a $10k\Omega$ resistor.                                                          |  |

| 28                            | MON+              | Monitors DC Voltage at OUT+. Internally connected to OUT+ through a $10k\Omega$ resistor.                                                        |  |

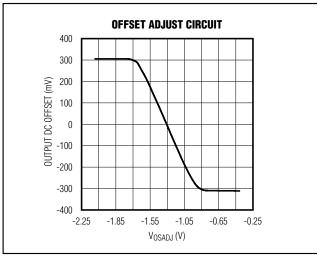

| 29                            | OSADJ             | DC Offset Control. Voltage at this pad sets the output DC offset when the offset adjust feature is enabled. (See Figure 3.)                      |  |

<sup>\*</sup>The MAX3910 can operate with a positive supply (V<sub>EE</sub> = GND) or a negative supply (V<sub>CC</sub> = GND). 4.75V ≤ (V<sub>CC</sub> - V<sub>EE</sub>) ≤ 5.5V.

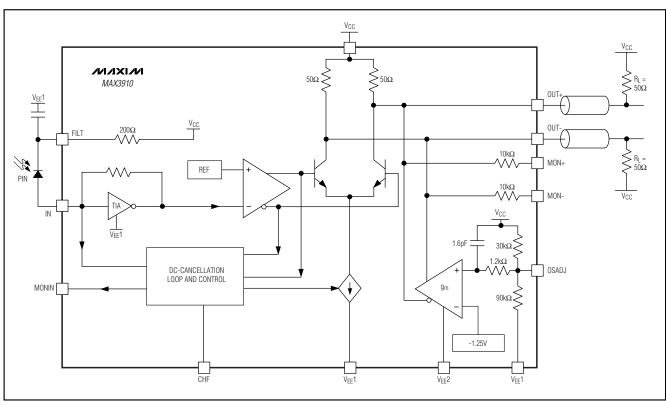

Figure 1. Functional Diagram

### **Detailed Description**

Figure 1 is a functional diagram of the MAX3910 linear transimpedance amplifier. It comprises a transimpedance amplifier stage, a gain stage, an output buffer, and a DC-cancellation circuit. An output offset adjust circuit is implemented to perform threshold adjust for systems using optical amplifiers.

### Transimpedance Amplifier

The photodiode current flows into the summing node of a high-gain amplifier and a shunt feedback resistor. A DC-cancellation circuit removes the average current, and the AC component is linearly converted into a voltage over a wide input range.

#### **DC-Cancellation Loop**

The DC-cancellation circuit uses low-frequency feedback to remove the DC component of the input signal. This feature centers the input signal within the transimpedance amplifier's linear range, thereby reducing pulse-width distortion (PWD) on large input signals. The DC-cancellation circuit has a built-in capacitor to achieve a low-frequency cutoff of 25kHz, and an external capaci-

tor bonded between CHF and VCC can be used to further reduce the cutoff frequency. This circuit minimizes PWD for data sequences that exhibit a 50% duty cycle and mark density. A duty cycle or mark density significantly different from 50% causes the MAX3910 to generate PWD.

### **Voltage Amplifier**

The single-ended signal from the transimpedance amplifier stage is converted to a differential signal and further amplified.

#### **Output Buffer**

In addition to having a wide linear range, the MAX3910 has a soft-limiting feature. For inputs less than 950µAp-p, the MAX3910 operates linearly. Beyond this range, a soft-limiting feature is implemented so that the differential output swing is proportional to the input current, as shown in Figure 2. The output buffer is back-terminated with  $50\Omega$  on-chip resistors and can drive either a DC-coupled  $50\Omega$  load to VCC or a  $50\Omega$  AC-coupled load.

Figure 2. Linear Range of the MAX3910

### Offset Adjust Circuit

Connecting VEE2 to the negative supply enables the offset adjust circuit. The circuit compares the external voltage applied to the OSADJ pad to an internal (VCC - 1.25V) reference to introduce a DC offset at the differential outputs (Figure 3). This function is useful in systems that need threshold adjust. For AC-coupled loads, the circuit must be disabled.

The input network of the offset adjust circuit creates a lowpass filter with a cutoff frequency of approximately 85MHz. If the pad is left unconnected, an internal voltage-divider sets the voltage at the pad to (VCC - 1.25V). The input impedance is approximately  $20k\Omega$ .

Figure 3. Offset Adjust Circuit Behavior

#### **MONIN Pad**

The voltage at MONIN ( $V_{MONIN}$ ) serves as a received signal strength indicator (RSSI). The transimpedance gain of the average input current ( $I_{INAVE}$ ) to  $V_{MONIN}$  is typically:

$$\frac{\Delta V_{MONIN}}{\Delta I_{INAVF}} = 1000(V/A)$$

### Design Procedure

### **Power Supply**

The MAX3910 requires wideband power-supply decoupling. Power-supply bypassing should provide low impedance between VEE1 and VCC for frequencies up to 10GHz. If the offset-adjust circuit is enabled, it is recommended that the same filtering be applied to VEE2.

#### Photodiode Filter

Supply-voltage noise at the cathode of the photodiode produces a noise current I = CPD  $\Delta V/\Delta t,$  which reduces the receiver sensitivity (CPD is the photodiode capacitance). The MAX3910 contains an internal  $200\Omega$  resistor between the FILT pad and VCC. Combining this resistor with an external capacitor connected between the FILT pad and VEE1 creates a lowpass filter, which reduces photodiode noise current and improves receiver sensitivity. Current generated by supply-noise voltage is divided between the external capacitance and the photodiode capacitance. Assuming the filter capacitance is much larger than the photodiode capacitance, the input noise current because of supply noise is:

$$I_{NOISE} = \frac{V_{NOISE} \times C_{PD}}{R_{FII} T \times C_{FII} T}$$

where  $C_{\text{FILT}}$  is the external capacitance. If the amount of tolerable noise is known, the filter capacitance can be selected easily.

#### Wire Bonding

For high-current density and reliable operation, the MAX3910 uses gold metalization. Make connections to the die with gold wire only. Aluminum bonding is not recommended. Die thickness is typically 8 mils. Bondwire inductance between the photodiode and the IN pad can be optimized to obtain best performance. Higher inductance improves bandwidth, and lower bondwire inductance reduces time domain ringing. Keep bondwires on all other pads as short as possible to optimize performance. The backside of the MAX3910 die is fully insulated and can be connected to VCC or VEE.

### **Input Capacitance**

Noise and bandwidth are adversely affected by capacitance on the MAX3910's input node. Use any techniques available to minimize input capacitance.

### **Output-Coupling Capacitors**

The outputs of the MAX3910 can be AC- or DC-coupled. For more information on selecting AC-coupling capacitors, visit Maxim's website and follow the links to HFAN-01.1: *Choosing AC-Coupling Capacitors*.

## Applications Information

### **Optical Power Relations**

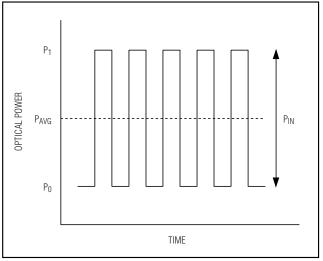

Many MAX3910 specifications relate to the input signal amplitude. When working with fiber optic receivers, the input sometimes is expressed in terms of average optical power and extinction ratio.

Optical power relations are shown in Table 1 for an average mark density of 50% and an average duty cycle of 50%.

### **Optical Sensitivity Calculation**

The MAX3910 input-referred RMS noise current (I<sub>N</sub>) generally determines receiver sensitivity. To obtain a system bit-error rate of 10<sup>-12</sup>, the signal-to-noise ratio must be 14.1 or better. The input sensitivity, expressed in average power, can be estimated as:

Sensitivity =

$$10log \left( \frac{14.1 \times l_N \times (r_e + 1)}{2 \times \rho \times (r_e - 1)} \times 1000 \right) dBm$$

where  $\rho$  is the photodiode responsivity in A/W, and  $I_{N}$  is measured in amperes.

### **Input Optical Overload**

The overload is the largest input that the MAX3910 accepts while meeting specifications. Optical overload can be estimated in terms of average power with the following equation:

Overload =

$$10\log \left( \frac{I_{OL} \times (r_e + 1)}{2 \times \rho (r_e - 1)} \right) dBm$$

where IOL(mAp-p) is the DC overload for the MAX3910.

### **Optical Linear Range**

The MAX3910 has high gain and operates in a linear range for inputs not exceeding:

$$Linear range = 10log \left( \frac{I_{LIN} \times (r_e + 1)}{2 \times \rho (r_e - 1)} \right) dBm$$

where ILIN(mAp-p) is the peak-to-peak linear range.

### **Table 1. Optical Power Relations\***

| PARAMETER                          | SYMBOL          | PIN-PACKAGE                                               |

|------------------------------------|-----------------|-----------------------------------------------------------|

| Average                            | Pavg            | $P_{AVG} = (P0 + P1) / 2$                                 |

| Extinction                         | r <sub>e</sub>  | $r_e = P1 / P0$                                           |

| Optical<br>Power of a 1            | P1              | $P1 = 2P_{AVG} \frac{r_e}{r_e + 1}$                       |

| Optical<br>Power of a 0            | P0              | $P0 = 2P_{AVG} / (r_e + 1)$                               |

| Optical<br>Modulation<br>Amplitude | P <sub>IN</sub> | $P_{IN} = P1 - P0 = 2P_{AVG} \frac{r_{e} - 1}{r_{e} + 1}$ |

<sup>\*</sup>Assuming a 50% average mark density.

Figure 4. Optical Power Relations

### **Pad Coordinates**

| PAD | NAME              | COORDINATES (µm) |               |  |

|-----|-------------------|------------------|---------------|--|

| PAD | NAME              | Х                | <b>Y</b> 1259 |  |

| 1   | V <sub>EE</sub> 1 | 38               |               |  |

| 2   | MONIN             | 43               | 1034          |  |

| 3   | N.C.              | 43               | 908           |  |

| 4   | N.C.              | 43               | 782           |  |

| 5   | IN                | 43               | 656           |  |

| 6   | FILT              | 43               | 530           |  |

| 7   | N.C.              | 50               | 282           |  |

| 8   | V <sub>EE</sub> 1 | 47               | 47            |  |

| 9   | V <sub>EE</sub> 1 | 173              | 47            |  |

| 10  | V <sub>EE</sub> 1 | 299              | 47            |  |

| 11  | V <sub>EE</sub> 1 | 425              | 47            |  |

| 12  | V <sub>EE</sub> 1 | 551              | 47            |  |

| 13  | V <sub>EE</sub> 1 | 677              | 47            |  |

| 14  | V <sub>EE</sub> 1 | 803              | 47            |  |

| 15  | V <sub>EE</sub> 1 | 929              | 47            |  |

| 16  | V <sub>EE</sub> 1 | 1055             | 47            |  |

| 17  | V <sub>EE</sub> 1 | 1181             | 47            |  |

| 18  | VCC               | 1255             | 267           |  |

| 19  | Vcc               | 1255             | 393           |  |

| 20  | OUT-              | 1255             | 519           |  |

| 21  | V <sub>C</sub> C  | 1255             | 645           |  |

| 22  | OUT+              | 1255             | 771           |  |

| 23  | Vcc               | 1255             | 897           |  |

| 24  | V <sub>CC</sub>   | 1255             | 1055          |  |

| 25  | CHF               | 1172             | 1259          |  |

| 26  | Vcc               | 1046             | 1259          |  |

| 27  | MON-              | 920              | 1259          |  |

| 28  | MON+              | 794              | 1259          |  |

| 29  | OSADJ             | 668              | 1259          |  |

| 30  | V <sub>C</sub> C  | 542              | 1259          |  |

| 31  | V <sub>EE</sub> 1 | 416              | 1259          |  |

| 32  | V <sub>EE</sub> 1 | 290              | 1259          |  |

| 33  | VFF1              | 164              | 1259          |  |

Coordinates are in µm from the lower left corner of the circuit die to the center of the pad. For more information, refer to HFAN-08.0.1: Understanding Bonding Coordinates and Physical Die Size.

### **Chip Information**

TRANSISTOR COUNT: 1291

PROCESS: BiPOLAR SiGe, SOI

Die Size: 1.6mm × 1.6mm

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.