# 16-Bit Low-Power Stereo Audio ADC With Microphone Bias and Microphone Amplifier

### FEATURES

- Analog Front End:

- Stereo Single End Input With MUX

- Mono Differential Input

- Stereo Programmable Gain Amplifier

- Microphone Boost Amplifier and Bias

- Analog Performances Dynamic Range: 90 dB

- Power-Supply Voltage

- 1.71 V to 3.6 V for Digital I/O Section

- 1.71 V to 3.6 V for Digital Core Section

- 2.4 V to 3.6 V for Analog Section

- Low Power Dissipation:

- 13 mW in Record, 1.8/2.4 V, 48 kHz, Stereo

- 5.3 mW in Record, 1.8/2.4 V, 8 kHz, Mono

- 3.3 μW in All Power Down

- Sampling Frequency: 5 kHz to 50 kHz

- Auto Level Control for Recording

- Operation by Single Clock Input Without PLL

- System Clock: Common Audio Clock (256 f<sub>s</sub>/384 f<sub>s</sub>), 12/24, 13/26, 13.5/27, 19.2/38.4, 19.68/39.36 MHz

- 2 (I<sup>2</sup>C) or 3 (SPI) Wire Serial Control

- Programmable Function by Register Control:

- Digital Soft Mute

- Power Up/Down Control for Each Module

- 30-dB to -12-dB Gain for Analog Inputs

- 0/12/20-dB Boost for Microphone Input

- Parameter Settings for ALC

- Three-Band Tone Control and 3D Sound

- High-Pass Filter and Two-Stage Notch Filter

- Pop Noise Reduction Circuit

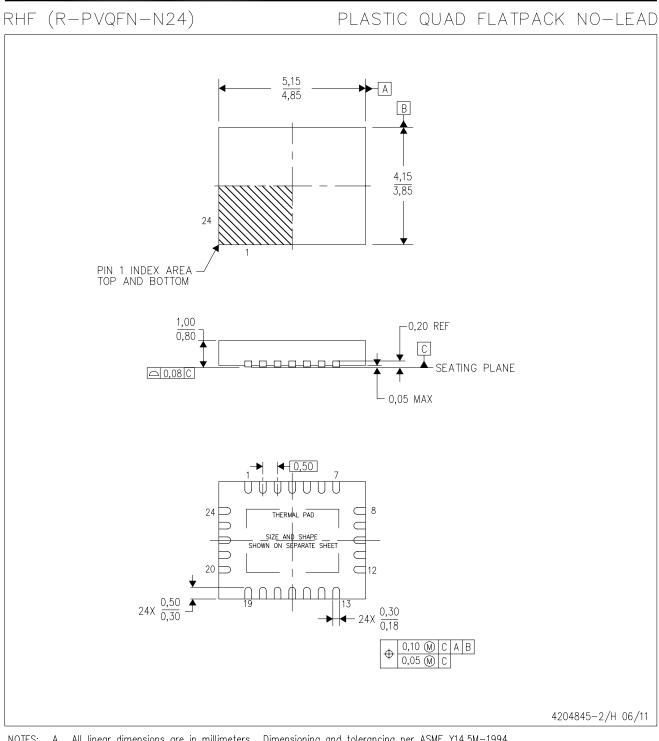

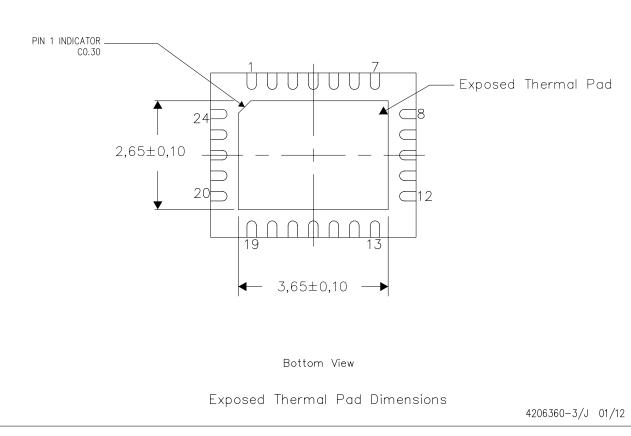

- Package:

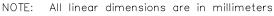

- 24-QFN (4 mm imes 5 mm)

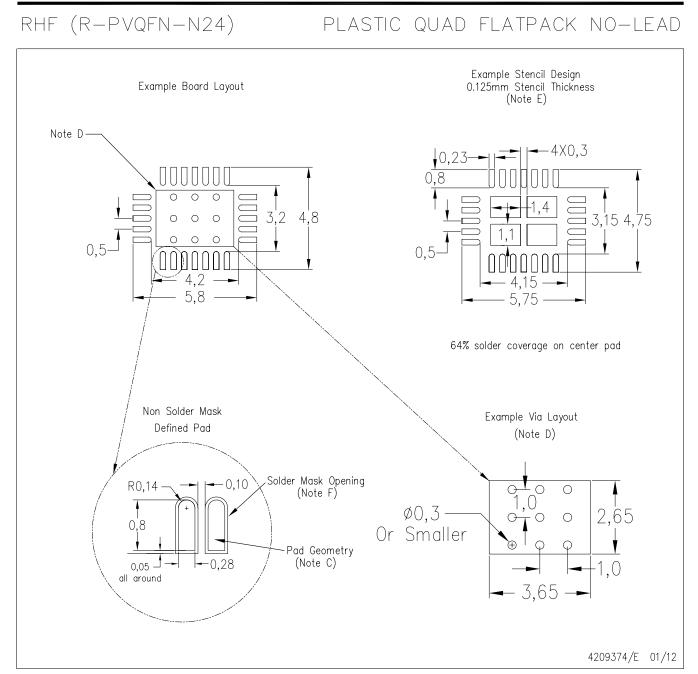

- 24-DSBGA (2.49 mm × 3.49 mm)

- Operation Temperature Range: -40°C to 85°C

# **APPLICATIONS**

- Portable Audio Player, Cellular Phone

- Video Camcorder, Movie Digital Still Camera

- PMP/DMB, Voice Recorder

# DESCRIPTION

The PCM1870 is a low-power stereo ADC designed for portable digital audio applications, with line-input amplifier, microphone amplifier, boost bias. programmable gain control, sound effects, and auto level control (ALC). It is available in 24-QFN (4-mm  $\times$ 5-mm) and 24-DSBGA (2.49-mm  $\times$  3.49-mm) packages to save footprint. The PCM1870 accepts right-justified, left-justified, l<sup>2</sup>S, and DSP formats, providing easy interfacing to audio DSP and encoder chips. Sampling rates up to 50 kHz are supported. The user-programmable functions are accessible through a 2- or 3-wire serial control port.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

# PCM1870

#### SLAS544A-MAY 2007-REVISED SEPTEMBER 2007

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                          |                                              | PCM1870    | UNIT   |

|--------------------------|----------------------------------------------|------------|--------|

| $V_{DD}, V_{IO}, V_{CC}$ | Supply voltage                               | -0.3 to 4  | V      |

|                          | Ground voltage differences: DGND, AGND, PGND | ±0.1       | V      |

|                          | Input voltage                                | -0.3 to 4  | V      |

|                          | Input current (any pins except supplies)     | ±10        | mA     |

|                          | Ambient temperature under bias               | -40 to 110 | °C     |

|                          | Storage temperature                          | -55 to 150 | °C     |

|                          | Junction temperature                         | 150        | °C     |

|                          | Lead temperature (soldering)                 | 260 / 5    | °C / s |

|                          | Package temperature (reflow, peak)           | 260        | °C     |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicted under recommended operating conditions is not impled. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### **RECOMMENDED OPERATING CONDITIONS**

|                                   |                                 |                     | MIN   | NOM  | MAX    | UNIT |

|-----------------------------------|---------------------------------|---------------------|-------|------|--------|------|

| V <sub>CC</sub>                   | Analog supply voltage           |                     | 2.4   | 3.3  | 3.6    | V    |

| V <sub>DD</sub> , V <sub>IO</sub> | Digital supply voltage          |                     | 1.71  | 3.3  | 3.6    | V    |

|                                   | Digital input logic family      |                     |       | CMOS |        |      |

|                                   |                                 | SCKI system clock   | 3.072 |      | 18.432 | MHz  |

|                                   | Digital input clock frequency   | LRCK sampling clock | 8     |      | 48     | kHz  |

|                                   | Digital output load capacitance |                     |       |      | 10     | pF   |

| T <sub>A</sub>                    | Operating free-air temperature  |                     | -40   |      | 85     | °C   |

## **ELECTRICAL CHARACTERISTICS**

All specifications at  $T_A = 25^{\circ}C$ ,  $V_{DD} = V_{IO} = V_{CC} = V_{PA} = 3.3$  V,  $f_S = 48$  kHz, system clock = 256  $f_S$ , and 16-bit data, unless otherwise noted

|                 |                                                     |                                       | PCM1870RHF, PCM1870YZF     |                      |                      |               |  |

|-----------------|-----------------------------------------------------|---------------------------------------|----------------------------|----------------------|----------------------|---------------|--|

|                 | PARAMETER                                           | TEST CONDITIONS                       | MIN                        | TYP                  | MAX                  | UNIT          |  |

|                 | ОАТА                                                |                                       |                            |                      |                      |               |  |

| Data For        | rmat                                                |                                       |                            |                      |                      |               |  |

|                 | Resolution                                          |                                       |                            | 16                   |                      | Bits          |  |

|                 | Audio data interface format                         |                                       | I <sup>2</sup> S, left-, I | right-justifie       | ed, DSP              |               |  |

|                 | Audio data bit length                               |                                       |                            | 16                   |                      | Bits          |  |

|                 | Audio data format                                   |                                       | MSB-firs                   | t, 2s-compl          | ement                |               |  |

| f <sub>S</sub>  | Sampling frequency                                  |                                       | 5                          |                      | 50                   | kHz           |  |

|                 |                                                     | V <sub>DD</sub> < 2 V                 |                            |                      | 27                   |               |  |

|                 | System clock                                        | V <sub>DD</sub> > 2 V                 |                            |                      | 40                   | MHz           |  |

| DIGITAL         | . INPUT/OUTPUT                                      |                                       |                            |                      |                      |               |  |

|                 | Logic family                                        |                                       | CMC                        | S compatil           | ole                  |               |  |

| VIH             |                                                     |                                       | 0.7 V <sub>IO</sub>        |                      |                      |               |  |

| VIL             | Input logic level                                   |                                       |                            |                      | 0.3 V <sub>IO</sub>  | VDC           |  |

| IIH             |                                                     | V <sub>IN</sub> = 3.3 V               |                            |                      | 10                   |               |  |

| IIL             | Input logic current                                 | V <sub>IN</sub> = 0 V                 |                            |                      | -10                  | μA            |  |

| V <sub>OH</sub> |                                                     | $I_{OH} = -2 \text{ mA}$              | 0.75 V <sub>IO</sub>       |                      |                      |               |  |

| V <sub>OL</sub> | Output logic level                                  | $I_{OL} = 2 \text{ mA}$               |                            |                      | 0.25 V <sub>IO</sub> | VDC           |  |

|                 | PUT TO DIGITAL OUTPUT THROUGH                       | ADC (AIN1L/R, AIN2L/R AND PGINL/R-ALC | = OFF, PG                  | 1 = PG2 =            | -                    | = 0 dE        |  |

| Dynamic         | c Performance                                       | •                                     |                            |                      |                      |               |  |

|                 |                                                     |                                       |                            | 2.828                |                      | Vp-p          |  |

|                 | Full-scale input voltage                            | 0 dB                                  |                            | 1                    |                      | Vrm           |  |

|                 | Dynamic range                                       | EIAJ, A-weighted                      |                            | 90                   |                      | dB            |  |

| SNR             | Signal-to-noise ratio                               | EIAJ, A-weighted                      | 83                         | 90                   |                      | dB            |  |

|                 | Channel separation                                  |                                       |                            | 87                   |                      | dB            |  |

| THD+N           | Total harmonic distortion + noise                   | –1 dB                                 |                            | 0.009%               | 0.017%               |               |  |

| Analog I        | Input                                               |                                       |                            |                      |                      |               |  |

|                 | Center voltage                                      |                                       |                            | 0.5 V <sub>CC</sub>  |                      | V             |  |

|                 | ¥                                                   | AIN1L, AIN1R, AIN2L, and AIN2R        | 10                         | 20                   |                      |               |  |

|                 | Input impedance                                     | PGINL and PGINR, PG3 = PG4 = -12 dB   | 70                         | 142                  |                      | kΩ            |  |

|                 |                                                     | PGINL and PGINR, PG3 = PG4 = 30 dB    | 4.7                        | 9.5                  |                      |               |  |

| ANALOO          | G OUTPUTS (AOL AND AOR)                             | 1                                     |                            |                      |                      |               |  |

|                 | Center voltage                                      |                                       |                            | 0.5 V <sub>CC</sub>  |                      | V             |  |

|                 |                                                     |                                       | 10                         | 00                   |                      | kΩ            |  |

|                 | Load resistance                                     |                                       |                            |                      |                      |               |  |

|                 | Load resistance                                     |                                       |                            |                      | 20                   | pF            |  |

| MICROP          | Load capacitance                                    | 2 = PG3 = PG4 = 0 dB                  |                            |                      | 20                   | pF            |  |

| MICROP          | Load capacitance<br>PHONE BIAS—ALC = OFF, PG1 = PG2 | 2 = PG3 = PG4 = 0 dB                  |                            | 0.75 Vcc             | 20                   | pF<br>V       |  |

| MICROP          | Load capacitance                                    | 2 = PG3 = PG4 = 0 dB                  |                            | 0.75 V <sub>CC</sub> | 20                   | pF<br>V<br>mA |  |

# **ELECTRICAL CHARACTERISTICS (continued)**

All specifications at  $T_A = 25^{\circ}$ C,  $V_{DD} = V_{IO} = V_{CC} = V_{PA} = 3.3$  V,  $f_S = 48$  kHz, system clock = 256  $f_S$ , and 16-bit data, unless otherwise noted

|                 |                                                | TEAT CONDITIONS                | PCM1870RH            | IF, PCM18         | 370YZF               |      |

|-----------------|------------------------------------------------|--------------------------------|----------------------|-------------------|----------------------|------|

|                 | PARAMETER                                      | TEST CONDITIONS                | MIN                  | TYP               | MAX                  | UNIT |

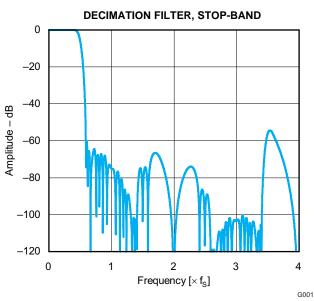

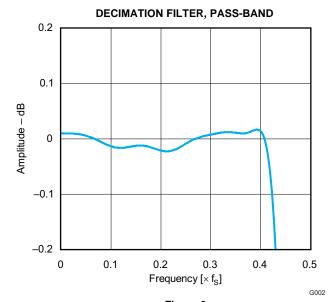

| FILTER          | R CHARACTERISTICS                              |                                | U                    |                   |                      |      |

| Decima          | ation Filter for ADC                           |                                |                      |                   |                      |      |

|                 | Pass band                                      |                                |                      |                   | 0.408 f <sub>S</sub> |      |

|                 | Stop band                                      |                                | 0.591 f <sub>S</sub> |                   |                      |      |

|                 | Pass-band ripple                               |                                |                      |                   | ±0.02                | dB   |

|                 | Stop-band attenuation                          | f < 3.268 f <sub>S</sub>       | -60                  |                   |                      | dB   |

|                 | Group delay                                    |                                |                      | 17/f <sub>S</sub> |                      | S    |

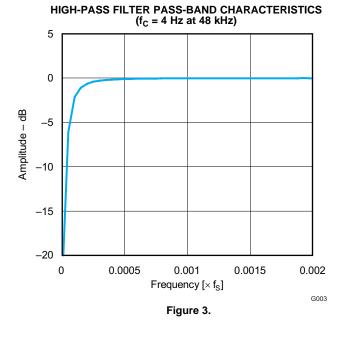

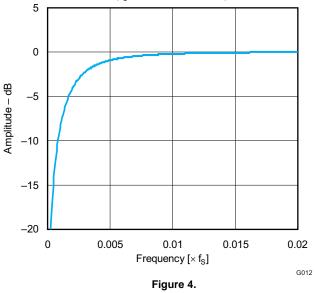

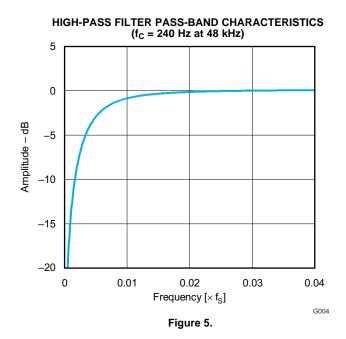

| High-P          | ass Filter for ADC                             |                                |                      |                   | i                    |      |

|                 |                                                | –3 dB                          |                      | 3.74              |                      |      |

|                 | Frequency response ( $f_c = 4 Hz$ )            | –0.5 dB                        |                      | 10.66             | 0.408 f <sub>S</sub> | Hz   |

|                 |                                                | –0.1 dB                        |                      | 24.20             |                      |      |

|                 |                                                | –3 dB                          |                      | 118.77            |                      |      |

|                 | Frequency response (f <sub>c</sub> = 120 Hz)   | –0.5 dB                        |                      | 321.75            |                      | Hz   |

|                 | $\frac{1}{10000000000000000000000000000000000$ | –0.1 dB                        |                      | 605.52            |                      |      |

|                 |                                                | –3 dB                          |                      | 235.68            |                      |      |

|                 | Frequency response (f <sub>c</sub> = 240 Hz)   | –0.5 dB                        |                      | 609.95            |                      | Hz   |

|                 |                                                | –0.1 dB                        |                      | 2601.2            |                      |      |

| POWE            | R SUPPLY AND SUPPLY CURRENT                    |                                |                      |                   | i                    |      |

| V <sub>IO</sub> |                                                | V <sub>IO</sub>                | 1.71                 | 3.3               | 3.6                  |      |

| V <sub>DD</sub> | Voltage range                                  | V <sub>DD</sub>                | 1.71                 | 3.3               | 3.6                  | VDC  |

| V <sub>CC</sub> |                                                | V <sub>cc</sub>                | 2.4                  | 3.3               | 3.6                  |      |

|                 | Curratu aurrant                                | BPZ input, all active, no load |                      | 8                 | 12                   | mA   |

|                 | Supply current                                 | All inputs are held static.    |                      | 1                 | 10                   | μA   |

|                 | Dower dissipation                              | BPZ input                      |                      | 26.4              | 39.6                 | mW   |

|                 | Power dissipation                              | All inputs are held static.    |                      | 3.3               | 33                   | μW   |

| TEMPE           | RATURE CONDITION                               |                                |                      |                   | I.                   |      |

|                 | Operation temperature                          |                                | -40                  |                   | 85                   | °C   |

| $\theta_{JA}$   | Thermal resistance                             |                                |                      | 35                |                      | °C/W |

4

P0057-01

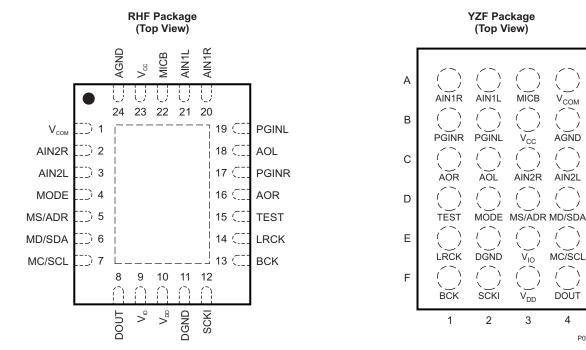

### **PIN ASSIGNMENTS**

**Table 1. TERMINAL FUNCTIONS**

| TERMINAL         |     |     |     |                                                                     |  |

|------------------|-----|-----|-----|---------------------------------------------------------------------|--|

| NAME             | N   | 0.  | I/O | DESCRIPTION                                                         |  |

| NAME             | RHF | YZF |     |                                                                     |  |

| AGND             | 24  | B4  | -   | Ground for analog                                                   |  |

| AIN1L            | 21  | A2  | I   | Analog input 1 for L-channel                                        |  |

| AIN1R            | 20  | A1  | I   | Analog input 1 for R-channel                                        |  |

| AIN2L            | 3   | C4  | I   | Analog input 2 for L-channel                                        |  |

| AIN2R            | 2   | C3  | I   | Analog input 2 for R-channel                                        |  |

| AOL              | 18  | C2  | 0   | Microphone amplifier output for L-channel                           |  |

| AOR              | 16  | C1  | 0   | Microphone amplifier output for R-channel                           |  |

| BCK              | 13  | F1  | I/O | Serial bit clock                                                    |  |

| DGND             | 11  | E2  | -   | Ground for digital                                                  |  |

| DOUT             | 8   | F4  | 0   | Serial audio data output                                            |  |

| LRCK             | 14  | E1  | I/O | O Left- and right-channel clock                                     |  |

| MC/SCL           | 7   | E4  | I   | Mode control clock for 3-wire / 2-wire interface                    |  |

| MD/SDA           | 6   | D4  | I/O | Mode control data for 3-wire / 2-wire interface                     |  |

| MICB             | 22  | A3  | 0   | Microphone bias source output                                       |  |

| MODE             | 4   | D2  | I   | 2- or 3-wire interface selection (LOW: SPI, HIGH: I <sup>2</sup> C) |  |

| MS/ADR           | 5   | D3  | I   | Mode control select for 3-wire / 2-wire interface                   |  |

| PGINL            | 19  | B2  | I   | Analog input to gain amplifier for L-channel                        |  |

| PGINR            | 17  | B1  | I   | Analog input to gain amplifier for R-channel                        |  |

| SCKI             | 12  | F2  | I   | System clock                                                        |  |

| TEST             | 15  | D1  | I   | Test Pin. Should be connected to ground.                            |  |

| V <sub>CC</sub>  | 23  | B3  | -   | Power supply for analog                                             |  |

| V <sub>COM</sub> | 1   | A4  | -   | Common voltage for analog                                           |  |

| V <sub>DD</sub>  | 10  | F3  | -   | Power supply for digital core                                       |  |

| V <sub>IO</sub>  | 9   | E3  | -   | Power supply for digital I/O                                        |  |

Copyright © 2007, Texas Instruments Incorporated

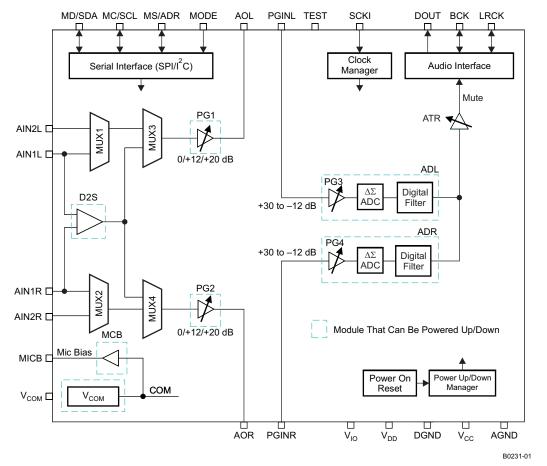

### FUNCTIONAL BLOCK DIAGRAM

### **TYPICAL PERFORMANCE CURVES**

All specifications at  $T_A = 25^{\circ}C$ ,  $V_{DD} = V_{IO} = V_{CC} = V_{PA} = 3.3$  V,  $f_S = 8$  kHz to 48 kHz, system clock = 256  $f_S$  and 16-bit data, unless otherwise noted.

Figure 1.

Figure 2.

HIGH-PASS FILTER PASS-BAND CHARACTERISTICS (f<sub>c</sub> = 120 Hz at 48 kHz)

PCM1870

SLAS544A-MAY 2007-REVISED SEPTEMBER 2007

# **TYPICAL PERFORMANCE CURVES (continued)**

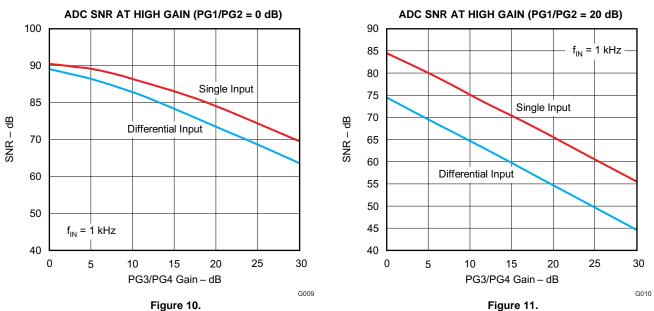

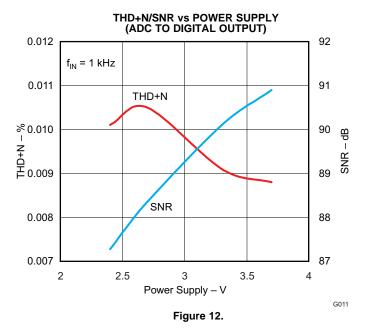

All specifications at  $T_A = 25^{\circ}C$ ,  $V_{DD} = V_{IO} = V_{CC} = V_{PA} = 3.3$  V,  $f_S = 8$  kHz to 48 kHz, system clock = 256  $f_S$  and 16-bit data, unless otherwise noted.

# PCM1870

SLAS544A-MAY 2007-REVISED SEPTEMBER 2007

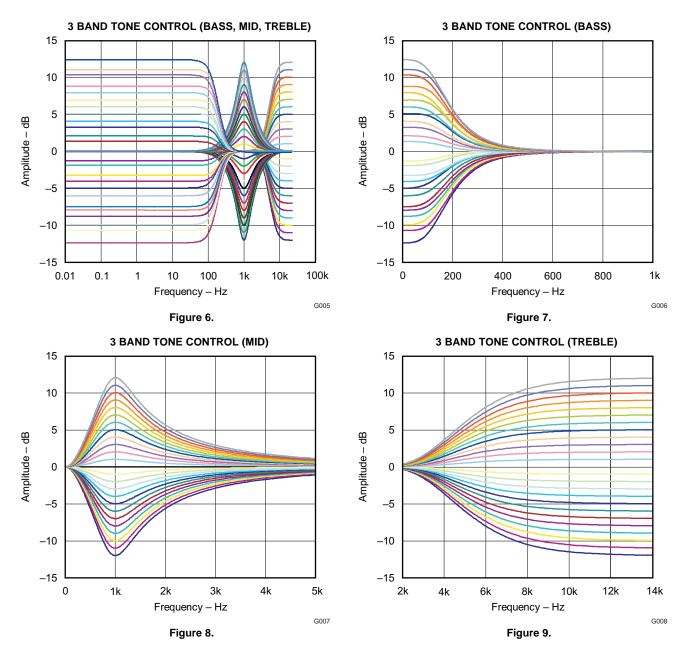

# **TYPICAL PERFORMANCE CURVES (continued)**

All specifications at  $T_A = 25^{\circ}$ C,  $V_{DD} = V_{IO} = V_{CC} = V_{PA} = 3.3$  V,  $f_S = 44.1$  kHz, system clock = 256  $f_S$  and 16-bit data, unless otherwise noted.

# **TYPICAL PERFORMANCE CURVES (continued)**

All specifications at  $T_A = 25^{\circ}C$ ,  $V_{DD} = V_{IO} = V_{CC} = V_{PA} = 3.3$  V,  $f_S = 48$  kHz, system clock = 256  $f_S$  and 16-bit data, unless otherwise noted.

### PCM1870 DESCRIPTION

### Analog Input

The AIN1L, AIN1R, AIN2L and AIN2R pins can be used as microphone or line inputs with selectable 0- or 20-dB boost and 1-Vrms input. All analog inputs have high input impedance (20 k $\Omega$ ), which is not changed by gain settings. One pair of inputs is selected by register 87 (AIL[1:0], AIR[1:0]). AIN1L and AIN1R can also be used as a monaural differential input.

### Gain Setting for Analog Input

Analog signals can be adjusted from 30 dB to -12 dB in 1-dB steps after the 0-, 12- or 20-dB boost amplifier. Gain level can be set for each channel by register 79, 80 (ALV[5:0], ARV[5:0]).

### A/D Converter

The ADC includes a multilevel delta-sigma modulator, aliasing filter, decimation filter, high-pass filter and notch filter and can accept 1 Vrms as full-scale input voltage. The decimation filter has a digital soft mute controlled by register 81 (RMUL, RMUR), and the high-pass and notch filters can be disabled by register 81 (HPF[1:0]) and registers 96 through 104 if they are not needed to cancel dc offset or avoid wind noise.

#### Common Voltage

Unbuffered common voltage. The  $V_{COM}$  pin is normally biased to 0.5  $V_{CC}$ , and it provides common voltage to internal circuitry. Connecting a 4.7- $\mu$ F capacitor to this pin is recommended to optimize analog performance.

#### Microphone Bias

The MICB pin is a microphone bias source for an external microphone, which can provide 2 mA (typ) bias current.

#### Auto Level Control (ALC) for Recording

The sound when microphone recording should be adjusted to a suitable level without saturation. The digitally controlled auto level control (ALC) automatically expands small input signals and compresses large input signals while recording. Expansion level, compression level, attack time, and recovery time can be selected by register 83. See the bit descriptions of register 83 for detailed settings.

### 3D Sound

A 3D sound effect is provided by mixing L-channel and R-channel data through a band-pass filter with two control parameters, mixing ratio and band-pass filter characteristic. The control parameters are set in register 95 (3DP[3:0], 3FLO). The 3D sound effect is applied to the ADC digital output.

#### **3-Band Tone Control**

Tone control has bass, midrange, and treble controls that can be adjusted from 12 dB to -12 dB in 1-dB steps by register 92 to 94 (LGA[4:0], MGA[4:0] and HGA[4:0]). Register 92 (LPAE), which attenuates the digital input signal automatically, can prevent clipping of the output signal at settings higher than 0 dB for bass control. LPAE is not effective for midrange and treble control.

#### High-Pass Filter and Notch Filter

The high-pass filter cuts dc offset in the analog section of the ADC and can be set to 4 Hz, 120 Hz, or 240 Hz at 48-kHz sampling by register 81 (HPF[1:0]).

Notch filters remove noise at particular frequencies, CCD noise, motor noise and other mechanical noise in an application. The PCM1870 has two notch filters, whose center frequency and frequency bandwidth can be programmed by registers 96 to 104.

### Digital Monaural Mixing

The audio data can be mixed to monaural digital data from stereo digital data in the internal audio interface section by register 96 (MXEN).

### Zero-Cross Detection

Zero-cross detection minimizes audible zipper noise while changing analog volume and digital attenuation. This function can be applied to digital input or digital output by register 86 (ZCRS).

### Power Up/Down for Each Module

Using register 73 (PBIS), register 82 (PAIR, PAIL, PADS, PMCB, PADR, PADL), and register 90 (PCOM), unused modules can be powered down to minimize power consumption (13 mW when recording only).

### **Digital Interface**

All digital I/O pins can interface at various power supply voltages. The  $V_{IO}$  pin can be connected to a 1.71-V to 3.6-V power supply.

### Power Supply

The V<sub>CC</sub> pin can be connected to 2.4 V to 3.6 V. The V<sub>DD</sub> pin and V<sub>IO</sub> pin can be connected to 1.71 to 3.6 V. A different voltage can be applied to each of these pins (for example,  $V_{DD} = 1.8$  V,  $V_{IO} = 3.3$  V).

### DESCRIPTION OF OPERATION

### System Clock Input

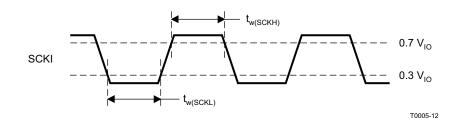

The PCM1870 can accept input clocks of various frequencies without a PLL. The clocks are used for clocking of the digital filters, auto level control, and delta-sigma modulators, and classified into common-audio and application-specific clocks. Table 2 shows frequencies of the common audio clock and the application-specific clock. Figure 13 shows timing requirements for system clock inputs. The sampling rate and frequency of the system clock are determined by settings in register 86 (MSR[2:0]) and register 85 (NPR[5:0]). Note that the sampling rate of the application-specific clock has a little sampling error. The details are shown in Table 8.

#### Table 2. Frequency of Common Audio Clock

|                            | FREQUENCY                                              |

|----------------------------|--------------------------------------------------------|

| Common audio clock         | 11.2896, 12.288, 16.9344, 18.432 MHz                   |

| Application-specific clock | 12, 13, 13.5, 24, 26, 27, 19.2, 19.68, 38.4, 39.36 MHz |

| PARAMETERS                        | SYMBOL               | MIN | UNIT |

|-----------------------------------|----------------------|-----|------|

| System clock pulse duration, high | t <sub>w(SCKH)</sub> | 14  | ns   |

| System clock pulse duration, low  | t <sub>w(SCKL)</sub> | 14  | ns   |

Figure 13. System Clock Timing

### Power-On Reset and System Reset

The power-on-reset circuit outputs reset signal, typically at  $V_{DD} = 1.2$  V, and this circuit does not depend on the voltage of other power-supplies ( $V_{CC}$ ,  $V_{PA}$ , and  $V_{IO}$ ). Internal circuits are cleared to default status, then signals are removed from all analog and digital outputs. The PCM1870 does not require any power supply sequencing. Register data must be written after turning all power supplies on.

System reset is enabled by setting register 85 (SRST), and all registers are cleared automatically. All circuits are reset to their default status at once. Note that the PCM1870 has audible pop noise on the analog outputs when enabling SRST.

### Power On/Off Sequence

To reduce audible pop noise, a sequence of register settings is required after turning all power supplies on when powering up, or before turning the power supplies off when powering down. If some modules are not required for a particular application or operation, they should be placed in the power-down state after performing the power-on sequence. The recommended power-on and power-off sequences are shown in Table 3 and Table 4, respectively.

### Table 3. Recommended Power-On Sequence

| STEP | REGISTER<br>SETTINGS | NOTE                                                               |

|------|----------------------|--------------------------------------------------------------------|

| 1    | —                    | Turn ON all power supplies <sup>(1)</sup>                          |

| 2    | 5102 <sub>H</sub>    | ADC audio interface format (left-justified) (2)                    |

| 3    | 5A00 <sub>H</sub>    | PG1, PG2 gain control (0 dB)                                       |

| 4    | 4980 <sub>H</sub>    | Analog bias power up                                               |

| 5    | 5601 <sub>H</sub>    | Zero-cross detection enable                                        |

| 6    | 4A01 <sub>H</sub>    | V <sub>COM</sub> power up                                          |

| 7    | 523F <sub>H</sub>    | Analog front end (ADL, ADR, D2S, MCB, PG1, 2, 5, 6) power up       |

| 8    | 5711 <sub>H</sub>    | Analog input (MUX3, MUX4) select. Analog input (MUX1, MUX2) select |

| 9    | 4F0C <sub>H</sub>    | Analog input L-ch (PG3) volume (0 dB) <sup>(3)</sup>               |

| 10   | 500C <sub>H</sub>    | Analog input R-ch (PG4) volume (0 dB) (3)                          |

(1) V<sub>DD</sub> should be turned on first or at the same time with other power supplies. It is recommended to set the register data after turning on all power supplies and while the system clock is running.

(2) The audio interface format should be set to match the DSP or decoder being used.

(3) Any level is acceptable for volume or attenuation. The level should return to that recorded in the register data when system was last powered off.

#### Table 4. Recommended Power-Off Sequence

| STEP | REGISTER<br>SETTINGS | NOTE                                                                                               |

|------|----------------------|----------------------------------------------------------------------------------------------------|

| 1    | 5132 <sub>H</sub>    | ADC L-ch/R-ch digital soft mute enable, ADC audio interface format (left-justified) <sup>(1)</sup> |

| 2    | 5200 <sub>H</sub>    | Analog front end (ADL, ADR, D2S, MCB, PG1, 2, 5, 6) power down                                     |

| 3    | 4A00 <sub>H</sub>    | V <sub>COM</sub> power down                                                                        |

| 4    | 4900 <sub>H</sub>    | Analog bias power down                                                                             |

| 5    | —                    | Turn OFF all power supplies. <sup>(2)</sup>                                                        |

(1) The audio interface format should be set to match the DSP or decoder being used.

(2) Power-supply sequencing is not required. It is recommended to make the required register settings while the system clock is running, then turn off all power supplies.

### **Power-Supply Current**

The current consumption of the PCM1870 depends on the power-up/down status of each circuit module. In order to save power consumption, disabling each module is recommended when it is not used in an application or operation. Table 5 shows current consumption in some states.

|                                                                       | POW                        | ER SUPPL                   |                                                    | NT [mA] | PD                                 | [mW]                               |  |

|-----------------------------------------------------------------------|----------------------------|----------------------------|----------------------------------------------------|---------|------------------------------------|------------------------------------|--|

| OPERATION MODE                                                        | V <sub>DD</sub><br>(1.8 V) | V <sub>DD</sub><br>(3.3 V) | V <sub>DD</sub> V <sub>CC</sub><br>(3.3 V) (3.3 V) |         | TOTAL<br>(V <sub>DD</sub> = 1.8 V) | TOTAL<br>(V <sub>DD</sub> = 3.3 V) |  |

| ALL POWER DOWN                                                        | 0.000                      | 0.000                      | 0.001                                              | 0.000   | 0.003                              | 0.003                              |  |

| Recording (f <sub>S</sub> = 48 kHz)                                   |                            |                            |                                                    |         |                                    |                                    |  |

| Line input (AIN2L/AIN2R)                                              | 1.78                       | 3.71                       | 4.58                                               | 0.10    | 18.3                               | 27.7                               |  |

| Mic input (AIN1L/AIN1R, 20 dB)                                        | 1.79                       | 3.71                       | 5.06                                               | 0.10    | 19.9                               | 29.3                               |  |

| Mic input (AIN1L/AIN1R, 20 dB) with ALC                               | 2.73                       | 5.59                       | 5.06                                               | 0.10    | 21.6                               | 35.5                               |  |

| Mono mic input (AIN1L, 20 dB)                                         | 1.33                       | 2.80                       | 3.56                                               | 0.10    | 14.1                               | 21.3                               |  |

| Mono mic input (AIN1L, 20 dB) with ALC                                | 2.21                       | 4.60                       | 3.56                                               | 0.10    | 15.7                               | 27.3                               |  |

| Mono diff mic input (AIN1L/AIN1R, 20 dB)                              | 1.33                       | 2.80                       | 3.88                                               | 0.10    | 15.2                               | 22.4                               |  |

| Mono diff mic input (AIN1L/AIN1R, 20 dB) with ALC                     | 2.21                       | 4.60                       | 3.88                                               | 0.10    | 16.8                               | 28.3                               |  |

| Recording (f <sub>S</sub> = 22.05 kHz)                                |                            | ••                         |                                                    | · · ·   |                                    | •                                  |  |

| Line input (AIN2L/AIN2R)                                              | 0.82                       | 1.66                       | 3.71                                               | 0.10    | 13.7                               | 18.1                               |  |

| Mic input (AIN1L/AIN1R, 20 dB)                                        | 0.82                       | 1.66                       | 4.20                                               | 0.10    | 15.3                               | 19.7                               |  |

| Mic input (AIN1L/AIN1R, 20 dB) with ALC                               | 1.26                       | 2.55                       | 4.20                                               | 0.10    | 16.1                               | 22.6                               |  |

| Mono mic input (AIN1L, 20 dB)                                         | 0.61                       | 1.23                       | 2.74                                               | 0.10    | 10.1                               | 13.4                               |  |

| Mono mic input (AIN1L, 20 dB) with ALC                                | 1.03                       | 2.10                       | 2.74                                               | 0.10    | 10.9                               | 1.63                               |  |

| Mono diff mic input (AIN1L/AIN1R, 20 dB)                              | 0.61                       | 1.23                       | 3.06                                               | 0.10    | 11.2                               | 14.5                               |  |

| Mono diff mic input (AIN1L/AIN1R, 20 dB) with ALC                     | 1.02                       | 2.08                       | 3.06                                               | 0.10    | 11.9                               | 17.3                               |  |

| Recording (f <sub>S</sub> = 16 kHz)                                   |                            |                            |                                                    |         |                                    |                                    |  |

| Line input (AIN2L/AIN2R)                                              | 0.59                       | 1.18                       | 3.51                                               | 0.10    | 12.7                               | 15.8                               |  |

| Mic input (AIN1L/AIN1R, 20 dB)                                        | 0.59                       | 1.18                       | 3.99                                               | 0.10    | 14.2                               | 17.4                               |  |

| Mic input (AIN1L/AIN1R, 20 dB) with ALC                               | 0.91                       | 1.85                       | 3.99                                               | 0.10    | 14.8                               | 19.6                               |  |

| Mono mic input (AIN1L, 20 dB)                                         | 0.44                       | 0.87                       | 2.55                                               | 0.10    | 9.2                                | 11.6                               |  |

| Mono mic input (AIN1L, 20 dB) with ALC                                | 0.75                       | 1.52                       | 2.55                                               | 0.10    | 9.8                                | 13.8                               |  |

| Mono diff mic input (AIN1L/AIN1R, 20 dB)                              | 0.44                       | 0.87                       | 2.87                                               | 0.10    | 10.3                               | 12.7                               |  |

| Mono diff mic input (AIN1L/AIN1R, 20 dB) with ALC                     | 0.74                       | 1.50                       | 2.87                                               | 0.10    | 10.8                               | 14.8                               |  |

| Recording (f <sub>S</sub> = 8 kHz)                                    |                            |                            |                                                    |         |                                    |                                    |  |

| Line input (AIN2L/AIN2R)                                              | 0.29                       | 0.54                       | 3.23                                               | 0.10    | 11.2                               | 12.8                               |  |

| Mic input (AIN1L/AIN1R, 20 dB)                                        | 0.29                       | 0.54                       | 3.72                                               | 0.10    | 12.8                               | 14.4                               |  |

| Mic input (AIN1L/AIN1R, 20 dB) with ALC                               | 0.46                       | 0.88                       | 3.72                                               | 0.10    | 13.1                               | 15.5                               |  |

| Mono mic input (AIN1L, 20 dB)                                         | 0.22                       | 0.39                       | 2.29                                               | 0.10    | 8.0                                | 9.2                                |  |

| Mono mic input (AIN1L, 20 dB) with ALC                                | 0.37                       | 0.70                       | 2.29                                               | 0.10    | 8.2                                | 10.2                               |  |

| Mono diff mic input (AIN1L/AIN1R, 20 dB)                              | 0.22                       | 0.39                       | 2.61                                               | 0.10    | 9.0                                | 10.2                               |  |

| Mono diff mic input (AIN1L/AIN1R, 20 dB) with ALC)                    | 0.37                       | 0.70                       | 2.61                                               | 0.10    | 9.3                                | 11.3                               |  |

| Condition: 256 f <sub>S</sub> , 16 bits, slave mode, zero data input, | no load                    |                            |                                                    |         |                                    |                                    |  |

### **Table 5. Power Consumption Table**

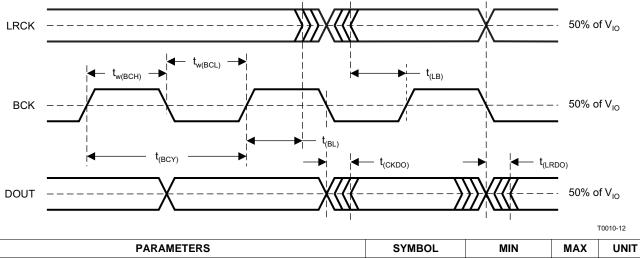

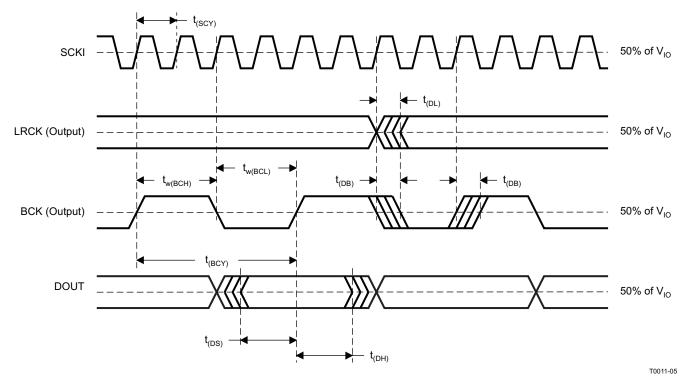

### Audio Serial Interface

The audio serial interface of the PCM1870 consists of LRCK, BCK and DOUT. Sampling rate ( $f_s$ ), left and right channel are present on LRCK. DOUT transmits the serial data from the decimation filter for the ADC. BCK is used to transmit the serial audio data on DOUT at its high-to-low transition. BCK and LRCK should be synchronized with audio system clock. Ideally, it is recommended that they are derived from it.

The PCM1870 requires LRCK to be synchronized with the system clock. The PCM1870 do not need a specific phase relationship between LRCK and the system clock.

The PCM1870 has both master mode and slave mode interface formats, which can be selected by register 84 (MSTR). LRCK and BCK are generated from the system clock in master mode.

### Audio Data Formats and Timing

The PCM1870 supports I<sup>2</sup>S, right-justified, left-justified, and DSP formats. The data formats are shown in Figure 16, and they are selected using resister 70 (RFM[1:0], PFM[1:0]). All formats require binary 2s-complement, MSB-first audio data. The default format is I<sup>2</sup>S. Figure 14 shows a detailed timing diagram.

| PARAMETERS                                                                 | SYMBOL              | MIN                                   | MAX | UNIT |

|----------------------------------------------------------------------------|---------------------|---------------------------------------|-----|------|

| BCK pulse cycle time (I <sup>2</sup> S, left- and right-justified formats) | t <sub>(BCY)</sub>  | 1/(64f <sub>S</sub> ) <sup>(1)</sup>  |     |      |

| BCK pulse cycle time (DSP format)                                          | t <sub>(BCY)</sub>  | 1/(256f <sub>S</sub> ) <sup>(1)</sup> |     |      |

| BCK high-level time                                                        | t <sub>w(BCH)</sub> | 35                                    |     | ns   |

| BCK low-level time                                                         | t <sub>w(BCL)</sub> | 35                                    |     | ns   |

| BCK rising edge to LRCK edge                                               | t <sub>(BL)</sub>   | 10                                    |     | ns   |

| LRCK edge to BCK rising edge                                               | t <sub>(LB)</sub>   | 10                                    |     | ns   |

| DOUT delay time from BCK falling edge                                      | t <sub>(CKDO)</sub> |                                       | 40  | ns   |

(1)  $f_S$  is the sampling frequency.

Figure 14. Audio Interface Timing (Slave Mode)

| PARAMETERS                      | SYMBOL              | MIN                                   | MAX | UNIT |

|---------------------------------|---------------------|---------------------------------------|-----|------|

| SCKI pulse cycle time           | t <sub>(SCY)</sub>  | 1/(256f <sub>S</sub> ) <sup>(1)</sup> |     |      |

| LRCK edge from SCKI rising edge | t <sub>(DL)</sub>   | 5                                     | 140 | ns   |

| BCK edge from SCKI rising edge  | t <sub>(DB)</sub>   | 5                                     | 140 | ns   |

| BCK pulse cycle time            | t <sub>(BCY)</sub>  | 1/(64f <sub>S</sub> ) <sup>(1)</sup>  |     |      |

| BCK high-level time             | t <sub>w(BCH)</sub> | 146                                   |     | ns   |

| BCK low-level time              | t <sub>w(BCL)</sub> | 146                                   |     | ns   |

| DOUT setup time                 | t <sub>(DS)</sub>   | 10                                    |     | ns   |

| DOUT hold time                  | t <sub>(DH)</sub>   | 10                                    |     | ns   |

(1) f<sub>S</sub> is up to 48 kHz. f<sub>S</sub> is the sampling frequency Figure 15. Audio Interface Timing (Master Mode)

# PCM1870

(a) Right-Justified Data Format; L-Channel = HIGH, R-Channel = LOW LRCK R-Channe L-Channe (= 32 f<sub>S</sub>, 48 f<sub>S</sub>, or 64 f<sub>S</sub> 16-Bit Right-Justified DOUT 15 16 15 11 12 16 MSB I SB MSB I SB (b) I<sup>2</sup>S Data Format; L-Channel = LOW, R-Channel = HIGH L-Channe R-Channel LRCK <u>ਗ਼ਗ਼ਗ਼ਗ਼ਗ਼ਗ਼ਗ਼ਗ਼ਗ਼ਗ਼ਗ਼ਗ਼ਗ਼ਗ਼ਗ਼ਗ਼ਗ਼ਗ਼ਗ਼ਗ਼ਗ਼ਗ਼ਗ਼</u> BCK ∱L∱I∱I **fififi** (= 32 f<sub>S</sub>, 48 f<sub>S</sub>, or 64 f<sub>s</sub>)<sup>(1)</sup> DOUT LSB LSB (c) Left-Justified Data Format; L-Channel = HIGH, R-Channel = LOW LRCK L-Channel R-Channel ┟┫┫┫┫┫┫┫┫┫ BCK I ♠ (= 32 f<sub>s</sub>, 48 f<sub>s</sub>, or 64 f<sub>s</sub>) DOUT 2 3 4 15 16 1 2 15 1 2 1 5 6 11 12 3 16 MSB I SB MSB LSB (d) Burst BCK Interface Format in Master Mode; L-Channel = HIGH, R-Channel = LOW LRCK I -Channel R-Channel በብብብብብብብ **fififi** ſſ BCK (= 32 f<sub>S</sub>, 48 f<sub>S</sub> DOUT 2 1 2 LSB LSB MSB (e) DSP Format LRCK <u>ללת המתומת ה</u> BCK (= 32 f<sub>s</sub>, 48 128 fo or 256 fo DOUT 5 6 12 16 1 3 15 2 R MSB LSB MSB LSB T0009-09 (1) All audio interface formats support BCK = 64 f<sub>S</sub> in master mode (register 69, MSTR = 1). When set to multisampling

rate, f<sub>S</sub> of BCK is set to half the rate of the DSM operation frequency.

### Figure 16. Audio Data Output Formats

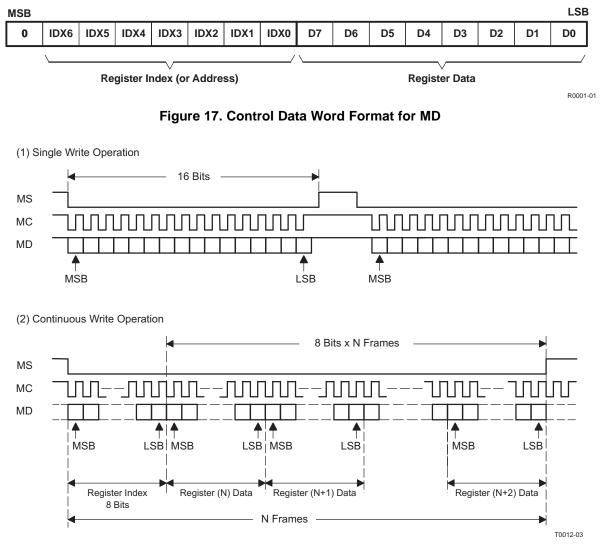

## THREE-WIRE INTERFACE (SPI, MODE (PIN 28) = LOW)

All write operations for the serial control port use 16-bit data words. Figure 17 shows the control data word format. The most significant bit must be 0. There are seven bits, labeled IDX[6:0], that set the register address for the write operation. The least-significant eight bits, D[7:0], contain the data to be written to the register specified by IDX[6:0].

Figure 18 shows the functional timing diagram for writing to the serial control port. To write the data into the mode register, the data is clocked into an internal shift register on the rising edge of the MC clock. The serial data should change on the falling edge of the MC clock and should be LOW during write mode. The rising edge of MS should be aligned with the falling edge of the last MC clock pulse in the 16-bit frame. The MC can run continuously between transactions while MS is in the LOW state.

Figure 18. Register Write Operation

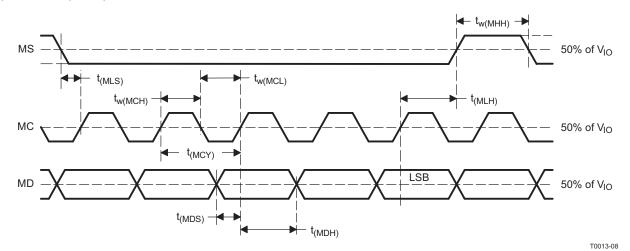

## Three-Wire Interface (SPI) Timing Requirements

Figure 19 shows a detailed timing diagram for the serial control interface. These timing parameters are critical for proper control port operation.

| PARAMETERS                        | SYMBOL              | MIN                | TYP | MAX | UNIT |

|-----------------------------------|---------------------|--------------------|-----|-----|------|

| MC pulse cycle time               | t <sub>(MCY)</sub>  | 500 <sup>(1)</sup> |     |     | ns   |

| MC low-level time                 | t <sub>w(MCL)</sub> | 50                 |     |     | ns   |

| MC high-level time                | t <sub>w(MCH)</sub> | 50                 |     |     | ns   |

| MS high-level time                | t <sub>w(MHH)</sub> | See <sup>(1)</sup> |     |     | ns   |

| MS falling edge to MC rising edge | t <sub>(MLS)</sub>  | 50                 |     |     | ns   |

| MS hold time                      | t <sub>(MLH)</sub>  | 20                 |     |     | ns   |

| MD hold time                      | t <sub>(MDH)</sub>  | 15                 |     |     | ns   |

| MD setup time                     | t <sub>(MDS)</sub>  | 20                 |     |     | ns   |

(1)  $3/(128 f_S)$  s (min), where  $f_S$  is the sampling frequency

### Figure 19. SPI Interface Timing

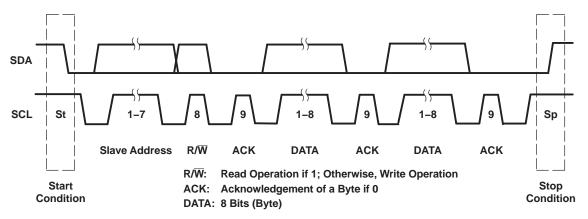

# TWO-WIRE INTERFACE [I<sup>2</sup>C, MODE (PIN 28) = HIGH]

The PCM1870 supports the  $I^2C$  serial bus and the data transmission protocol for the  $I^2C$  standard as a slave device. This protocol is explained in  $I^2C$  specification 2.0.

In I<sup>2</sup>C mode, the control terminals are changed as follows.

| TERMINAL NAME | PROPERTY     | DESCRIPTION              |

|---------------|--------------|--------------------------|

| MS/ADR        | Input        | I <sup>2</sup> C address |

| MD/SDA        | Input/output | I <sup>2</sup> C data    |

| MC/SCL        | Input        | I <sup>2</sup> C clock   |

### **Slave Address**

| MSB |   |   |   |   |   |     | LSB |  |

|-----|---|---|---|---|---|-----|-----|--|

| 1   | 0 | 0 | 0 | 1 | 1 | ADR | R/W |  |

The PCM1870 has its 7-bit slave address. The first six bits (MSBs) of the slave address are factory preset to 1000 11. The next bit of the address byte is the device select bit, which can be user-defined by ADR terminal. A maximum of two PCM1870s can be connected on the same bus at one time. Each PCM1870 responds when it receives its own slave address.

#### Packet Protocol

A master device must control packet protocol, which is start condition, slave address with read/write bit, data if write or acknowledgement if read, and stop condition. The PCM1870 supports only slave-receiver and slave-transmitter.

Write Operation

| Transmitter | М  | М             | М   | S   | М    | S   | М    | S   | М  |

|-------------|----|---------------|-----|-----|------|-----|------|-----|----|

| Data Type   | St | Slave Address | R/W | ACK | DATA | ACK | DATA | ACK | Sp |

### **Read Operation**

| Transmitter | М  | М             | М   | S   | S    | М   | S    | М    | М  |

|-------------|----|---------------|-----|-----|------|-----|------|------|----|

| Data Type   | St | Slave Address | R/W | ACK | DATA | ACK | DATA | NACK | Sp |

M: Master Device St: Start Condition S: Slave Device Sp: Stop Condition

T0049-03

### Figure 20. Basic I<sup>2</sup>C Framework

### Write Operation

A master can write any PCM1870 registers using single access. The master sends a PCM1870 slave address with a write bit, a register address, and the data. When undefined registers are accessed, the PCM1870 does not send an acknowledgement. The Figure 21 shows a diagram of the write operation.

| Transmitter | М  | М             | М | S   | М           | S   | М          | S   | М  |

|-------------|----|---------------|---|-----|-------------|-----|------------|-----|----|

| Data Type   | St | Slave Address | W | ACK | Reg Address | ACK | Write Data | ACK | Sp |

M: Master Device S: Slave Device

St: Start Condition W: Write ACK: Acknowledge Sp: Stop Condition

R0002-01

### Figure 21. Framework for Write Operation

### **Read Operation**

A master can read the PCM1870 register. The value of the register address is stored in an indirect index register in advance. The master sends a PCM1870 slave address with a read bit after storing the register address. Then the PCM1870 transfers the data which the index register points to. Figure 22 shows a diagram of the read operation.

| Transmitter | М  | М             | М | S   | М           | S   | М  | М             | М | S   | S         | М    | М  |

|-------------|----|---------------|---|-----|-------------|-----|----|---------------|---|-----|-----------|------|----|

| Data Type   | St | Slave Address | W | ACK | Reg Address | ACK | Sr | Slave Address | R | ACK | Read Data | NACK | Sp |

M: Master Device S: Slave Device St: Start Condition

Sr: Repeated Start Condition ACK: Acknowledge Sp: Stop Condition NACK: Not Acknowledge

W: Write R: Read

R0002-02

NOTE: The slave address after the repeated start condition must be the same as the previous slave address.

### Figure 22. Read Operation

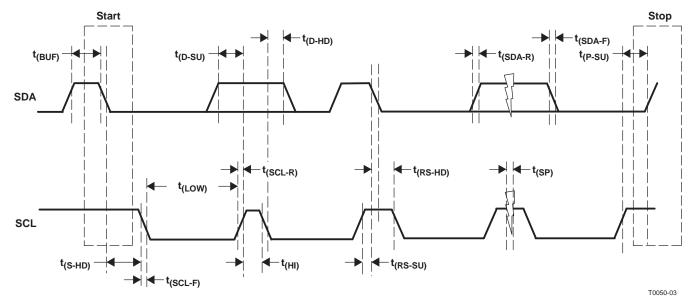

### **Timing Diagram**

| TIMING CH            | IARACTERISTICS                                   |            |                         |      |      |

|----------------------|--------------------------------------------------|------------|-------------------------|------|------|

| SYMBOL               | PARAMETER                                        | CONDITIONS | MIN                     | MAX  | UNIT |

| f <sub>SCL</sub>     | SCL clock frequency                              | Standard   |                         | 100  | kHz  |

| t <sub>(BUF)</sub>   | Bus free time between a STOP and START condition | Standard   | 4.7                     |      | μs   |

| t <sub>(LOW)</sub>   | Low period of the SCL clock                      | Standard   | 4.7                     |      | μs   |

| t <sub>(HI)</sub>    | High period of the SCL clock                     | Standard   | 4                       |      | μs   |

| t <sub>(RS-SU)</sub> | Setup time for START condition                   | Standard   | 4.7                     |      | μs   |

| t <sub>(S-HD)</sub>  | Hold time for START condition                    | Standard   | 4                       |      | μs   |

| t <sub>(D-SU)</sub>  | Data setup time                                  | Standard   | 250                     |      | ns   |

| t <sub>(D-HD)</sub>  | Data hold time                                   | Standard   | 0                       | 900  | ns   |

| t <sub>(SCL-R)</sub> | Rise time of SCL signal                          | Standard   | 20 + 0.1 C <sub>B</sub> | 1000 | ns   |

| t <sub>(SCL-F)</sub> | Fall time of SCL signal                          | Standard   | 20 + 0.1 C <sub>B</sub> | 1000 | ns   |

| t <sub>(SDA-R)</sub> | Rise time of SDA signal                          | Standard   | 20 + 0.1 C <sub>B</sub> | 1000 | ns   |

| t <sub>(SDA-F)</sub> | Fall time of SDA signal                          | Standard   | 20 + 0.1 C <sub>B</sub> | 1000 | ns   |

| t <sub>(P-SU)</sub>  | Setup time for STOP condition                    | Standard   | 4                       |      | μs   |

| C <sub>B</sub>       | Capacitive load for SDA and SCL line             |            |                         | 400  | pF   |

| t <sub>(SP)</sub>    | Pulse duration of spike suppressed               |            |                         | 25   | ns   |

Figure 23. I<sup>2</sup>C Interface Timing

### USER-PROGRAMMABLE MODE CONTROLS

### **Register Map**

The mode control register map is shown in Table 6. Each register includes an index (or address) indicated by the IDX[6:0] bits.

| REGISTER       | IDX [6:0]<br>(B14–B8) | DESCRIPTION                                              | B7   | B6   | В5   | B4   | B3   | B2   | B1   | В0   |

|----------------|-----------------------|----------------------------------------------------------|------|------|------|------|------|------|------|------|

| Register 73    | 49h                   | Analog bias power up/down                                | PBIS | RSV  |

| Register 74    | 4Ah                   | V <sub>COM</sub> power up/down                           | RSV  | PCOM |

| Register 79    | 4Fh                   | Volume for ADC input (L-ch)                              | RSV  | RSV  | ALV5 | ALV4 | ALV3 | ALV2 | ALV1 | ALV0 |

| Register 80    | 50h                   | Volume for ADC input (R-ch)                              | RSV  | RSV  | ARV5 | ARV4 | ARV3 | ARV2 | ARV1 | ARV0 |

| Register 81    | 51h                   | ADC high pass-filter, soft mute, audio interface         | HPF1 | HPF0 | RMUL | RMUR | RSV  | DSMC | RFM1 | RFM0 |

| Register 82    | 52h                   | ADC, MCB, PG1, 2, 5, 6, D2S power up/down                | RSV  | RSV  | PAIR | PAIL | PADS | PMCB | PADR | PADL |

| Register 83    | 53h                   | Auto level control for recording                         | RALC | RSV  | RRTC | RATC | RCP1 | RCP0 | RLV1 | RLV0 |

| Register 84    | 54h                   | Master mode                                              | RSV  | RSV  | RSV  | RSV  | RSV  | MSTR | RSV  | BIT0 |

| Register 85    | 55h                   | System reset, sampling rate control                      | SRST | RSV  | NPR5 | NPR4 | NPR3 | NPR2 | NPR1 | NPR0 |

| Register 86    | 56h                   | BCK config, master mode, zero cross                      | MBST | MSR2 | MSR1 | MSR0 | RSV  | RSV  | RSV  | ZCRS |

| Register 87    | 57h                   | Analog input select (MUX1, 2, 3, 4)                      | AD2S | RSV  | AIR1 | AIR0 | RSV  | RSV  | AIL1 | AIL0 |

| Register 90    | 5Ah                   | V <sub>COM</sub> power up/down, ramp up/down time, boost | RSV  | RSV  | RSV  | RSV  | RSV  | RSV  | G20R | G20L |

| Register 92    | 5Ch                   | Bass boost gain level (200 Hz)                           | LPAE | RSV  | RSV  | LGA4 | LGA3 | LGA2 | LGA1 | LGA0 |

| Register 93    | 5Dh                   | Middle boost gain level (1 kHz)                          | RSV  | RSV  | RSV  | MGA4 | MGA3 | MGA2 | MGA1 | MGA0 |

| Register 94    | 5Eh                   | Treble boost gain level (5 kHz)                          | RSV  | RSV  | RSV  | HGA4 | HGA3 | HGA2 | HGA1 | HGA0 |

| Register 95    | 5Fh                   | Sound effect source select, 3D sound                     | RSV  | 3DEN | RSV  | 3FL0 | 3DP3 | 3DP2 | 3DP1 | 3DP0 |

| Register 96    | 60h                   | 2-stage notch filter, digital monaural mixing            | NEN2 | NEN1 | NUP2 | NUP1 | RSV  | RSV  | RSV  | MXEN |

| Register 97    | 61h                   | 1st-stage notch filter lower coefficient (a1)            | F107 | F106 | F105 | F104 | F103 | F102 | F101 | F100 |

| Register 98    | 62h                   | 1st-stage notch filter upper coefficient (a1)            | F115 | F114 | F113 | F112 | F111 | F110 | F109 | F108 |

| Register 99    | 63h                   | 1st-stage notch filter lower coefficient (a2)            | F207 | F206 | F205 | F204 | F203 | F202 | F201 | F200 |

| Register 100   | 64h                   | 1st-stage notch filter upper coefficient (a2)            | F215 | F214 | F213 | F212 | F211 | F210 | F209 | F208 |

| Register 101   | 65h                   | 2nd-stage notch filter lower coefficient (a1)            | S107 | S106 | S105 | S104 | S103 | S102 | S101 | S100 |

| Register 102   | 66h                   | 2nd-stage notch filter upper coefficient (a1)            | S115 | S114 | S113 | S112 | S111 | S110 | S109 | S108 |

| Register 103   | 67h                   | 2nd-stage notch filter lower coefficient (a2)            | S207 | S206 | S205 | S204 | S203 | S202 | S201 | S200 |

| Register 104   | 68h                   | 2nd-stage notch filter upper coefficient (a2)            | S215 | S214 | S213 | S212 | S211 | S210 | S209 | S208 |

| Register 124   | 7Ch                   | Mic boost                                                | RSV  | RSV  | RSV  | RSV  | RSV  | RSV  | G12R | G12L |

| ADC: A/D conv  | erter MCB             | : Microphone bias                                        |      |      |      |      |      |      |      |      |

| PGx: Analog in | put buffer            | D2S: Differential to single-ended amplifier              |      |      |      |      |      |      |      |      |

| Register 73   |         |          |         | -        |        |         |                    |         |         |            |     | -   |            |     |     |      |

|---------------|---------|----------|---------|----------|--------|---------|--------------------|---------|---------|------------|-----|-----|------------|-----|-----|------|

|               | B15     | B14      | B13     | B12      | B11    | B10     | B9                 | B8      | B7      | <b>B</b> 6 | B5  | B4  | <b>B</b> 3 | B2  | B1  | B0   |

| Register 73   | 0       | IDX6     | IDX5    | IDX4     | IDX3   | IDX2    | IDX1               | IDX0    | PBIS    | RSV        | RSV | RSV | RSV        | RSV | RSV | RSV  |

| IDX[6:0]: 1   | 00 10   | 01b (4   | 19h) R  | egiste   | er 73  |         |                    |         |         |            |     |     |            |     |     |      |

| PBIS: Pow     | er Up   | /Dow     | n Cor   | trol f   | or Bia | IS      |                    |         |         |            |     |     |            |     |     |      |

| Default valu  | ue: 0   |          |         |          |        |         |                    |         |         |            |     |     |            |     |     |      |

| This bit is u | ised to | o cont   | rol po  | wer u    | o/dow  | n for t | he an              | alog bi | as circ | uit.       |     |     |            |     |     |      |

| PBIS = 0      | I       | Power of | down (d | lefault) |        |         |                    |         |         |            |     |     |            |     |     |      |

| PBIS = 1      | l       | Power u  | qu      |          |        |         |                    |         |         |            |     |     |            |     |     |      |

| Register 74   | 4       |          |         |          |        |         |                    |         |         |            |     |     |            |     |     |      |

| <b>j</b>      | B15     | B14      | B13     | B12      | B11    | B10     | B9                 | B8      | B7      | <b>B6</b>  | B5  | B4  | B3         | B2  | B1  | B0   |

| Register 74   | 0       | IDX6     | IDX5    | IDX4     | IDX3   | IDX2    | IDX1               | IDX0    | RSV     | RSV        | RSV | RSV | RSV        | RSV | RSV | PCOM |

| IDX[6:0]: 1   | 00 10   | 10b (4   | IAh) F  | Reaiste  | er 74  |         |                    |         |         |            |     |     |            |     |     |      |

| PCOM: Po      |         | ``       | ,       | •        |        | сом     |                    |         |         |            |     |     |            |     |     |      |

| Default valu  |         | •        |         |          |        | 00.11   |                    |         |         |            |     |     |            |     |     |      |

| This bit is u | ised to | o cont   | rol po  | wer u    | o/dow  | n for \ | V <sub>сом</sub> . |         |         |            |     |     |            |     |     |      |

| PCOM = 0      |         | Power of | down (d | lefault) |        |         |                    |         |         |            |     |     |            |     |     |      |

| PCOM = 0 | Power down (default) |

|----------|----------------------|

| PCOM = 1 | Power up             |

| Register 79 | ) and | 80   |      |      |      |      |      |      |     |     |      |      |      |      |      |      |

|-------------|-------|------|------|------|------|------|------|------|-----|-----|------|------|------|------|------|------|

| -           | B15   | B14  | B13  | B12  | B11  | B10  | B9   | B8   | B7  | B6  | B5   | B4   | B3   | B2   | B1   | B0   |

| Register 79 | 0     | IDX6 | IDX5 | IDX4 | IDX3 | IDX2 | IDX1 | IDX0 | RSV | RSV | ALV5 | ALV4 | ALV3 | ALV2 | ALV1 | ALV0 |

| Register 80 | 0     | IDX6 | IDX5 | IDX4 | IDX3 | IDX2 | IDX1 | IDX0 | RSV | RSV | ARV5 | ARV4 | ARV3 | AR2  | ARV1 | ARV0 |

### IDX[6:0]: 100 1111b (4Fh) Register 79

IDX[6:0]: 101 0000b (50h) Register 80

### ALV[5:0]: Gain Control for PG3 (ADC Analog Input R-Channel)

### ARV[5:0]: Gain Control for PG4 (ADC Analog Input L-Channel)

Default value: 00

PG3 and PG4 can be independently controlled for ADC input from 30 dB to -12 dB in 1-dB steps. ADC output may have zipper noise when changing levels. In the PCM1870, the noise can be reduced when making the change by using zero-cross detection (Register 85, ZCRS).

| ALV[5:0], A | RV[5:0] |                    | ALV[5:0], A | RV[5:0] |                    |

|-------------|---------|--------------------|-------------|---------|--------------------|

| BINARY      | HEX     | GAIN LEVEL SETTING | BINARY      | HEX     | GAIN LEVEL SETTING |

| 10 1010     | 2A      | 30 dB              | 01 0100     | 14      | 8 dB               |

| 10 1001     | 29      | 29 dB              | 01 0011     | 13      | 7 dB               |

| 10 1000     | 28      | 28 dB              | 01 0010     | 12      | 6 dB               |

| 10 0111     | 27      | 27 dB              | 01 0001     | 11      | 5 dB               |

| 10 0110     | 26      | 26 dB              | 01 0000     | 10      | 4 dB               |

| 10 0101     | 25      | 25 dB              | 00 1111     | 0F      | 3 dB               |

| 10 0100     | 24      | 24 dB              | 00 1110     | 0E      | 2 dB               |

| 10 0011     | 23      | 23 dB              | 00 1101     | 0D      | 1 dB               |

| 10 0010     | 22      | 22 dB              | 00 1100     | 0C      | 0 dB               |

| 10 0001     | 21      | 21 dB              | 00 1011     | 0B      | –1 dB              |

| 10 0000     | 20      | 20 dB              | 00 1010     | 0A      | -2 dB              |

| 01 1111     | 1F      | 19 dB              | 00 1001     | 09      | –3 dB              |

| 01 1110     | 1E      | 18 dB              | 00 1000     | 08      | -4 dB              |

| 01 1101     | 1D      | 17 dB              | 00 0111     | 07      | –5 dB              |

| 01 1100     | 1C      | 16 dB              | 00 0110     | 06      | -6 dB              |

| 01 1011     | 1B      | 15 dB              | 00 0101     | 05      | -7 dB              |

| 01 1010     | 1A      | 14 dB              | 00 0100     | 04      | 8 dB               |

| 01 1001     | 19      | 13 dB              | 00 0011     | 03      | –9 dB              |

| 01 1000     | 18      | 12 dB              | 00 0010     | 02      | –10 dB             |

| 01 0111     | 17      | 11 dB              | 00 0001     | 01      | –11 dB             |

| 01 0110     | 16      | 10 dB              | 00 0000     | 00      | -12 dB (default)   |

| 01 0101     | 15      | 9 dB               |             |         |                    |

### Table 7. Gain Level Setting

| Register 8 <sup>-</sup> | 1   |      |      |      |      |      |      |      |      |      |      |      |     |      |      |      |

|-------------------------|-----|------|------|------|------|------|------|------|------|------|------|------|-----|------|------|------|

|                         | B15 | B14  | B13  | B12  | B11  | B10  | B9   | B8   | B7   | B6   | B5   | B4   | B3  | B2   | B1   | B0   |

| Register 81             | 0   | IDX6 | IDX5 | IDX4 | IDX3 | IDX2 | IDX1 | IDX0 | HPF1 | HPF0 | RMUL | RMUR | RSV | DSMC | RFM1 | RFM0 |

**IDX[6:0]:** 101 0001b (51h) Register 81

### HPF[1:0]: High-Pass Filter Selection

Default value: 00

The PCM1870 has a digital high-pass filter to remove dc voltage at the input of the ADC. The cutoff frequency of the high-pass filter can be selected.

| HPF[1:0] | High Pass Filter Selection                |

|----------|-------------------------------------------|

| 0 0      | f <sub>C</sub> = 4 Hz at 48 kHz (default) |

| 0 1      | f <sub>C</sub> = 240 Hz at 48 kHz         |

| 10       | f <sub>C</sub> = 120 Hz at 48 kHz         |

| 11       | High-pass filter disabled                 |

### **RMUL: Digital Soft Mute Control for ADC L-Channel**

### **RMUR: Digital Soft Mute Control for ADC R-Channel**

Default value: 1

The digital output of the ADC can be independently muted or unmuted. The transition from the current volume level to mute, or the return to the previous volume setting from mute, occurs at the rate of one 1-dB step for each  $8/f_S$  time period. When RMUL and RMUR = 0, the digital data is increased from mute to the previous attenuation level, and when RMUL and RMUR = 1, the digital data is decreased from the current attenuation level to mute. In the PCM1870, audible zipper noise can be reduced by using zero-cross detection (register 85, ZCRS).

RMUL, RMUR = 0 Mute disabled RMUL, RMUR = 1 Mute enabled (default)

### DSMC: Waiting Time Turn ADC Mute Off at Power Up

Default value: 0

ADC digital output has waiting time at power up when DSMC = 0. It is recommended to set DSMC = 0.

| DSMC = 0 | 10 ms at 48 kHz (default) |

|----------|---------------------------|

| DSMC = 1 | No wait                   |

### RFM[1:0]: Audio Interface Selection for ADC (Digital Output)

Default value: 00

The audio interface format for ADC digital output has I<sup>2</sup>S, right-justified, left-justified, and DSP formats.

| RFM[1:0] | Audio Interface Selection for ADC Digital Output |

|----------|--------------------------------------------------|

| 0 0      | I <sup>2</sup> S (default)                       |

| 0 1      | Right-justified                                  |

| 10       | Left-justified                                   |

| 11       | DSP mode                                         |

| Register 82 | 2<br>B15 | B14  | B13  | B12  | B11  | B10  | В9   | B8   | B7  | B6  | В5   | В4   | B3   | B2   | B1   | В0   |  |

|-------------|----------|------|------|------|------|------|------|------|-----|-----|------|------|------|------|------|------|--|

| Register 82 | 0        | IDX6 | IDX5 | IDX4 | IDX3 | IDX2 | IDX1 | IDX0 | RSV | RSV | PAIR | PAIL | PADS | PMCB | PADR | PADL |  |

### **IDX[6:0]:** 101 0010b (52h) Register 82

### PAIR: Power Up/Down for PG2 and PG6 (Gain Amplifier for Analog Input R-Channel)

PAIR: Power Up/Down for PG1 and PG5 (Gain Amplifier for Analog Input L-Channel)

Default value: 0

This bit is used to control power up/down for PG1, -2 and PG5, -6 (gain amplifier for analog input).

PAIR, PAIL = 0 Power down (default) PAIR, PAIL = 1 Power up

#### PADS: Power Up/Down for D2S (Differential Amplifier) of AIN1L and AIN1R

Default value: 0

This bit is used to control power up/down for D2S (differential-to-single amplifier).

| PADS = 0 | Power down (default) |

|----------|----------------------|

| PADS = 1 | Power up             |

### PMCB: Power Up/Down Control for Microphone Bias Source

Default value: 0

This bit is used to control power up/down for the microphone bias source.

| PMCB = 0 | Power down (default) |

|----------|----------------------|

| PMCB = 1 | Power up             |

### PADR: Power Up/Down Control for ADR (ADC and Digital Filter R-Channel)

### PADL: Power Up/Down Control for ADL (ADC and Digital Filter L-Channel)

Default value: 0

This bit is used to control power up/down for the ADC and decimation filter.

PADR, PADL = 0 Power down (default) PADR, PADL = 1 Power up

### TEXAS NSTRUMENTS www.ti.com

#### SLAS544A-MAY 2007-REVISED SEPTEMBER 2007

#### **Register 83**

| •           | B15 | B14  | B13  | B12  | B11  | B10  | B9   | B8   | B7   | B6  | B5   | B4   | B3   | B2   | B1   | B0   |

|-------------|-----|------|------|------|------|------|------|------|------|-----|------|------|------|------|------|------|

| Register 83 | 0   | IDX6 | IDX5 | IDX4 | IDX3 | IDX2 | IDX1 | IDX0 | RALC | RSV | RRTC | RATC | RCP1 | RCP0 | RLV1 | RLV0 |

### IDX[6:0]: 1010011b (53h) Register 83

### **RALC: Automatic Level Control (ALC) Enable for Recording**

Default value: 0

Auto level control can be enabled with some parameters for microphone input or lower-level analog source.

| RALC = 0 | Disabled (default) |

|----------|--------------------|

| RALC = 1 | Enabled            |

### **RRTC: ALC Recovery Time Control for Recording**

### Default value: 0

This bit selects the time during which a gain level change completes to compress the signal when the input to the ADC increases in amplitude.

| RRTC = 0 | 3.4 s (default) |

|----------|-----------------|

| RRTC = 1 | 13.6 s          |

### **RATC: ALC Attack Time Control for Recording**

#### Default value: 0

This bit selects the time during which a gain level change completes to expand the signal when the input to the ADC decreases in amplitude.

| RATC = 0 | 1 ms (default) |

|----------|----------------|

| RATC = 1 | 2 ms           |

### RCP[1:0]: ALC Compression Level Control for Recording

#### Default value: 00

Auto level control can set the compression level to -2, -6, or -12 dB. Higher-level signals should be compressed to avoid saturation or degradation of sound quality.

| RCP[1:0] | ALC Compression Level Control for Recording |

|----------|---------------------------------------------|

| 0 0      | -2 dB (default)                             |

| 0 1      | -6 dB                                       |

| 10       | –12 dB                                      |

| 11       | Reserved                                    |

### RLV[1:0]: ALC Expansion Level Control for Recording

### Default value: 00

Auto level control can set the expansion level to 0, 6, 14, or 24 dB. Lower-level signals should be expanded to make a small signal easy to hear. If set to 0 dB, the ALC can be operated only as a limiter.

| RLV[1:0] | ALC Expansion Level Control for Recording |