January 2012

# FAB3103 2.3 Watt Class-D Audio Amplifier with Integrated

**Boost Regulator and Automatic Gain Control**

### Features

FAIRCHILD

- High Output, Low Distortion Class-D Mono Speaker Amplifier

- o 2.3W into 8Ω from 3.6V Supply (10% THD+N)

- $\circ$  1.85W into 8 $\Omega$  from 3.6V Supply (1% THD+N)

- o 0.01% THD+N into 8Ω (100mW)

- High-Efficiency Boost Regulator Provides Higher Output Power Over Li-Ion Battery Voltages

ο 85% Total Efficiency (3.6V, 8Ω, P<sub>Ω</sub> = 1.0W)

- Adaptive Boost Shutdown at Lower Output Power Increases Efficiency and Reduces Quiescent Current Consumption:

- $\circ$  I<sub>DD</sub> = 2.7mA from 3.6V Supply

- Automatic Gain Control (AGC) Monitors Battery Voltage and Dynamically Adjusts Gain, Extending Battery Runtime

- Reduced Noise Floor Enhances Audio Playback

38µV Output Noise (A-Weighted)

- 100dB SNR (A-Weighted)

- Low-EMI Design Allows Filterless Operation

- High-Power Supply Ripple Rejection:

- 88dB PSRR (f<sub>RIPPLE</sub> = 217Hz, Boost Enabled)

70dB PSRR (f<sub>RIPPLE</sub> = 217Hz, Boost Bypassed)

- High Noise Rejection Using Differential Audio Inputs:

- 75dB CMRR (f<sub>IN</sub> = 1kHz)

- 71dB CMRR (f<sub>IN</sub> = 217Hz)

- Short-Circuit Protection

- Under-Voltage Protection

- "Click and Pop" Suppression

- Available in 12-Bump, 0.5mm Pitch, WLCSP

Space-Saving 1.86mm x 1.44mm Package

### Description

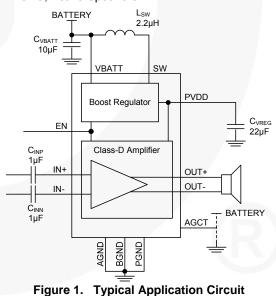

The FAB3103 is a mono Class-D audio amplifier with an integrated boost regulator that achieves high output audio over a power supply range of 2.5V to 5.2V.

Automatic Boost Shutdown dynamically shuts down the boost regulator at low output power for greater efficiency and lower quiescent current consumption.

Automatic Gain Control (AGC) monitors the battery and reduces gain as the battery voltage drops to limit maximum current consumption, extending battery runtime and preventing mobile device shutdown.

### Applications

- Smart Phones, Feature Phones

- Tablets, Portable Gaming Devices

- GPS, Active Speakers

### **Ordering Information**

| Part Number | Operating Temperature Range | Package                                                         | Packing Method               |

|-------------|-----------------------------|-----------------------------------------------------------------|------------------------------|

| FAB3103UCX  | -40°C to +85°C              | 12-Bump, 0.5mm Pitch, Wafer-Level<br>Chip-Scale Package (WLCSP) | 3000 Units<br>on Tape & Reel |

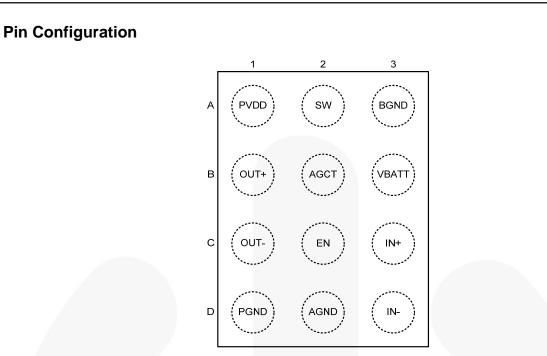

### Pin Definitions

| WLCSP | Name  | Туре         | Description                                                                                                   |  |  |  |

|-------|-------|--------------|---------------------------------------------------------------------------------------------------------------|--|--|--|

| B1    | OUT+  | Output       | Positive audio output                                                                                         |  |  |  |

| C1    | OUT-  | Output       | Negative audio output                                                                                         |  |  |  |

| C3    | IN+   | Analog Input | Positive audio input                                                                                          |  |  |  |

| D3    | IN-   | Analog Input | Negative audio input                                                                                          |  |  |  |

| C2    | EN    | CMOS Input   | Shutdown signal for boost regulator and amplifier:<br>VBATT=enabled, PGND=shutdown (internal 300KΩ pull-down) |  |  |  |

| B2    | AGCT  | Analog Input | AGC trip-point setting                                                                                        |  |  |  |

| B3    | VBATT | Power        | Supply voltage                                                                                                |  |  |  |

| A2    | SW    | Power        | Boost regulator switching node                                                                                |  |  |  |

| A1    | PVDD  | Power        | Boost regulator output                                                                                        |  |  |  |

| A3    | BGND  | Ground       | Boost regulator ground – connect to PGND and AGND with a ground plane.                                        |  |  |  |

| D1    | PGND  | Ground       | Power ground – connect to BGND and AGND with a ground plane.                                                  |  |  |  |

| D2    | AGND  | Ground       | Analog ground – connect to BGND and PGND with a ground plane.                                                 |  |  |  |

### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol            | Parameter                                               | Min. | Max.                      | Unit             |

|-------------------|---------------------------------------------------------|------|---------------------------|------------------|

| V <sub>BATT</sub> | Voltage on VBATT Pin                                    | -0.3 | 6.0                       | V                |

| V <sub>OUT</sub>  | Voltage on OUT-, OUT+ Pins                              | -0.3 | V <sub>BSTOUT</sub> + 0.3 | V                |

| V <sub>IN</sub>   | Voltage on IN+, IN-, SW, EN, AGCT Pins                  | -0.3 | V <sub>BATT</sub> + 0.3   | V                |

| VINDIFF           | Differential Voltage Across IN+, IN- Pins While Enabled | -1.5 | 1.5                       | V <sub>rms</sub> |

| PD                | Power Dissipation                                       |      | Internally Limited        |                  |

### **Dissipation Ratings**

| Symbol           | Parameter                                                                | Min. | Тур. | Max. | Unit |

|------------------|--------------------------------------------------------------------------|------|------|------|------|

| TJ               | Junction Temperature                                                     |      |      | 150  | °C   |

| T <sub>STG</sub> | Storage Temperature Range                                                | -65  |      | 150  | °C   |

| TL               | Lead Temperature (Soldering, 10s)                                        |      |      | 300  | °C   |

| $\Theta_{JA}$    | Thermal Resistance, JEDEC Standard, Multilayer Test<br>Boards, Still Air |      | 77   |      | °C/W |

### **Electrostatic Discharge Protection**

| Symbol | Parameter                  | Condition                                                                                                              | Level | Unit |

|--------|----------------------------|------------------------------------------------------------------------------------------------------------------------|-------|------|

|        | Human Body Model (HBM)     | EIA/JESD22-A114                                                                                                        | ±3    | ΚV   |

| ESD    | Charged Device Model (CDM) | According to "EIA/JESD22-C101 Level III"<br>Compatible with "IEC61340-3-3 Level C4" or<br>"ESD-STM5.3.1-1999 Level C4" | ±1    | κv   |

### **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol             | Parameter                                 | Min.               | Тур. | Max. | Unit |

|--------------------|-------------------------------------------|--------------------|------|------|------|

| TA                 | Operating Temperature Range               | -40                |      | 85   | °C   |

| $V_{BATT}$         | V <sub>BATT</sub> Supply Voltage Range    | 2.5                | 4.5/ | 5.2  | V    |

| Lsw                | Inductor (at Peak Inductor Current: 1.5A) | 1.4 <sup>(1)</sup> | 2.2  |      | μH   |

| C <sub>VBATT</sub> | VBATT Capacitor                           | 4.7 <sup>(1)</sup> | 10.0 |      | μF   |

| $C_{\text{PVDD}}$  | PVDD Capacitor                            | 6.8 <sup>(1)</sup> | 22.0 |      | μF   |

| CAGCT              | Capacitive Load on AGCT                   |                    |      | 10   | pF   |

| $R_L$              | Load Resistance                           |                    | 8    |      | Ω    |

Note:

1. Capacitors experience degradation over time and this is accelerated with increased temperature. It is therefore recommended to use the stated typical values.

FAB3103 — 2.3 Watt Class-D Audio Amplifier with Integrated Boost Regulator and Automatic Gain Control

### **Electrical Characteristics**

Unless otherwise noted: AGCT=GND,  $R_L=8\Omega + 33\mu$ H, f=1KHz, and audio measurement bandwidth=22Hz to 20KHz (AES17). Typical values are at V<sub>BATT</sub>=3.6V, T<sub>A</sub>=25°C, with typical external component values.

| Symbol               | Parameter                                                      | Cor                                                                        | nditions                                        | Min. | Тур. | Max. | Uni |

|----------------------|----------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------|------|------|------|-----|

| I <sub>DD</sub>      | Quiescent Current                                              | Inputs AC Grounded, E                                                      | EN=HIGH                                         |      | 2.7  |      | mA  |

| I <sub>SD</sub>      | Shutdown Current                                               | EN=PGND, Inputs AC                                                         | EN=PGND, Inputs AC Grounded                     |      | 0.1  | 2.0  | μA  |

| t <sub>wu</sub>      | Wake-Up Time                                                   | From LOW to HIGH EN                                                        | N Transition to Full                            |      | 5    | 12   | ms  |

| f <sub>SW(AMP)</sub> | Class-D Switching<br>Frequency                                 |                                                                            |                                                 |      | 300  |      | KHz |

| Vos                  | Differential Output Offset<br>Voltage                          | Inputs AC Grounded                                                         |                                                 |      | 1.67 | 5.00 | mV  |

| Av                   | Gain                                                           | AGC Inactive                                                               |                                                 | 9.5  | 10.0 | 10.5 | V/V |

|                      | Innut Desistance                                               | Gain=10V/V                                                                 | Differential                                    | 24   | 30   | 36   | KO  |

| R <sub>IN</sub>      | Input Resistance                                               | (AGC Inactive)                                                             | Single-Ended                                    | 12   | 15   | 18   | KΩ  |

| R <sub>STD</sub>     | Single-Ended Input<br>Impedance During<br>Shutdown             | EN=PGND, AC-Couple<br>per Input                                            | ed Inputs, V <sub>INx</sub> < 2V <sub>rms</sub> | 80   |      |      | KΩ  |

| V <sub>STD</sub>     | Maximum Single-Ended<br>Input Voltage Swing<br>During Shutdown | EN=PGND, AC-Coupled Inputs                                                 |                                                 | 2    |      |      | Vrm |

|                      | THD+N Added to Audio<br>Signal at Inputs During<br>Shutdown    | EN=PGND, AC-Coupled Inputs,<br>Source Impedance < 1Ω                       |                                                 |      |      | 0.02 | %   |

|                      | Total Harmonic Distortion                                      | P <sub>OUT</sub> =100mW                                                    |                                                 |      | 0.01 |      |     |

| THD+N                | Plus Noise                                                     | P <sub>OUT</sub> =500mW                                                    |                                                 |      | 0.02 |      | %   |

| _                    |                                                                | THD+N $\leq$ 10%                                                           |                                                 |      | 2.3  |      |     |

| Po                   | Output Power                                                   | THD+N $\leq$ 1%                                                            |                                                 |      | 1.85 |      | W   |

| I <sub>DLMT</sub>    | Class-D Output Current<br>Limit                                |                                                                            |                                                 |      | 1.4  |      | A   |

|                      |                                                                | Inputs Shorted, AC<br>Grounded, Output                                     | f <sub>RIPPLE</sub> =1KHz, Boost<br>Enabled     |      | 85   |      |     |

| PSRR                 | Power Supply Rejection                                         | Referred;<br>V <sub>RIPPLE</sub> =200mV <sub>P-P</sub>                     | f <sub>RIPPLE</sub> =217Hz, Boost<br>Enabled    |      | 88   |      | dB  |

|                      | Ratio                                                          | Square Centered<br>Around V <sub>BATT</sub> =3.8V,<br>50% Duty Cycle, 10µs | f <sub>RIPPLE</sub> =1KHz, Boost<br>Bypassed    |      | 77   |      |     |

|                      |                                                                | Rise/Fall Time                                                             | f <sub>RIPPLE</sub> =217Hz, Boost<br>Bypassed   |      | 70   |      |     |

|                      |                                                                | Output Referred,                                                           | f <sub>RIPPLE</sub> =1KHz                       |      | 75   |      |     |

|                      |                                                                | V <sub>RIPPLE</sub> =200m V <sub>P-P</sub><br>Square, 50% Duty             |                                                 |      |      |      |     |

| CMRR                 | Common-Mode Rejection                                          | Cycle, 10µs Rise/Fall                                                      |                                                 |      |      |      | dB  |

|                      | Ratio                                                          | Time, Inputs Shorted<br>and AC-Coupled to<br>VRIPPLE                       | f <sub>RIPPLE</sub> =217Hz                      | 71   |      |      |     |

| $V_{\text{BIAS}}$    | IN+, IN- Bias Voltage                                          |                                                                            |                                                 |      | 1.2  |      | V   |

| η                    | Efficiency                                                     | R <sub>L</sub> =8Ω + 33μH , P <sub>OUT</sub> =                             | 1.0W                                            |      | 85   |      | %   |

FAB3103 — 2.3 Watt Class-D Audio Amplifier with Integrated Boost Regulator and Automatic Gain Control

### **Electrical Characteristics**

Unless otherwise noted: AGCT=GND,  $R_L=8\Omega + 33\mu$ H, f=1KHz, and audio measurement bandwidth=22Hz to 20KHz (AES17). Typical values are at  $V_{BATT}=3.6V$ ,  $T_A=25^{\circ}$ C, with typical external component values.

| Symbol                      | Parameter                                   | Conc                                                    | litions                 | Min.  | Тур.  | Max.  | Unit             |

|-----------------------------|---------------------------------------------|---------------------------------------------------------|-------------------------|-------|-------|-------|------------------|

|                             |                                             | P <sub>OUT</sub> =1.85W, A-Weighte                      | d                       |       | 100   |       |                  |

| SNR                         | Signal-To-Noise Ratio                       | POUT=1.85W, Unweighte                                   | d                       |       | 97    |       | dB               |

|                             |                                             | A-Weighted                                              |                         |       | 38    |       |                  |

| en                          | Output Noise                                | Unweighted                                              |                         |       | 51    |       | μV <sub>rm</sub> |

| $T_{STD}$                   | Thermal Shutdown                            | Junction Temperature                                    |                         |       | 165   |       | °C               |

| T <sub>HYS</sub>            | Thermal Shutdown<br>Hysteresis              | Junction Temperature                                    |                         |       | 25    |       | °C               |

| V <sub>ULVO</sub>           | VBATT Under-Voltage Shut                    | down                                                    |                         | 1.8   | 2.1   | 2.3   | V                |

| $V_{\text{HYS}}$            | VBATT Under-Voltage Hyst                    | eresis                                                  |                         |       | 120   | 300   | mV               |

| $f_{\text{SW}(\text{REG})}$ | Boost Converter Switching                   | g Frequency                                             |                         |       | 1.2   |       | MHz              |

| ILIMIT(SU)                  | Boost Converter Inrush<br>Current Limit     | PV <sub>DD</sub> Rising from 0V to V <sub>BATT</sub>    |                         |       |       | 600   | mA               |

| t <sub>INRUSH</sub>         | Boost Converter Inrush<br>Time              | PV <sub>DD</sub> Rising from 0V to V <sub>BATT</sub>    |                         |       |       | 1000  | μs               |

|                             | Auto Boost Startup<br>Current Ramp Rate     | $PV_{DD}$ Rising from $V_{BATT}$ to 5.6V                |                         |       | 15    |       | mΑ/μ             |

| I <sub>BOOST</sub>          | Boost Converter Peak<br>Input Current Limit | Open-Loop Limit                                         |                         | 1100  | 1600  | 2100  | mA               |

| V <sub>BSTOUT</sub>         | Boost Converter Output Voltage              |                                                         |                         | 5.55  | 5.65  | 5.75  | V                |

| V <sub>BSTSTD</sub>         | Auto Boost Shutdown Thr                     | eshold Voltage                                          |                         |       | 2     |       | V <sub>pk</sub>  |

| t <sub>HOLD</sub>           | Auto Boost Shutdown Hol                     | d Time                                                  |                         |       | 125   |       | ms               |

|                             |                                             | AGCT=Floating                                           |                         | 3.190 | 3.250 | 3.283 | 5                |

| V <sub>AGC</sub>            | AGC Trip Point                              | AGCT=GND                                                |                         | 3.480 | 3.550 | 3.586 | V                |

|                             |                                             | AGCT=VBATT                                              |                         | 3.680 | 3.750 | 3.788 | 1                |

|                             |                                             | AGCT=GND,                                               | V <sub>BATT</sub> =3.4V |       | 0.79  |       |                  |

|                             | Output Power with AGC                       | V <sub>IN</sub> =0.4V <sub>pk</sub> , 1KHz Sine<br>Wave | V <sub>BATT</sub> =3.0V |       | 0.45  |       | W                |

| t <sub>A</sub>              | AGC Attack Time                             |                                                         |                         |       | 20    |       | µs/dE            |

| t <sub>R</sub>              | AGC Release Time                            |                                                         |                         |       | 1600  |       | ms/d             |

|                             | AGC Step Size                               |                                                         |                         |       | 0.5   |       | dB               |

|                             | AGC Maximum Attenuation                     | n                                                       |                         |       | 10    |       | dB               |

| VIH                         | EN Logic Input High Voltage                 |                                                         | 1.1                     |       |       | V     |                  |

| VIL                         | EN Logic Input Low Voltag                   | ge                                                      |                         |       |       | 0.45  | V                |

| CIN                         | EN Capacitance                              |                                                         |                         |       | 10    |       | pF               |

| R <sub>PD</sub>             | EN Pull-Down Resistance                     |                                                         |                         |       | 300   |       | KΩ               |

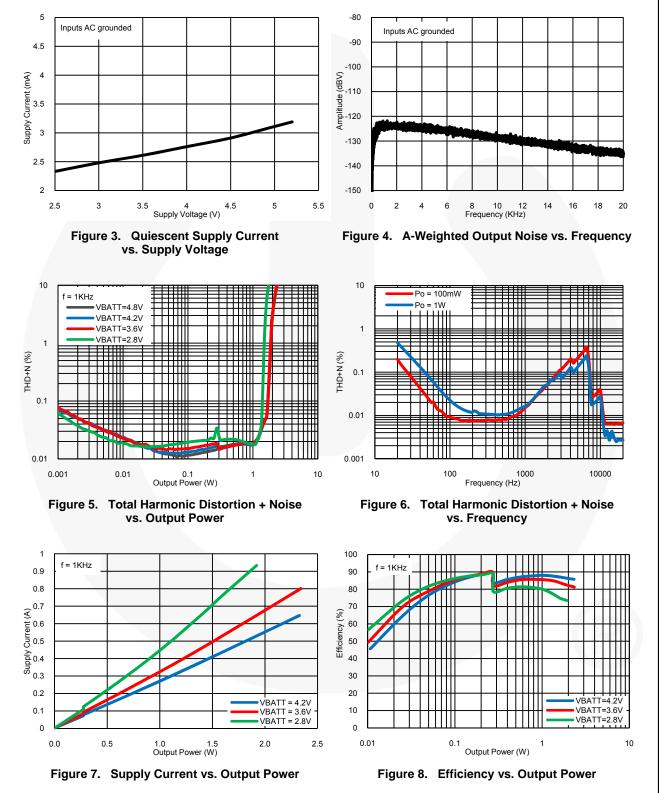

### **Typical Performance Characteristics**

Unless otherwise noted: AGCT = GND,  $R_L = 8\Omega + 33\mu H$ , f = 1KHz, audio measurement bandwidth 22Hz to 20KHz (AES17),  $V_{BATT} = 3.6V$ ,  $T_A = 25^{\circ}C$ , typical external component values.

### **Detailed Description**

### **Signal Path**

The FAB3103 features a fully differential signal path for noise rejection. The low-EMI design allows the OUT+ and OUT- pins to be connected directly to a speaker without an output filter.

The input section includes an 80KHz low-pass filter for removing out-of-band noise from audio sources, such as sigma delta DACs.

### Shutdown

If EN is grounded, the Class-D amplifier and the boost regulator are turned off. IN+ and IN- are high impedance. Audio signals present at IN+ and IN- with amplitude less than the maximum differential input voltage swing are not distorted by the FAB3103 (see *Electrical Characteristics*).

When EN transitions from LOW to HIGH during the wake-up time (see Electrical Characteristics), the FAB3103 charges the input DC blocking capacitors to the Common Mode voltage before enabling the Class-D amplifier. To minimize click and pop during turn-on, audio signals should not be present during the wake-up period. Other devices that are connected to the same input signal, if not muted, may experience a pop due to this capacitor charging.

There is no limitation on the length of shutdown. Remaining charge on the PVDD capacitor at startup (for example, if EN is LOW for only a short period) does not affect startup behavior.

The EN pin has an internal  $300K\Omega$  pull-down resistor. EN must be LOW when V<sub>BATT</sub> is lower than the V<sub>BATT</sub> under-voltage shutdown voltage (see Electrical Characteristics). EN must remain LOW for at least 100µs after V<sub>BATT</sub> rises above the V<sub>BATT</sub> under-voltage shutdown voltage.

### **Class-D Amplifier Over-Current Protection**

If the output current of the Class-D amplifier exceeds limits (see the Electrical Characteristics), the amplifier is disabled for approximately one second. (Other systems, such as the boost regulator and AGC, remain active.) After one second, the amplifier is re-enabled. If the fault condition still exists, the amplifier is disabled again. This cycle repeats until the fault condition is removed.

### **Speaker Size**

The FAB3103 was designed for use with small speakers found in mobile applications. The back EMF in larger speakers can cause PVDD to peak above safe levels. To check safe operation, monitor PVDD while driving a dynamic signal (such as music) at maximum levels. If PVDD peaks above 6.2V, connect a 6V Zener diode between PVDD and PGND.

### Low EMI

To minimize EMI, edge-rate control for the boost regulator and Class-D amplifier can be employed.

The boost regulator's edge-rate control is disabled by default. For devices with 20ns boost edge rates or 10ns boost edge rates, contact a Fairchild Representative. This is a factory option that cannot be changed in the application, but is available from Fairchild.

The Class-D amplifier's edge-rate control is disabled by default. For devices with 20ns Class-D edge rates, contact a Fairchild Representative. This is a factory option that cannot be changed in the application, but is available from Fairchild.

### **Automatic Boost Shutdown**

Automatic boost shutdown changes the Class-D amplifier supply voltage as a function of audio output level. At audio output levels above  $2V_{pk}$ , the boost converter generates 5.65V from the input battery voltage. If the output level is below  $2V_{pk}$  for more than 125ms, the boost converter is switched off and the Class-D amplifier is supplied directly from the battery. As a result, efficiency is improved at low audio output levels and quiescent current consumption is reduced.

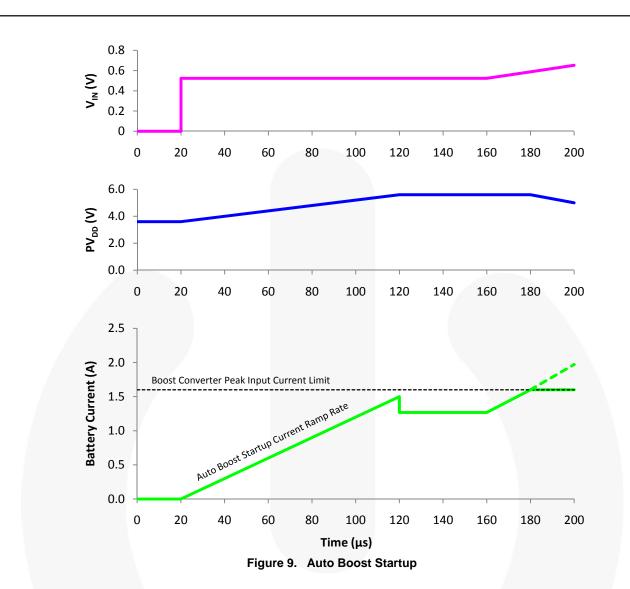

Figure 9 shows an example of an auto boost startup event. At first, the boost converter is off and PVDD is the same voltage as VBATT. At 20µs, a large audio signal is presented at the inputs, which causes the boost converter to start up. From 20µs to 120µs, battery current is ramped up. The auto boost startup current ramp rate is 15mA/µs. This ramp is enforced to avoid sudden current draw spikes from the battery.

At 120 $\mu$ s, after PV<sub>DD</sub> has reached the Boost Converter Output Voltage, the ramp is released and battery current falls to a level capable of sustaining the speaker amplifier's outputs. At 160 $\mu$ s, the input signal begins to rise, which increases battery current. At 180 $\mu$ s, the boost converter peak input current limit is enforced and battery current levels off, which causes PV<sub>DD</sub> to droop.

The boost regulator should not be used to drive any loads other than the Class-D amplifier.

### Automatic Gain Control

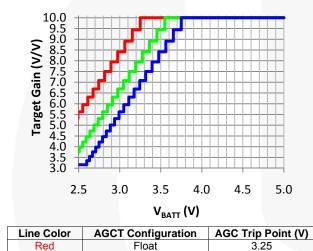

Due to constant output power, the amount of VBATT current needed to maintain a given output amplitude is inversely proportional to VBATT voltage. This produces very large current requirements at low  $V_{BATT}$ . The AGC eases low- $V_{BATT}$  current demands by reducing the gain when VBATT voltage drops below a trip point. One of three different trip points may be selected by shorting AGCT to VBATT, shorting AGCT to PGND, or floating *AGCT* (see Electrical Characteristics).

The trip point is determined upon power-on and when EN transitions from LOW to HIGH. If AGCT is changed during operation, the new value is not read until power or EN is cycled.

When  $V_{BATT}$  is above the trip point, the AGC has no effect on the signal path.

When  $V_{BATT}$  is at or below the trip point, target gain is reduced in 0.5dB steps according to the equation:

$$G_{t \operatorname{arg} et} = G_{I} - S_{L}G_{I}\left(\frac{V_{T} - V_{batt}}{V_{out \max}}\right)$$

(1)

where:

Green

Blue

$V_T$  = AGC trip point set by the AGCT pin; and

V<sub>BATT</sub> = Voltage at the VBATT pin.

Target gain can be reduced by as much as 10dB.

Note that the state of auto boost shutdown has no effect on the AGC.

Figure 10 shows target gain vs. battery voltage.

| Figure 10. | Taraat ( | lain ve | Rattory ' | AnetioV |

|------------|----------|---------|-----------|---------|

3.55

3.75

Ground

VBATT

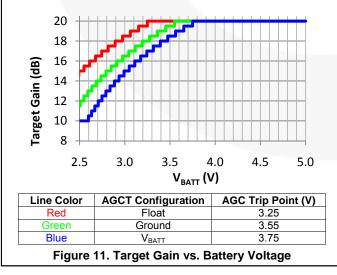

Figure 11 is similar to Figure 10 except that the target gain is expressed in dB rather than V/V.

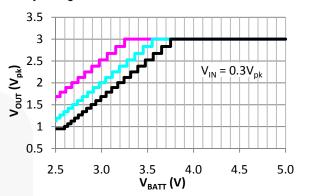

Figure 12 shows examples of peak output voltage vs. battery voltage.

| Line<br>Color | AGCT<br>Configuration | AGC Trip<br>Point (V) | Input Voltage<br>(V <sub>pk</sub> ) |

|---------------|-----------------------|-----------------------|-------------------------------------|

| Magenta       | Float                 | 3.25                  | 0.3                                 |

| Cyan          | Ground                | 3.55                  | 0.3                                 |

| Black         | VBATT                 | 3.75                  | 0.3                                 |

Figure 12. Output Voltage vs. Battery Voltage

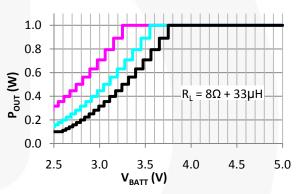

Figure 13 shows examples of output power vs. battery voltage with a  $0.4V_{pk}$  sinusoidal input signal.

| Line<br>Color | AGCT<br>Configuration | AGC Trip<br>Point (V) | Input Voltage<br>(V <sub>pk</sub> ) |

|---------------|-----------------------|-----------------------|-------------------------------------|

| Magenta       | Float                 | 3.25                  | 0.3                                 |

| Cyan          | Ground                | 3.55                  | 0.3                                 |

| Black         | VBATT                 | 3.75                  | 0.3                                 |

### Figure 13. Output Power vs. Battery Voltage Examples (V<sub>IN</sub>=0.4V<sub>pk</sub> Sine)

The speed at which gain can change is limited (see *Electrical Characteristics*); therefore, the actual gain may lag the target gain if  $V_{BATT}$  voltage changes quickly.

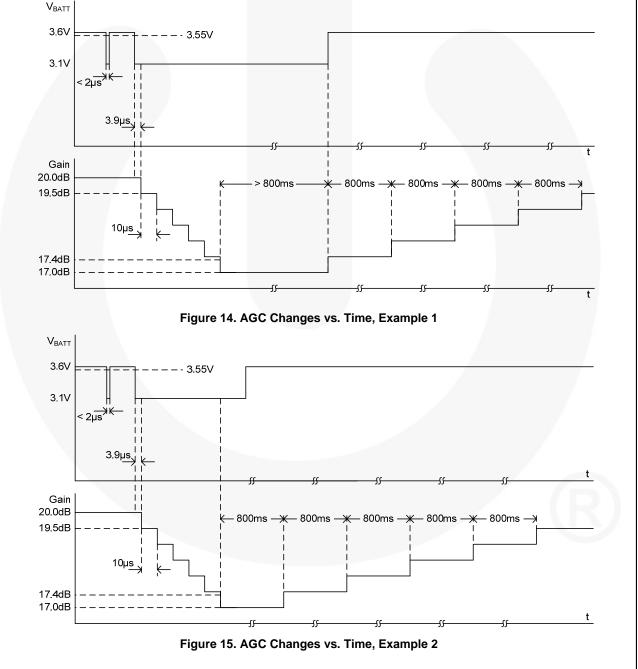

Figure 14 and Figure 15 show examples of AGC changes over time. In these examples, AGCT is grounded, so the AGC trip point is 3.55V.

- 1. Initially, V<sub>BATT</sub> is 3.6V and gain is 10V/V (20dB).

- 2. A narrow  $V_{\text{BATT}}$  drop of less than 2µs is ignored by the AGC.

- 3. The next  $V_{BATT}$  drop lasts longer and the AGC is tripped. The initial 0.5dB gain reduction occurs 3.9µs after  $V_{BATT}$  crosses below the 3.55V trip point.

- 4.  $V_{BATT}$  is now 3.1V, so target gain is  $10V/V 3V/V \times 10V/V \times [(3.55V 3.1V) / 5.2V] = 7.40V/V = 17.4dB.$

- 5. Gain continues to drop by 0.5dB every 10µs until it is below the target gain, where it settles at 17.0dB.

- When V<sub>BATT</sub> rises above the trip point, gain increases by 0.5dB. If more than 800ms has passed since the last gain change, gain rises immediately, as shown in Figure 14. Otherwise, gain does not rise until after 800ms has passed, as shown in Figure 15.

- 7. While  $V_{BATT}$  remains above the trip point, gain continues to increase by 0.5dB every 800ms until it returns to 20dB.

The intent of the AGC circuitry is to limit current draw from the battery to extend runtime. This is particularly important for handsets that incorporate advanced shutdown algorithms to measure battery voltage. The AGC circuit dynamically adjusts the amplifier gain based on the trip point used. Even though the amplifier gain is reduced in response to lower battery voltages, two conditions result in continued higher current draw: 1) the handset volume is turned up in an attempt to maintain the same loudness, or 2) the input signal is increased. If one or both of these conditions exist, even though the amplifier gain is reduced in response to lower battery voltage, current draw remains elevated, eventually resulting in handset shutdown.

# FAB3103 2.3 Watt Class-D Audio Amplifier with Integrated Boost Regulator and Automatic Gain Control

## **Applications Information**

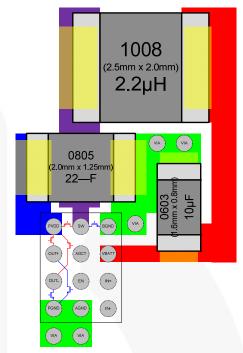

### Layout Considerations

General layout and supply bypassing play a major role in analog performance and thermal characteristics. Fairchild offers an evaluation board to guide layout and aid device evaluation. Contact a Fairchild representative for information about evaluation boards. Following the recommended layout configuration (shown in Figure 16) provides optimum performance for the device. For best results, follow the steps and recommended routing rules listed below.

### **Recommended Routing / Layout Rules**

- Do not run analog and digital signals in parallel.

- Traces must run on top of the ground plane.

- Avoid routing at 90° angles.

CVBATT

- . Place bypass capacitors within 2.54mm (0.1 inches) of the device power pin.

- . Minimize all trace lengths to reduce series inductance.

- Connect BGND, PGND, and AGND together using a single ground plane.

Figure 16. Recommended PCB Layout

### Vendor Part Number Value Component Murata LQM2HPN2R2NJCL 2.2µH Lsw Murata GRM21AR60J226UE80K 22µF CPVDD Murata GRM188R60J106UE82J 10µF

### Table 1 – Recommended Passive Components

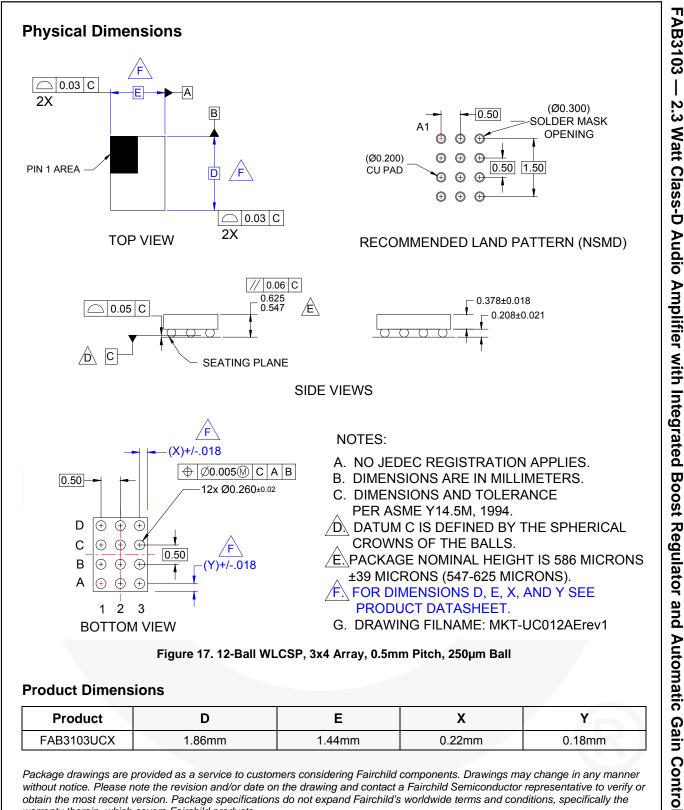

### **Product Dimensions**

| Product    | D      | E      | X      | Y      |

|------------|--------|--------|--------|--------|

| FAB3103UCX | 1.86mm | 1.44mm | 0.22mm | 0.18mm |

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent version. Package specifications do not expand Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductors online packaging area for the most recent packaging drawings and tape and reel specifications. http://www.fairchildsemi.com/packaging/